но соединены с выходами первого и третьего одноразрядных коммутаторов, информационный вход третьего одноразрядного коммутатора соединен с выходом генератора импульсов, подключенного к счетному входу счетчика, вход генератора импульсов соединен с выходом второго одноразрядного коммутатора, соединенного с установочным входом триггера, и является вьгходом окончания преобразования преобразователя, выход элемента И-НЕ соединен

с BTopbiM управляющим входом второго одноразрядного коммутатора, информационный вход которого соединен с выходом второго элемента И, входы которого соединены с выходами регистра двоичного кода, вход записи регистра двоично-десятичного кода соединен с выходом элемента ИЛИ, второй вход которого соединен с выходом третьего одноразрядного коммутатора,выход регистра двоичного кода подключен к второму информационному входу сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1975 |

|

SU708344A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1989 |

|

SU1662005A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1978 |

|

SU742923A1 |

| Устройство для преобразования двоично-десятичного кода в двоичный код и обратно | 1990 |

|

SU1755375A1 |

| Преобразователь двоичного кода вдВОичНО-дЕСяТичНый и дВОичНО-дЕСяТичНОгОВ дВОичНый | 1979 |

|

SU849197A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1985 |

|

SU1292188A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1292187A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОЙ ДРОБИ В ДВОИЧНУЮ ДРОБЬ | 1979 |

|

SU826335A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283979A1 |

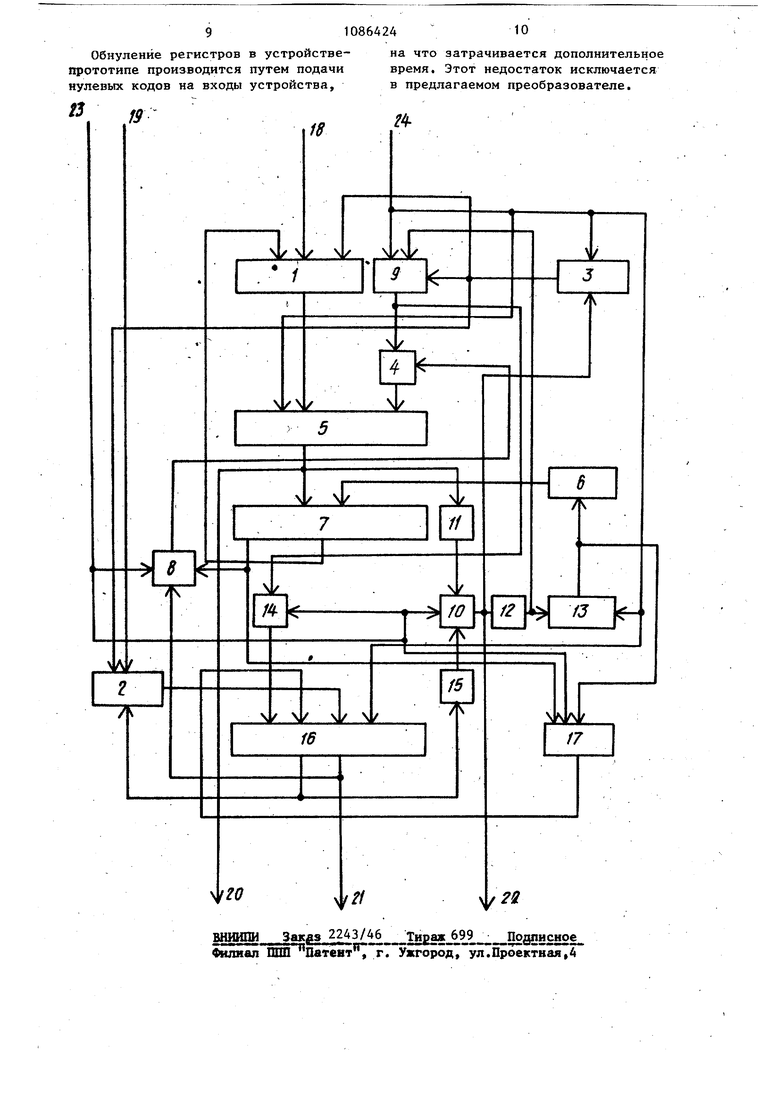

ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В ДВОИЧНО-ДЕСЯТИЧНЬЙ И ОБРАТНО, содержащий регистр двоичного кода, регистр двоично-десятичного кода, сумматор, блок хранения эквивалентов, выход которого соединен с первым информационным входом сумматора, генератор импульсов, первый и второй элементы И, элемент ИЛИ, отличающийся тем, что, с целью повьшения быстродействия, в него введены первый и второй многоразрядные коммутаторы, первый, второй и третий одноразрядные коммутаторы, счетчик, дешифратор, триггер и элемент И-НЕ, причем сумматор и блок хранения эквивалентов выполнены двоичными, выходы счетчика соединены с разрядными входами дешифратора и блока хранения эквивалентов, выходы дешифратора соединены с первой группой информационных входов регистр двоич но-десятйчного кода, выходы которого соединены с входами элемента И-НЕ и с первой группой информационных входов первого многоразрядного коммутатора, вторая группа информационных входов которого является первой группой информационных входов преобразователя, управляющий вход которого соединен с первыми управляющими входами первого и второго одноразрядных коммутаторов, первым входом элемента ИЛИ и запрещающим входом де- шифратора, выход переноса сумматора соединен с управляющим входом- дешифратора и информагционным входом первого одноразрядного коммутатора, второй управляющий вход которого соединен с выходом старшего разряда регистра двоично-десятичного кода, вторая группа информационных входов которого соединена с выходами первоQ б го многоразрядного коммутатора, уп(Л равляющий вход которого соединен с выходом триггера, подключенного к (Управляющему входу второго многоразрядного коммутатора и первому управляющему входу третьего одноразрядного коммутатора, второй управляющий ход которого является входом начальной установки преобразоватеоо ля и соединен с входами сброса триг05 гера, счетчика, регистров двоичного и двоично-десятичного кодов, выходы которых являются соответственно первой и второй группами информационных выходов преобразователя, вторая группа информационных входов которого соединена с первыми информационными входами второго многоразрядного коммутатора, вторы)е информационные входы которого соединены с выходами сумматора, а выходы соединены с инфорцаIционными входами регистра двоичного кода, вход записи которого соединен с выходом первого элемента И, первый и второй входы которого соответствен

Изобретение относится к области цифровой вычислительной техники и может быть использовано в специализированных устройствах и вычислительных машинах..

Известен преобразователь двоичного кода в двоично-десятичный и обратно, содержащий регистр двоичного числа, регистр двоично-десятичного числа, формирователь эквивалентов, переключатель эквивалентов, одноразрядный сумматор и блок управлениями

Недостаток данного преобразователя состоит в низком быстродействии что является следствием последовательной обработки значений разрядов. Наиболее близким к предлагаемому по технической сущности и схемному решению является преобразователь двоичного кода в двоично-десятичный и двоично-десятичного кода в двоичный, содержащий регистр двоичного числа, блок двоично-десятичных эквивалентов, двоично-десятнчньй : сумматор регистр двоично-десятичных чисел, распределитель импульсов, схему сравнения, генератор импульсов, первый и второй элементы И, элемент ИЛИ, элемент НЕ, первую, вторую, третью и четвертую группь элементов И, примем выходы распределителя импульсов подключены к входам первой и второй групп элементов И, к вторым входам которых присоединены выходы разрядов двоичного регистра, выходы элементов И первой и второй групп подключены к входам блока двоично-десятичных эквивалентов, выходы которого подклю чены к входам двоично-десятичного

сумматора, выходы которого соединены с входами регистра двоично-десятичны чисел С 2 3.

Недостаток этого преобразователя состоит в относительно низкой средней скорости преобразования в режиме преобра- ования двоичного кода в двоино-десятичный, связанной с последовательным опросом всех разрядов двоичного числа.

Целью изобретения является повышение быстродействия преобразователя

Поставленная цель достигается тем, что в преобразователь двоичного кода в двоично-десятичный и обратно, содержащий регистр, двоичного кода, регистр двоично-десятичного кода, сумматор, блок хранения эквивалентов выход которого соединен с первым информационным входом сумматора, генератор импульсов, первый и второй элементы И, элемент ИЛИ, введены первый и второй многоразрядные -коммутаторы, первый, второй и третий одноразрядные коммутаторы, счетчик, дешифратор, триггер и элемент И-НЕ, причем сумматор и блок хранения эквивалентов выполнены двоичными, выходы счетчика соединены с разрядными входами дешифратора и блока хранения эквивалентов, выходы дешифратора соединены с первой группой информационных входов регистра двоично-десятичного кода, выходы которого соединены с входами элемента И-НЕ и с первой группой информационных входов первого многоразрядного коммутатора, вторая группа информационных входов которого является первой группой информационных входов преобразователя, управляющий вход которого соединен с первыми управляющими входами первого и второго одноразрядных коммутаторов, первым входом элемента ИЛИ и запрещающим входом дешифратора, выход переноса сумматора соединен с управляющим входом дешифратора и информационным входом первого одноразрядного коммутатора, второй управляющий вход которого соединен с выходом старшего разряда регистра двоично-десятичного кода, вторая группа информационных входов которого соединена с выходами первого многоразрядного коммутатора, управляющий вход которого соединен с выходом триггера, подключенного к управляющему входу второго многоразрядного коммутатора и первому управляющему входу третьего одноразряд ного коммутатора, второй управляющий вход которого является входом началь ной установки преобразователя и соединен с входами сброса триггера, счетчика, регистров двоичного и двои но-десятичного кодов, выходы которых являются соответственно первой и второй группами информационных выходов преобразователя, вторая группа информационных входов которого соеди нена с первыми информационными входа ми второго многоразрядного коммутатора, вторые информационные входы которого соединены с выходами сумматора, а вьпсоды соединены с информационными входами регистра двоичного кода, вход записи которого соединен с выходом первого элемента И, первый и.второй входы которого соответствен-40

но соединены с выходами первого и третьего одноразрядных коммутаторов, информационный вход третьего одноразрядного коммутатора соединен с выходом генератора импульсов, подключенного к счетному входу счетчика, вход генератора импульсов соединен с выходом второго одноразрядного коммутатора, соединенного с установочным входом триггера, и является выходом окончания преобразования преобразователя, выход элемента И-НЕ соединен с вторым управляющим входом второго одноразрядного коммутатора, информационный вход которого соединен с выходом второго элемента И, входы которого соединены с выходами регистра двоичного кода, вход записи

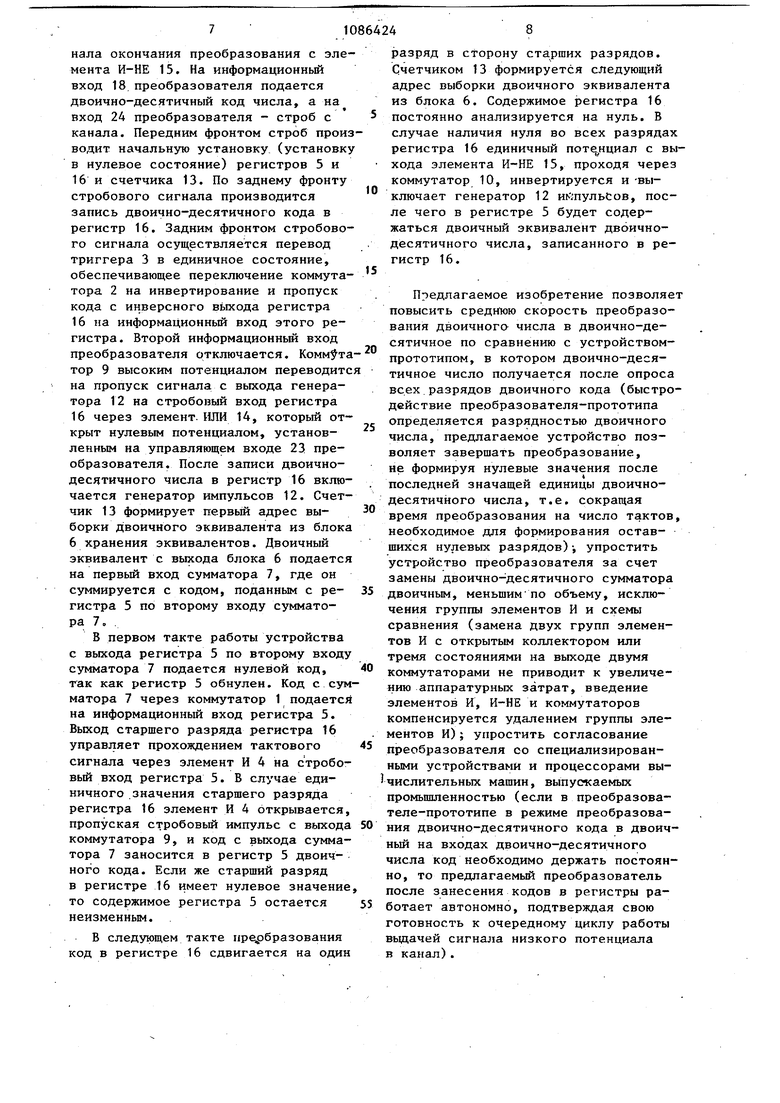

ляющем входе 23 преобразователя до подачи кода числа устанавливается высокий потенциал. На информационный вход 18 преобразователя подаетрегистра двоично-десятичного кода соединен с выходом элемента ИЛИ, второй вход которого соединен с выходом третьего одноразрядного коммутатора, выход регистра двоичного кода подключен к второму информационному входу cyviMaTopa. На чертеже приведена структурная схема предлагаемого преобразователя. Преобразователь содержит многоразрядные коммутаторы 1 и 2, триггер 3, элемент И 4, регистр 5 двоичного кода, двоичный блок 6 хранения эквивалентов, двоичный сумматор 7, одноразрядные коммутаторы 8-10, элемент И 11, генератор 12 импульсов, счетчик 13, элемент ИЛИ 14, элемент И-НЕ 15, регистр 16 двоично-десятичного кода, дешифратор 17. Коммутатор 1 предназначен для передачи в регистр 5 инвертированного двоичного кода с информационного входа 18 преобразователя или прямого кода с выхода сумматора 7. Коммутатор 2 осуществляет передачу кода с информационного входа 19 преобразователя или с выходов регистра 16 двоично-десятичного кода. Выходы регистров 5 и 16 являются первой 20 и второй 21 группами вьпсодов преобразователя, выход 22 которого является выходом конца преобразования. Управляющий вход 23 задает выбор закона преобразования, а вход начальной установки 24 осуществляет подготовку преобразователя к работе. Предлагаемый преобразователь работает следующим образом. В режиме преобразования двоичного /числа вдвоично-десятичное на управ-, ся двоичный код. Строб, приходящий по входу 24 преобразователя, передним фронтом производит установку регистров 5 и 16 и счетчика 13 в нулевое состояние. Задним фронтом стробового сигнала двоичный код, подаваемый по входу 18 преобразователя, заносится в регистр двоичного кода 5, триггер 3 переводится в единичное состояние, обеспечивая проход сигналов стробирования с генератора 12 через одноразрядный коммутатор 9 и элемент И 4 на регистр 5 двоичного кода, а также пересылку результата вычитания с выхода сумматора 7 через коммутатор 1 на вход регистра 5. Высокий потенциал на управляющем входе 23 разрешает проход сигнала с выхода разряда переноса сумматора 7 через коммутатор 8 на вход элемента И 4, который формирует сигнал занесения информации в регист 5 по результату вычитания. Второй коммутатор 10 высоким потенциалом на управляющем входе устанавливается на пропуск сигнала с элемента И 11 на вход генератора 12 импульсов, и этот же потенциал на управляющем входе 23 разрешает раб.оту дешифратора 17. Предлагаемый преобразователь позволяет использовать одни и те же коды двоичных эквивалентов в обоих режимах преобразования, поэтому двоичный код, проходя через коммутатор 1, инвертируется. После занесения двоичного кода в регистр 5 вклюfчается генератор 12 импульсов. Счетчик 13 формирует первый адрес выборки двоичного эквивалента из блока , 6 хранения эквивалентов. Двоичный эквивалент из блока 6 подается по первому информационному входу сумматора 7, по второму информационному входу которого подается инвертирован ный код преобразуемого двоичного чис ла с выхода регистра 5. В сзмматоре 7 происходит вычитание двоичного эквивалента из кода преобразуемого чис ла, и если вычитание имеет отрицательный результат, о чем говорит высокий потенциал на выходе переноса сумматора, то двоичный код преобразуемого числа остается в регистре 5 без изменения, так как прохождение , стробового сигнала на вход регистра 5через элемент И 4 запрещего нулевым потенциалом с выхода одноразрядного коммутатора 8. Соответствующее значение разряда регистра 16 также остается нулевым, так как высокий потенциал на выходе переноса сумматора 7 запрещает формирование импульса низкого потенциал дешифратора 17. Счетчик 13 формирует следующий адрес выборки двоичного эквивалента из блока 6. Если вычитание вновь имеет отрицательный резуль тат, то процесс повторяется. В блоке 6хранения эквивалентов хранятся двоичные коды чисел 1,2,4,8,10,20, 40,80,100,200,400,800,1000, 2000, 4000, 8000 и т.д. Количество хранимь двоичных чисел определяется разрядностью преобразуемых двоичных чисел. Вычитание двоичных эквивалентов из кода преобразуемого числа начинается с большего двоичного эквивалента, т.е. по первому адресу блока 6 хранится больший двоичный эквивалент. В случае успешного вычитания двоичного эквивалента из кода преобразуемого числа на выходе разряда переноса двоичного сумматора 7 устанавливается нулевой потенциал, который, поступая на дешифратор 17, разрешает формирование сигнала установки в единичное состояние соответствующего разряда регистра 16. Номер разряда заносимой единицы определяется счетчиком 13. Нулевой потенциал с выхода переноса сумматора 7, проходя через коммутатор 8 на вход элемента И 4, инвертируется и разрешает проход стробового сигнала занесения на вход регистра 5. Результат вычитания с выхода сумматора 7 через коммутатор 1 заносится в регистр 5. Процесс вычисления повторяется, но с двоичными эквивалентами сравнивается уже результат вычитания, полученный в предьщущем цикле вычисления. Преобразование продолжается до тех пор, пока элемент И 11 не зафиксирует нулевой результат в регистре 5. В этом случае элементом И 11 и коммутатором to формируется сигнал выключения генератора 12,останавливающий формирование импульсов на выходе элемента И 4. Этим же сигналом осуществляется перевод триггера 3 в нулевое состояние, обеспечивающее пропуск в устройство нового кода для преобразования и строба его занесения. Готовность устройства к приему нового кода подтверждается низким потенциалом, устанавливающимся на выходе 22 устройства. После выключения генератора сигналом с выхода элемента И 11 в регистре 16 содержится двоично-десятичный эквивалент преобразуемого двоичного числа. В режиме преобразования двоичнодесятичного числа в двоичное на управляющий вход 23 преобразователя подается нулевой потенциал, который запрещает работу дешифратора 17, разрешает проход сигнала через коммутатор 8 со старшего разряда регистра 16 на вход элемента И 4, переводит второй коммутатор 10 на пропуск сигнала окончания преобразования с эле мента И-НЕ 15. На информационньш вход 18, преобразователя подается двоично-десятичный код числа, а на вход 24 преобразователя - строб с канала. Передним фронтом строб прои водит начальную установку (установк в нулевое состояние) регистров 5 и 16 и счетчика 13. По заднему фронту стробового сигнала производится запись двоично-десятичного кода в регистр 16. Задним фронтом стробово го сигнала осуществляется перевод триггера 3 в единичное состояние, обеспечивающее переключение коммута тора 2 на инвертирование и пропуск кода с инверсного вьпсода регистра 16 на информационный вход этого регистра. Второй информационный вход преобразователя отключается. Коммут тор 9 высоким потенциалом переводит на пропуск сигнала с выхода генератора 12 на стробоный вход регистра 16 через элемент. ИЛИ 14, который открыт нулевым потенциалом, установленным на управляющем входе 23 преобразователя. После записи двоичнодесятичного числа в регистр 16 вклю чается генератор импульсов 12. Счет чик 13 формирует первьш адрес выборки двоичного эквивалента из блок 6 хранения эквивалентов. Двоичный эквивалент с выхода блока 6 подаетс на первый вход сумматора 7, где он суммируется с кодом, поданным с регистра 5 по второму входу сумматора 7 . В первом такте работы устройства с выхода регистра 5 по второму входу сумматора 7 подается нулевой код, так как регистр 5 обнулен. Код с сум матора 7 через коммутатор 1 подаетс на информационный вход регистра 5. Выход старшего разряда регистра 16 управляет прохождением тактового сигнала через элемент И 4 на стробовый вход регистра 5. В случае единичного значения старшего разряда регистра 16 элемент И 4 открывается пропуская стробовый импульс с выхода коммутатора 9, и код с выхода сумматора 7 заносится в регистр 5 двоичного кода. Если же старший разряд в регистре 16 имеет нулевое значение то содержимое регистра 5 остается неизменным. В следующем такте пр бразования код в регистре 16 сдвигается на один разряд в сторону старших разрядов. Счетчиком 13 формируется следующий адрес выборки двоичного эквивалента из блока 6. Содержимое регистра 16 постоянно анализируется на нуль. В случае наличия нуля во всех разрядах регистра 16 единичный пот нциал с выхода элемента И-НЕ 15, проходя через коммутатор 10, инвертируется и -выключает генератор 12 иКшульСов, после чего в регистре 5 будет содержаться двоичный эквивалент двоичнодесятичного числа, записанного в регистр 16. Ппедлагаемое изобретение позволяет повысить среднТою скорость преобразования двоичного числа в двоично-десятичное по сравнению с устройствомпрототипом, в котором двоично-десятичное число получается после опроса всех разрядов двоичного кода (быстродействие преобразователя-прототипа определяется разрядностью двоичного числа, предлагаемое устройство позволяет завершать преобразование, не формируя нулевые значения после последней значащей единицы двоичнодесятичного числа, т.е. сокращая время преобразования на число тактов, необходимое для формирования оставшихся нулевых разрядов)-, упростить устройство преобразователя за счет замены двоично-десятичного сумматора двоичным, меньшим по объему, исключения группы элементов И и схемы сравнения (замена двух групп элементов И с открытым коллектором или тремя состояниями на выходе двумя коммутаторами не приводит к увеличению аппаратурных затрат, введение элементов И, И-НЕ и коммутаторов компенсируется удалением группы элементов И); упростить согласование преобразователя со специализированными устройствами и процессорами вычислительных машин, выпускаемых промьшшенностью (если в преобразователе-прототипе в режиме преобразования двоично-десятичного кода в двоичный на входах двоично-десятичного числа код необходимо держать постоянно, то предлагаемый преобразователь после занесения кодов в регистры работает автономно, подтверждая свою готовность к очередному циклу работы вьвдачей сигнала низкого потенциала в канал).

Обнуление регистров в устройствепрототипе производится путем подачи нулевых кодов на входы устройства.

Я

19

18

L

/

/

f /

f6

на что затрачивается дополнительное время. Этот недостаток исключается в предлагаемом преобразователе.

/4(

f:

L

l

f

12

-

7V

17

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Преобразователь правильной двоичнодесятичной дроби в двоичную дробь и целых двоичных чисел в двоично-десятичные числа | 1974 |

|

SU526886A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1977 |

|

SU732853A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-04-15—Публикация

1982-11-18—Подача