Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, решающих усилителях с малыми значениями э.д.с. смещения нуля и его дрейфа в условиях воздействия температуры или радиации).

В современной радиоэлектронной аппаратуре находят применение операционные усилители (ОУ) с существенными различными параметрами. Особое место занимают ОУ с простейшей архитектурой, содержащие небольшое число элементов. На их основе выполняются, например, различные классы селективных цепей, где число маломощных усилителей может измеряться десятками единиц. Предлагаемое изобретение относится к данному типу устройств.

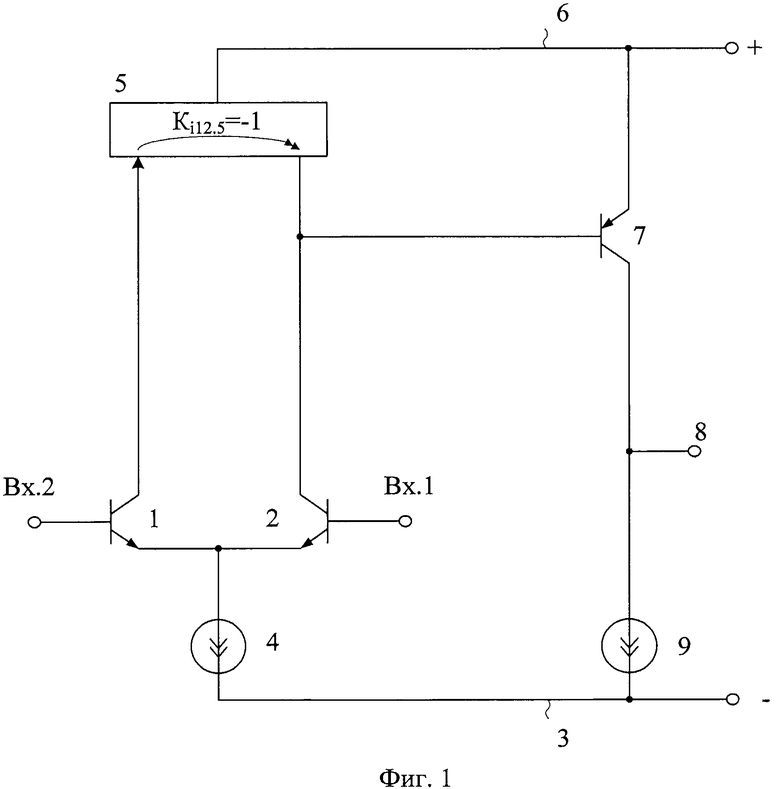

Наиболее близкой по технической сущности к заявляемому ОУ является классическая схема фиг.1 (патент США №6.549.072, fig.1, он же патент СА 2472125), которая стала основой построения большого числа аналоговых устройств различного назначения, в том числе микросхем (574УД3, 153УД2, 1407УД3, СА3078 и др. [1-13]).

Существенный недостаток известного ОУ фиг.1 состоит в том, что он имеет невысокий коэффициент усиления по напряжению (Ку).

Основная задача предлагаемого изобретения состоит в повышении Ку. Дополнительная - уменьшение напряжения смещения нуля (Uсм).

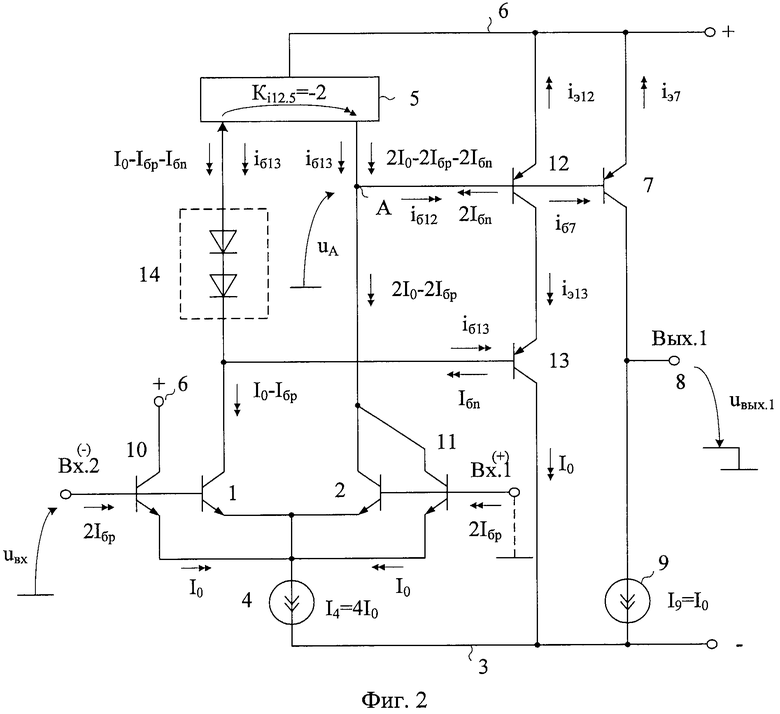

Поставленная задача решается тем, что в дифференциальном усилителе, фиг.1, содержащем первый 1 и второй 2 входные транзисторы, объединенные эмиттеры которых связаны с первым 3 источником питания через первый 4 токостабилизирующий двухполюсник, токовое зеркало 5, общий эмиттерный выход которого соединен со вторым 6 источником питания, первый 7 выходной транзистор, эмиттер которого связан со вторым 6 источником питания, коллектор соединен с выходом устройства 8 и через второй токостабилизирующий двухполюсник 9 подключен к первому 3 источнику питания, а база подключена к выходу токового зеркала 5 и коллектору второго 2 входного транзистора, причем коллектор первого 1 входного транзистора связан со входом токового зеркала 5, предусмотрены новые элементы и связи - в схему введены третий 10 и четвертый 11 входные транзисторы, эмиттеры которых подключены к эмиттерам первого 1 и второго 2 входных транзисторов, коллектор четвертого 11 входного транзистора соединен с коллектором второго 2 входного транзистора, базы второго 2 и четвертого 11 входных транзисторов соединены, базы третьего 10 и первого 1 входных транзисторов связаны друг с другом, коллектор третьего 10 входного транзистора подключен ко второму 6 источнику питания, база первого 12 дополнительного транзистора соединена с базой первого 7 выходного транзистора, эмиттер первого 12 дополнительного транзистора подключен к шине второго 6 источника питания, коллектор первого 12 дополнительного транзистора связан с эмиттером второго 13 дополнительного транзистора, база второго 13 дополнительного транзистора соединена с коллектором первого 1 входного транзистора, а коллектор второго 13 дополнительного транзистора подключен к первому 3 источнику питания, причем коэффициент передачи по току токового зеркала 5 близок к двум единицам.

Схема усилителя-прототипа показана на фиг.1. На фиг.2 представлена схема заявляемого устройства в соответствии с п.1 и п.2 формулы изобретения.

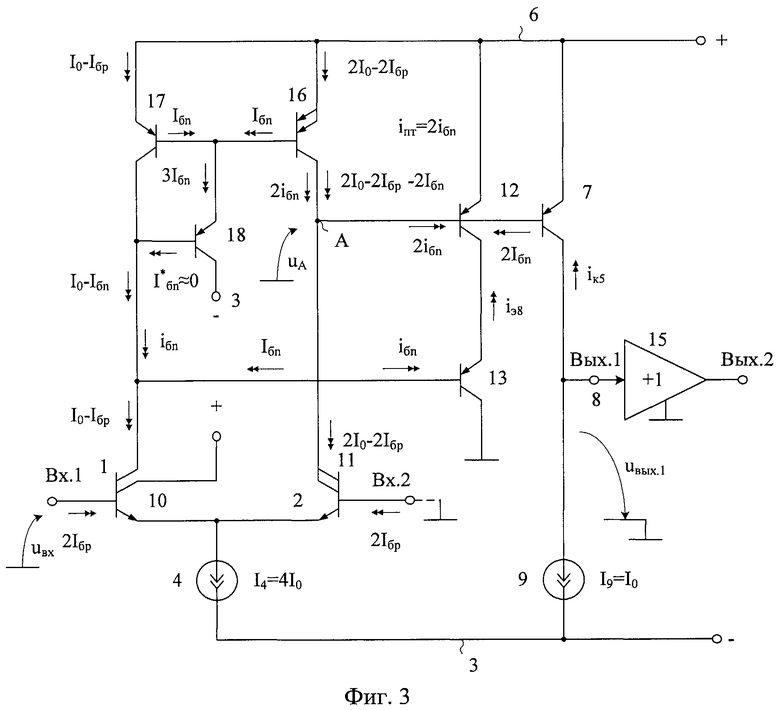

На фиг.3 показана схема заявляемого устройства в соответствии с п.3 формулы изобретения.

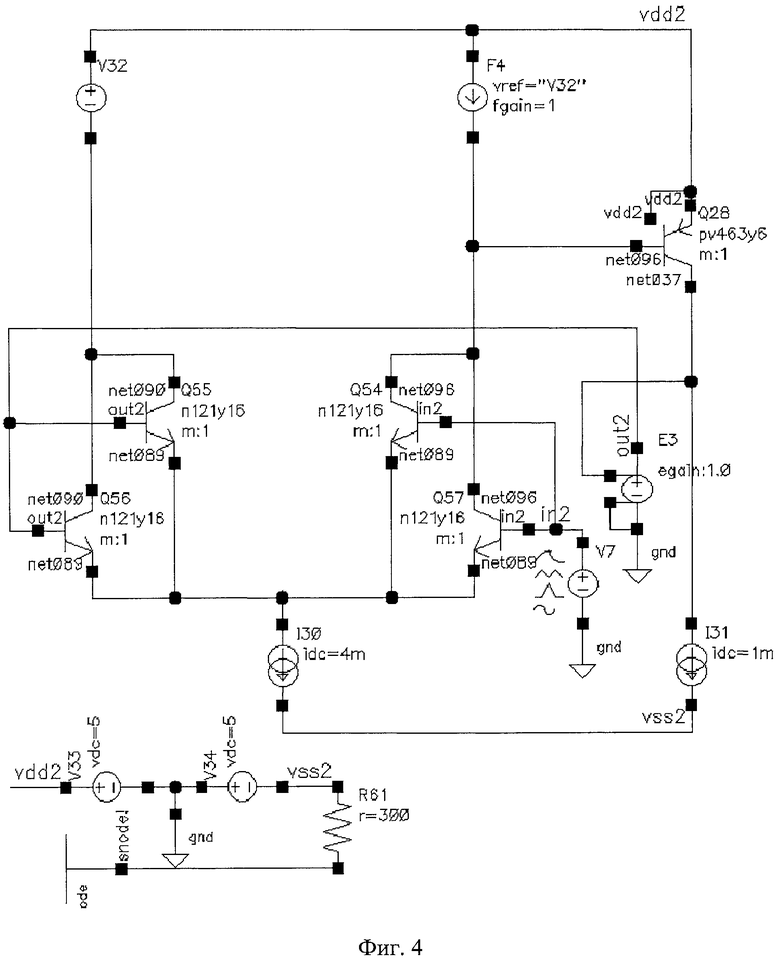

На фиг.4 показана схема ДУ-прототипа в среде компьютерного моделирования Cadence на моделях интегральных транзисторов HJW ФГУП НПП «Пульсар».

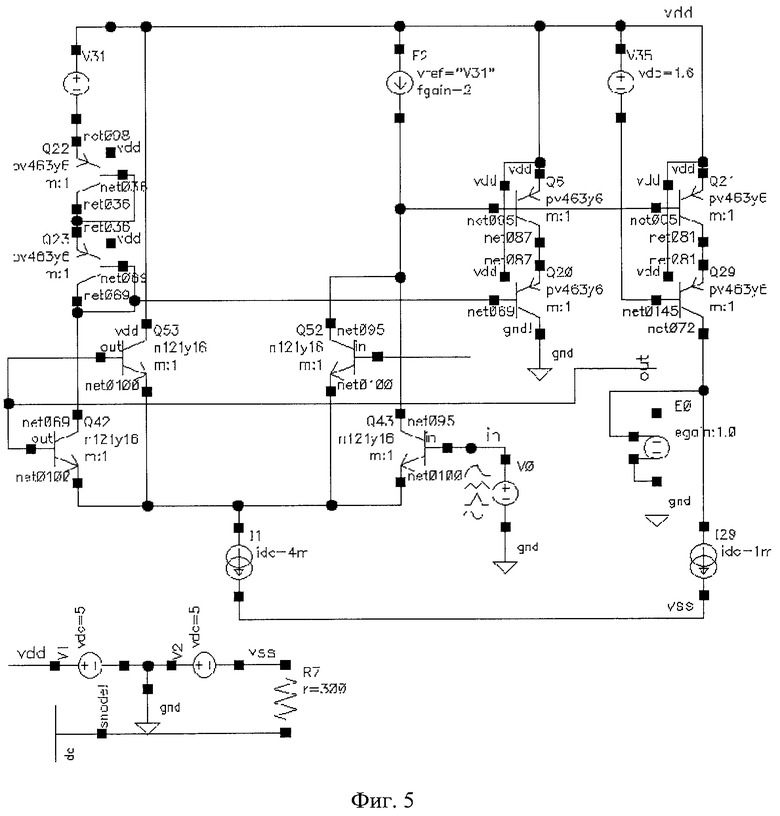

На фиг.5 показана схема заявляемого устройства в среде компьютерного моделирования Cadence на моделях интегральных транзисторов HJW ФГУП НПП «Пульсар».

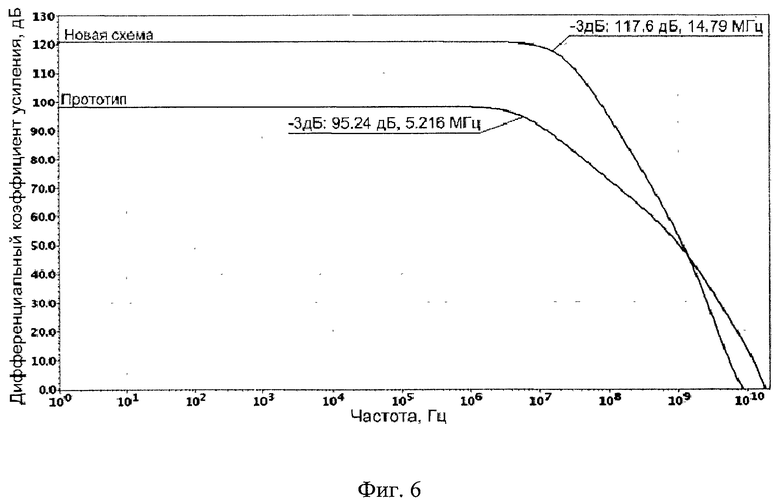

На фиг.6 приведены амплитудно-частотные характеристики сравниваемых схем фиг.4 и фиг.5.

Дифференциальный усилитель, фиг.2, содержит первый 1 и второй 2 входные транзисторы, объединенные эмиттеры которых связаны с первым 3 источником питания через первый 4 токостабилизирующий двухполюсник, токовое зеркало 5, общий эмиттерный выход которого соединен со вторым 6 источником питания, первый 7 выходной транзистор, эмиттер которого связан со вторым 6 источником питания, коллектор соединен с выходом устройства 8 и через второй токостабилизирующий двухполюсник 9 подключен к первому 3 источнику питания, а база подключена к выходу токового зеркала 5 и коллектору второго 2 входного транзистора, причем коллектор первого 1 входного транзистора связан со входом токового зеркала 5. В схему введены третий 10 и четвертый 11 входные транзисторы, эмиттеры которых подключены к эмиттерам первого 1 и второго 2 входных транзисторов, коллектор четвертого 11 входного транзистора соединен с коллектором второго 2 входного транзистора, базы второго 2 и четвертого 11 входных транзисторов соединены, базы третьего 10 и первого 1 входных транзисторов связаны друг с другом, коллектор третьего 10 входного транзистора подключен ко второму 6 источнику питания, база первого 12 дополнительного транзистора соединена с базой первого 7 выходного транзистора, эмиттер первого 12 дополнительного транзистора подключен к шине второго 6 источника питания, коллектор первого 12 дополнительного транзистора связан с эмиттером второго 13 дополнительного транзистора, база второго 13 дополнительного транзистора соединена с коллектором первого 1 входного транзистора, а коллектор второго 13 дополнительного транзистора подключен к первому 3 источнику питания, причем коэффициент передачи по току токового зеркала 5 близок к двум единицам.

На фиг.2 в соответствии с п.2 формулы изобретения коллектор первого 1 входного транзистора связан со входом токового зеркала через дополнительную цепь согласования потенциалов 14. Необходимость введения цепи согласования потенциалов 14 определяется схемой токового зеркала 5. Например, при реализации токового зеркала 5 в соответствии с п.3 формулы изобретения цепь согласования потенциалов 14 может не вводиться.

На фиг.3 в соответствии с п.3 формулы изобретения токовое зеркало 5 содержит первый 16 и второй 17 вспомогательные транзисторы, эмиттеры которых соединены со вторым 6 источником питания, базы объединены и подключены к эмиттеру третьего 18 вспомогательного транзистора, коллектор второго 17 вспомогательного транзистора соединен с базой третьего 18 вспомогательного транзистора и является входом токового зеркала 5, коллектор первого 16 вспомогательного транзистора является выходом токового зеркала 5, причем площадь эмиттерного перехода первого 16 вспомогательного транзистора приблизительно в два раза превышает площадь эмиттерного перехода второго 17 вспомогательного транзистора. Практически это означает параллельное включение двух транзисторов в качестве составного транзистора 16.

Для определения Uсм ДУ рассмотрим основные токовые соотношения в схеме фиг.2.

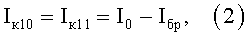

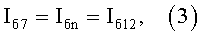

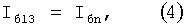

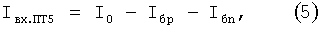

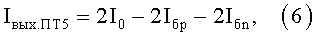

Если принять, что ток общей эмиттерной цепи входного дифференциального каскада 1 на транзисторах 1, 2, 10, 11 равен 4I0, а ток двухполюсника 9 I9=I0, то токи в схеме фиг.2

где Iбр, Iбn - ток базы n-p-n (p-n-p) транзисторов ДУ при Iэ=I0.

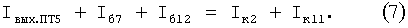

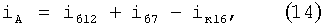

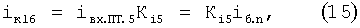

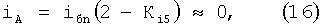

Учитывая, что коэффициент передачи по току токового зеркала 5 равен двум единицам (Кi12.5=2), можно найти ток в узле «А»:

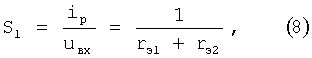

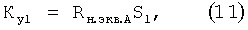

Подставляя (1)-(6) в (7), находим, что сумма токов в узле «А» равна нулю. Как следствие, это уменьшает напряжение смещения нуля Uсм. Действительно, разностный ток Iр в узле «А» ДУ фиг.1 создает Uсм, зависящее от крутизны S1 преобразования входного напряжения uвх ДУ фиг.1 в выходной ток узла «А»

где rэ1=rэ2 - сопротивления эмиттерных переходов входных транзисторов 1 и 2.

Поэтому для схем фиг.2

где S2 - крутизна входного каскада фиг.2.

Таким образом, в ДУ-прототипе Ip≠0, и, как следствие, систематическая составляющая напряжения смещения нуля Uсм получается на порядок больше.

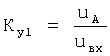

Рассмотрим работу ДУ фиг.3 на переменном токе - определим его коэффициент усиления по напряжению:

где  - коэффициент усиления первого каскада;

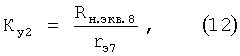

- коэффициент усиления первого каскада;

- коэффициент усиления второго каскада.

- коэффициент усиления второго каскада.

Причем

где Rн.экв.А - эквивалентное выходное сопротивление узла «А»;

Rн.экв.8 - эквивалентное сопротивление в цепи выхода 8 (коллекторная нагрузка транзистора 7);

S1 - крутизна преобразования входного напряжения ДУ в выходной ток узла «А»;

rэ7 - сопротивление эмиттерного перехода транзистора 7.

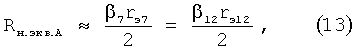

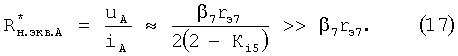

Основная составляющая Rн.экв.А в ДУ-прототипе - параллельно включенные входные сопротивления транзисторов 12 и 7 в схеме с общим эмиттером:

где β7 (β12) - коэффициент усиления по току базы транзистора 7 (12).

В заявляемой схеме токовое зеркало 5 на транзисторах 16, 17 и 18 обеспечивает усиление по току в два раза и формирует усиленную в два раза передачу в узел «А» приращения тока базы транзистора 13. Как следствие, суммарное приращение токов в узле «А», вызванное изменением напряжения uA, будет равно нулю:

где Кi5=2 - коэффициент усиления по току токового зеркала 5 (транзисторы 16-18).

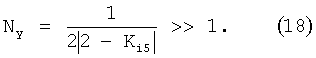

Это эквивалентно повышению эффективного сопротивления в узле «А»:

Повышение  по сравнению с Rн.экв.А ДУ-прототипа повышает в Ny-раз коэффициент усиления по напряжению ДУ фиг.2.

по сравнению с Rн.экв.А ДУ-прототипа повышает в Ny-раз коэффициент усиления по напряжению ДУ фиг.2.

Данные выводы подтверждаются результатами компьютерного моделирования сравниваемых схем (фиг.6) - предлагаемый ДУ имеет на порядок более высокий Ку.

Таким образом, заявляемое устройство имеет существенные преимущества в сравнении с прототипом.

Источники информации

1. Патент США №4.410.859 fig.1.

2. Патент США №4.721.920.

3. Патент США №4.783.637.

4. А.св. СССР №678639.

5. Патент США №4.560.948.

6. А.св. №1193773.

7. Патент США №4.463.319.

8. Патент W003/063344A1.

9. Патент США №5.343.164.

10. Патент США №4.417.216.

11. Патент США №5.365.191 fig.7.

12. Патент США №4.163.908.

13. Патент Японии №54-37561 fig.1.

| название | год | авторы | номер документа |

|---|---|---|---|

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412529C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2411636C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2411638C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2010 |

|

RU2414807C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2411639C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2010 |

|

RU2421884C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412539C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2354041C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412530C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2411635C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, решающих усилителях с малыми значениями э.д.с. смещения нуля и его дрейфа в условиях воздействия температуры или радиации). Технический результат: повышение Ку, а также уменьшение напряжения смещения нуля (Uсм). Дифференциальный усилитель содержит первый (1) и второй (2) входные транзисторы, объединенные эмиттеры которых связаны с первым (3) источником питания через первый (4) токостабилизирующий двухполюсник, токовое зеркало (5), общий эмиттерный выход которого соединен со вторым (6) источником питания, первый (7) выходной транзистор, эмиттер которого связан со вторым (6) источником питания, коллектор соединен с выходом устройства (8) и через второй токостабилизирующий двухполюсник (9) подключен к первому (3) источнику питания, а база подключена к выходу токового зеркала (5) и коллектору второго (2) входного транзистора, причем коллектор первого (1) входного транзистора связан со входом токового зеркала (5). В схему введены третий (10) и четвертый (11) входные транзисторы, эмиттеры которых подключены к эмиттерам первого (1) и второго (2) входных транзисторов, коллектор четвертого (11) входного транзистора соединен с коллектором второго (2) входного транзистора, базы второго (2) и четвертого (11) входных транзисторов соединены, базы третьего (10) и первого (1) входных транзисторов связаны друг с другом, коллектор третьего (10) входного транзистора подключен ко второму (6) источнику питания, база первого (12) дополнительного транзистора соединена с базой первого (7) выходного транзистора, эмиттер первого (12) дополнительного транзистора подключен к шине второго (6) источника питания, коллектор первого (12) дополнительного транзистора связан с эмиттером второго (13) дополнительного транзистора, база второго (13) дополнительного транзистора соединена с коллектором первого (1) входного транзистора, а коллектор второго (13) дополнительного транзистора подключен к первому (3) источнику питания, причем коэффициент передачи по току токового зеркала (5) близок к двум единицам. 2 з.п. ф-лы, 6 ил.

1. Дифференциальный усилитель, содержащий первый (1) и второй (2) входные транзисторы, объединенные эмиттеры которых связаны с первым (3) источником питания через первый (4) токостабилизирующий двухполюсник, токовое зеркало (5), общий эмиттерный выход которого соединен со вторым (6) источником питания, первый (7) выходной транзистор, эмиттер которого связан со вторым (6) источником питания, коллектор соединен с выходом устройства (8) и через второй токостабилизирующий двухполюсник (9) подключен к первому (3) источнику питания, а база подключена к выходу токового зеркала (5) и коллектору второго (2) входного транзистора, причем коллектор первого (1) входного транзистора связан со входом токового зеркала (5), отличающийся тем, что в схему введены третий (10) и четвертый (11) входные транзисторы, эмиттеры которых подключены к эмиттерам первого (1) и второго (2) входных транзисторов, коллектор четвертого (11) входного транзистора соединен с коллектором второго (2) входного транзистора, базы второго (2) и четвертого (11) входных транзисторов соединены, базы третьего (10) и первого (1) входных транзисторов связаны друг с другом, коллектор третьего (10) входного транзистора подключен ко второму (6) источнику питания, база первого (12) дополнительного транзистора соединена с базой первого (7) выходного транзистора, эмиттер первого (12) дополнительного транзистора подключен к шине второго (6) источника питания, коллектор первого (12) дополнительного транзистора связан с эмиттером второго (13) дополнительного транзистора, база второго (13) дополнительного транзистора соединена с коллектором первого (1) входного транзистора, а коллектор второго (13) дополнительного транзистора подключен к первому (3) источнику питания, причем коэффициент передачи по току токового зеркала (5) близок к двум единицам.

2. Дифференциальный усилитель по п.1, отличающийся тем, что коллектор первого (1) входного транзистора связан со входом токового зеркала через дополнительную цепь согласования потенциалов (14).

3. Дифференциальный усилитель по п.1, отличающийся тем, что токовое зеркало (5) содержит первый (16) и второй (17) вспомогательные транзисторы, эмиттеры которых соединены со вторым (6) источником питания, базы объединены и подключены к эмиттеру третьего (18) вспомогательного транзистора, коллектор второго (17) вспомогательного транзистора соединен с базой третьего (18) вспомогательного транзистора и является входом токового зеркала (5), коллектор первого (16) вспомогательного транзистора является выходом токового зеркала (5), причем площадь эмиттерного перехода первого (16) вспомогательного транзистора приблизительно в два раза превышает площадь эмиттерного перехода второго (17) вспомогательного транзистора.

| US 6549072 В1, 15.04.2003 | |||

| US 4418290 А, 29.11.1983 | |||

| US 4095164 А, 13.06.1978 | |||

| ПОЛОННИКОВ Д.Е | |||

| Операционные усилители: принципы построения, теория, схемотехника | |||

| - М.: Энергоатомиздат, 1983, с.94, рис.3.9. |

Авторы

Даты

2012-03-27—Публикация

2010-05-07—Подача