ПЕРЕКРЕСТНАЯ ССЫЛКА НА РОДСТВЕННЫЕ ЗАЯВКИ

Данная заявка является частичным продолжением патентной заявки США №11/702 979 и притязает на приоритет патентной заявки США №11/702 979, поданной 5 февраля 2007, и предварительной патентной заявки США №60/764 955, поданной 3 февраля 2006. Все содержимое патентной заявки США №11/702 979 и предварительной патентной заявки США №60/764 955 включено в настоящее описание посредством ссылки.

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ И СУЩНОСТЬ ИЗОБРЕТЕНИЯ

Скорость компьютера можно увеличивать, используя два общих подхода: увеличивать скорость выполнения команды или выполнять больше команд параллельно. Поскольку скорость выполнения команды приближается к пределам подвижности электронов в кремнии, параллелизм становится лучшей альтернативой для увеличения скорости компьютера.

Предыдущие попытки параллелизма включали в себя:

1. Совмещение выборки следующей команды с выполнением текущей команды.

2. Конвейерная обработка команд. Конвейер команд разбивает каждую команду на максимально большое количество частей и затем пытается отобразить последовательные команды на параллельные исполнительные устройства. Теоретическое максимальное улучшение редко достигается из-за неэффективности многошаговых команд, неспособности многих программ обеспечивать достаточно много последовательных команд для сохранения параллельных исполнительных устройств заполненными, и большие затраты времени при возникновении логических структур перехода, цикла или выбора, при которых требуется повторное заполнение исполнительных устройств.

3. Одна команда - множество данных или SIMD. Эту методику можно найти в наборе команд Intel SSE, который воплощен в Intel Pentium 3 и в других процессорах. В этой методике одну команду выполняют с множеством наборов данных. Эта методика удобна только для специальных приложений, таких как воспроизведение компьютерной графики.

4. Гиперкуб. Эта методика использует большие двумерные массивы и иногда трехмерные массивы процессоров и локальной памяти. Связи и соединения, необходимые для поддержания этих массивов процессоров, по существу ограничивают их очень специализированными приложениями.

Конвейер является блоком выполнения команд, состоящим из множества последовательных ступеней, на которых последовательно выполняются этапы выполнения команды, такие как выборка, декодирование, выполнение, сохранение и т.д. Несколько конвейеров можно размещать параллельно так, чтобы команды программы подавались к каждому конвейеру одна за другой, пока все конвейеры не будут выполнять команды. Затем заполнение командами повторяется с исходного конвейера. Когда N конвейеров заполнены командами и выполняют программу, результирующая производительность теоретически является такой же, как при увеличении в N раз скорости выполнения для одного исполнительного устройства.

Успешная конвейерная обработка зависит от следующего:

1. Необходимо, чтобы выполнение команды можно было определить как несколько последовательных состояний.

2. Все команды должны иметь одинаковое количество состояний.

3. Количество состояний, приходящихся на каждую команду, определяет максимальное количество параллельных исполнительных устройств.

Так как конвейерная обработка может обеспечивать увеличение производительности, основываясь на количестве параллельных конвейеров, и так как количество параллельных конвейеров определяется количеством состояний в команде, конвейеры способствуют использованию сложных команд со многими состояниями.

Компьютеры с большим количеством конвейеров очень редко обеспечивают производительность, которая находится около теоретического увеличения производительности, ожидаемого от параллельных конвейерных исполнительных устройств. Некоторые из причин этого недостатка конвейерной обработки включают в себя:

1. Программы состоят не только из последовательных команд. Различные исследования показывают, что изменения потока выполнения происходят каждые 8-10 команд. Любой переход, который изменяет процесс выполнения программы, нарушает работу конвейера. Попытки минимизировать нарушения работы конвейера имеют тенденцию быть сложными и неполными при их уменьшении.

2. Предписание, чтобы все команды имели одинаковое количество состояний, часто приводит к тому, что использование конвейеров соответствует требованиям команд с самыми низкими требованиями (т.е. самой медленной и самой сложной команды). Из-за использования конвейера все команды приводят к одинаковому количеству состояний, независимо от того нужны они или нет. Например, логические операции (такие как AND (И) или OR (ИЛИ)) выполняются на порядок быстрее, чем ADD (СЛОЖЕНИЕ), но часто обеим назначается одинаковое количество времени для выполнения.

3. Конвейеры поощряют использование сложных команд со многими состояниями. Команды, которым требуется два состояния, обычно растягиваются для заполнения 20 состояний, потому что это - глубина конвейера. (Intel Pentium 4 использует конвейер с 20 состояниями).

4. Время, необходимое для каждого состояния конвейера, должно учитывать задержки распространения через логическую схему и соответствующие транзисторы, в дополнение к допустимому отклонению конструкции или допускам для конкретного состояния.

5. Арбитраж доступа к регистру конвейера и к другим ресурсам часто уменьшает производительность из-за соответствующих транзисторам задержек распространения в логической схеме арбитража.

6. Существует верхний предел количества состояний, на которые может быть разбита команда, выше которого дополнительные состояния фактически замедляют выполнение, а не ускоряют его. Некоторые исследования предполагают, что конвейерная архитектура процессора Alpha корпорации Digital Equipment Corporation последнего поколения превысила эту точку и фактически работает медленнее, чем предыдущая версия процессора с более коротким конвейером.

Разделение конвейеров на части

Одной из перспектив переработки конструкции ЦП является рассмотрение возможности разделения конвейерных исполнительных устройств на множество (N) упрощенных процессоров. (Регистры и некоторые другие логические схемы, возможно, придется дублировать в такой конструкции). Каждый из N упрощенных процессоров будут иметь следующие преимущества перед обсуждаемой выше архитектурой с конвейерами:

1. Нет остановов конвейерной обработки. Нет необходимости в предсказании переходов.

2. Команды могут использовать столько времени, сколько им нужно, а не все назначенное одинаковое время выполнения, равное времени выполнения самой медленной команды.

3. Команды можно упрощать с помощью уменьшения необходимых состояний выполнения, таким образом уменьшая недостатки конвейера.

4. Каждое состояние, удаленное из конвейера, может устранять задержки распространения и удалять допустимые ограничения конструкции, необходимые для состояния.

5. Можно устранять арбитраж регистров.

Кроме того, у системы с N упрощенными процессорами могут быть следующие преимущества перед ЦП с конвейерами:

1. Предел максимального конвейерного параллелизма будет устранен.

2. В отличие от процессора с конвейерной обработкой информации, множество автономных процессоров можно выборочно выключать для уменьшения потребляемой мощности, если они не используются.

Другие проблемы при существующем подходе к параллелизму

Многие реализации параллелизма соответствуют пределам закона Амдала (Amdahl). Ускорение через параллелизм ограничено издержками из-за не преобразуемых в последовательную форму частей задачи. В основном когда величина параллелизма увеличивается, связи, необходимые для его поддержания, уничтожают ускорение из-за параллелизма.

Ожидание зеленого сигнала светофора на максимальных оборотах двигателя

Другим недостатком существующих процессоров является невозможность масштабирования вычислительной мощности для удовлетворения требований непосредственных вычислений. Большинство компьютеров проводит большую часть своего времени, ожидая чего-нибудь, что должно произойти. Они ждут ввода/вывода, следующей команды, доступа к памяти или иногда взаимодействия с пользователем. Данное ожидание является неэффективной тратой вычислительной мощности. Кроме того, потраченное на ожидание компьютерное время часто приводит к увеличению потребляемой мощности и тепловыделения.

Исключениями к данному правилу ожидания являются такие варианты применения, как контроллеры управления двигателем, процессоры обработки сигнала и маршрутизаторы межсетевого экрана. Эти применения являются превосходными кандидатами на ускорение с помощью параллелизма из-за предопределенной природы наборов задач и наборов решений. Задача, которая требует результата N независимых умножений, может быть решена более быстро с использованием N блоков умножения.

Воспринимаемой (субъективной) производительностью универсального компьютера на самом деле является его пиковая производительность. Самое близкое, что универсальный компьютер получает к тому, чтобы стать занятым, является выполнение видеоигры с быстрым обновлением изображения, компиляция большого исходного файла или поиск в базе данных. В оптимальном случае при воспроизведении видео структуризируют для обработки на специальной аппаратуре шейдерной обработки, преобразования и воспроизведения. Одним из способов организации программирования для таких специальных аппаратных средств является использование «потоков».

Потоки являются независимыми программами, которые являются изолированными и редко обмениваются данными с другими потоками. Обычным использованием потоков является сбор данных о медленной деятельности в реальном масштабе времени и обеспечение собранных результатов. Поток можно также использовать для обработки изменений на дисплее. Поток может переходить через тысячи или миллионы состояний прежде, чем потребуется дополнительное взаимодействие с другим потоком. Независимые потоки представляют возможность увеличения производительности через параллелизм.

Многие программные компиляторы поддерживают генерацию и управление потоками в целях структуризации процесса разработки программного обеспечения. Ту же самую структуризацию поддерживает параллельная обработка с помощью множества ЦП через методику параллелизма на уровне потоков, осуществляемую в оптимизированном для потоков микропроцессоре (TOMI) согласно предпочтительному варианту осуществления.

Параллелизм на уровне потоков

Организация поточной обработки является хорошо понимаемой методикой для структуризации программы на одном ЦП. Параллелизм на уровне потоков может обеспечивать ускорение программы через использование процессора TOMI.

Одним из существенных преимуществ процессора TOMI по сравнению с другими параллельными подходами является то, что процессор TOMI требует минимальных изменений в существующих методиках создания программного обеспечения. Не требуется разрабатывать новые алгоритмы. Многие существующие программы, возможно, придется перекомпилировать, но не придется существенно переписывать.

Эффективную компьютерную архитектуру TOMI следует создавать из большого количества упрощенных процессоров. Различная архитектура может использоваться для различных типов вычислительных задач.

Основные компьютерные операции

Для универсального компьютера самыми обычными операциями по порядку снижения частоты являются: загрузка и сохранение; упорядочение; и математические и логические операции.

Загрузка и сохранение

Параметрами команд LOAD (загрузка) и STORE (сохранение) являются источник и адресат. Мощностью команд LOAD и STORE является диапазон адресов источника и адресата (например, 4 Гб является более мощным диапазоном, чем 256 байтов). Локальность текущего источника и адресата важна для многих наборов данных. Плюс 1, минус 1 являются самыми удобными. Увеличение величины смещения от текущего источника и адресата по нарастающей становится менее удобным.

На команды LOAD и STORE может также влиять иерархия памяти. LOAD из памяти может быть самой медленной операцией, которую может выполнять ЦП.

Упорядочение (установление последовательности)

Переходы и циклы являются основными командами упорядочения. Изменения последовательности команд, основанные на проверке, являются способом, которым компьютеры принимают решения.

Математические и логические операции

Математические и логические операции являются наименее используемыми из этих трех видов операций. Логические операции являются самыми быстрыми операциями, которые ЦП может выполнять, и они могут требовать задержки всего одного логического элемента. Математические операции более сложны, так как старшие биты зависят от результатов операций с младшими битами. 32-разрядная команда ADD может потребовать задержки по меньшей мере 32 логических схем, даже с предсказанием переноса. Команда MULTIPLY (умножить) с использованием методики сдвига и сложения может потребовать время, равное выполнению 32 команд ADD.

Соглашения о размере команды

Совершенный набор команд состоял бы из кодов операций, которые являются достаточно большими для выбора бесконечного количества возможных источников, адресатов, операций и следующих команд. К сожалению, коды операции совершенного набора команд имели бы бесконечную ширину, и пропускная способность команд поэтому была бы равна нулю.

Разработка компьютера для большой пропускной способности команд вовлекает создание набора команд с кодами операции, которые могут эффективно определять самые обычные источники, адресаты, операции и следующие команды с помощью наименьшего количества битов кода операции.

Большие коды операции приводят к высоким требованиям к пропускной способности шины команд, и результирующая архитектура будет быстро ограничена узким местом фон Неймана (von Neumann), где производительность компьютера ограничена скоростью, с которой он выбирает команды из памяти.

Если шина памяти имеет ширину 64 бита, то можно выбирать одну 64-битовую команду, две 32-битовые команды, четыре 16-битовые команды или восемь 8-битовых команд в каждом цикле памяти. 32-битовая команда должна быть в два раза более полезной, чем 16-битовая команда, так как она сокращает пропускную способность команд вдвое.

Главная цель разработки набора команд состоит в уменьшении избыточности команд. В общем случае оптимизированный эффективный набор команд использует локальность и команд, и данных. Самая простая оптимизация команд была давно сделана. Для большинства компьютерных программ наиболее вероятной следующей командой является последовательно следующая команда в памяти. Поэтому вместо того чтобы каждая команда имела поле следующей команды, большинство команд предполагает, что следующей командой является текущая команда +1. Можно создавать архитектуру с нулевым количеством битов для источника и нулевым количеством битов для адресата.

Архитектура со стеком

Компьютерную архитектуру со стеком также называют архитектурой с нулевым операндом. Архитектура со стеком выполняет все операции, основываясь на содержимом стека магазинного типа. Операции с двумя операндами требуют, чтобы оба операнда присутствовали в стеке. Когда данная операция выполняется, оба операнда извлекаются из стека, операцию выполняют и результат помещают назад в стек. У компьютеров с архитектурой со стеком могут быть очень короткие коды операции, так как подразумевают, что источник и адресат находятся в стеке.

Большинство программ требует содержимого глобальных регистров, которые не всегда могут быть доступны в стеке, когда это необходимо. Попытки минимизировать возникновение таких ситуаций включают в себя индексирование стека, что предоставляет возможность обращаться к другим операндам, чем те которые находятся на вершине стека. Индексация стека требует или дополнительных битов кода операции, что приводит к большим командам, или дополнительных операций для помещения значения индекса стека в сам стек. Иногда определяют один или большее количество дополнительных стеков. Лучшим, но не оптимальным решением является комбинация архитектур со стеком/с регистром.

Работа архитектуры со стеком также часто избыточна таким образом, что в ней игнорируется очевидная оптимизация. Например, каждая операция POP (извлечение из стека) и PUSH (запись в стек) может привести к бесполезному использованию времени операции обращения к памяти, когда стек обрабатывается в памяти. Кроме того, операция со стеком может использовать операнд, который может быть сразу необходим для следующей операции, таким образом требуя дублирования операнда с возможным выполнением еще одной операции с памятью. Рассматривают, например, операцию умножения всех элементов одномерного массива на 15.

В архитектуре со стеком ее осуществляют с помощью:

1. Записывают (PUSH) начальный адрес массива.

2. Копируют (DUPLICATE) адрес (таким образом создают адрес для сохранения результата в массиве).

3. Копируют (DUPLICATE) адрес (таким образом создают адрес для считывания из массива).

4. Выполняют косвенную запись (PUSH INDIRECT) (записывают содержимое массива в ячейку, на которую указывает вершина стека).

5. Записывают (PUSH) 15.

6. Умножают (MULTIPLY) (на 15 содержимое массива, который считывают в строке 3).

7. Переставляют ячейки (SWAP) (получают адрес массива на вершине стека для следующей команды).

8. Выполняют косвенное извлечение (POP INDIRECT) (извлекают (POP) результат умножения и сохраняют его назад в массив).

9. Выполняют увеличение адреса (INCREMENT) (указывают на следующий элемент массива).

10. Переходят на этап 2, пока массив не будет завершен.

Счетчик цикла в строке 9 требует дополнительного параметра. В некоторых архитектурах этот параметр сохраняют в другом стеке.

В гипотетической архитектуре с регистром/накапливающим сумматором (аккумулятором) данный пример осуществляют с помощью:

1. STORE POINTER начальный адрес массива.

2. READ POINTER (считывают содержимое по адресу, указанному в накапливающем сумматоре).

3. Умножают (MULTIPLY) на 15.

4. STORE POINTER (сохраняют результат по указанному адресу).

5. INCREMENT POINTER.

6. Переходят на строку 2, пока массив не будет завершен.

Архитектура со стеком содержит девять этапов по сравнению с пятью этапами для архитектуры с регистром в приведенном выше примере. Кроме того, операции со стеком имеют по меньшей мере 3 возможных дополнительных обращения к памяти из-за операций со стеком. Управление циклами в гипотетической архитектуре регистра/накапливающего сумматора можно легко обрабатывать в регистре.

Стек удобен для оценки выражений и используется также в большинстве компиляторов. Стек также удобен для вложенных операций, таких как вызов функции. Большинство компиляторов языка C воплощают вызов функции с помощью стека. Однако без дополнения памятью общего назначения архитектура со стеком требует большого количества дополнительных перемещений данных и управления данными. В целях оптимизации операции со стеком PUSH (запись в стек) и POP (извлечение из стека) должны также быть отделены от математических и логических операций. Но как можно заметить из приведенного выше примера, стек особенно неэффективен при повторной загрузке и сохранении данных, так как адреса массива используются с помощью команд PUSH INDIRECT и POP INDIRECT.

В одном из аспектов изобретение содержит систему, содержащую: (a) множество параллельных процессоров в одном чипе (микросхеме); и (b) компьютерную память, расположенную на данном чипе и доступную каждому из процессоров; причем каждый из процессоров предназначен для обработки минимального набора команд, и причем каждый из процессоров содержит схемы локальной кэш-памяти, выделенные каждому из по меньшей мере трех определенных регистров в процессоре.

В различных вариантах осуществления: (1) размер каждой из схем локальной кэш-памяти равен одной строке оперативной памяти в чипе; (2) упомянутые по меньшей мере три определенных регистра, связанных со схемой кэш-памяти, включают в себя регистр команды, регистр источника и регистр адресата; (3) минимальный набор команд содержит семь базовых команд; (4) каждый из процессоров предназначен для обработки одного потока; (5) накапливающий сумматор является операндом для каждой команды, кроме команды приращения; (6) адресатом для каждой базовой команды всегда является регистр операнда; (7) существуют три регистра с автоматическим увеличением и три регистра с автоматическим уменьшением; (8) набор команд не содержит команд BRANCH и JUMP; (9) каждая команда имеет длину самое большее 8 битов; и (10) один главный процессор отвечает за управление каждым из параллельных процессоров.

В другом аспекте изобретение содержит систему, содержащую: (a) множество параллельных процессоров в одном чипе; и (b) компьютерную память, расположенную на данном чипе и доступную каждому из процессоров, причем каждый из процессоров предназначен для обработки набора команд, оптимизированного для параллельной обработки на уровне потоков.

В различных вариантах осуществления: (1) каждый из процессоров предназначен для обработки минимального набора команд; (2) каждый из процессоров содержит схемы локальной кэш-памяти, выделенные каждому из по меньшей мере трех определенных регистров в процессоре; (3) размер каждой из схем локальной кэш-памяти равен одной строке оперативной памяти в чипе; (4) упомянутые по меньшей мере три определенных регистра включают в себя регистр команды, регистр источника и регистр адресата; (5) минимальный набор команд содержит семь базовых команд; (6) каждый из процессоров предназначен для обработки одного потока; (7) один главный процессор отвечает за управление каждым из параллельных процессоров; и (8) минимальный набор команд включает в себя минимальный набор расширений команд для оптимизации работы процессора и обеспечения эффективности программного компилятора.

В другом варианте осуществления изобретение содержит способ параллельной обработки на уровне потоков, использующий множество параллельных процессоров, главный процессор и компьютерную память в одном чипе, причем каждый из множества процессоров предназначен для обработки минимального набора команд и для обработки одного потока, данный способ содержит: (a) выделение схем локальной кэш-памяти каждому из трех определенных регистров в каждом из множества процессоров; (b) выделение одного из множества процессоров для обработки одного потока; (c) обработку каждого из выделенных потоков с помощью упомянутых процессоров; (d) обработку результатов каждого из потоков, обработанных с помощью этих процессоров; (e) высвобождение одного из множества процессоров после того как поток обработан; и (f) минимальный набор команд включает в себя минимальный набор команд для оптимизации управления процессором.

В различных вариантах осуществления минимальный набор команд содержит семь базовых команд, и команды в минимальном наборе команд имеют длину самое большее 8 битов. Минимальный набор команд может также включать в себя набор расширений команд, кроме этих семи базовых команд, которые оптимизируют внутреннюю работу ЦП TOMI, и помогают оптимизировать выполнение команд программы, выполняемой ЦП TOMI, и оптимизируют работу программных компиляторов для ЦП TOMI.

Варианты осуществления изобретения с множеством ядер ЦП TOMI могут также включать в себя ограниченный набор команд управления процессором, используемых для управления множеством ядер ЦП.

В другом аспекте изобретение содержит систему, содержащую: (a) множество параллельных процессоров, установленных на модуле памяти; (b) внешний контроллер памяти; и (c) центральный процессор общего назначения; причем каждый из параллельных процессоров предназначен для обработки набора команд, оптимизированного для параллельной обработки на уровне потоков.

В различных вариантах осуществления: (1) каждый из параллельных процессоров предназначен для обработки минимального набора команд; (2) один или большее количество битов, выделенных в регистре режима памяти, предназначены для включения или выключения одного или большего количества параллельных процессоров; (3) модуль памяти является модулем памяти с двухсторонним расположением микросхем; (4) каждый из процессоров предназначен для обработки одного потока; (5) множество потоков совместно используют данные через совместно используемую память; (6) множество потоков совместно используют данные через одну или большее количество совместно используемых переменных; (7) модуль памяти является одним или большим количеством из: DRAM, SRAM и флэш-памяти; (8) по меньшей мере один из параллельных процессоров работает в качестве главного процессора, а другие параллельные процессоры работают в качестве подчиненных процессоров; (9) каждый из процессоров имеет тактовую частоту, и каждый из процессоров кроме главного процессора выполнен с возможностью корректировки тактовой частоты процессора для оптимизации или производительности, или потребляемой мощности; (10) каждый из процессоров выполнен с возможностью работы или в качестве главного процессора, или в качестве подчиненного процессора; (11) главный процессор запрашивает выполнение обработки с помощью нескольких подчиненных процессоров, ждет выходную информацию от нескольких подчиненных процессоров и комбинирует данную выходную информацию; (12) главный процессор объединяет выходную информацию от этих нескольких процессоров по мере приема выходной информации от каждого из этих нескольких процессоров; (13) низкая рассеиваемая мощность обеспечивается с помощью остановки одного или большего количества из параллельных процессоров; и (14) каждый из параллельных процессоров связан со счетчиком команд и должен останавливать работу при записи всех единиц (1) в счетчик команд, связанный с данным параллельным процессором.

В другом аспекте изобретение содержит систему, содержащую множество параллельных процессоров, внедренных в кристалл динамической оперативной памяти (DRAM), причем это множество параллельных процессоров связано с внешним контроллером памяти и внешним процессором, причем каждый из параллельных процессоров предназначен для обработки набора команд, оптимизированного для параллельной обработки на уровне потоков.

В различных других вариантах осуществления: (1) кристалл устанавливают в корпус со схемой расположения выводов DRAM; (2) параллельные процессоры устанавливают на модуле памяти с двухсторонним расположением микросхем; (3) система работает как DRAM, кроме тех случаев когда процессоры включены через регистр режима DRAM; (4) внешний процессор предназначен для перемещения данных и команд из соответствующего постоянного запоминающего устройства в DRAM; (5) постоянное запоминающее устройство является флэш-памятью; и (6) внешний процессор предназначен для обеспечения интерфейса ввода/вывода между параллельными процессорами и внешними устройствами.

В другом аспекте изобретение содержит систему, содержащую: (a) множество процессоров в одном чипе; и (b) компьютерную память, расположенную на данном чипе и доступную каждому из процессоров, причем каждый из процессоров предназначен для обработки минимального набора команд, и причем каждый из процессоров содержит схемы локальной кэш-памяти, выделенные каждому из по меньшей мере трех определенных регистров в процессоре.

В различных других вариантах осуществления: (1) размер каждой из схем локальной кэш-памяти равен одной строке оперативной памяти в чипе; (2) каждый процессор имеет доступ к внутренней шине данных оперативной памяти в чипе, и внутренняя шина данных имеет ширину одной строки оперативной памяти; (3) ширина внутренней шины данных равна 1024, 2048, 4096, 8192, 16 328 или 32 656 битов; (4) ширина внутренней шины данных кратна 1024 битам; (5) схемы локальной кэш-памяти, выделенные каждому из по меньшей мере трех определенных регистров в процессоре, предназначены для заполнения или сброса за один цикл чтения из памяти или записи в память; (6) минимальный набор команд состоит по существу из семи базовых команд; (7) набор базовых команд включает в себя команды ADD, XOR, INC, AND, STOREACC, LOADACC и LOADI; (8) каждая команда в минимальном наборе команд имеет длину самое большее 8 битов; (9) минимальный набор команд содержит множество расширений команд для оптимизации выполнения последовательностей команд в процессоре, причем такие расширения команд состоят по существу из менее чем 20 команд; (10) каждое расширение команды имеет длину самое большее 8 битов; (11) минимальный набор команд содержит набор команд для выборочного управления множеством процессоров в чипе; (12) каждая команда управления процессором имеет длину самое большее 8 битов; (13) множество процессоров создают в одном чипе с компьютерной памятью, расположенной в данном чипе, используя полупроводниковый производственный процесс, разработанный для монолитных устройств памяти; (14) полупроводниковый производственный процесс использует менее 4 слоев металлических соединений; (15) полупроводниковый производственный процесс использует менее 3 слоев металлических соединений; (16) интеграция множества процессоров в схему компьютерной памяти приводит к менее чем 30%-ному увеличению площади кристалла чипа; (17) интеграция множества процессоров в схему компьютерной памяти приводит к менее чем 20%-ному увеличению площади кристалла чипа; (18) интеграция множества процессоров в схему компьютерной памяти приводит к менее чем 10%-ному увеличению площади кристалла чипа; (19) интеграция множества процессоров в схему компьютерной памяти приводит к менее чем 5%-ному увеличению площади кристалла чипа; (20) менее 250 000 транзисторов используются для создания каждого из процессоров в чипе; (21) чип производят с использованием полупроводникового производственного процесса, который использует менее 4 слоев металлических соединений; (22) каждый из процессоров предназначен для обработки одного потока; (23) накапливающий сумматор является операндом для каждой базовой команды, кроме команды INCREMENT (приращение); (24) адресатом для каждой базовой команды всегда является регистр операнда; (25) существуют три регистра с автоматическим увеличением и три регистра с автоматическим уменьшением; (26) каждой базовой команде требуется для завершения только один такт; (27) набор команд не содержит команд BRANCH и JUMP; и (28) один главный процессор отвечает за управление каждым из параллельных процессоров.

В другом аспекте изобретение содержит систему, содержащую: (a) множество параллельных процессоров в одном чипе; и (b) компьютерную память, расположенную на данном чипе и доступную каждому из процессоров, причем каждый из процессоров предназначен для обработки набора команд, оптимизированного для параллельной обработки на уровне потоков; и причем каждый из процессоров имеет доступ к внутренней шине передачи данных компьютерной памяти в чипе, и внутренняя шина данных не шире одной строки памяти.

В различных вариантах осуществления: (1) каждый из процессоров предназначен для обработки минимального набора команд; (2) каждый из процессоров содержит схемы локальной кэш-памяти, выделенные каждому из по меньшей мере трех определенных регистров в процессоре; (3) размер каждой из схем локальной кэш-памяти равен одной строке компьютерной памяти в чипе; (4) упомянутые по меньшей мере три определенных регистра включают в себя регистр команды, регистр источника и регистр адресата; (5) минимальный набор команд состоит по существу из семи базовых команд; (6) набор базовых команд включает в себя команды ADD, XOR, INC, AND, STOREACC, LOADACC и LOADI; (7) каждая команда в наборе команд имеет длину самое большее 8 битов; (8) каждый из процессоров предназначен для обработки одного потока; (9) один главный процессор отвечает за управление каждым из параллельных процессоров; (10) минимальный набор команд содержит множество расширений команд для оптимизации выполнения последовательностей команд в процессоре, причем такие расширения команд содержат менее чем 20 команд; (11) каждое расширение команд имеет длину самое большее 8 битов; (12) минимальный набор команд содержит набор команд для выборочного управления множеством процессоров в чипе; (13) каждая команда управления процессором имеет длину самое большее 8 битов; и (14) множество процессоров можно создавать в одном чипе с компьютерной памятью, расположенной в данном чипе, используя полупроводниковый производственный процесс, разработанный для монолитных устройств памяти.

В другом аспекте изобретение содержит способ параллельной обработки на уровне потоков, используя множество параллельных процессоров, главный процессор и компьютерную память в одном чипе, причем каждый из множества процессоров предназначен для обработки минимального набора команд и обработки одного потока, при этом данный способ содержит: (a) выделение схем локальной кэш-памяти каждому из трех определенных регистров в каждом из множества процессоров; (b) выделение одного из множества процессоров для обработки одного потока; (c) обработку каждого из выделенных потоков процессорами; (d) обработку результатов каждого потока, обработанных процессорами; и (e) высвобождение одного из множества процессоров после того как поток обработан.

В различных вариантах осуществления: (1) минимальный набор команд состоит по существу из семи базовых команд; (2) базовые команды содержат команды ADD, XOR, INC, AND, STOREACC, LOADACC и LOADI; (3) минимальный набор команд содержит набор команд для выборочного управления множеством процессоров; (4) каждая команда управления процессором имеет длину самое большее 8 битов; (5) способ дополнительно содержит этап обращения каждого из процессоров к компьютерной памяти, используя внутреннюю шину передачи данных памяти, причем внутренняя шина передачи данных имеет ширину одной строки памяти в чипе; и (6) каждая команда в минимальном наборе команд имеет длину самое большее 8 битов.

В другом аспекте изобретение содержит систему, содержащую: (a) множество процессоров, внедренных в чип памяти, который совместим с корпусами стандартных устройств электронной промышленности и схемой размещения выводов таких устройств памяти; и (b) один или большее количество процессоров можно активировать через информацию, передаваемую в регистр режима памяти чипа памяти, причем чип памяти функционально совместим с работой стандартных промышленных устройств памяти, кроме тех случаев когда один или большее количество процессоров активируются через регистр режима памяти.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

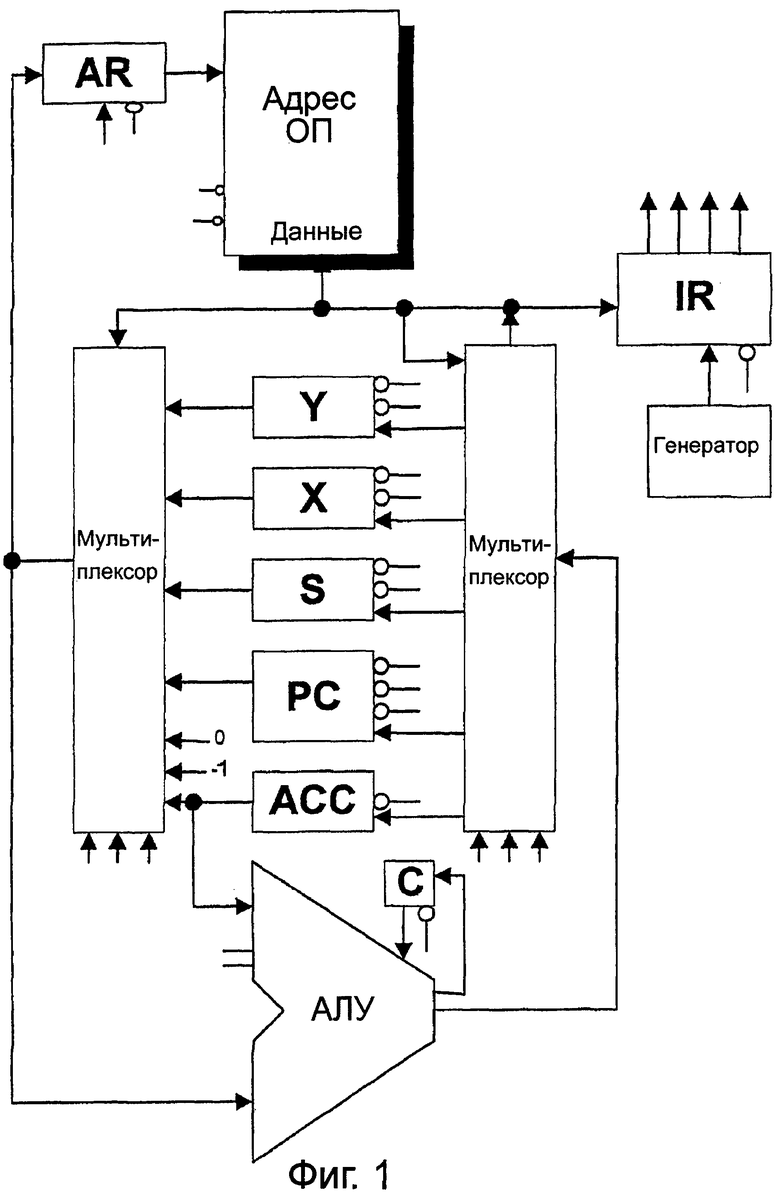

Фиг.1 изображает примерную архитектуру TOMI одного из вариантов осуществления.

Фиг.2 показывает примерный набор базовых команд.

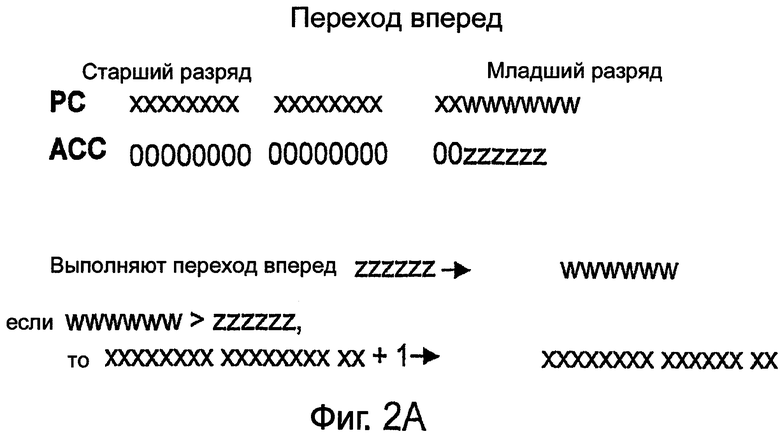

Фиг.2A показывает работу перехода вперед.

Фиг.2B показывает распределение памяти для команд для примерного набора команд TOMI.

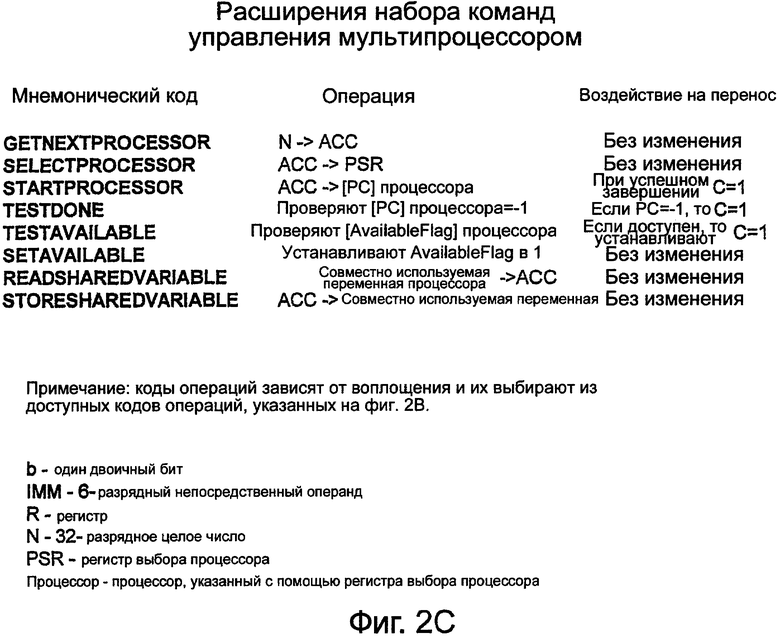

Фиг.2C показывает примерный набор из множества расширений команд управления процессором TOMI.

Фиг.2D показывает схему программирования синхронизации для процессора TOMI.

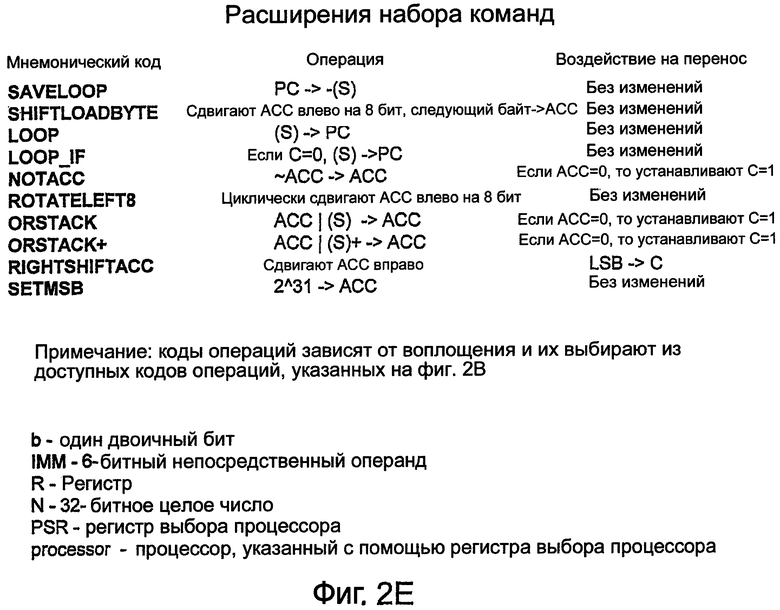

Фиг.2E показывает примерный набор расширений команд.

Фиг.3 показывает фактические адреса при различных способах адресации.

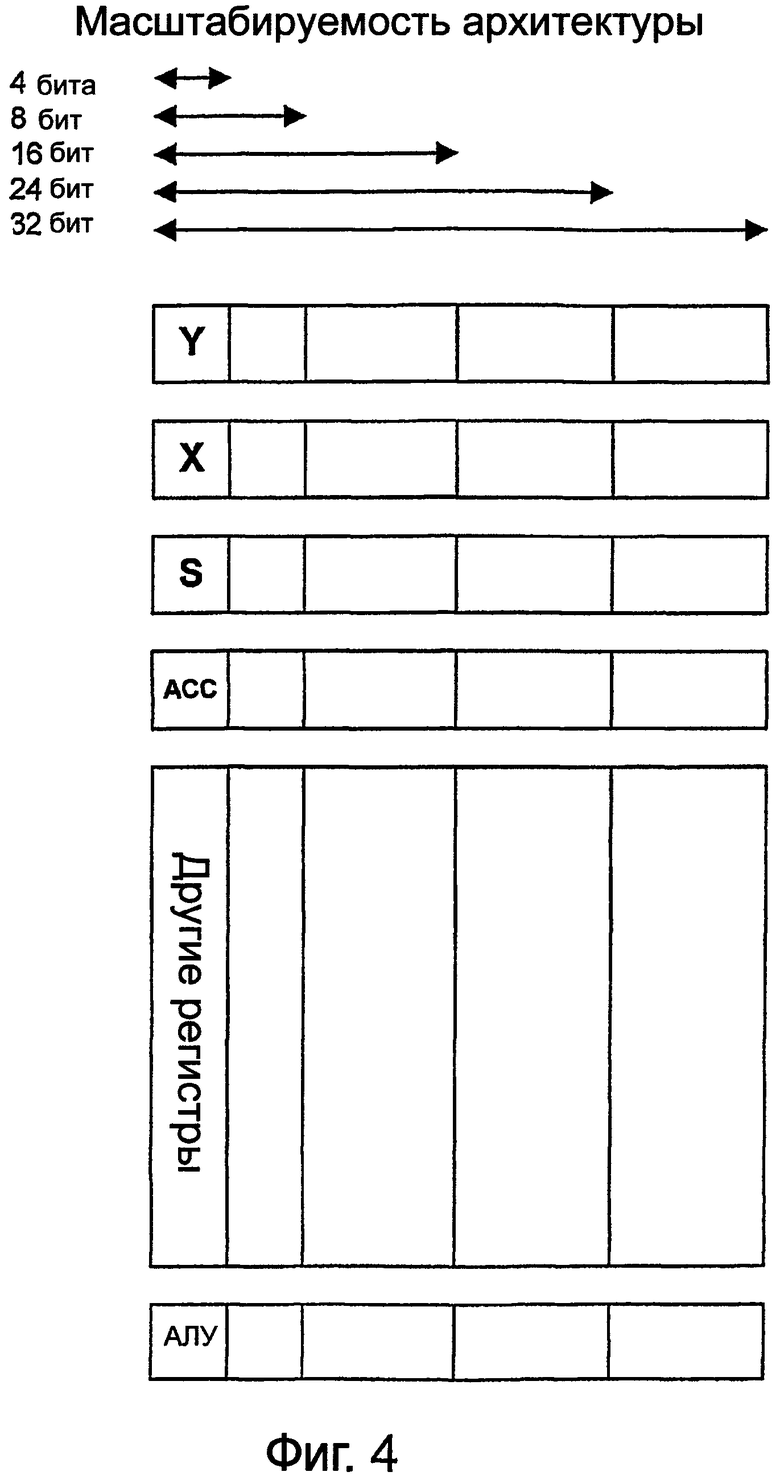

Фиг.4 показывает как легко создавать тракты передачи данных 4-32 битов.

Фиг.5 изображает примерные схемы локальной кэш-памяти.

Фиг.6 изображает примерные состояния управления кэш-памятью.

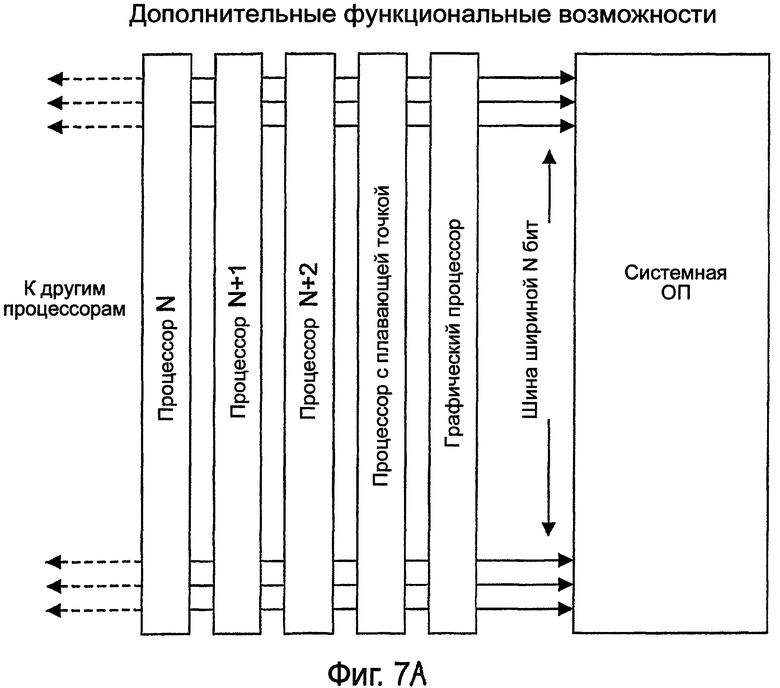

Фиг.7A показывает один из вариантов осуществления дополнительных функциональных возможностей обработки, организованных для использования широкой системной шины оперативной памяти (ОП).

Фиг.7B показывает примерную схему для чередования строк данных для двух блоков памяти, к которым обращается процессор TOMI.

Фиг.8 изображает примерное распределение памяти.

Фиг.9 изображает примерную таблицу доступности процессоров.

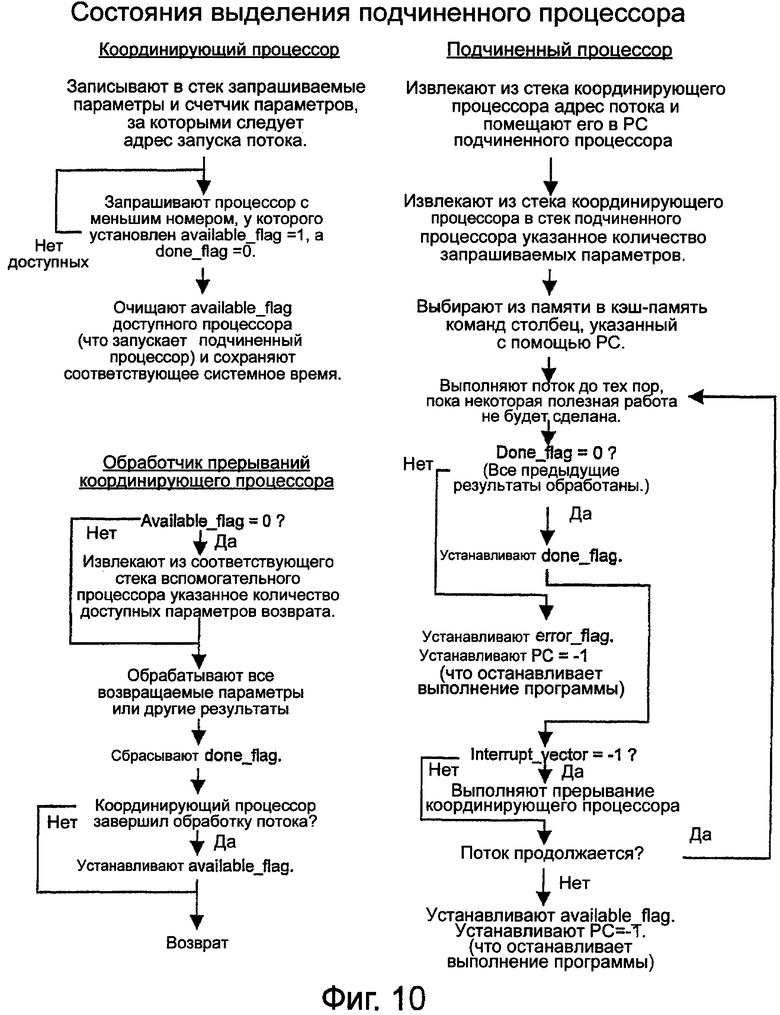

Фиг.10 показывает три компонента выделения процессора.

Фиг.10A показывает вариант осуществления множества процессоров TOMI в корпусе DIMM.

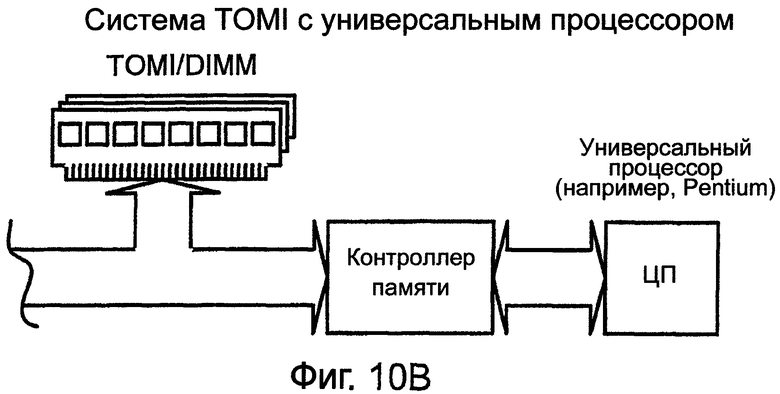

Фиг.10B показывает вариант осуществления множества процессоров TOMI на модуле DIMM, которые взаимодействуют с универсальным ЦП.

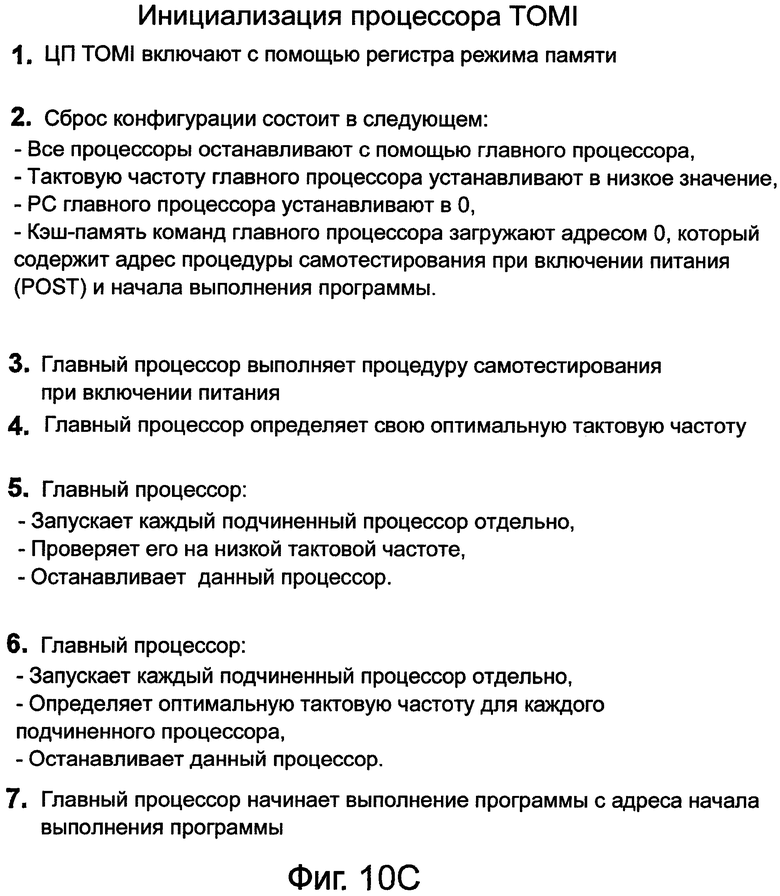

Фиг.10C изображает примерную инициализацию процессора TOMI для варианта осуществления множества процессоров TOMI.

Фиг.10D показывает использование регистра режима памяти для инициализации процессора TOMI.

Фиг.10E изображает примерную диаграмму состояний доступности процессора TOMI.

Фиг.10F показывает примерную конструкцию схемы связи между процессорами.

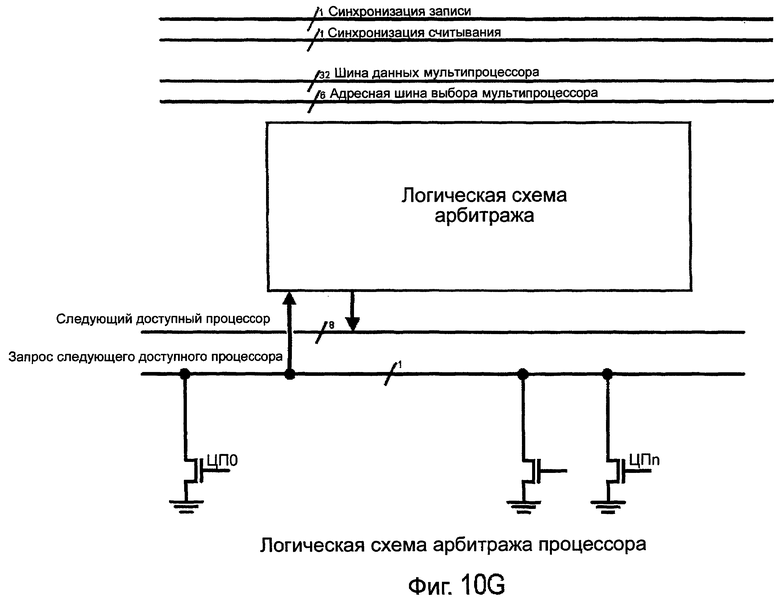

Фиг.10G показывает примерную аппаратную реализацию для идентификации процессора TOMI для выполнения задания.

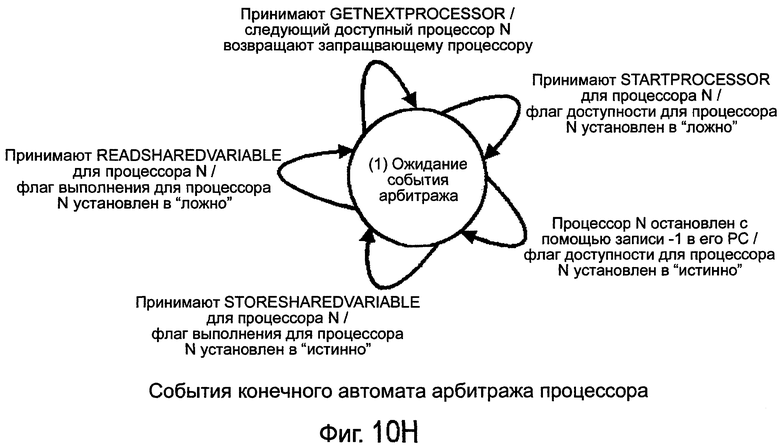

Фиг.10H показывает примерную схему арбитража процессора.

Фиг.11 изображает примерное разделение на составные части.

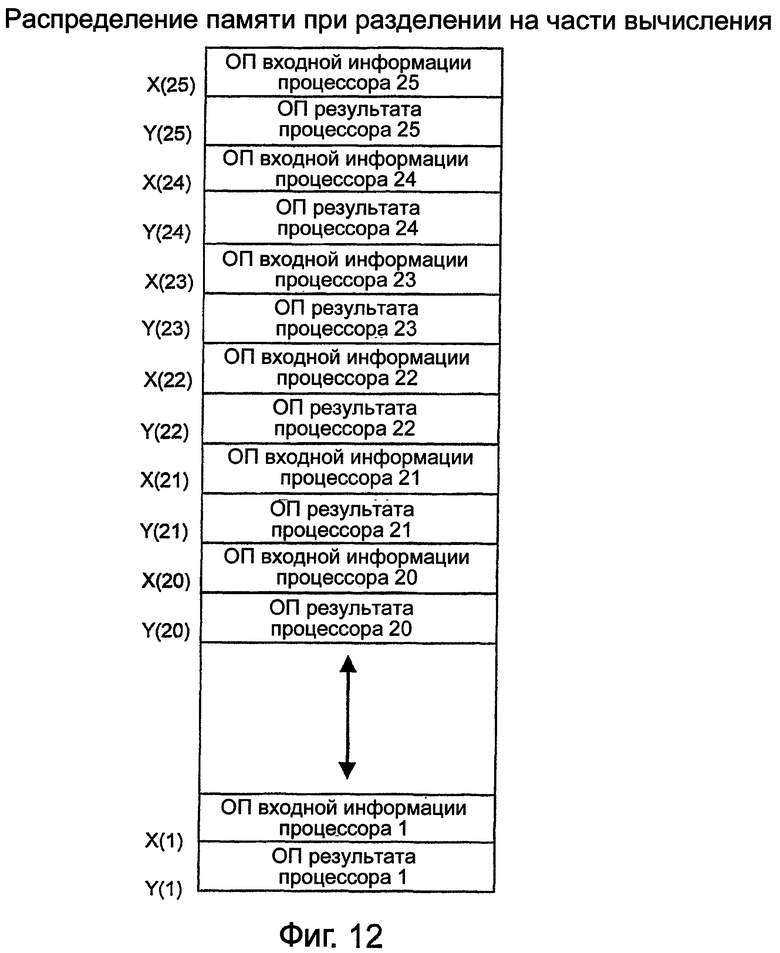

Фиг.12 изображает примерную системную ОП.

Фиг.13A изображает примерный общий план компоновки монолитного (единого) массива из 64 процессоров TOMI.

Фиг.13B изображает другой примерный общий план компоновки монолитного массива процессоров TOMI.

Фиг.14A изображает примерный общий план компоновки чипа контроллера ввода/вывода TOMI (TOMIPCC).

Фиг.14B изображает примерную конструкцию для применения переводчика с одного языка на другой для сотового телефона с использованием TOMIPCC.

Фиг.14C изображает примерную конструкцию для применения ориентированной на память базы данных с использованием TOMIPCC и множества DIMM TOMI.

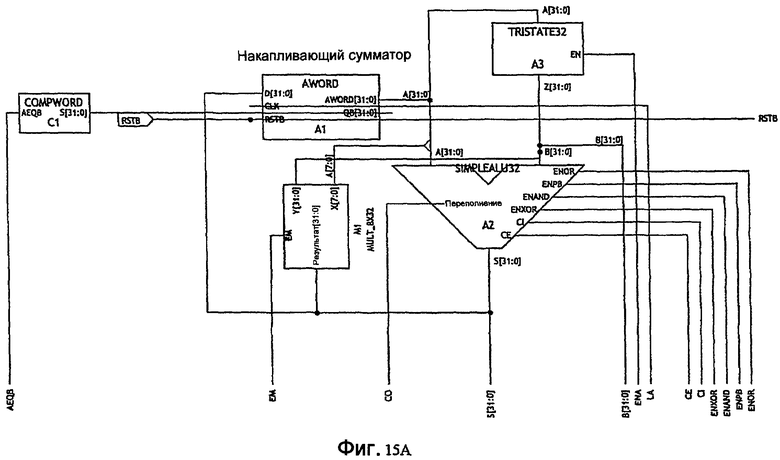

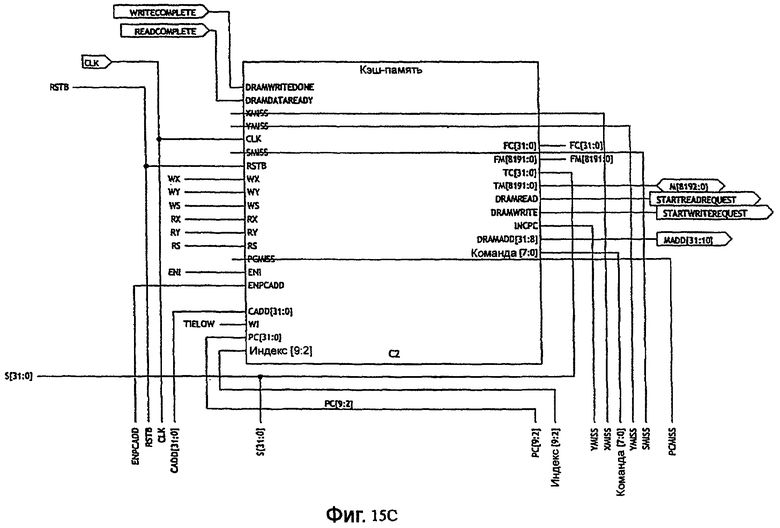

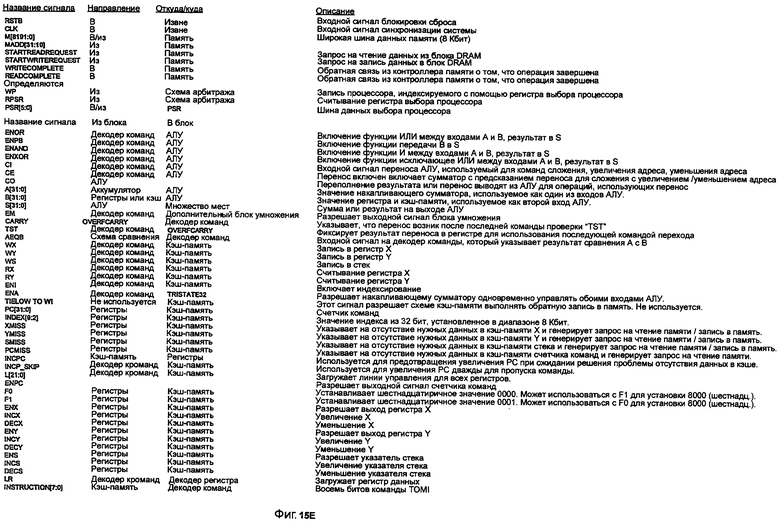

Фиг.15A-15D показывают высокоуровневые схемы примерного варианта осуществления 32-разрядного процессора TOMI.

Фиг.15E показывает описания сигналов для схем, показанных на фиг.15A-D.

ПОДРОБНОЕ ОПИСАНИЕ КОНКРЕТНЫХ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ

В архитектуре TOMI по меньшей мере одного из вариантов осуществления настоящего изобретения предпочтительно использует минимальное количество логических схем, которые могут работать в качестве универсального компьютера. Наиболее распространенным операциям уделяют первостепенное значение. Большинство операций являются очевидными, стандартными и доступными для оптимизации с помощью компилятора.

В одном из вариантов осуществления архитектура TOMI является разновидностью архитектуры с накапливающим сумматором, регистром и стеком, как показано на фиг.1. В данном варианте осуществления:

1. Как в архитектуре с накапливающим сумматором, накапливающий сумматор всегда является одним из операндов, за исключением команды INCREMENT (приращение).

2. Как в архитектуре с регистром, адресатом всегда является один из регистров операнда.

3. Накапливающий сумматор и счетчик команд находятся также в пространстве регистров и поэтому с ними можно проводить операции.

4. Три специальных регистра являются регистрами с автоматическим увеличением и автоматическим уменьшением, и они удобны для создания стеков и потоков ввода/вывода.

5. Все команды имеют длину 8 битов, что упрощает и ускоряет декодирование команды.

6. Нет команд BRANCH или JUMP.

7. Существует только семь базовых команд, что предоставляют возможность использовать для оператора 3 бита из 8-битовой команды, как показано на фиг.2.

Некоторые из преимуществ предпочтительного варианта осуществления включают в себя:

1. Все операции работают на максимальной скорости, которую обеспечивают логические схемы, вместо ограничения одинаковым значением, которое требует конвейер. Логические операции являются самыми быстрыми. Математические операции являются следующими самыми быстрыми. Операции, требующие доступа к памяти, являются самыми медленными.

2. Данную архитектуру можно масштабировать к любой ширине данных, ограниченной только выводами корпуса, временем переноса в сумматоре и возможностью применения.

3. Данная архитектура является архитектурой приблизительно с минимальными функциональными возможностями, необходимыми для выполнения всех операций универсального компьютера.

4. Архитектура является очень прозрачной, очень стандартной, и большинство операций доступно для оптимизации с помощью компилятора.

Данная архитектура разработана так, чтобы было достаточно просто скопировать ее много раз на одном монолитном чипе. В одном из вариантов осуществления множество копий ЦП внедряют как единое целое с памятью. Упрощенный 32-разрядный ЦП можно воплощать менее чем в 1500 схемах, причем большинство схем определяют регистры. Почти 1000 ЦП TOMI предпочтительного варианта осуществления можно воплощать, используя то же самое количество транзисторов, как один Intel Pentium 4.

Сокращенный набор команд в ЦП TOMI представляют для выполнения операций, необходимых для универсального компьютера. Чем меньше набор команд для процессора, тем более эффективно он будет работать. ЦП TOMI разработан с необычно низким количеством команд по сравнению с современной архитектурой процессора. Например, в одном из вариантов осуществления ЦП TOMI имеет 25 команд по сравнению с процессором Pentium Intel, который имеет 286 команд, процессором Intel Itanium Montecito с 195 командами, процессором StrongARM с 127 командами и процессором IBM Cell с более чем 400 командами.

Команды в наборе базовых команд для ЦП TOMI являются упрощенными и предназначены для выполнения за один такт системы, в противоположность 30 тактам, требуемым для процессора Pentium последнего поколения. Архитектура ЦП TOMI является «безконвейерной» архитектурой. Данная архитектура и выполнение команды за один такт значительно уменьшают или устраняют остановы, зависимости и потраченные впустую такты, что можно найти в других архитектурах с параллельной обработкой или конвейерами. Хотя базовой команде требуется только один такт для выполнения, когда тактовая частота увеличивается (и время такта уменьшается), время, требуемое для перемещения результата выполнения через транзисторные схемы для сложных математических команд (таких, как ADD), может достигать предела одного такта. В таких случаях может быть оптимальным предоставлять два такта для выполнения определенной команды, чтобы не замедлять выполнение более быстрых команд. Это будет зависеть от оптимизации конструкции ЦП по отношению к системной тактовой частоте, производственному процессу и топологии схемы.

Упрощенный набор команд TOMI позволяет создавать 32-разрядный ЦП TOMI с помощью менее чем 5000 транзисторов (который не включает в себя кэш-память). Высокоуровневые схемы варианта осуществления одного 32-разрядного ЦП TOMI показаны на фиг.15A-15D, причем описания сигналов показаны на фиг.15E. Даже вместе со схемами кэш-памяти и соответствующими логическими схемами декодирования 32-разрядный ЦП TOMI можно создавать, используя от 40 000 до 200 000 транзисторов (в зависимости от размера кэш-памяти ЦП), по сравнению с 250 000 000 транзисторов, необходимых для чипа микропроцессора Intel Pentium последнего поколения. Стандартная архитектура микропроцессоров (таких как Intel Pentium, Itanium, IBM Cell и StrongARM, если назвать некоторые из них) требует большое и постоянно увеличивающееся количество транзисторов для обеспечения все возрастающего увеличения производительности обработки. Архитектура ЦП TOMI противоречит такому развитию производства, используя необычно низкое количество транзисторов в ядре ЦП. Небольшое количество транзисторов ЦП TOMI обеспечивает множество преимуществ.

Из-за компактного размера ЦП TOMI множество ЦП можно создавать в одном и том же кремниевом чипе. Это также позволяет создавать множество ЦП в одном и том же чипе с основной памятью, такой как DRAM (динамическая оперативная память), с небольшой дополнительной стоимостью производства по отношению к стоимости производства самого чипа DRAM. Таким образом, множество ЦП TOMI можно помещать в один чип для параллельной обработки только с минимальным увеличением площади кристалла чипа DRAM и стоимости производства. Например, DRAM на 512 Мбайт содержит приблизительно 700 миллионов транзисторов. 64 ЦП TOMI (принимая 200 000 транзисторов для одного ЦП TOMI) добавили бы только 12,8 миллионов транзисторов к любой конструкции DRAM. Для DRAM на 512 Мбайт 64 ЦП TOMI увеличили бы площадь кристалла менее чем на 5%.

ЦП TOMI разработаны для производства с использованием существующих недорогих процессов производства серийно выпускаемой памяти, например устройств DRAM, SRAM (статической оперативной памяти) и флэш-памяти. Небольшое количество транзисторов в ЦП TOMI означает, что ЦП можно создавать на небольшой площади и них можно легко соединять в кремнии, используя недорогой полупроводниковый производственный процесс с 2 слоями металлических соединений, а не сложные и дорогие производственные процессы, используемые для производства больших чипов микропроцессоров (таких, как Intel Pentium), в которых используются 8 или большее количество слоев металлических соединений, или другие технологические процессы создания логических схем. Современные чипы DRAM и другой серийно выпускаемой памяти используют более простые и с меньшей стоимостью полупроводниковые производственные процессы с меньшим количеством слоев (например, 2) металлических соединений для достижения более низких производственных затрат, более высокого объема производства и более высокого выхода готовых изделий. Полупроводниковый производственный процесс для серийно выпускаемых устройств памяти в общем случае характеризуется разработкой устройств с низким потреблением тока; в то время как процессы, используемые для создания современных микропроцессоров, стремятся к характеристикам высокой скорости и высокой эффективности, а не к низкому потреблению тока на уровне транзистора. Возможность эффективно воплощать ЦП TOMI с помощью того же самого производственного процесса, который используется для DRAM и других устройств памяти, позволяет внедрять ЦП TOMI в существующие чипы DRAM (или другие чипы памяти) и использовать дешевые производственные процессы с высоким выходом годных изделий чипов памяти. Это также обеспечивает такое преимущество, что ЦП TOMI можно производить, используя тот же самый корпус и схему размещения выводов устройства (приводя в соответствие, например, к стандартам JEDEC (объединенного инженерного совета по электронным устройствам) для устройств памяти), производственное оборудование, тестовые приборы и тестовые коды, которые в настоящее время находятся в промышленном использовании для DRAM и других чипов памяти. Предпочтительный вариант описывает внедрение ЦП в традиционную DRAM. Это благоприятно контрастирует с альтернативой внедрение DRAM в традиционный микропроцессор. Из-за его большого количества транзисторов по сравнению с предпочтительным вариантом осуществления настоящего изобретения традиционный микропроцессор будет, вероятно, генерировать намного больше электрических помех и тепла, что может неблагоприятно влиять на производительность и надежность внедренной DRAM. Кроме того, внедрение DRAM в традиционный микропроцессор, вероятно, потребует процесс с 8 или большим количеством слоев металлических соединений по сравнению с 2 слоями предпочтительного варианта осуществления. При сравнении результирующее внедрение DRAM в традиционный микропроцессор, вероятно, будет иметь более высокую стоимость, более низкий выход годных изделий, более высокую потребляемую мощность, и в конечном счете более низкую производительность.

Другим преимуществом предпочтительного варианта осуществления является то, что ЦП TOMI являются достаточно небольшими (и требуют небольшой мощности), так что они могут физически находиться рядом со схемой DRAM (или другой памяти) и обеспечивать доступ ЦП к очень широкой внутренней шине данных DRAM. В современных видах динамической оперативной памяти эта шина имеет ширину 1024, 4096 или 8192 битов (или кратна ей), что также обычно соответствует ширине одной строки данных в блоке данных в пределах конструкции DRAM. (Для сравнения шина данных Intel Pentium имеет ширину 64 бита, а шина Intel Itanium - 128 битов). Размер внутренних схем кэш-памяти ЦП TOMI можно устанавливать так, чтобы он соответствовал размеру строки DRAM, чтобы кэш-память ЦП можно было заполнять (или сбрасывать) в одном цикле чтении из памяти или записи в память DRAM. ЦП TOMI использует очень широкую внутреннюю шину данных DRAM в качестве шины данных для ЦП TOMI. Схемы кэш-памяти ЦП TOMI можно разрабатывать для воспроизведения конструкции схемы-защелки строки и/или столбца DRAM для эффективной операции компоновки и создания схемы, что включает в себя передачу данных в кэш-память ЦП TOMI.

Другим преимуществом предпочтительного варианта осуществления является низкий уровень электрических помех, которые генерируют ЦП TOMI, из-за низкого количества транзисторов и из-за того, что данный ЦП использует очень широкую внутреннюю шину данных DRAM для доступа к памяти вместо постоянного управления схемой ввода/вывода для доступа за данными к памяти, расположенной вне данного чипа. Находящиеся в чипе схемы кэш-памяти ЦП обеспечивают непосредственный доступ к данным для обработки, таким образом минимизируя потребность в обращениях к памяти, расположенной вне данного чипа.

Целью разработки архитектуры процессора является обеспечение максимальной емкости и скорости обработки при минимизации мощности, требуемой для обеспечения этой скорости обработки. ЦП архитектуры TOMI является высокоскоростным процессором, потребляющим чрезвычайно мало мощности. Потребляемая мощность процессора непосредственно соотносится с количеством транзисторов, используемых в конструкции. Небольшое количество транзисторов ЦП TOMI минимизирует его потребляемую мощность. Упрощенный и эффективный набор команд также позволяет ЦП TOMI уменьшать свою потребляемую мощность. Кроме того, использование кэш-памяти ЦП TOMI и доступ к находящейся в чипе памяти с использованием широкой внутренней шины данных DRAM избавляют от необходимости постоянно управлять схемой ввода/вывода для доступа к памяти вне данного чипа. Один ЦП TOMI, работающий с тактовой частотой 1 ГГц, будет потреблять приблизительно 20-25 милливатт мощности. Напротив, процессор Intel Pentium 4 требует 130 ватт на частоте 2,93 ГГц, процессор Intel Itanium требует 52 ватт на частоте 1,6 ГГц, процессор StrongARM требует 1 ватт на частоте 200 МГц, и процессор IBM Cell требует 100 ватт на частоте 3,2 ГГц. Известно, что тепловыделение в процессоре непосредственно соотносится с суммарной мощностью, которая требуется процессору. Чрезвычайно малая мощность архитектуры ЦП TOMI избавляет от необходимости использования вентиляторов, больших радиаторов и экзотических механизмов охлаждения, которые можно найти в существующей архитектуре микропроцессоров. В то же самое время архитектура ЦП TOMI с низким энергопотреблением предоставляет возможность применять новые батареи с низким энергопотреблением и использовать электропитание от солнечной энергии.

Набор команд

Эти семь базовых команд в примерном наборе команд показаны на фиг.2 вместе с их битовым отображением. Каждая команда предпочтительно состоит из одного 8-битового слова.

Способы адресации

Фиг.3 показывает фактические адреса при различных способах адресации.

Способы адресации:

Непосредственный способ

Регистровый способ

Косвенный регистровый способ

Косвенный регистровый способ с автоматическим увеличением адреса

Косвенный регистровый способ с автоматическим уменьшением адреса

Особые случаи

Регистр 0 и регистр 1 - оба относятся к счетчику команд (PC). В одном из вариантов осуществления все операции с регистром 0 (PC) в качестве операнда зависят от того, равен ли 1 бит переноса накапливающего сумматора (C). Если C=1, то старое значение PC меняют со значением в накапливающем сумматоре (ACC). Все операции с регистром 1 (PC) в качестве операнда являются безусловными.

В альтернативном варианте осуществления операции записи с регистром 0 (PC) в качестве адресата зависят от равенства 0 бита переноса (C). Если C=1, то никакие операции не выполняются. Если C=0, то значение в накапливающем сумматоре (ACC) записывают в PC, и управление программой переходит на новый адрес PC. Операции записи с регистром 1 (PC) в качестве адресата являются безусловными. Значение в накапливающем сумматоре (ACC) записывают в PC, и управление программой переходит на новый адрес PC.

При операциях чтения с регистром 0 в качестве источника загружают значение PC+2. Таким образом, адрес вершины цикла можно считывать и сохранять для последующего использования. В большинстве случаев адрес цикла будет помещен в стек (S). При операции чтения с регистром 1 в качестве источника загружают значение, на которое указывает следующее полное слово, адресуемое с помощью PC. Таким образом, можно загружать 32-разрядный непосредственный операнд. 32-разрядный непосредственный операнд должен быть выровнен по границе слова, но команда LOADACC может находиться в любом байте в 4-байтовом слове, непосредственно предшествующем 32-разрядному непосредственному операнду. При следующем выполнении чтения PC будут увеличивать таким образом, чтобы он обращался к первой выровненной по границе слова команде после 32-разрядного непосредственного операнда.

Отсутствие перехода

Операции Branch и Jump обычно являются сложной проблемой для разработчиков ЦП, потому что они требуют множества бит «драгоценного» пространства кода операции. Функцию выполнения перехода можно создавать с помощью загрузки необходимого адреса перехода в ACC, используя LOADACC, xx, и затем используя команду STOREACC, PC для выполнения перехода. Переход можно выполнять в зависимости от состояния C, хранящегося в регистре 0.

Пропуск

Пропуск можно создавать с помощью выполнения INC, PC. Выполнение требует два цикла - один для завершения цикла увеличения текущего значения PC и один для INC. Пропуск можно выполнять в зависимости от состояния C с помощью увеличения регистра 0.

Относительный переход

Относительный переход можно создавать с помощью загрузки необходимого смещения в ACC и последующего выполнения команды ADD, PC. Относительный переход можно выполнять в зависимости от состояния C с помощью выполнения сложения с регистром 0.

Переходы вперед

Переходы вперед более удобны, чем переходы назад, поскольку адрес памяти для переходов назад, необходимый для циклов, легко зафиксировать с помощью сохранения PC в качестве этапов программы через вершину цикла в первый раз.

Более эффективный переход вперед, чем относительный переход, можно создавать с помощью загрузки младших битов конечной точки перехода в ACC и последующего сохранения в PC. Так как к PC можно обращаться и условно, и безусловно, в зависимости от использования регистра 0 или регистра 1, переход вперед может также быть условным или безусловным в зависимости от выбора регистра PC (регистра 0 или регистра 1) в качестве операнда-адресата.

Например:

LOADI, #1C

STOREACC, PC

Если старшие биты ACC равны нулю, то только 6 младших битов перемещают в регистр PC. Старшие биты регистра остаются неизменными, если 6 младших битов текущего регистра PC меньше значения ACC, которое будет загружено. Если 6 младших битов текущего регистра PC больше значения ACC, которое будет загружено, то текущий регистр PC увеличивают, начиная с 7-го бита.

Это позволяет эффективно переходить вперед до 31 команд. Этот способ перехода вперед должен использоваться, когда это возможно, потому что ему не только требуется 2 команды по сравнению с 3 командами для относительного перехода, но ему не требуется прохождения через сумматор, что является одной из самых медленных операций. Фиг.2A показывает работу перехода вперед.

Циклы

Вершину цикла можно сохранять, используя LOADACC, PC. Результирующий указатель на вершину логической структуры цикла можно затем сохранять в регистре или помещать в один из автоиндексируемых регистров. Внизу цикла указатель можно извлекать с помощью LOADACC, EA и восстанавливать в PC, используя STOREACC, PC, таким образом вызывая цикл в обратном направлении. Цикл можно выполнять в зависимости от состояния C, хранящегося в регистре 0, таким образом, вызывая условный цикл в обратном направлении.

Самомодифицирующийся код

Можно написать самомодифицирующийся код, используя STOREACC, PC. Команду можно создавать или выбирать в ACC и затем сохранять в PC, где она выполняется как следующая команда. Эта методика может использоваться для создания логической структуры CASE.

Предполагают массив таблицы переходов в памяти, состоящий из N адресов и базового адреса JUMPTABLE. Для удобства JUMPTABLE может находится в младших адресах памяти, таким образом ее адрес можно создавать с помощью LOADI или с помощью LOADI, за которой следуют один или большее количество правых сдвигов, ADD, ACC.

Предполагают, что индекс таблицы переходов находится в ACC, а базовый адрес таблицы переходов находится в регистре общего назначения под названием JUMPTABLE:

ADD, JUMPTABLE добавляют индекс к базовому адресу таблицы переходов.

LOADACC, (JUMPTABLE) загружают индексированный адрес

STOREACC, PC выполняют переход

Если младшая память, начиная с 0000, выделена системным вызовам, каждый системный вызов можно выполнять следующим образом, где SPECIAL_FUNCTION является названием непосредственного операнда 0-63:

LOADI, SPECIAL_FUNCTION загружают номер системного вызова

LOADACC, (ACC) загружают адрес системного вызова

STOREACC, PC переходят к функции

Правый сдвиг

Базовая архитектура не предполагает операции правого сдвига. Если такая операция требуется, то решение предпочтительного варианта осуществления состоит в определении одного из регистров общего назначения в качестве «регистра правого сдвига». STOREACC, RIGHTSHIFT сохраняет ACC, сдвинутый вправо на одну позицию, в «регистр правого сдвига», где его значение можно считывать с помощью LOADACC, RIGHTSHIFT.

Масштабируемость архитектуры

Архитектуре TOMI предпочтительно свойственны 8-битовые команды, но разрядность данных не требуется ограничивать. Фиг.4 показывает, как легко создавать любые тракты передачи данных с разрядностью 4-32 битов. Для обработки данных с большей разрядностью требуется только увеличение разрядности набора регистров, внутренних трактов передачи данных и арифметико-логического устройства до необходимого размера. Верхнее предельное значение для трактов передачи данных ограничено только задержкой распространения переноса сумматора и ресурсами транзистора.

Предпочтительную архитектуру TOMI для простоты осуществляют как конфигурацию памяти фон Неймана, но также возможна реализация архитектуры Гарварда (с отдельными шинами передачи данных и команд).

Обычные математические операции

Математические операции с двоичными дополнительными кодами можно выполнять несколькими способами. Регистр общего назначения можно предварительно устанавливать во все «1» и называть ALLONES. Операнд, как предполагают, будет находиться в регистре под названием OPERAND:

LOADACC, ALLONES

XOR, OPERAND

INC, OPERAND двоичный дополнительный код остается в регистре OPERAND.

Обычные конструкции компилятора

Большинство компьютерных программ генерируют с помощью компилятора. Поэтому удобная архитектура вычислительной системы должна иметь большой опыт по части обычных конструкций компилятора.

Компилятор языка C обычно поддерживает стек для передачи параметров для вызова функции. Регистры S, X или Y можно использовать в качестве указателя вершины стека. Вызов функции помещает параметры в один из автоиндексируемых регистров, работающих в качестве стека, используя, например, STOREACC, (X)+. При входе в функцию параметры будут извлекать в регистры общего назначения для использования.

Относительная адресация в стеке

Существуют моменты времени, когда при вызове функции передают больше элементов, чем могут вместить регистры общего назначения. Для следующего примера предполагают, что при операции записи в стек уменьшают адрес стека. Если S используется в качестве регистра стека, то считывают N-й элемент относительно вершины стека:

LOADI, N

STOREACC, X

LOADACC, S

ADD, X

LOADACC, (X)

Индексация в массиве

При входе в функцию массива базовый адрес массива располагают в регистре общего назначения под названием ARRAY. Для считывания N-го элемента в массиве:

LOADI, N

STOREACC, X

LOADACC, ARRAY

ADD, X

LOADACC, (X)

Индексация в массиве элементов из N слов

Иногда массив будет выделен для элементов шириной N слов. Базовый адрес массива располагают в регистре общего назначения под названием ARRAY. Для обращения к первому слову N-го элемента в массиве шириной 5 слов:

LOADI, N

STOREACC, X сохраняют во временном регистре

ADD, ACC умножают на 2

ADD, ACC еще раз на 2=4

ADD, X плюс 1=5

LOADACC, ARRAY

ADD, X плюс базовый адрес массива

LOADACC, (X)

Набор расширений команд

Другой вариант осуществления изобретения включает в себя расширения этих семи базовых команд, показанных на фиг.2. Набор расширений команд, показанный на фиг.2E, помогает дополнительно оптимизировать внутреннюю работу процессора TOMI, команд программы и программных компиляторов для процессора TOMI.

SAVELOOP - эта команда помещает текущее значение счетчика команд в стек. Saveloop будет наиболее вероятно выполняться наверху логической структуры цикла. Внизу цикла сохраненное значение счетчика команд будет скопировано из стека и сохранено в счетчике команд, выполняя переход назад к вершине цикла.

SHIFTLOADBYTE - данная команда сдвигает ACC влево на 8 битов, считывает 8-битовый байт после команды и помещает его в младшие 8 битов ACC. Таким образом длинные непосредственные операнды можно загружать с помощью последовательности команд. Например, для загрузки 14-битового непосредственного операнда:

LOADI, #14 || загружают 6 старших битов 14-битового операнда.

SHIFTLOADBYTE || сдвигают 6 битов на 8 позиций влево и загружают следующее 8-битовое значение.

CONSTANT #E8 || восемь битов непосредственного операнда.

Результирующее шестнадцатеричное значение в ACC будет 14E8.

LOOP - данная команда копирует вершину стека в счетчик команд. Цикл будет наиболее вероятно выполняться внизу логической структуры цикла после выполнения Saveloop для сохранения счетчика команд наверху цикла. Когда LOOP выполняется, сохраненный счетчик команд копируют из стека и сохраняют в счетчике команд, выполняя переход назад к вершине цикла.

LOOP_IF - данная команда копирует вершину стека в счетчик команд. Она выполняет условный цикл, основываясь на значении C. Loop_if будет наиболее вероятно выполняться внизу логической структуры цикла после выполнения Saveloop для сохранения счетчика команд наверху цикла. Когда Loop_if выполняется, если C=0, то сохраненный счетчик команд будет скопирован из стека и сохранен в счетчике команд, выполняя переход назад к вершине цикла. Если C=1, то счетчик команд увеличится для указания на следующую последовательную команду.

NOTACC - выполняют двоичное дополнение каждого бита ACC. Если ACC=0, то устанавливают C в 1. Иначе устанавливают C в 0.

ROTATELEFT8 - выполняют циклический сдвиг 8 битов ACC влево. На каждом этапе циклического сдвига старшие биты, выдвигаемые из ACC, сдвигают в младшие биты ACC.

ORSTACK - выполняют «логическое ИЛИ» с ACC и значением на вершине стека. Помещают результат в ACC. Если ACC=0, то устанавливают C в 1. Иначе устанавливают C в 0.

ORSTACK+ - выполняют «логическое ИЛИ» с ACC и значением на вершине стека. Помещают результат в ACC. После логической операции увеличивают указатель вершины стека, S. Если ACC =0, то устанавливают C в 1. Иначе устанавливают C в 0.

RIGHTSHIFTACC - сдвиг ACC вправо на один бит. Младший бит ACC сдвигают в C.

SETMSB - устанавливают старший бит ACC. Нет никаких изменений в C. Эта команда используется при выполнении сравнения со знаком.

Локальное кэширование TOMI

Кэш-память является памятью, которая имеет меньший размер и более быстрый доступ, чем оперативная память. Уменьшенное время доступа и локальность обращаемых программ и данных позволяют операциям кэш-памяти увеличивать производительность предпочтительного процессора TOMI для многих операций. С другой точки зрения кэш-память увеличивает производительность параллельной обработки, увеличивая независимость процессора TOMI от оперативной памяти. Относительная производительность кэш-памяти по отношению к оперативной памяти и количество циклов, которые процессор TOMI может выполнять, прежде чем потребуется другая загрузка из оперативной памяти в кэш-память или сохранение из кэш-памяти, определяют величину увеличения производительности из-за параллелизма процессоров TOMI.

Схемы локальной кэш-памяти TOMI увеличивают производительность из-за параллелизма процессоров TOMI. У каждого процессора TOMI предпочтительно существуют три связанные с ним схемы локальной кэш-памяти, как показано на фиг.5:

Команды - связана с PC

Источника - связана с регистром X

Адресата - связана с регистром Y

Так как кэш-память связана с определенными регистрами, а не с выборками «данных» или «команды», логика управления кэш-памятью является упрощенной, и время ожидания кэш-памяти значительно уменьшено. Оптимальная размерность этих схем кэш-памяти зависит от применения. Обычный вариант осуществления может потребовать 1024 байтов для каждой кэш-памяти. Другими словами, 1024 команды, и 256 32-разрядных слов источника и адресата. По меньшей мере два фактора определяют оптимальный размер схем кэш-памяти. Прежде всего количество состояний, которые процессор TOMI может выполнять перед тем как потребуется другая операция загрузки или сохранения кэш-памяти. Затем затраты на операцию загрузки или сохранения кэш-памяти из/в оперативную память по отношению к количеству циклов выполнения процессора TOMI, возможных во время данной операции оперативной памяти.

Внедрение процессоров TOMI в ОП

В одном из вариантов осуществления широкая шина соединяет большую внедренную память с кэш-памятью, таким образом операции загрузки или сохранения в кэш-памяти могут происходить быстро. Когда процессоры TOMI внедряют в ОП, загрузка или сохранение всей кэш-памяти состоит из одного цикла обращения к памяти к столбцу ОП. В одном из вариантов осуществления встроенная память будет отвечать на запросы 63 процессоров TOMI, таким образом время ответа при загрузке или сохранении кэш-памяти для одного процессора TOMI может быть увеличено до завершения загрузки или сохранения кэш-памяти другого процессора TOMI.

Кэш-память можно сохранять и загружать, основываясь на изменениях адресующих регистров X, Y, PC соответствующей памяти, как показано на фиг.6. Например, полная ширина регистра PC может составлять 24 бита. Если кэш-память PC составляет 1024 байта, то младшие 10 битов PC определяют доступ в пределах кэш-памяти PC. Когда PC записывают таким образом, что существуют изменения в старших 14 битах, требуется цикл загрузки кэш-памяти. ЦП TOMI, связанный с этой кэш-памятью PC, прекращает выполнение программы, пока цикл загрузки кэш-памяти не будет закончен, и указанную команду можно будет выбрать из кэш-памяти PC.

Двойная буферизация кэш-памяти

Вторичную кэш-память можно загружать, упреждая запрос загрузки кэш-памяти. Две кэш-памяти являются идентичными и поочередно выбираются и освобождаются, основываясь на содержимом старших 14 битов PC. В приведенном выше примере, когда старшие 14 битов PC изменяются для соответствия тем данным, которые предварительно кэшируют во вторичной кэш-памяти, вторичную кэш-память выбирают в качестве первичной кэш-памяти. Бывшая первичной кэш-память теперь становится вторичной кэш-памятью. Так как большинство компьютерных программ линейно увеличивается в памяти, в одном из вариантов осуществления изобретения вторичная кэш-память всегда выбирает содержимое кэш-памяти из оперативной памяти, к которой обращаются старшие 14 битов текущего PC плюс 1.

Добавление вторичной кэш-памяти уменьшает время, в течение которого процессор TOMI ожидает данные из памяти, которые будут выбирать из оперативной памяти, когда они перемещаются за пределы границы текущей кэш-памяти. Добавление вторичной кэш-памяти почти удваивает сложность процессора TOMI. Для оптимальной системы это удвоение сложности должно компенсироваться соответствующим удвоением производительности процессора TOMI. Иначе, два более простых процессора TOMI без вторичной кэш-памяти можно воплощать с помощью того же самого количества транзисторов.

Высокоскоростное умножение, операции с плавающей запятой, дополнительные функциональные возможности:

Целочисленное умножение и все операции с плавающей запятой требуют множества циклов для выполнения, даже с помощью специальных аппаратных средств. Таким образом эти операции можно передавать в другие процессоры, а не использовать для них базовый процессор TOMI. Однако простой блок умножения 16 бит ×16 бит можно добавлять к ЦП TOMI (использующему менее 1000 транзисторов) для обеспечения дополнительных функциональных возможностей и универсальности к архитектуре ЦП TOMI.

При операциях цифровой обработки сигнала (ЦОС) часто используют блоки умножения с большим количеством конвейеров, которые производят результат каждый цикл даже при том, что все умножение может потребовать множества циклов. Для приложений обработки сигналов, которые повторяют тот же самый алгоритм много раз, такая архитектура умножения оптимальна и ее можно внедрять в качестве периферийного процессора в процессор TOMI, но она, вероятно, увеличит сложность и уменьшит полную производительность, если ее внедрять непосредственно в процессор TOMI. Фиг.7A показывает один из примеров дополнительных функциональных возможностей обработки, организованных для использования широкой системной шины ОП.

Доступ к смежным блокам памяти

Физическую конструкцию схемы размещения памяти в чипах памяти часто разрабатывают так, чтобы транзисторы памяти были расположены в больших блоках («банках») ячеек памяти. Блоки обычно организовывают как прямоугольные области одинакового размера и размещают в два или большее количество столбцов в чипе. Схему размещения ячеек памяти в больших блоках ячеек можно использовать для ускорения доступа для чтения из памяти и/или для записи в память.

В одном из вариантов осуществления изобретения один или большее количество процессоров TOMI можно размещать между двумя столбцами блоков ячеек памяти в чипе памяти. Линии передачи данных строк для двух блоков памяти можно перемежать таким образом, что используя логическую схему, показанную на фиг.7B, процессор TOMI может обращаться или к блоку памяти A, или к блоку памяти B, включая «выбор A» или «выбор B». Таким образом можно удваивать память, непосредственно адресуемую определенным процессором TOMI в чипе памяти.

Стратегия прерываний TOMI

Прерывание является событием, внешним к нормальной последовательной работе процессора, которое заставляет процессор немедленно изменять свою последовательность операций. Примерами прерываний может быть завершение операции внешним устройством или условия ошибки некоторых аппаратных средств. Традиционным процессорам требуется много времени для быстрой остановки нормальной последовательной работы, сохранения состояния текущей операции, начала выполнения некоторой специальной операции для обработки, независимо от того, какое событие вызвало прерывание и когда специальная операция закончена - для восстановления предыдущего состояния и продолжения последовательной работы. Первичным показателем качества обработки прерывания является время ответа.

Прерывания создают несколько проблем традиционным процессорам. Они делают время выполнения неопределенным. Они тратят впустую циклы процессора, сохраняя и затем восстанавливая состояния. Они усложняют конструкцию процессора и могут вводить задержки, которые замедляют каждую операцию процессора.

Немедленный ответ на прерывание не нужен для большинства процессоров, исключениями являются обработка ошибок и те процессоры, которые непосредственно взаимодействуют с реальной деятельностью.

В одном из вариантов осуществления многопроцессорной системы TOMI только один процессор обладает возможностью первичного прерывания. Все другие процессоры работают непрерывно, пока они не завершат некоторое задание и пока сами не остановятся, или пока они не будут остановлены координирующим процессором.

Ввод/вывод

В одном из вариантов осуществления конфигурации процессора TOMI один процессор отвечает за все взаимодействие с внешним миром.

Управление прямым доступом к памяти (DMA)

В одном из вариантов осуществления непосредственный ответ на внешнее воздействие в системе процессора TOMI происходит через контроллер DMA. Контроллер DMA, когда этого требует внешнее устройство, перемещает данные из внешнего устройства на внутреннюю шину данных для записи в системную ОП. Тот же самый контроллер также перемещает данные из системной ОП на внешнее устройство, когда это требуется. Запрос DMA имеет самый высокий приоритет для доступа к внутренней шине.

Организация массива процессоров TOMI

Процессоры TOMI предпочтительных вариантов осуществления изобретения разработаны для копирования в большом количестве и для объединения с дополнительными функциональными возможностями обработки, с очень широкой внутренней шиной и системной памятью на монолитном чипе. Примерное распределение памяти для такой системы показано на фиг.8.

Распределение памяти для каждого процессора выделяет первые 32 ячеек (1F в шестнадцатеричном виде) для локальных регистров для данного процессора (см. фиг.3). Остальную память можно адресовать с помощью всех процессоров через их регистры кэш-памяти (см. фиг.6). Адресуемость системной ОП ограничена только шириной трех регистров, связанных со схемами кэш-памяти; PC, X и Y. Если регистры имеют ширину 24 бита, то полная адресуемость составляет 16 мегабайт, но не существует верхнего предела.

В одном из вариантов осуществления 64 процессора TOMI воплощают как единое целое с памятью. Один главный процессор отвечает за управление другими 63. Когда один из подчиненных (вспомогательных) процессоров находится в состоянии ожидания, он не получает сигналы синхронизации, так что он потребляет небольшое количество или совсем не потребляет мощность и выделяет небольшое количество или совсем не выделяет тепло. При инициализации работает только главный процессор. Главный процессор начинает выбирать и выполнять команды до того момента времени, когда поток должен начаться. Каждый поток предварительно компилируют и загружают в память. Для запуска потока главный процессор распределяет поток одному из ЦП TOMI.

Доступность процессора

Координацию доступности процессоров TOMI для выполнения задания предпочтительно обрабатывают с помощью таблицы доступности процессоров, показанной на фиг.9. Координирующий (главный) процессор предпочтительно может выполнять следующие функции:

1. Записывать в стек подчиненного процессора параметры вызова, которые включают в себя адрес выполнения потока, память-источник и память-адресат, но не ограничены ими.

2. Запускать подчиненный процессор.

3. Отвечать на событие завершения потока подчиненного процессора или с помощью опроса или с помощью ответа на прерывание.

Запрос процессора

Координирующий процессор может запрашивать процессор из таблицы доступности. Возвращают номер самого младшего процессора с флагом available_flag, установленным в «0». Координирующий процессор может затем устанавливать флаг available_flag, связанный с доступным процессором, в «1», таким образом запуская подчиненный процессор. Если ни один из процессоров не доступен, то запрос возвращает ошибку. Альтернативно, процессоры можно выделять с помощью координирующего процессора, основываясь на уровне приоритета, связанном с требуемым заданием, которое будут выполнять. Методики распределения ресурсов, основанные на приоритетных схемах, известны из предшествующего уровня техники. Фиг.10 показывает три предпочтительных компонента выделения процессора: операции инициирования координирующего процессора, операции подчиненного процессора и обработка результата с помощью координирующего процессора через ответ на прерывание.

Поэтапный запуск подчиненного процессора

1. Координирующий процессор записывает параметры потока для запуска в свой собственный стек. Параметры могут включать в себя: начальный адрес потока, память-источник для потока, память-адресат для потока и, наконец, parameter_count (счетчик параметров).

2. Координирующий процессор запрашивает доступный процессор.

3. Логическая схема выделения процессора возвращает или номер самого младшего по номеру подчиненного процессора, у которого и установлен его соответствующий флаг available_flag, и сброшен его соответствующий флаг done_flag, или ошибку.

4. Если возвращают ошибку, то координирующий процессор может или повторять запрос, пока подчиненный процессор не станет доступным, или выполнять некоторую специальную операцию для обработки ошибки.

5. Если возвращают номер доступного процессора, то координирующий процессор сбрасывает флаг available_flag для указанного процессора. Эта операция помещает количество параметров стека (parameter_count) в стек выбранного подчиненного процессора. Флаг done_flag обнуляют.

6. Подчиненный процессор извлекает верхний элемент стека и перемещает его в счетчик команд подчиненного процессора.

7. Подчиненный процессор затем выбирает столбец памяти, указанный счетчиком команд, в кэш-памяти команд.

8. Подчиненный процессор начинает выполнять команды с начала кэш-памяти команд. Первые команды, вероятно, извлекут параметры вызова из стека.

9. Подчиненный процессор выполняет поток из кэш-памяти команд. Когда поток завершается, он проверяет состояние связанного с ним флага done_flag. Если флаг done_flag установлен, то он ждет когда флаг done_flag будет сброшен, указывая, что координирующий процессор обработал все предыдущие результаты.

10. Если вектор прерывания, связанный с подчиненным процессором, установлен в -1, то прерывание не будет создано с помощью установки флага done_flag. Координирующий процессор может поэтому опрашивать, установлен ли флаг done_flag.

Когда координирующий процессор обнаруживает, что флаг done_flag установлен, он может обрабатывать результаты подчиненного процессора и может переназначать подчиненный процессор для выполнения нового задания. Когда результаты подчиненного процессора обработаны, соответствующий координирующий процессор сбрасывает соответствующий флаг done_flag.

Если вектор прерывания, связанный с подчиненным процессором, не равен -1, то установка соответствующего флаг done_flag заставит координирующий процессор прерваться и начать выполнять обработчик прерываний по адресу вектора прерывания.

Если соответствующий флаг available_flag также установлен, то координирующий процессор может также считывать параметры возврата, записанные в стек подчиненного процессора.

Обработчик прерываний обработает результаты подчиненного процессора и может переназначать подчиненный процессор для выполнения нового задания. Когда результаты подчиненного процессора обработаны, обработчик прерываний, работающий на координирующем процессоре, сбрасывает соответствующий флаг done_flag.

11. Если флаг done_flag сбрасывают, то подчиненный процессор устанавливает свой соответствующий флаг done_flag и сохраняет новое время начала (start_time). Подчиненный процессор может продолжать выполнять задание или может возвращаться в доступное состояние. Для возвращения в доступное состояние подчиненный процессор может помещать параметры возврата в свой стек, сопровождаемый счетчиком стека, и устанавливать свой флаг available_flag.

Управление процессорами TOMI с использованием регистра режима памяти