Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых интерфейсов и аналоговых микросхем различного функционального назначения (например, в компараторах, прецизионных решающих и инструментальных усилителях с малыми значениями статической погрешности и т.п.).

В современной радиоэлектронной аппаратуре находят применение дифференциальные операционные усилители (ОУ) с существенными различными параметрами. Особое место занимают ОУ с простейшей двухкаскадной архитектурой, содержащие небольшое число элементов. На их основе выполняются, например, различные классы селективных цепей, где число маломощных усилителей может измеряться десятками единиц. Предлагаемое изобретение относится к данному типу ОУ.

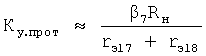

Наиболее близким по сущности к заявляемому техническому решению является классическая схема ОУ фиг.1, представленная в патенте США №4.223.276, fig.2, которая также присутствует в большом числе других патентов [1-15].

Существенный недостаток известного ОУ фиг.1 состоит в том, что он имеет повышенное значение систематической составляющей напряжения смещения нуля (Uсм), зависящей от свойств его архитектуры, а также сравнительно небольшой коэффициент усиления по напряжению (Ку) при низкоомных сопротивлениях нагрузки (Rн).

Основная задача предлагаемого изобретения состоит в уменьшении абсолютного значения Uсм и его температурного дрейфа.

Дополнительная задача - повышение Ку при малых Rн (50÷100 Ом).

Поставленная задача решается тем, что в прецизионном операционном усилителе фиг.1, содержащем входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, общая эмиттерная цепь которого соединена с первой 4 шиной источника питания, токовое зеркало 5, согласованное со второй 6 шиной источника питания, выход которого соединен со вторым 3 токовым выходом входного дифференциального каскада 1, а вход связан с первым 2 токовым выходом входного дифференциального каскада 1, выходной транзистор 7, эмиттер которого соединен с выходом устройства 8 через первую 9 цепь согласования потенциалов, токостабилизирующий двухполюсник 10, включенный между выходом устройства 8 и первой 4 шиной источника питания, предусмотрены новые элементы и связи - в схему введены первый 11, второй 12, третий 13 и четвертый 14 дополнительные транзисторы, а также дополнительный p-n переход 15, причем база первого 11 дополнительного транзистора соединена со вторым 3 выходом входного дифференциального каскада 1, база второго 12 дополнительного транзистора соединена с первым 2 токовым выходом входного дифференциального каскада 1, коллекторы первого 11 и второго 12 дополнительных транзисторов соединены с первой 4 шиной источника питания, эмиттер первого 11 дополнительного транзистора соединен с базой выходного 7 транзистора и коллектором третьего 13 дополнительного транзистора, эмиттер второго 12 дополнительного транзистора связан с коллектором четвертого 14 дополнительного транзистора, базы третьего 13 и четвертого 14 дополнительных транзисторов связаны с коллектором выходного транзистора 7, эмиттеры третьего 13 и четвертого 14 дополнительных транзисторов подключены ко второй 6 шине источника питания, а дополнительный p-n переход 15 включен между коллектором выходного транзистора 7 и второй 6 шиной источника питания, а вход токового зеркала 5 связан со вторым 2 токовым выходом входного дифференциального каскада 1 через вторую 16 цепь согласования потенциалов.

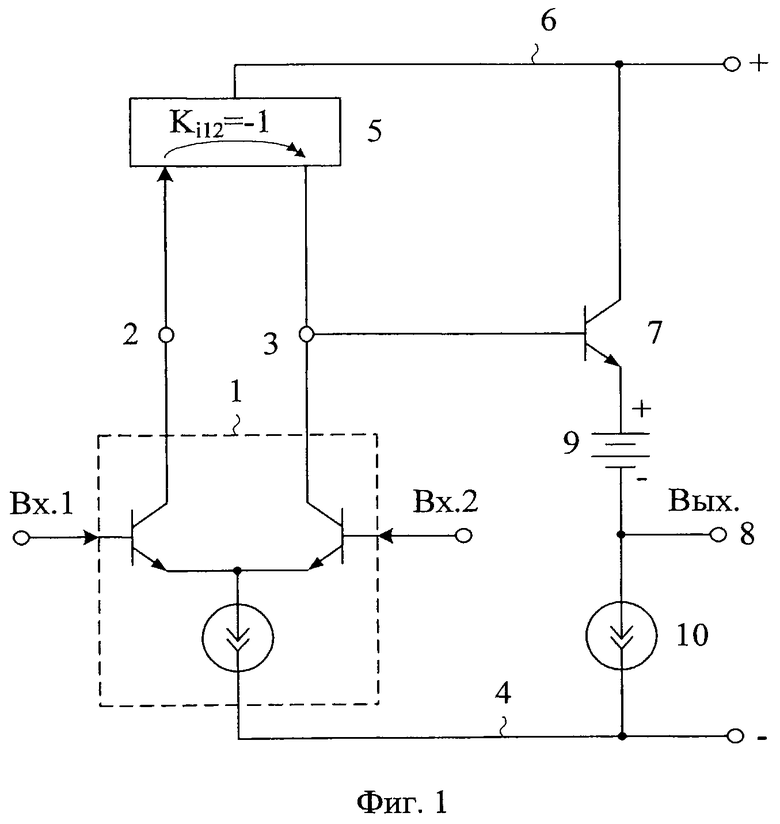

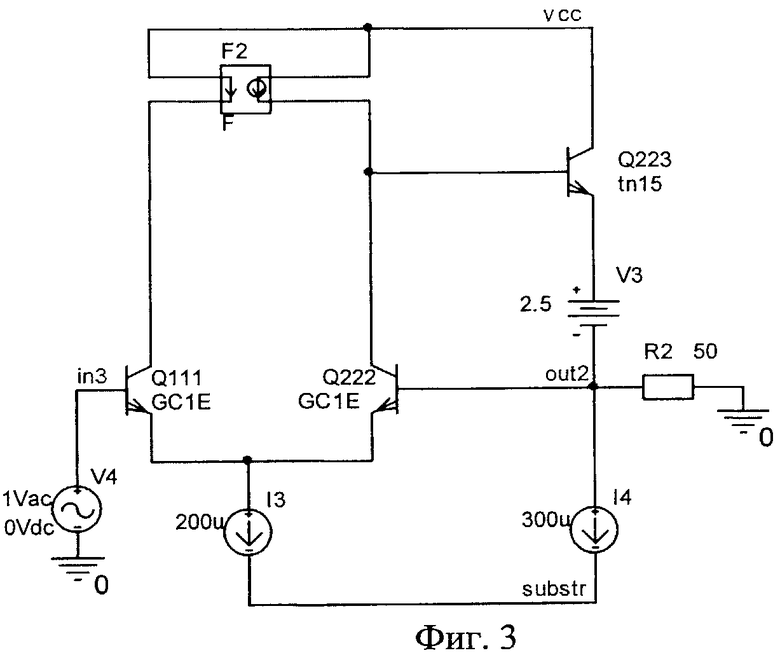

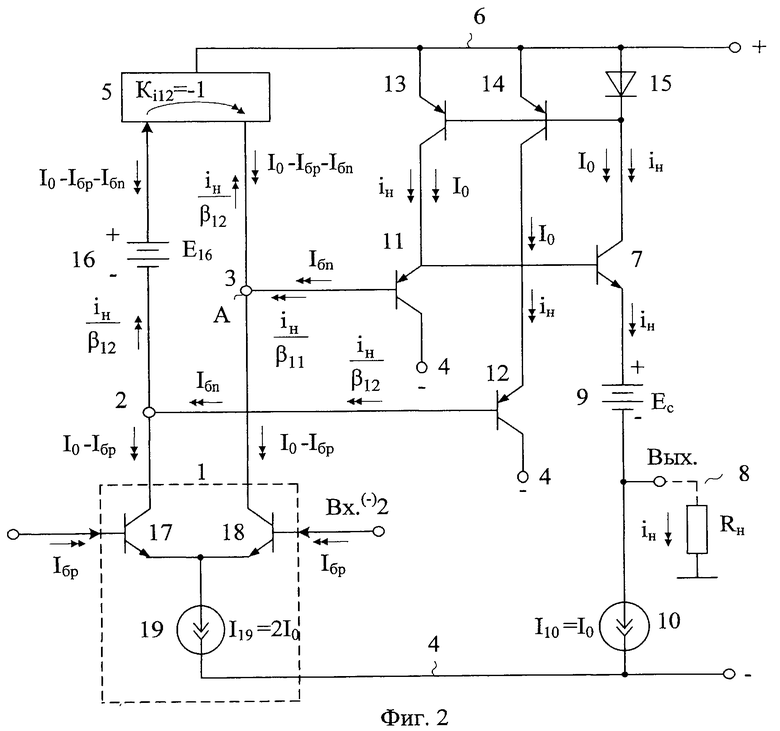

Схема усилителя-прототипа показана на фиг.1. На фиг.2 представлена схема заявляемого устройства в соответствии с формулой изобретения.

На фиг.3 показана схема операционного усилителя-прототипа, а на фиг.4 - заявляемого ОУ в среде компьютерного моделирования PSpice на моделях интегральных транзисторов аналогового базового матричного кристалла АБМК_1_3.

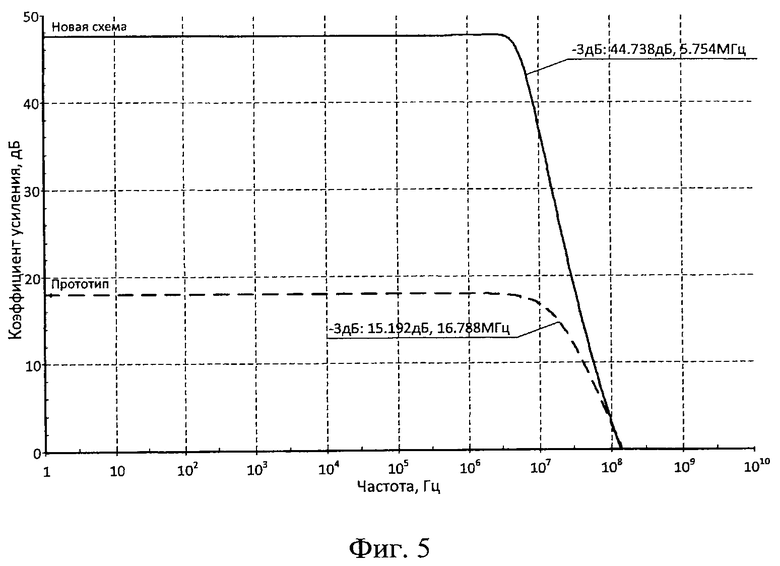

На фиг.5 приведены логарифмические амплитудно-частотные характеристики коэффициента усиления по напряжению сравниваемых схем ОУ фиг.3 и фиг.4.

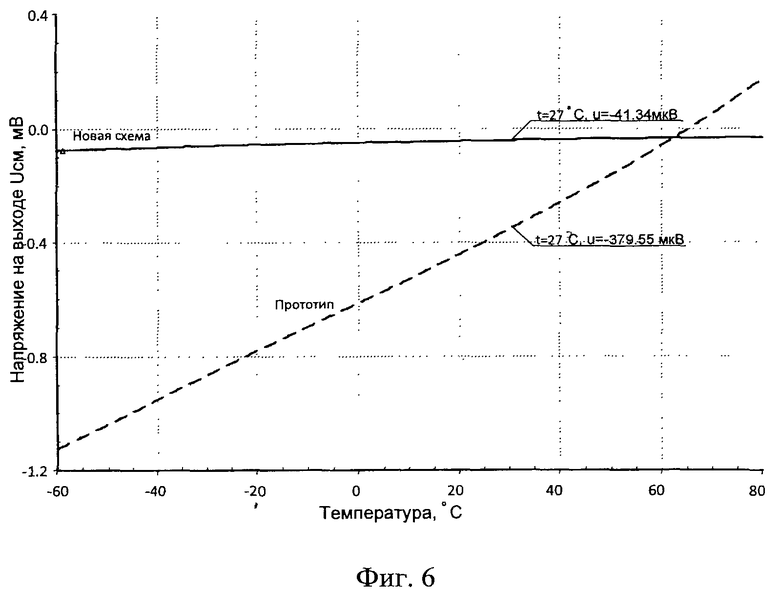

На фиг.6 показана зависимость напряжения смещения нуля сравниваемых схем ОУ фиг.3 и фиг.4 от температуры.

Прецизионный операционный усилитель фиг.2 содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, общая эмиттерная цепь которого соединена с первой 4 шиной источника питания, токовое зеркало 5, согласованное со второй 6 шиной источника питания, выход которого соединен со вторым 3 токовым выходом входного дифференциального каскада 1, а вход связан с первым 2 токовым выходом входного дифференциального каскада 1, выходной транзистор 7, эмиттер которого соединен с выходом устройства 8 через первую 9 цепь согласования потенциалов, токостабилизирующий двухполюсник 10, включенный между выходом устройства 8 и первой 4 шиной источника питания. В схему введены первый 11, второй 12, третий 13 и четвертый 14 дополнительные транзисторы, а также дополнительный p-n переход 15, причем база первого 11 дополнительного транзистора соединена со вторым 3 выходом входного дифференциального каскада 1, база второго 12 дополнительного транзистора соединена с первым 2 токовым выходом входного дифференциального каскада 1, коллекторы первого 11 и второго 12 дополнительных транзисторов соединены с первой 4 шиной источника питания, эмиттер первого 11 дополнительного транзистора соединен с базой выходного 7 транзистора и коллектором третьего 13 дополнительного транзистора, эмиттер второго 12 дополнительного транзистора связан с коллектором четвертого 14 дополнительного транзистора, базы третьего 13 и четвертого 14 дополнительных транзисторов связаны с коллектором выходного транзистора 7, эмиттеры третьего 13 и четвертого 14 дополнительных транзисторов подключены ко второй 6 шине источника питания, а дополнительный p-n переход 15 включен между коллектором выходного транзистора 7 и второй 6 шиной источника питания, а вход токового зеркала 5 связан со вторым 2 токовым выходом входного дифференциального каскада 1 через вторую 16 цепь согласования потенциалов.

В качестве цепей согласования потенциалов 9 и 16 могут использоваться стабилитроны или их транзисторные аналоги, прямосмещенные p-n переходы или резисторы.

Токовое зеркало 5 авторы рекомендуют выполнять в виде токовых зеркал Вильсона или их аналогов, имеющих малую погрешность передачи тока со входа на выход.

В частном случае входной дифференциальный каскад на чертеже фиг.2 реализован на транзисторах 17, 18 и источнике тока 19.

Рассмотрим факторы, определяющие систематическую составляющую напряжения смещения нуля (Uсм) в схеме фиг.2, т.е. зависящие от схемотехники ОУ.

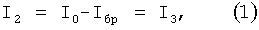

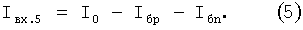

В качестве подсхемы 1 могут применяться различные входные дифференциальные каскады - на полевых транзисторах, с разным построением цепей стабилизации статического режима и т.п. Если выбрать I19=2I0, I10=I0, то токи выходов 2 и 3:

где Iбр - ток базы n-p-n транзисторов при токе эмиттера Iэi=I0;

I0 - заданное значение опорного тока, например, I0=1 мА.

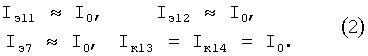

При этом токи эмиттеров и коллекторов транзисторов 11 и 12, 13 и 14, 7:

В этой связи токи базы транзисторов 11 и 12

где Iбn=Iэ.i/βi - ток базы p-n-p транзисторов 11, 12 при эмиттерном токе Iэ.i=I0;

βi - коэффициент усиления по току базы p-n-p транзисторов 11, 12.

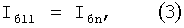

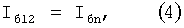

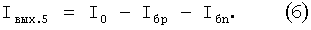

Входной ток токового зеркала 5:

Поэтому выходной ток токового зеркала 5 при коэффициенте передачи Кi12=1:

Как следствие, разность токов в узле «А» при его коротком замыкании на эквипотенциальную общую шину

где Iб11 - ток базы p-n-p транзистора 11;

I3 - ток выходного узла 3 (I3=I0-Iбр).

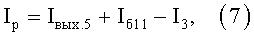

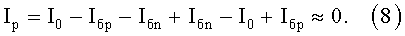

Подставляя (2)÷(6) в (7) находим, что разностный ток Iр, определяющий Uсм

Как следствие, при Ip=0 не требуется смещения нуля на входе ОУ на величину Uсм, подача которого на его входы Bx.(+)1, Bx.(-)2 компенсирует разностный ток Ip в узле «А». Данный вывод подтверждается компьютерным моделированием (фиг.6).

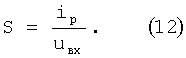

Таким образом, в заявляемом устройстве уменьшается систематическая составляющая Uсм, обусловленная конечной величиной β транзисторов и его радиационной (или температурной) зависимостью. Это уменьшает Uсм, так как разностный ток Ip в узле «А» создает Uсм, зависящее от крутизны преобразования S входного дифференциального напряжения uвx ОУ в выходной ток узла «А»:

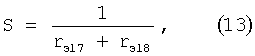

В частном случае (фиг.2):

где rэ17=rэ18 - сопротивления эмиттерных переходов входных транзисторов 17 и 18 входного дифференциального каскада 1.

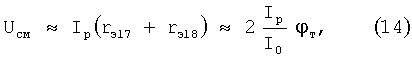

Поэтому для схемы фиг.2

где φт=26 мВ - температурный потенциал.

В ОУ-прототипе (фиг.1) Ip≠0, поэтому здесь систематическая составляющая Uсм получается на порядок больше (Uсм=-380 мкВ), чем в заявляемой схеме (Uсм=41,3 мкВ, (фиг.6)).

Компьютерное моделирование схем фиг.3-фиг.4 подтверждает (фиг.6) данные теоретические выводы.

Если необходимо обеспечить симметрию амплитуд положительных и отрицательных полуволн выходного напряжения ОУ фиг.2, то следует ввести цепи согласования потенциалов 9 и 16.

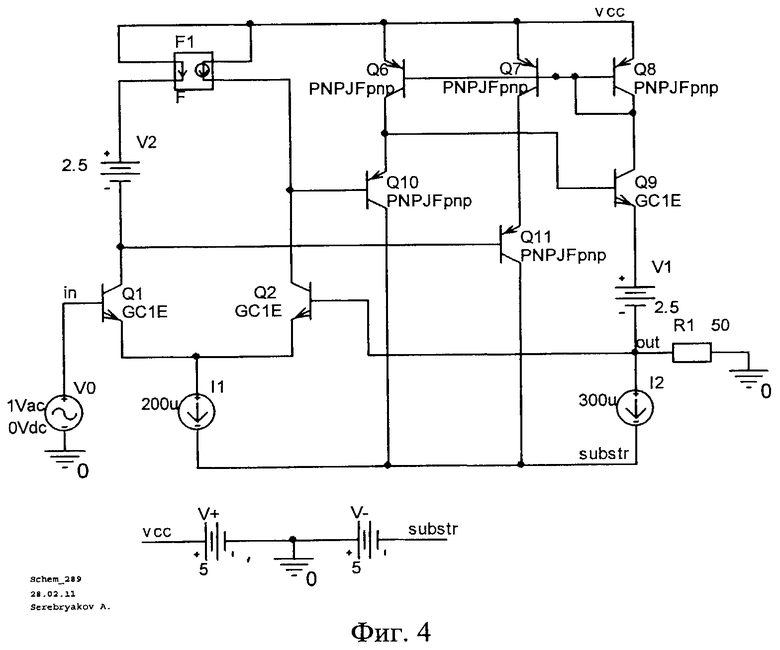

Рассмотрим далее факторы, определяющие коэффициент усиления по напряжению разомкнутого ОУ фиг.2.

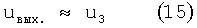

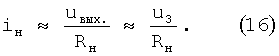

При изменении напряжения u3 на токовом выходе 3 изменяется напряжение на выходе ОУ 8 и ток через нагрузку Rн:

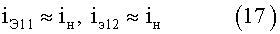

Приращение тока iн передается в коллектор транзистора 7 и далее через транзисторы 14 и 15 - в эмиттеры транзисторов 11 и 12:

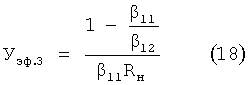

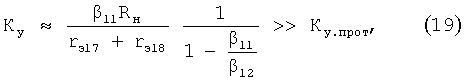

Переменная составляющая тока базы транзистора 12 (iб12) поступает на вход токового зеркала 5 и далее в узел «А», вызывая компенсацию переменной составляющей тока базы (iб11) транзистора 11. Как следствие эффективная проводимость (Уэф.3) в узле «А» уменьшается, что при β11=β12 повышает коэффициент усиления по напряжению ОУ фиг.2:

где  - коэффициент усиления по напряжению ОУ-прототипа фиг.1.

- коэффициент усиления по напряжению ОУ-прототипа фиг.1.

Данные выводы подтверждаются графиками фиг.5.

Таким образом, заявляемое устройство обладает существенными преимуществами в сравнении с прототипом по величине статической ошибки усиления сигналов постоянного тока и коэффициенту усиления по напряжению при низкоомных нагрузках.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №6.114.904, fig.1.

2. Патент США №5.144.169, fig.3.

3. Патент США №5.365.191, fig.9.

4. Патент США №4.223.276, fig.2.

5. Патент DE 2950824.

6. Патент JP 56094810.

7. Патент США №5.144.259, fig.1.

8. Патент США №4.306.198, fig.1.

9. Патент США №4.205.276, fig.3.

10. Патент США №4.757,275.

11. Патент США №4.367.419, fig.5.

12. Патент США №4.191.856, fig.1.

13. Патентная заявка США №2002/0097093, fig.7.

14. Патент JP 51-5545, кл. 9815 А7, 1976.

15. Патент США №6.870.426, fig.5.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412530C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412535C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2010 |

|

RU2446555C2 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402155C1 |

| КАСКОДНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402157C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2455757C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412540C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2400925C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2010 |

|

RU2419198C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412539C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых интерфейсов и аналоговых микросхем различного функционального назначения (например, в компараторах, прецизионных решающих и инструментальных усилителях с малыми значениями статической погрешности и т.п.). Технический результат заключается в уменьшении абсолютного значения Uсм и его температурного дрейфа, а также повышение коэффициента усиления для низкоомных нагрузок. Прецизионный операционный усилитель содержит входной дифференциальный каскад, токовое зеркало, выходной транзистор, первая и вторая цепи согласования потенциалов, токостабилизирующий двухполюсник, с первого по четвертый дополнительные транзисторы, дополнительный р-n переход. 6 ил.

Прецизионный операционный усилитель, содержащий входной дифференциальный каскад (1) с первым (2) и вторым (3) токовыми выходами, общая эмиттерная цепь которого соединена с первой (4) шиной источника питания, токовое зеркало (5), согласованное со второй (6) шиной источника питания, выход которого соединен со вторым (3) токовым выходом входного дифференциального каскада (1), а вход связан с первым (2) токовым выходом входного дифференциального каскада (1), выходной транзистор (7), эмиттер которого соединен с выходом устройства (8) через первую (9) цепь согласования потенциалов, токостабилизирующий двухполюсник (10), включенный между выходом устройства (8) и первой (4) шиной источника питания, отличающийся тем, что в схему введены первый (11), второй (12), третий (13) и четвертый (14) дополнительные транзисторы, а также дополнительный р-n переход (15), причем база первого (11) дополнительного транзистора соединена со вторым (3) выходом входного дифференциального каскада (1), база второго (12) дополнительного транзистора соединена с первым (2) токовым выходом входного дифференциального каскада (1), коллекторы первого (11) и второго (12) дополнительных транзисторов соединены с первой (4) шиной источника питания, эмиттер первого (11) дополнительного транзистора соединен с базой выходного (7) транзистора и коллектором третьего (13) дополнительного транзистора, эмиттер второго (12) дополнительного транзистора связан с коллектором четвертого (14) дополнительного транзистора, базы третьего (13) и четвертого (14) дополнительных транзисторов связаны с коллектором выходного транзистора (7), эмиттеры третьего (13) и четвертого (14) дополнительных транзисторов подключены ко второй (6) шине источника питания, а дополнительный р-n переход (15) включен между коллектором выходного транзистора (7) и второй (6) шиной источника питания, а вход токового зеркала (5) связан со вторым (2) токовым выходом входного дифференциального каскада (1) через вторую (16) цепь согласования потенциалов.

| US 4223276 А, 16.09.1980 | |||

| Пломбировальные щипцы | 1923 |

|

SU2006A1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2411634C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2408975C1 |

Авторы

Даты

2012-05-10—Публикация

2011-04-13—Подача