Текст описания приведен в факсимильном виде.

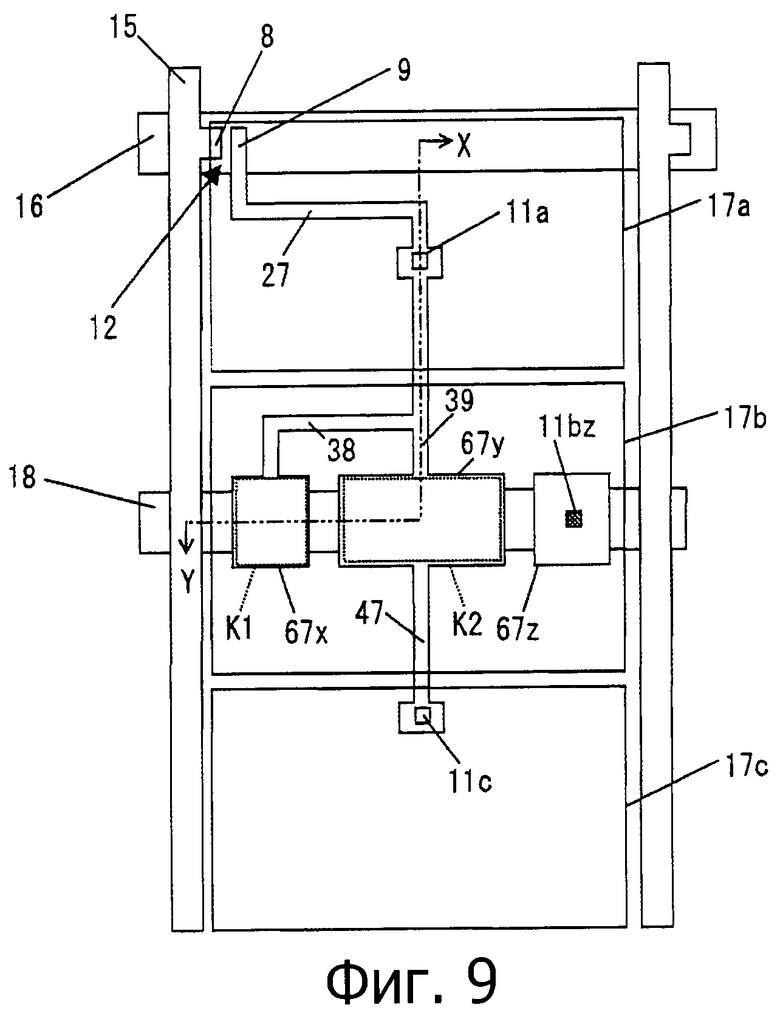

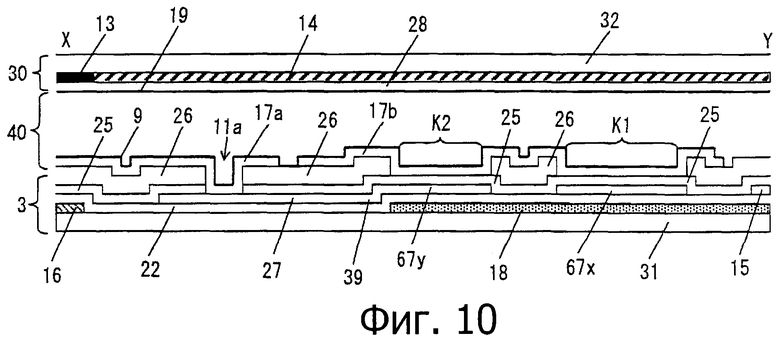

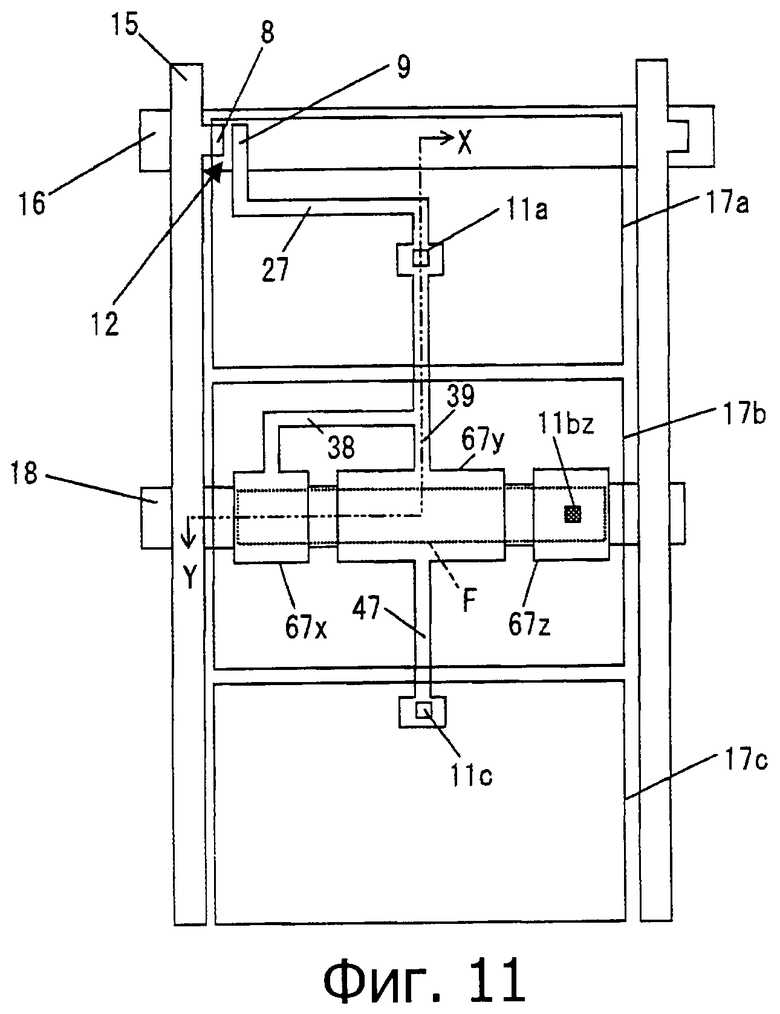

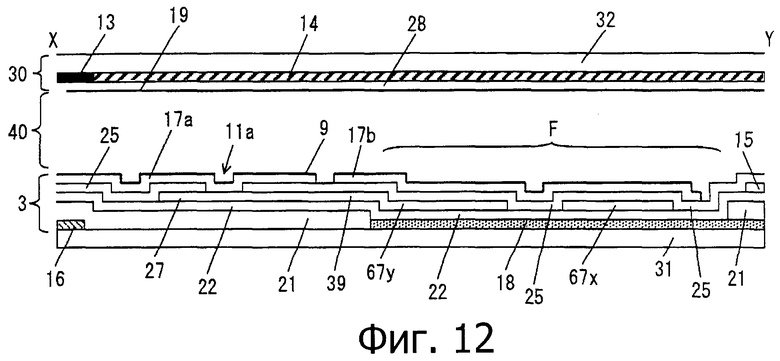

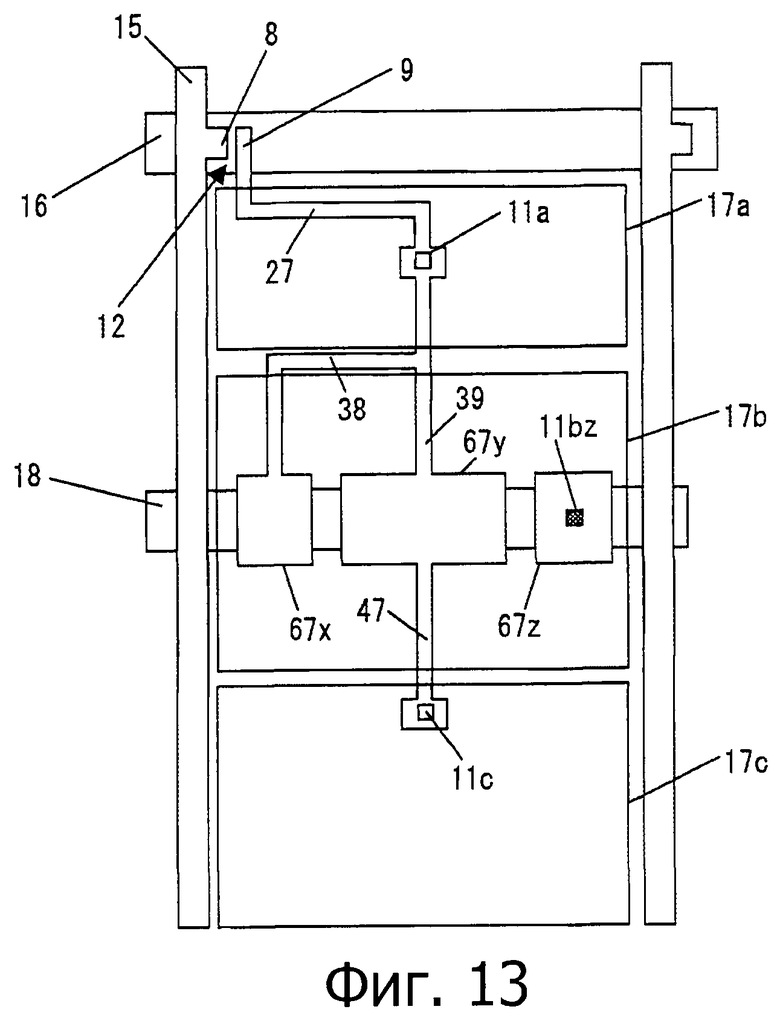

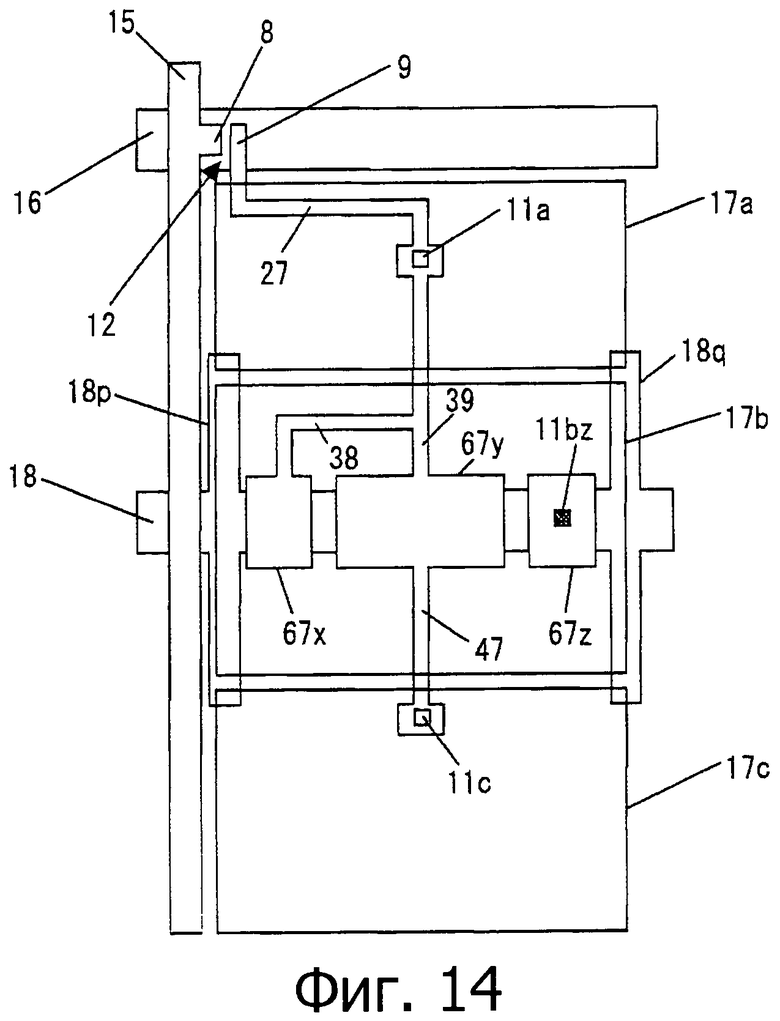

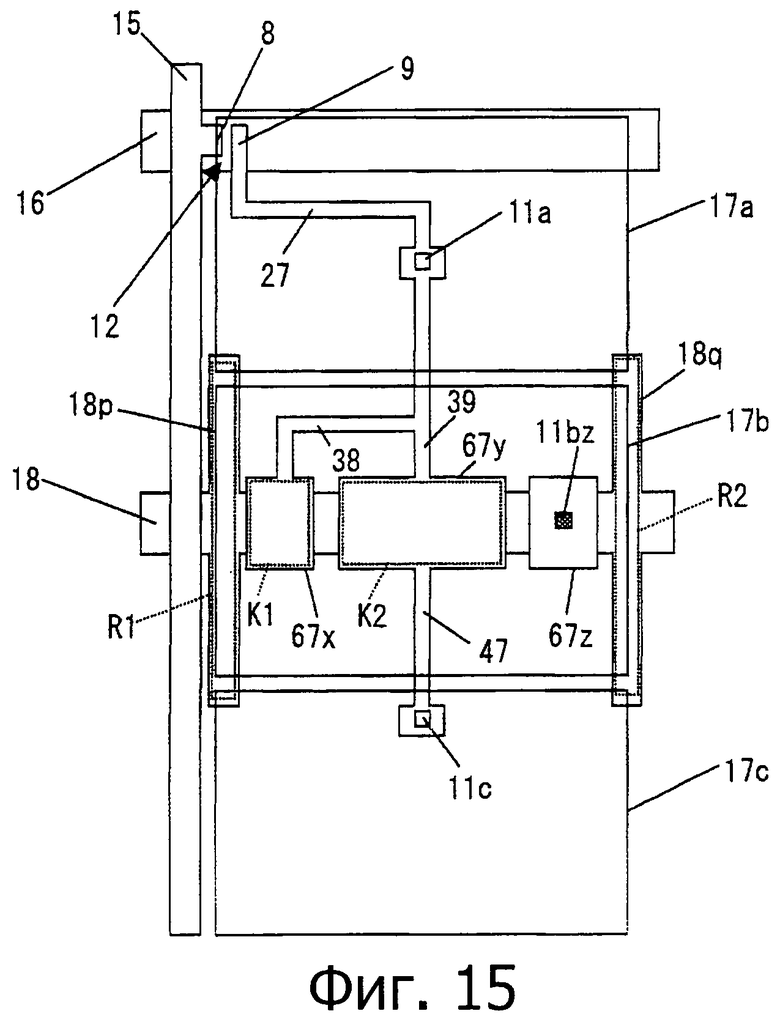

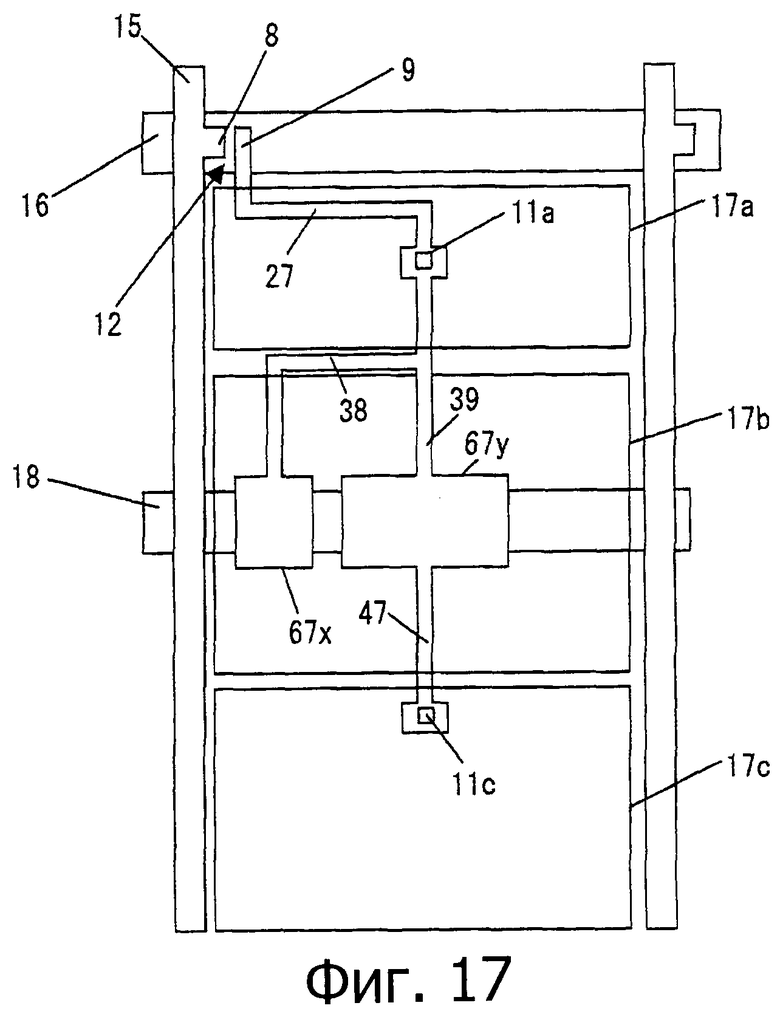

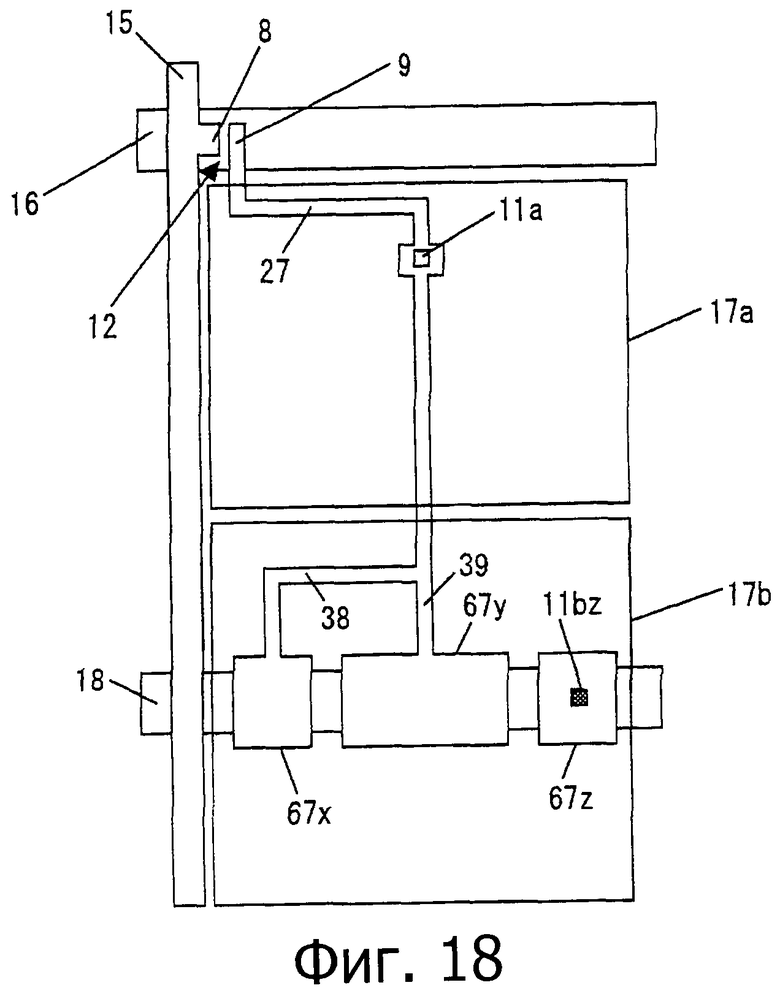

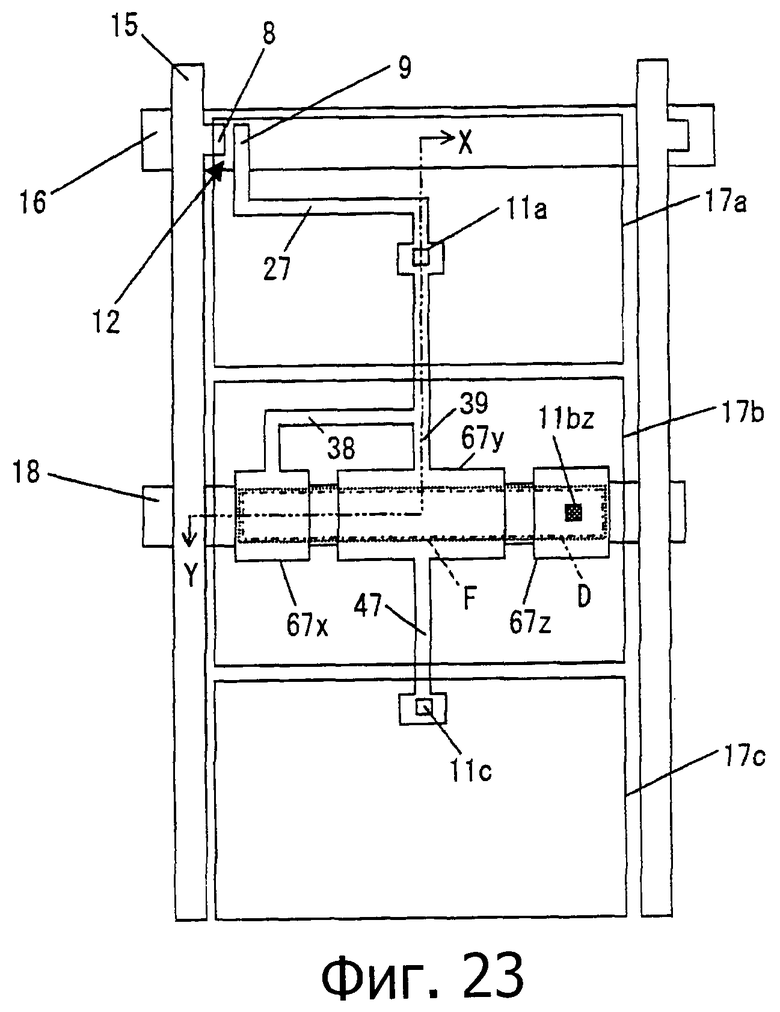

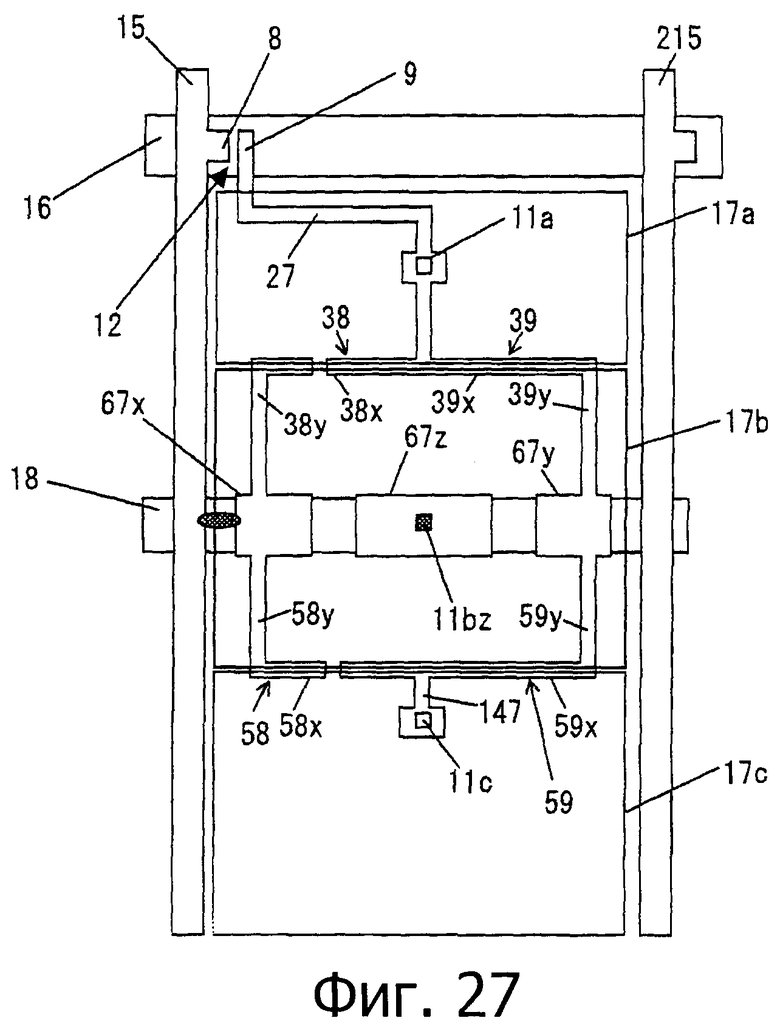

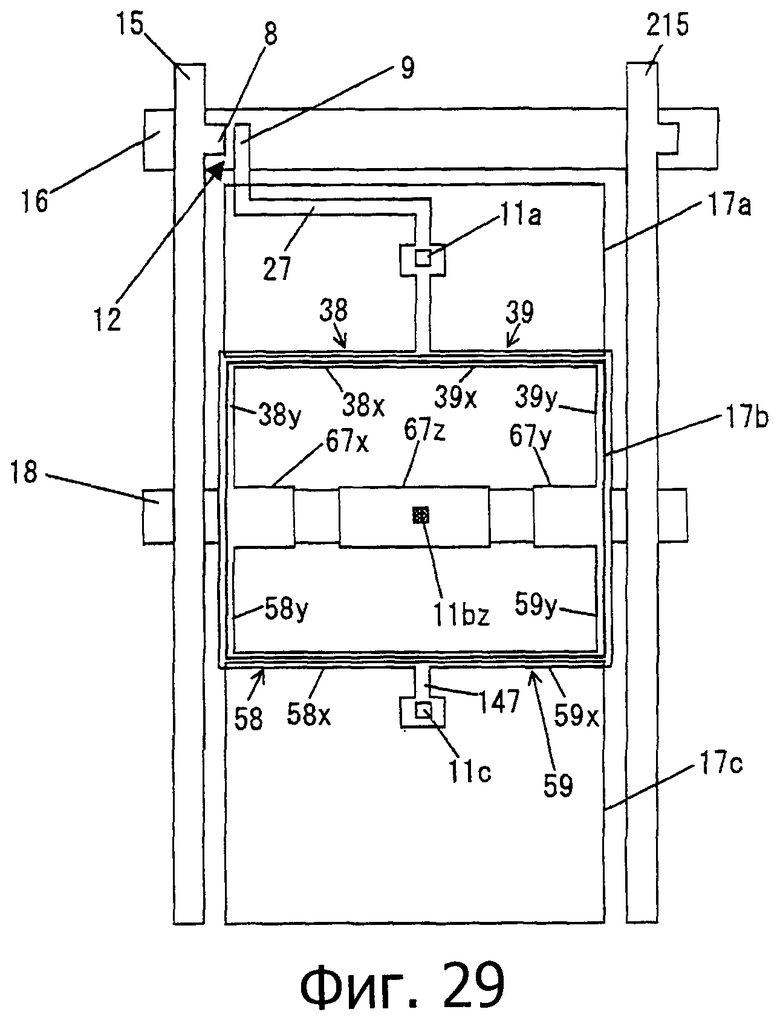

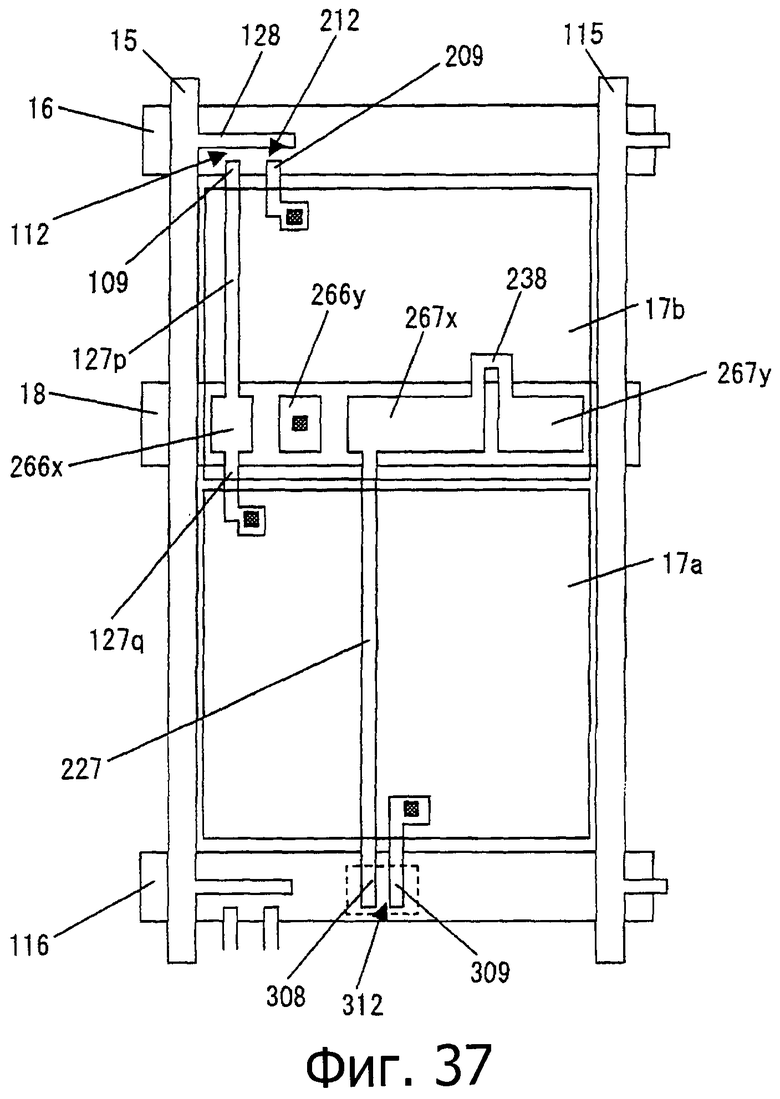

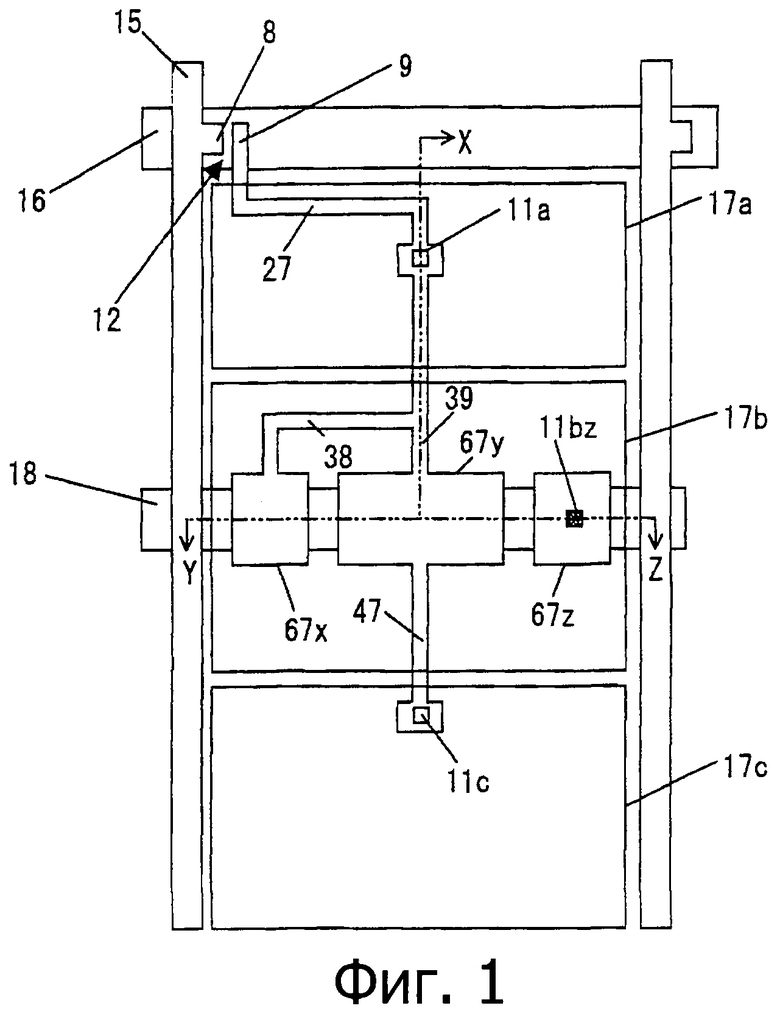

Каждая область пикселя включает в себя первый и второй электроды (17а, 17b) пикселя и первый и второй электроды (67х, 67y) конденсатора, расположенные в слое, в котором находится линия (15) сигнала данных. Первый и второй электроды конденсатора выровнены в направлении строки так, что они перекрывают линию (18) удерживающего конденсатора через первую изолирующую пленку и перекрывают второй электрод (17b) пикселя через вторую изолирующую пленку. Электрод (9) стока транзистора (12), первый электрод (17а) пикселя, первая соединительная линия (38), соединенная с первым электродом (67х) конденсатора и вторая соединительная линия, соединенная со вторым электродом (67y) конденсатора, электрически соединены друг с другом. Часть первой соединительной линии (38) и часть второй соединительной линии (39) не перекрывают линию (18) удерживающего конденсатора. Технический результат - увеличение выхода продукции при изготовлении подложки активной матрицы. 9 н. и 22 з.п. ф-лы, 38 ил.

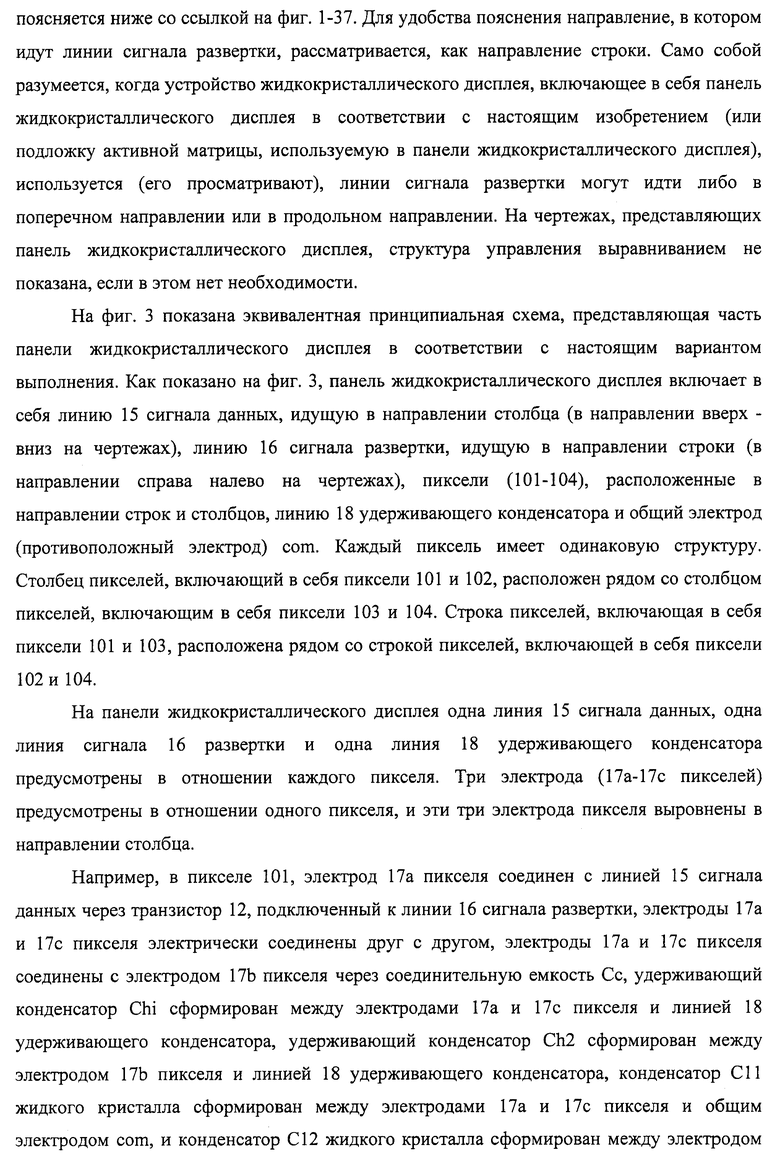

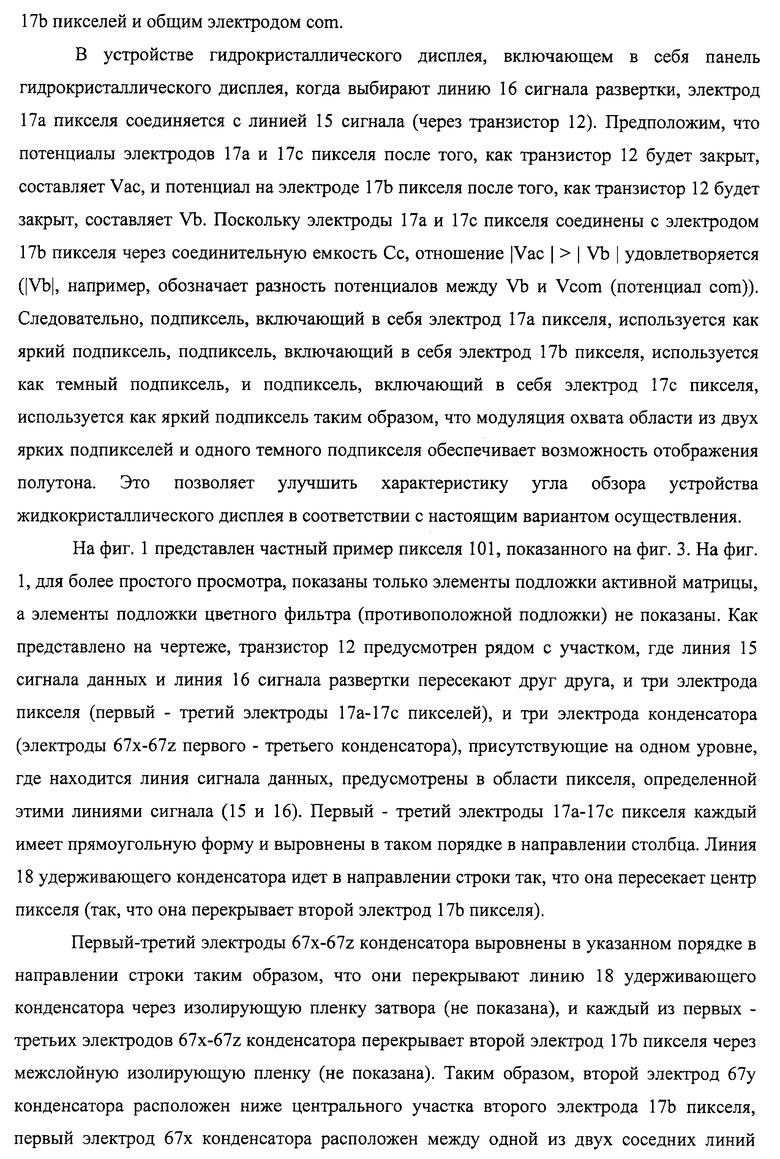

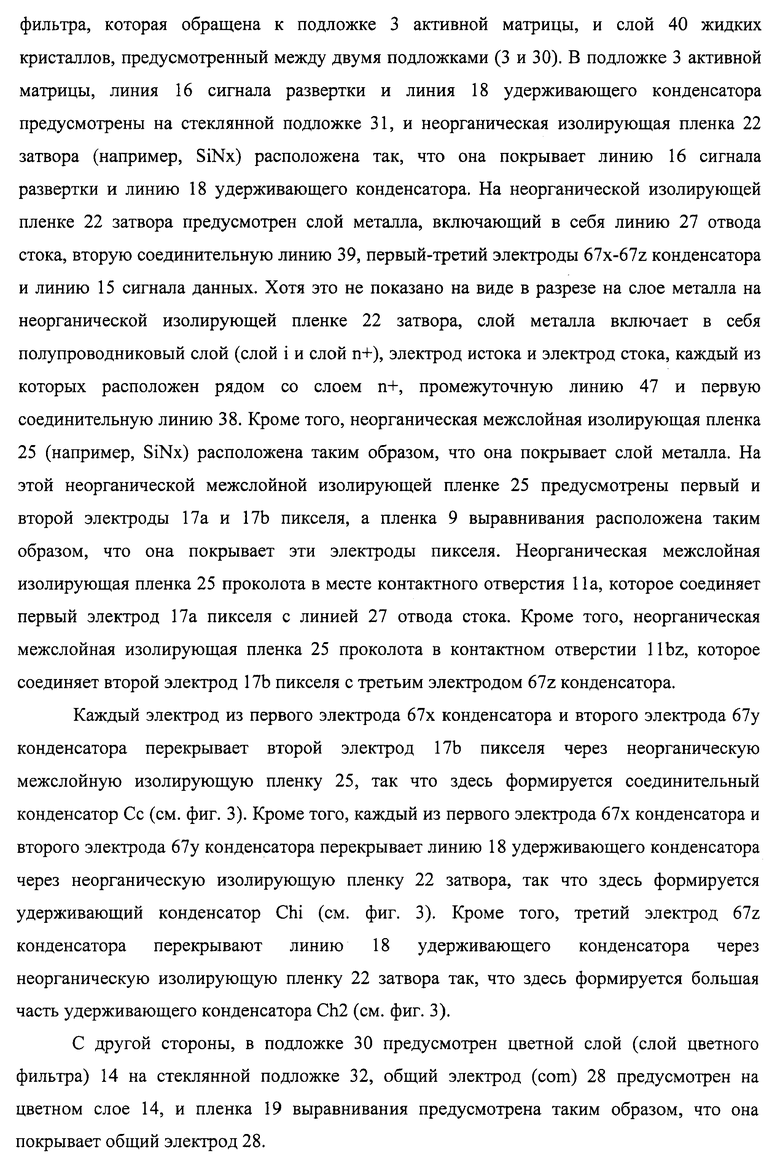

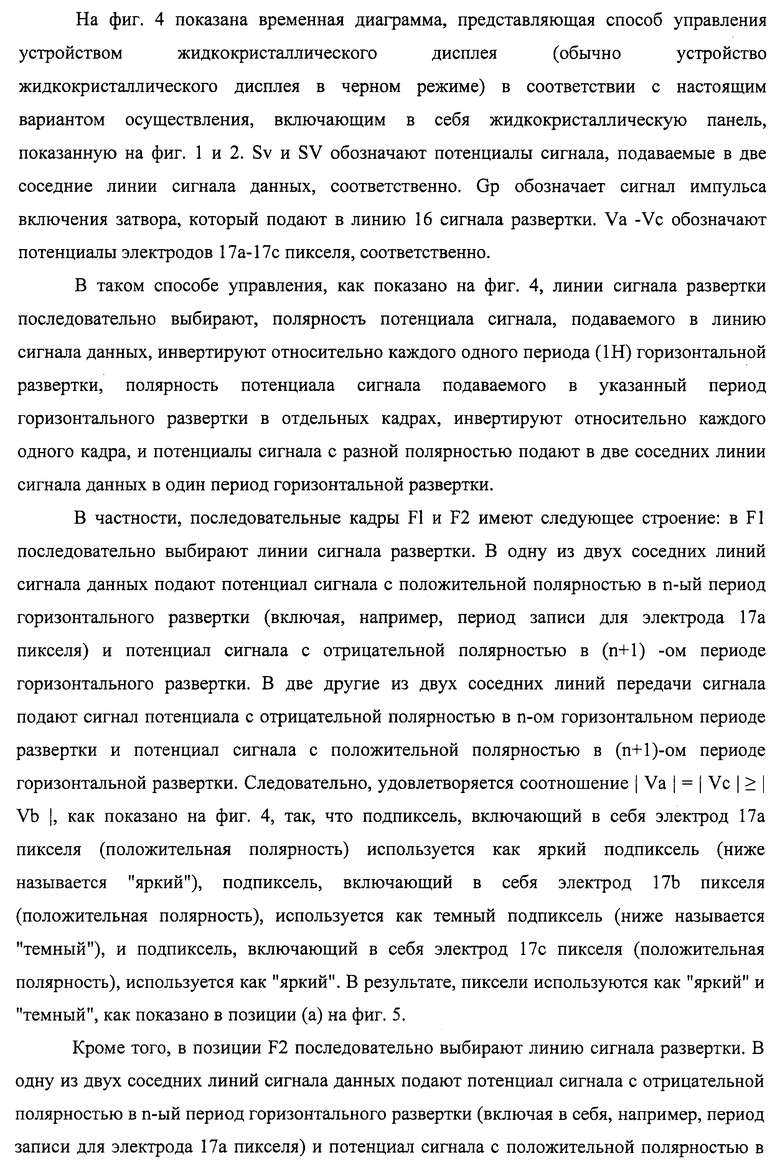

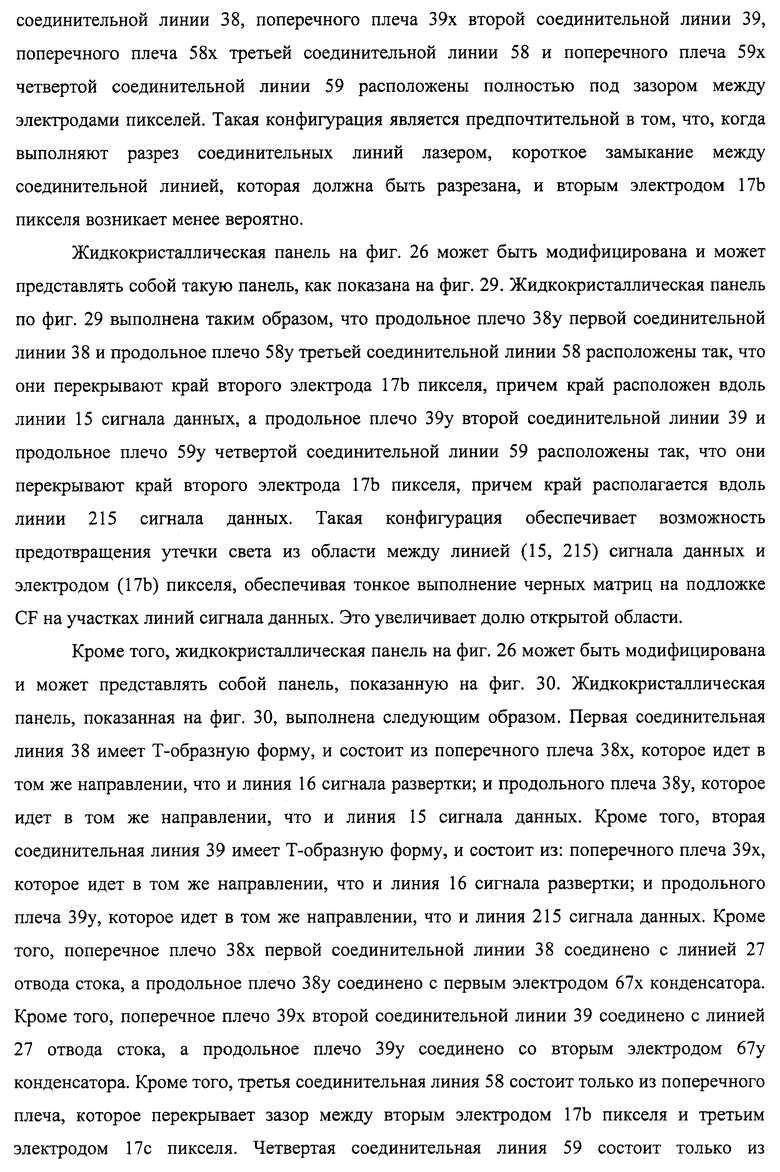

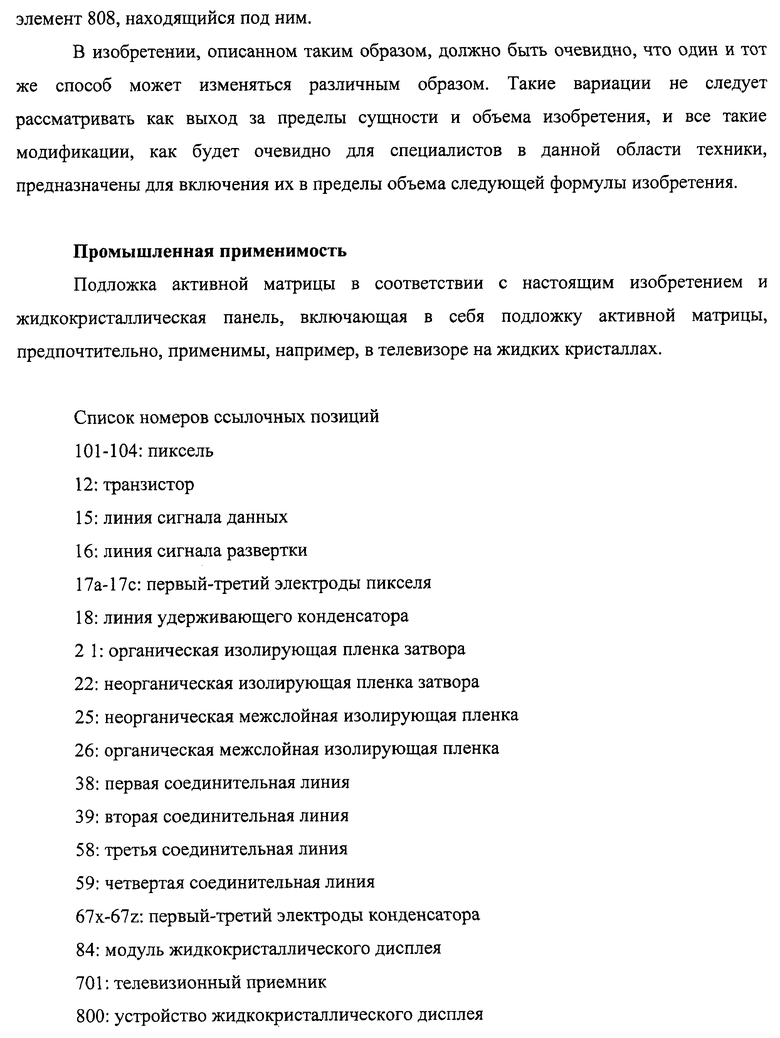

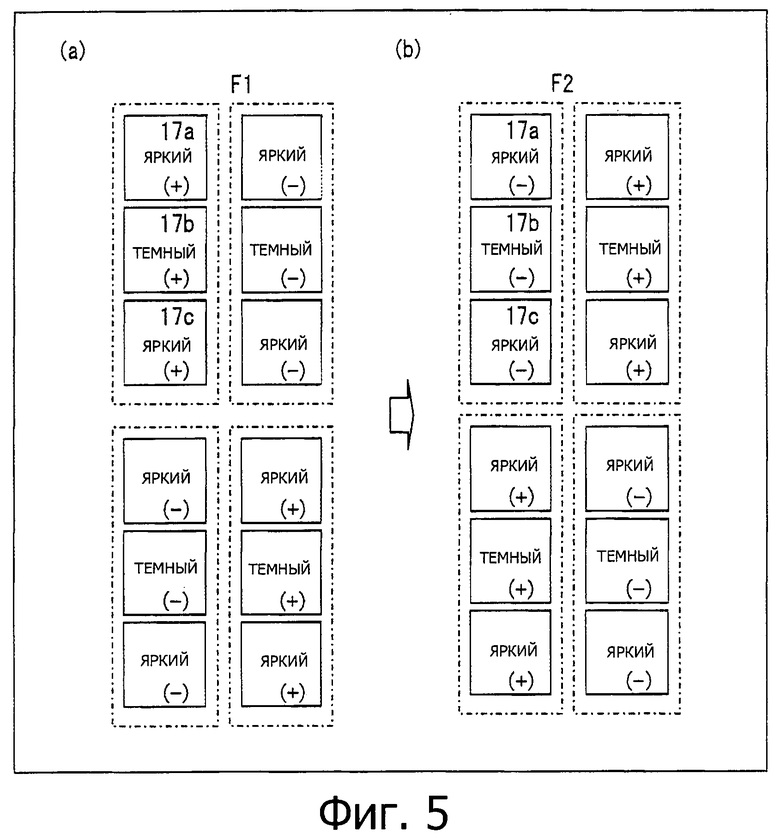

1. Подложка активной матрицы, содержащая линию сигнала развертки, вытянутую в направлении строки, линию сигнала данных, вытянутую в направлении столбца, транзистор, соединенный с линией сигнала развертки и линией сигнала данных, и линию удерживающего конденсатора, при этом

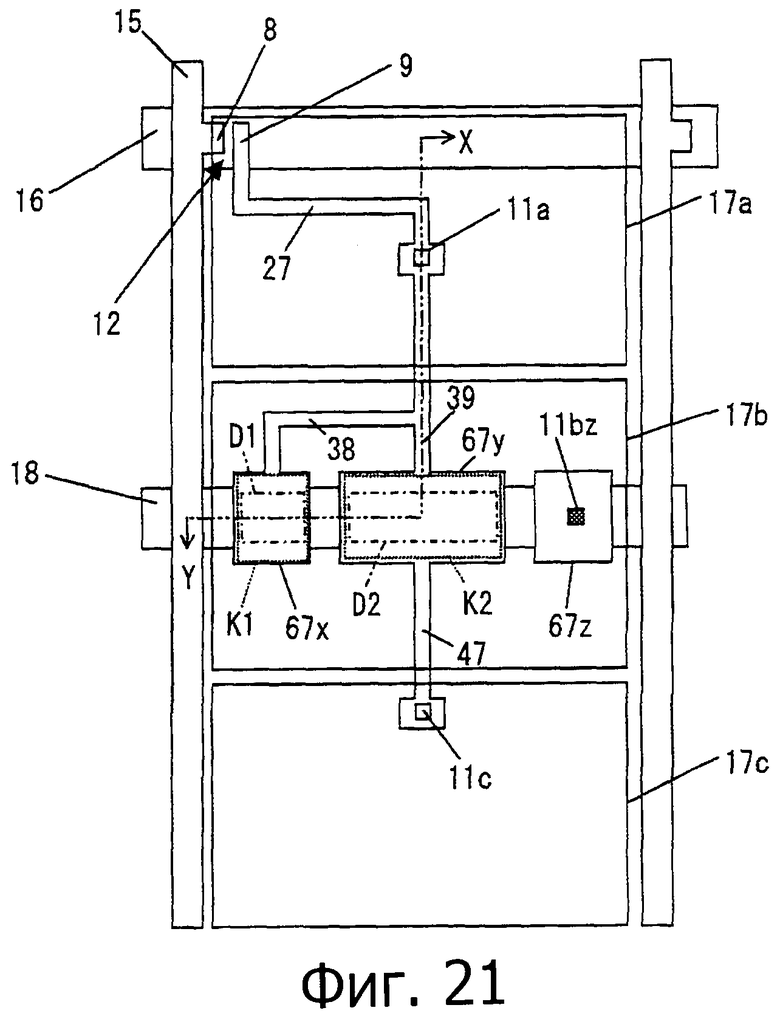

каждая область пикселя включает в себя первый электрод пикселя, второй электрод пикселя, первый электрод конденсатора, второй электрод конденсатора, первую соединительную линию и вторую соединительную линию, причем каждый электрод из первого электрода конденсатора и второго электрода конденсатора расположен в слое, в котором находится линия сигнала данных, первая соединительная линия соединена с первым электродом конденсатора, а вторая соединительная линия соединена со вторым электродом конденсатора,

первый электрод конденсатора и второй электрод конденсатора выровнены в направлении строки так, что они перекрывают линию удерживающего конденсатора через первую изолирующую пленку и перекрывают второй электрод пикселя через вторую изолирующую пленку,

один проводящий электрод транзистора, первый электрод пикселя, первая соединительная линия и вторая соединительная линия электрически соединены друг с другом, и

по меньшей мере часть первой соединительной линии и по меньшей мере часть второй соединительной линии не перекрывают линию удерживающего конденсатора.

2. Подложка активной матрицы по п.1, в которой

в каждой упомянутой области пикселя расположен третий электрод конденсатора, электрически соединенный со вторым электродом пикселя, причем третий электрод конденсатора перекрывает линию удерживающего конденсатора, и

первый электрод конденсатора, второй электрод конденсатора и третий электрод конденсатора выровнены в указанном порядке в направлении строки.

3. Подложка активной матрицы по п.2, дополнительно содержащая линию отвода, отходящую от упомянутого проводящего электрода транзистора, при этом

линия отвода соединена с первым электродом пикселя через контактное отверстие, линия отвода соединена с первой соединительной линией и со второй соединительной линией в слое, в котором расположены линия отвода, первая соединительная линия и вторая соединительная линия, а третий электрод конденсатора соединен со вторым электродом пикселя через контактное отверстие.

4. Подложка активной матрицы по любому из пп.1-3, в которой первая соединительная линия и/или вторая соединительная линия перекрывает зазор между первым электродом пикселя и вторым электродом пикселя.

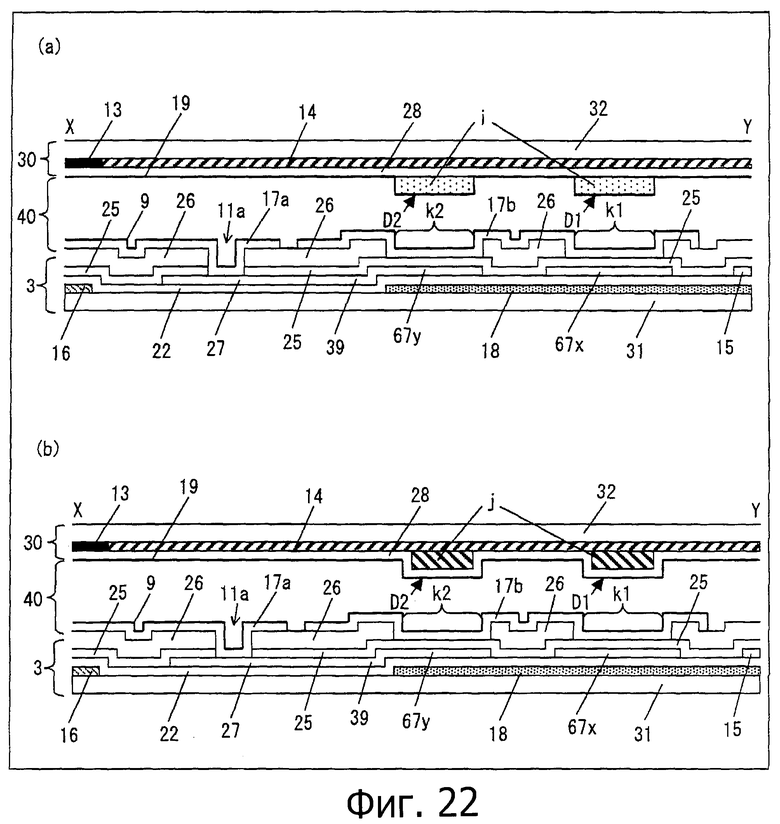

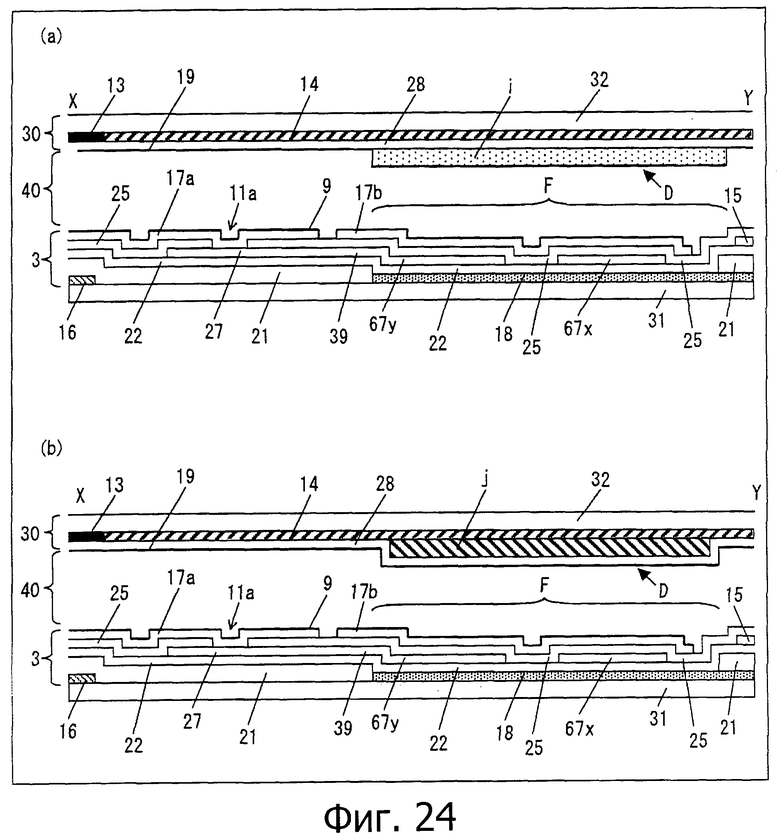

5. Подложка активной матрицы по любому из пп.1-3, в которой вторая изолирующая пленка представляет собой межслойную изолирующую пленку, которая покрывает канал транзистора.

6. Подложка активной матрицы по п.5, в которой

межслойная изолирующая пленка выполнена так, что по меньшей мере часть участка, перекрывающего первый электрод конденсатора и второй электрод пикселя, и по меньшей мере часть участка, перекрывающего второй электрод конденсатора и второй электрод пикселя, являются тонкими.

7. Подложка активной матрицы по п.6, в которой

межслойная изолирующая пленка включает в себя неорганическую межслойную изолирующую пленку и органическую межслойную изолирующую пленку, при этом

упомянутая по меньшей мере часть участка, перекрывающего первый электрод конденсатора и второй электрод пикселя, и упомянутая по меньшей мере часть участка, перекрывающего второй электрод конденсатора и второй электрод пикселя, выполнены так, что органическая межслойная изолирующая пленка утончена или органическая межслойная изолирующая пленка удалена.

8. Подложка активной матрицы по п.2, в которой первая изолирующая пленка представляет собой изолирующую пленку затвора.

9. Подложка активной матрицы по п.8, в которой изолирующая пленка затвора выполнена так, что по меньшей мере часть участка, перекрывающего линию удерживающего конденсатора и первый электрод конденсатора, по меньшей мере часть участка, перекрывающего линию удерживающего конденсатора и второй электрод конденсатора, и по меньшей мере часть участка, перекрывающего линию удерживающего конденсатора и третий электрод конденсатора, являются тонкими.

10. Подложка активной матрицы по п.9, в которой изолирующая пленка затвора включает в себя органическую изолирующую пленку затвора и неорганическую изолирующую пленку затвора, при этом

упомянутая по меньшей мере часть участка, перекрывающего линию удерживающего конденсатора и первый электрод конденсатора, упомянутая по меньшей мере часть участка, перекрывающего линию удерживающего конденсатора и второй электрод конденсатора, и упомянутая по меньшей мере часть участка, перекрывающего линию удерживающего конденсатора и третий электрод конденсатора, выполнены так, что органическая изолирующая пленка затвора утончена или органическая изолирующая пленка затвора удалена.

11. Подложка активной матрицы по п.6 или 9, в которой

первый электрод пикселя и линия сигнала развертки частично перекрывают друг друга.

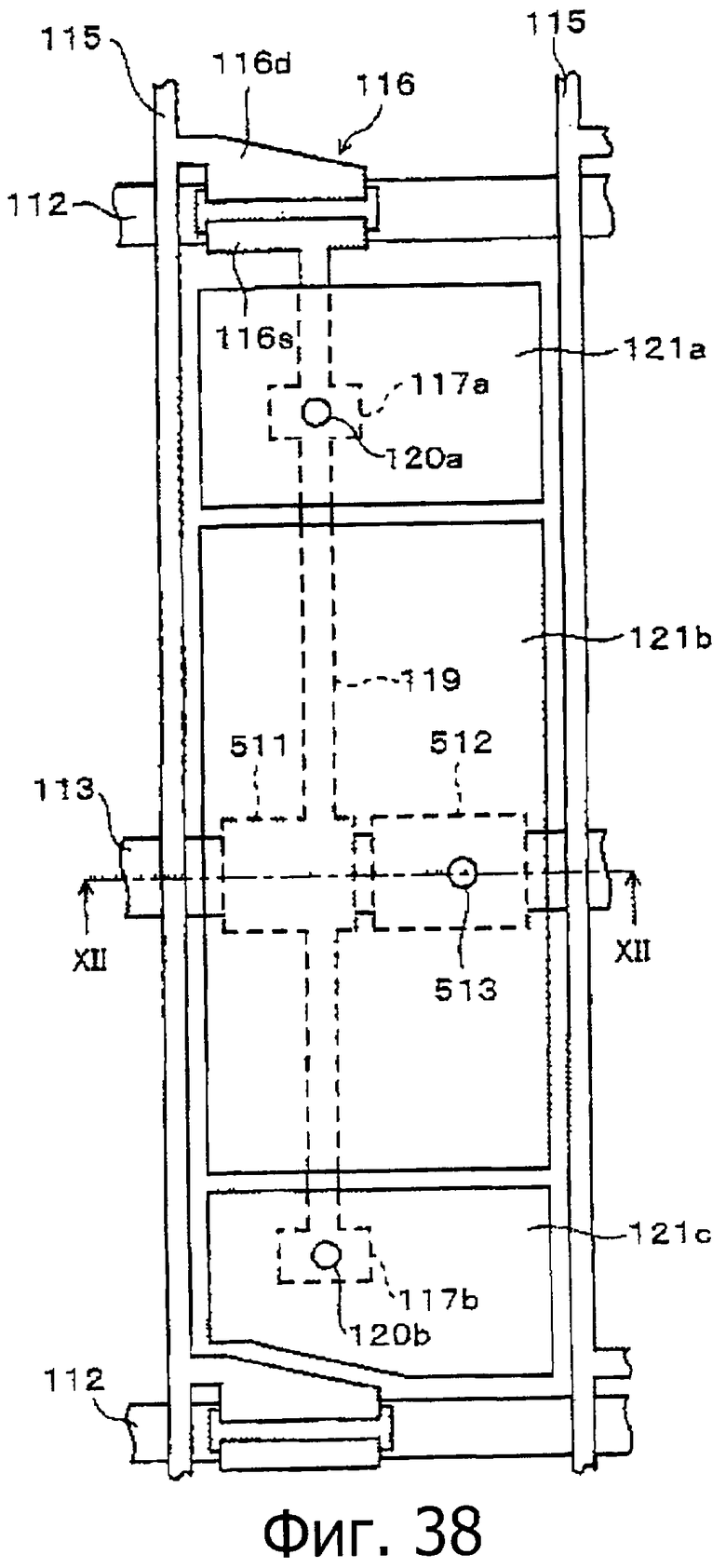

12. Подложка активной матрицы по любому из пп.1-3, дополнительно содержащая ответвление удерживающего конденсатора, причем

на виде сверху ответвление удерживающего конденсатора идет от линии удерживающего конденсатора вдоль линии сигнала данных так, чтобы перекрывать край второго электрода пикселя или проходить за пределами края.

13. Подложка активной матрицы по любому из пп.1-3, в которой зазор между первым электродом пикселя и вторым электродом пикселя служит в качестве структуры для управления выравниванием.

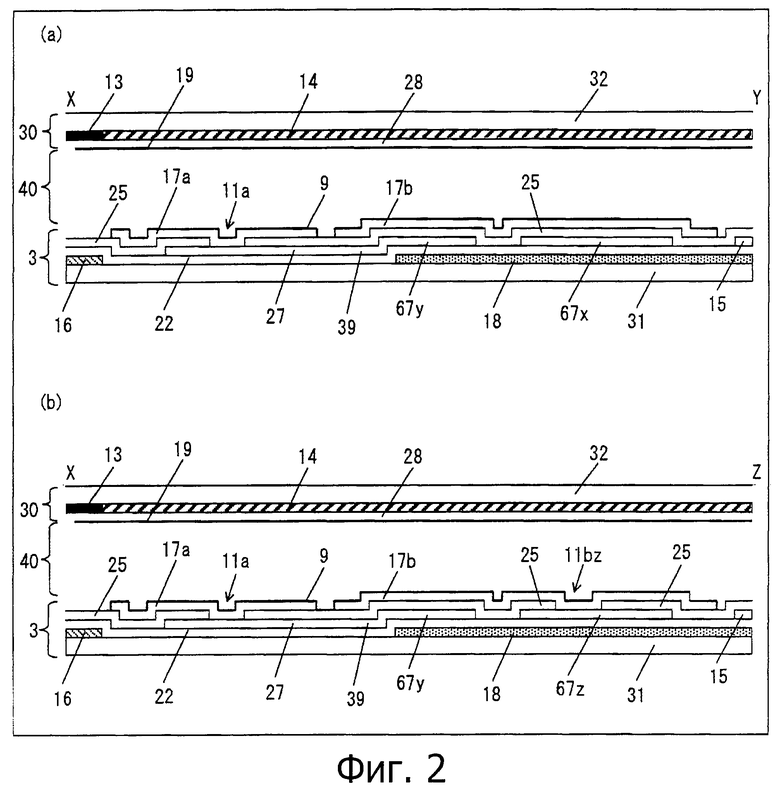

14. Подложка активной матрицы по любому из пп.1-3, в которой упомянутая каждая область пикселя включает в себя третий электрод пикселя, причем третий электрод пикселя электрически соединен с первым электродом пикселя.

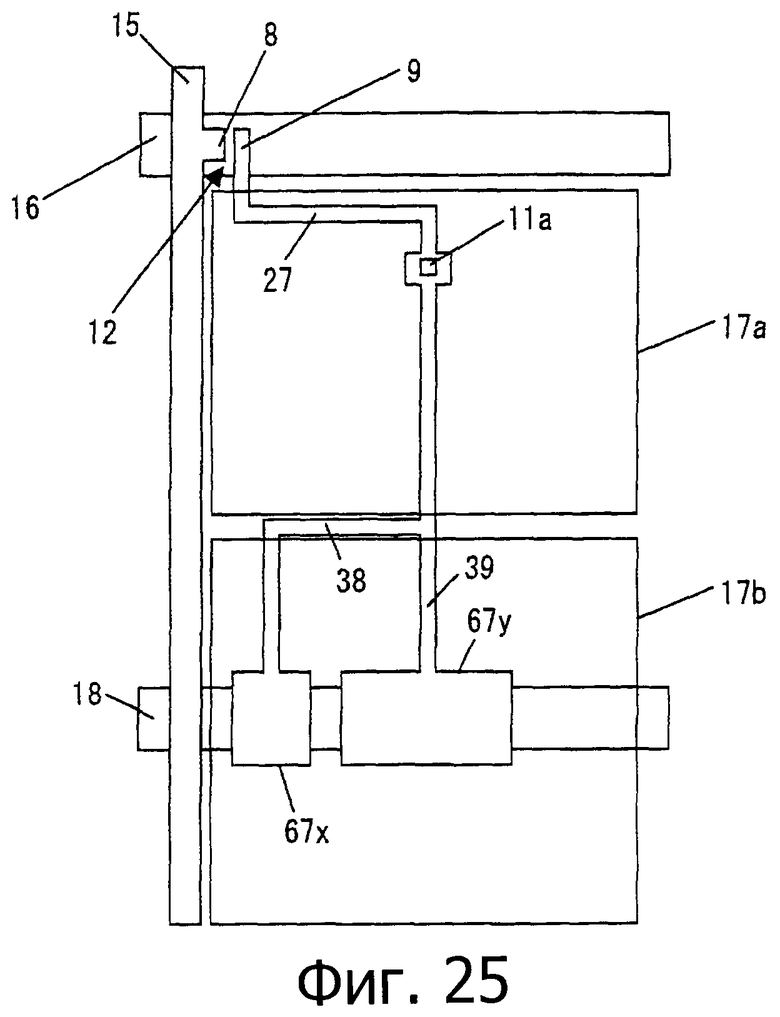

15. Подложка активной матрицы по п.14, в которой первый электрод пикселя, второй электрод пикселя и третий электрод пикселя выровнены в указанном порядке в направлении столбца.

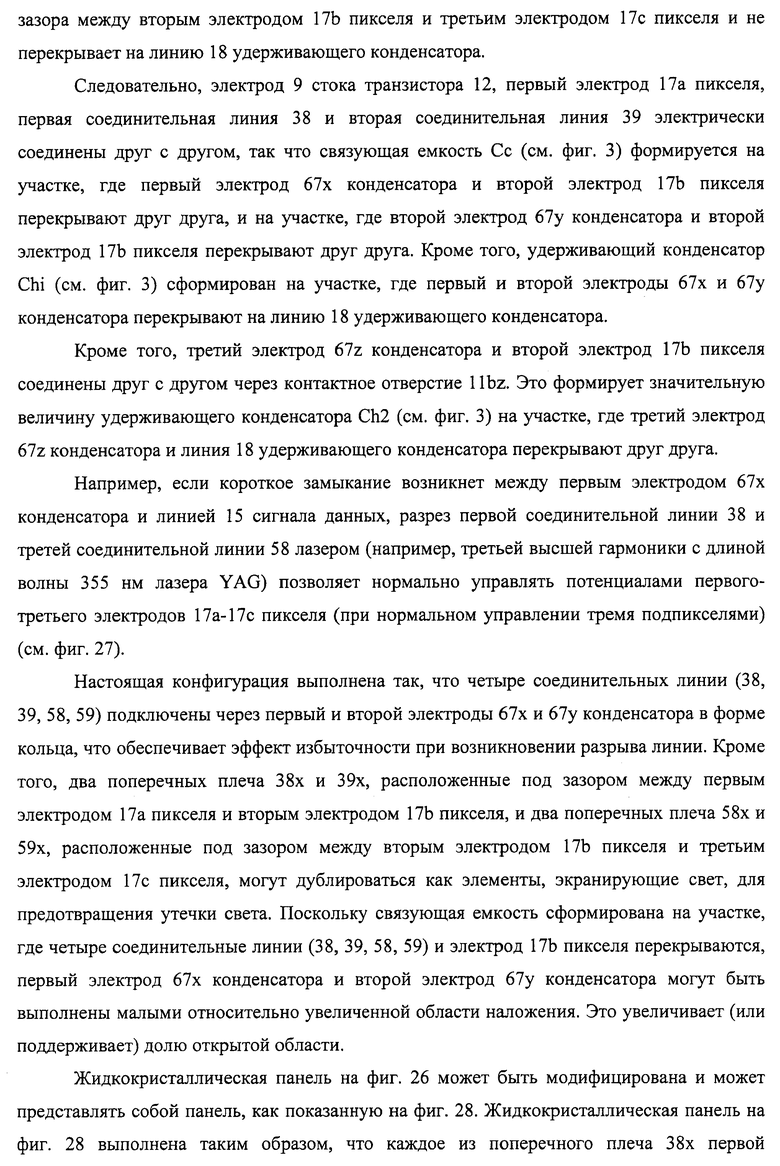

16. Подложка активной матрицы по п.1, в которой

в упомянутой каждой области пикселя расположен третий электрод конденсатора, электрически соединенный со вторым электродом пикселя, причем третий электрод конденсатора перекрывает линию удерживающего конденсатора, при этом

первый электрод конденсатора, третий электрод конденсатора и второй электрод конденсатора выровнены в указанном порядке в направлении строки.

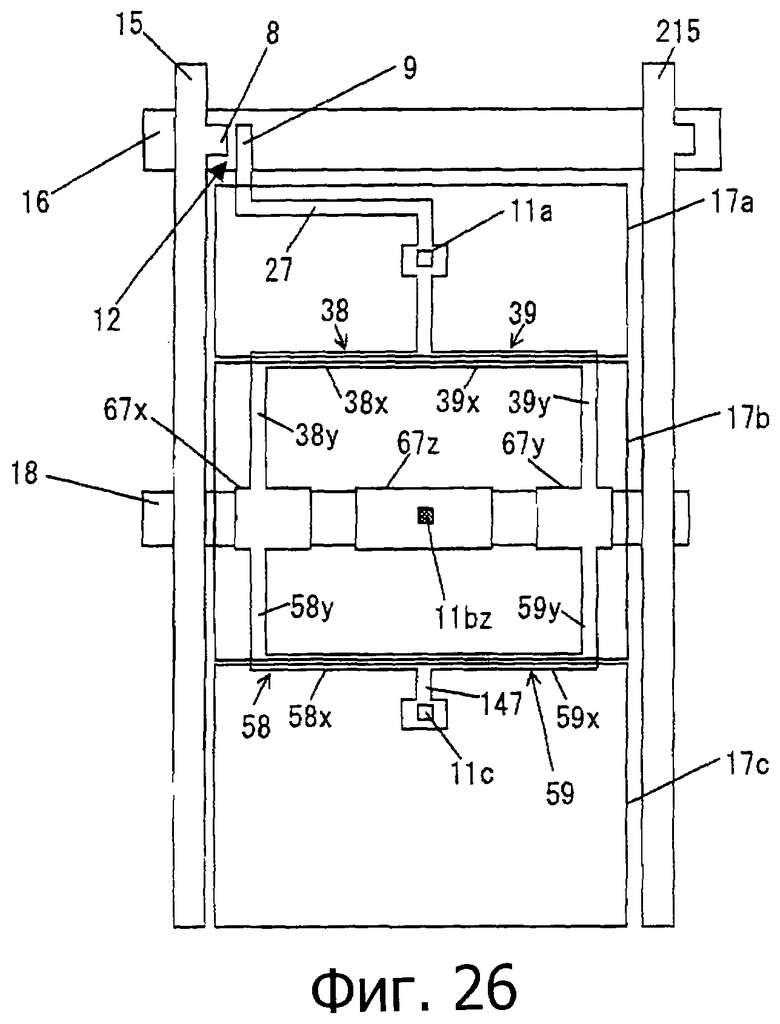

17. Подложка активной матрицы по п.16, в которой

упомянутая каждая область пикселя включает в себя третью соединительную линию, соединенную с первым электродом конденсатора, и четвертую соединительную линию, соединенную со вторым электродом конденсатора, при этом

первая соединительная линия и вторая соединительная линия соединены друг с другом, и третья соединительная линия и четвертая соединительная линия соединены друг с другом.

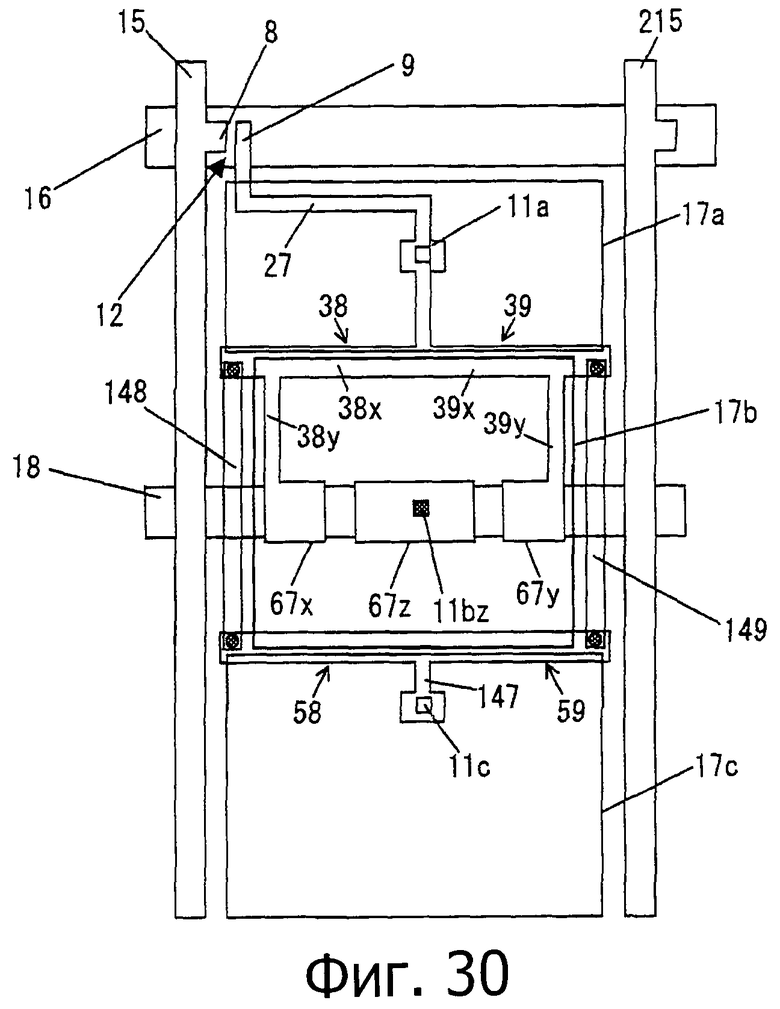

18. Подложка активной матрицы по п.17, в которой

упомянутая каждая область пикселя включает в себя третий электрод пикселя, причем первый электрод пикселя, второй электрод пикселя и третий электрод пикселя выровнены в указанном порядке в направлении столбца, при этом

третья соединительная линия и четвертая соединительная линия электрически соединены с третьим электродом пикселя, и

первая соединительная линия и вторая соединительная линия каждая частично перекрывает зазор между первым электродом пикселя и вторым электродом пикселя, а третья соединительная линия и четвертая соединительная линия каждая частично перекрывает зазор между вторым электродом пикселя и третьим электродом пикселя.

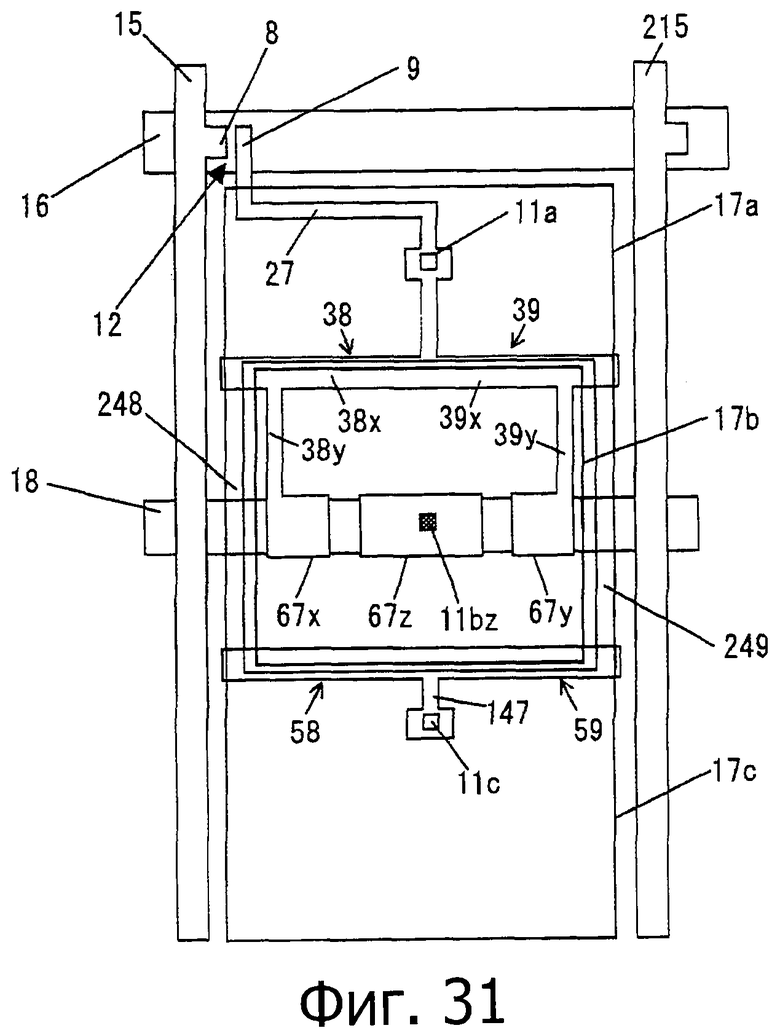

19. Подложка активной матрицы по п.17, в которой

упомянутая каждая область пикселя включает в себя третий электрод пикселя, причем первый электрод пикселя, второй электрод пикселя и третий электрод пикселя выровнены в указанном порядке в направлении столбца, при этом

третья соединительная линия и четвертая соединительная линия электрически соединены с третьим электродом пикселя, и

первая соединительная линия и третья соединительная линия каждая частично перекрывает один из двух краев второго электрода пикселя, расположенных вдоль линии сигнала данных, а вторая соединительная линия и четвертая соединительная линия каждая частично перекрывает другой из двух краев.

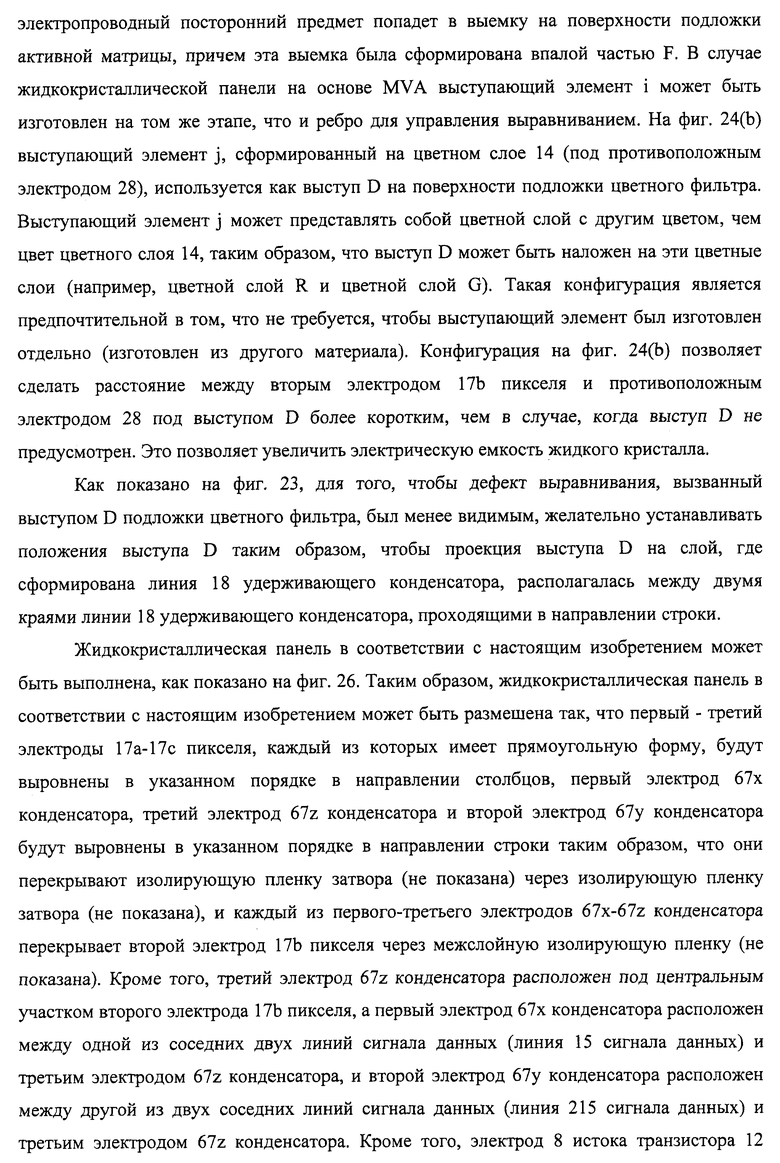

20. Жидкокристаллическая панель, содержащая подложку активной матрицы по п.6 и противоположную подложку, обращенную к подложке активной матрицы,

противоположная подложка имеет выпуклость на поверхности, причем выпуклость обращена к области подложки активной матрицы, где межслойная изолирующая пленка выполнена тонкой.

21. Жидкокристаллическая панель, содержащая подложку активной матрицы по п.9 и противоположную подложку, обращенную к подложке активной матрицы,

противоположная подложка имеет выпуклость на поверхности, причем выпуклость обращена к области подложки активной матрицы, где изолирующая пленка затвора выполнена тонкой.

22. Жидкокристаллическая панель по п.20 или 21, в которой

линия удерживающего конденсатора вытянута в направлении строки, при этом

проекция выпуклости поверхности противоположной подложки на слой, где расположена линия удерживающего конденсатора, располагается между двумя краями линии удерживающего конденсатора в направлении строки.

23. Жидкокристаллическая панель по п.20 или 21, в которой

противоположная подложка содержит ребра для управления совмещением, при этом

на противоположной подложке расположен выступающий элемент на участке, обращенном к области подложки активной матрицы, где межслойная изолирующая пленка является тонкой, причем выступающий элемент выполнен из того же материала, что и ребра.

24. Жидкокристаллическая панель по п.20 или 21, в которой

противоположная подложка представляет собой подложку цветного фильтра, при этом

на противоположной подложке расположен выступающий элемент на участке, обращенном к области подложки активной матрицы, где межслойная изолирующая пленка является тонкой, причем выступающий элемент выполнен из того же материала, что и цветной слой.

25. Жидкокристаллическая панель, содержащая подложку активной матрицы по любому из пп.1-3.

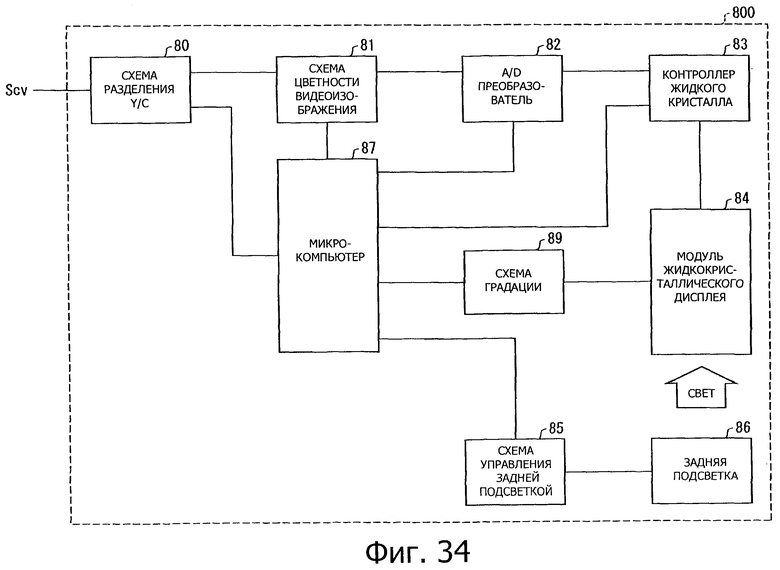

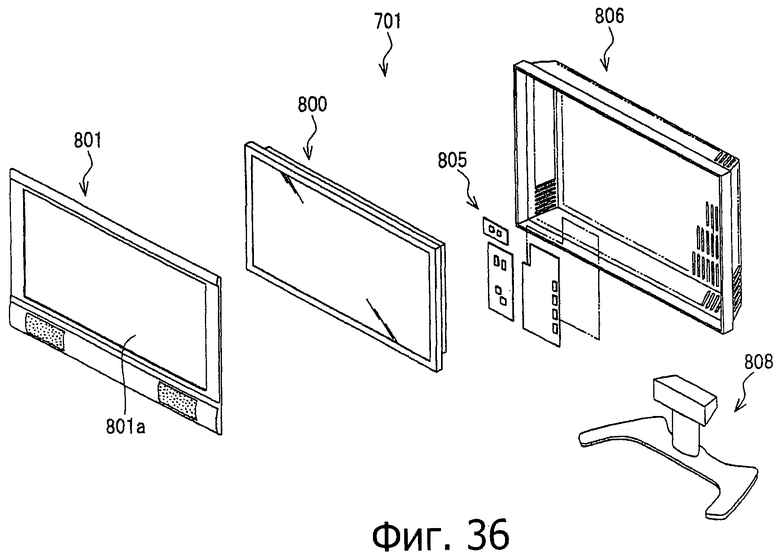

26. Жидкокристаллический модуль отображения, содержащий жидкокристаллическую панель по любому из пп.20-25 и устройство возбуждения.

27. Жидкокристаллическое устройство отображения, содержащее жидкокристаллический модуль отображения по п.26 и устройство - источник света.

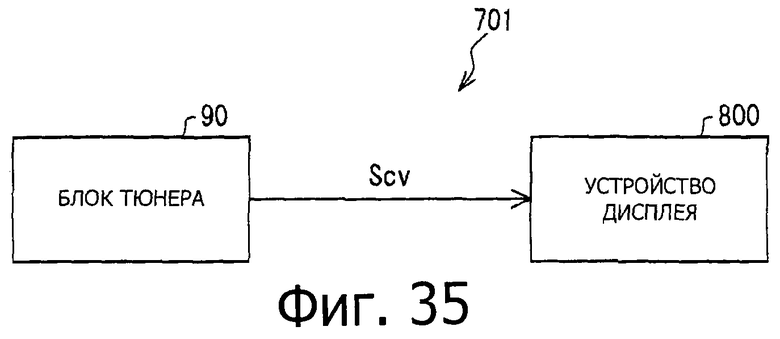

28. Телевизионный приемник, содержащий жидкокристаллическое устройство отображения по п.27 и блок тюнера для приема телевизионной широковещательной передачи.

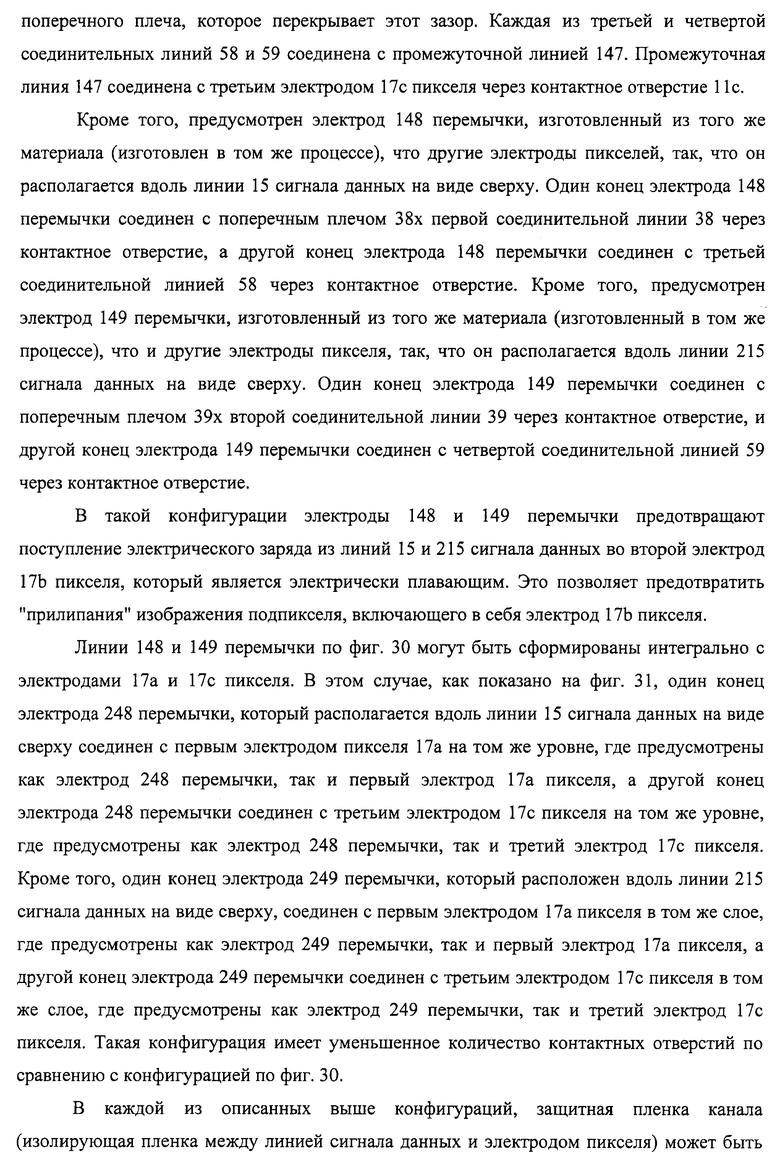

29. Способ изготовления подложки активной матрицы, включающей в себя линию сигнала развертки, вытянутую в направлении строки, линию сигнала данных, вытянутую в направлении столбца, транзистор, соединенный с линией сигнала развертки и линией сигнала данных, и линию удерживающего конденсатора, содержащий этапы, на которых:

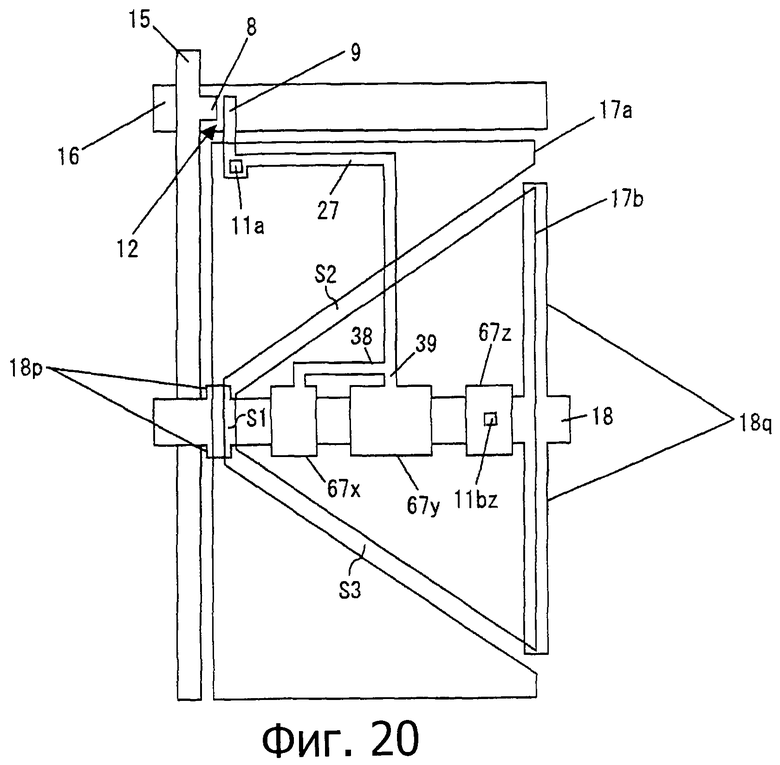

(i) формируют в каждой области пикселя первый электрод пикселя, второй электрод пикселя, первый электрод конденсатора и второй электрод конденсатора так, что первый электрод конденсатора и второй электрод конденсатора расположены в слое, в котором расположена линия сигнала данных; первый электрод конденсатора и второй электрод конденсатора выровнены в направлении строки так, чтобы перекрывать линию удерживающего конденсатора через первую изолирующую пленку и перекрывать второй электрод пикселя через вторую изолирующую пленку; один проводящий электрод транзистора, первый электрод пикселя, первая соединительная линия, соединенная с первым электродом конденсатора, и вторая соединительная линия, соединенная со вторым электродом конденсатора, электрически соединены друг с другом; и по меньшей мере часть первой соединительной линии и по меньшей мере часть второй соединительной линии не перекрывают линию удерживающего конденсатора; и

(ii) разрезают первую соединительную линию при коротком замыкании между первым электродом конденсатора и линией сигнала данных, и разрезают вторую соединительную линии при коротком замыкании между вторым электродом конденсатора и линией сигнала данных.

30. Способ по п.29, в котором

на этапе (i) формируют третий электрод конденсатора так, что третий электрод конденсатора соединен со вторым электродом пикселя через контактное отверстие, третий электрод конденсатора перекрывает линию удерживающего конденсатора, при этом первый электрод конденсатора, второй электрод конденсатора и третий электрод конденсатора выровнены в указанном порядке в направлении строки, причем

при коротком замыкании между третьим электродом конденсатора и линией сигнала данных удаляют участок второго электрода пикселя, находящийся в контактном отверстии.

31. Подложка активной матрицы, содержащая линию сигнала развертки, транзистор, соединенный с линией сигнала развертки, и линию удерживающего конденсатора, при этом

каждая область пикселя включает в себя первый электрод пикселя, второй электрод пикселя, первый электрод конденсатора, второй электрод конденсатора и соединительную линию, соединяющую первый электрод конденсатора и второй электрод конденсатора,

первый электрод конденсатора и второй электрод конденсатора каждый перекрывает линию удерживающего конденсатора через первую изолирующую пленку и перекрывает второй электрод пикселя через вторую изолирующую пленку,

один проводящий электрод транзистора электрически соединен с соединительной линией, причем упомянутый проводящий электрод или другой проводящий электрод транзистора электрически соединен с первым электродом пикселя, при этом

по меньшей мере часть соединительной линии не перекрывает линию удерживающего конденсатора.

| JP 2008112136 А, 15.05.2008 | |||

| JP 2008009058 А, 17.01.2008 | |||

| WO 2006054386 A1, 26.05.2006 | |||

| JP 2004264463 A, 24.09.2004. |

Авторы

Даты

2012-12-10—Публикация

2009-07-15—Подача