Изобретение относится к вычислительной технике и является аппаратным решением, обеспечивающим повышение производительности функционирования управляющих вычислительных систем, разрабатываемых с использованием логико-лингвистического подхода к описанию передаточных функций, а также позволяющим расширить функциональные возможности и многообразие реализуемых на его основе систем управления.

Системы обработки информации, основанные на логико-лингвистическом подходе, иначе называемые нечеткими системами, часто применяют для построения алгоритмически сложных систем принятия решений и управления. Нечеткие системы применяются для управления электроприводами, контейнерными кранами, антиблокировочными тормозными устройствами, а также для распознавания рукописных текстов, изображений, для голосового ввода данных и др.

В основу нечетких систем обработки информации положена база знаний, содержащая совокупность функций принадлежности и набор правил преобразования «вход-выход». В существующих нечетких системах база знаний загружается в память вычислительной системы на этапе ее программирования в процессе производства. Однако существует ряд задач управления, для решения которых требуется периодическое изменение закона управления, что в свою очередь требует изменения логико-лингвистического описания передаточных функций или даже самой структуры нечеткой системы управления.

Для практической реализации встраиваемых нечетких систем часто применяется их программная эмуляция на распространенных семействах микропроцессоров и микроконтроллеров (далее - процессоров) общего назначения. При этом затраты времени на обработку массивов служебных данных, описывающих нечеткие правила и функции принадлежности к входным и выходным термам, находятся в экспоненциальной зависимости от сложности нечеткой системы. Поэтому применение программных эмуляторов нечетких вычислений в ряде случаев сопряжено с проблемой недопустимо низкой для систем реального времени скорости выполнения эмуляции: частотные характеристики нечеткой системы принятия решений, реализованной программно, могут оказаться неудовлетворительными с точки зрения требований к скорости вычислений. Такой программный подход допустим только при низких требованиях к скорости принятия решений и темпу смены передаточных функций. Поэтому экономически выгодные программные эмуляторы нечетких систем на базе процессоров общего назначения оказываются технически непригодными для ряда высокоскоростных приложений и в системах принятия решений с переменной структурой.

Альтернативой программной эмуляции является аппаратная реализация нечеткой системы - аппаратный вычислитель нечетких логических функций. Он представляет собой устройство, выполняющее нечеткую обработку данных на аппаратом уровне и предназначенное для повышения производительности функционирования нечетких систем.

Одни из первых вычислительных систем со встроенной аппаратной поддержкой нечетких вычислений были созданы в AT&T Bell Labs и Togai InfraLogic в 1986-1989 гг. В настоящее время сектор средств аппаратного обеспечения нечетких вычислений неуклонно расширяется.

К нечетким вычислителям относится STFL WARP1.x фирмы STMicroelectornics, описанный в [1] - Проектирование встроенных систем на микроконтроллерах STMicroelectronics / Под ред. Харченко В.С., Орехова А.А. - Министерство образования и науки Украины, Национальный аэрокосмический университет им. Н Е. Жуковского «ХАИ», 2007. - 197 с. Он позволяет строить нечеткие вычислители с количеством правил до 256, содержащие до 16 входов разрядности 7 бит и до 16 выходов разрядности 10 бит. Этот вычислитель выполнен в 84-выводном корпусе PLCC или 100-выводном корпусе CPGA. При тактовой частоте 40 МГц он позволяет получить результат нечетких вычислений за 33 мкс для систем с 4 входами, 2 выходами и 32 правилами. Для взаимодействия с управляющим процессором используется 39-проводной интерфейс со следующими основными сигналами:

- PRST (вход) - «0»: инициализация, «1»: разрешение работы устройства;

- OFL (вход) - «1»: режим программирования памяти, «0»: режим вычислений;

- Sync (выход) - в режиме программирования внутренней памяти срез обозначает готовность нечеткого контроллера принять новое кодовое слово;

- А0-А9 (вход) - в режиме программирования: адрес ячейки внутренней памяти; в режиме вычислений не используются;

- 10-17 (вход) - в режиме программирования: кодовое слово, наносимое в ячейку; в режиме вычислений: значение очередного входа Xi;

- Fin (вход) - в режиме вычислений положительный импульс длительностью [1..2] периода Mclk отмечает начало ввода нового набора входов. С каждым новым импульсом Mclk на 10-17 должен быть новый Xi;

- NP (выход) - в режиме вычислений по окончании загрузки всех входов НК устанавливает «1»; по окончании считывания всех выходов НК устанавливаем «0» (можно снова подавать Fin);

- ЕР (выход) - «1»: выполняются вычисления: «0»: вычисления закончены;

- STB (выход) - «1»: очередной выход вычислен и должен быть считан с О0-О9

- OCNT0-OCNT3 (выход) - номер выхода Yj, доступного в данный момент на контактах О0-О9;

- О0-О9 (выход) - значение очередного выхода.

Такое количество служебных выводов требует отвлечения на организацию обмена служебной информацией существенной доли ресурсов управляющего процессора. Большинство существующих процессоров даже не обладают таким количеством выводов общего назначения и тем более таким количеством не занятых непосредственно в процессе управления выводов. Кроме того, обмен данными по внешнему интерфейсу занимает существенное время работы управляющего процессора.

К нечетким вычислителям также относится SAE81C99 фирмы Siemens. Он позволяет строить нечеткие вычислители с количеством правил до 16384, содержащие до 256 входов разрядности 8 бит и до 64 выходов разрядности 8 бит. Этот вычислитель выполнен в 44-выводном корпусе PMQFP. При тактовой частоте 20 МГц он позволяет получить результат нечетких вычислений за 36 мкс для систем с 4 входами, 1 выходом и 80 правилами.

По сравнению с ранее рассмотренным нечетким вычислителем он имеет меньшие габаритные размеры и требует меньшего количества выводов общего назначения управляющего процессора - 15 выводов - благодаря мультиплексированию сигналов на ряде выводов. Однако и это количество недопустимо велико для многих процессоров. Кроме того, сохраняется проблема низкой скорости обмена по внешнему интерфейсу, усугубляемая многофункциональностью этих выводов.

Нечеткие вычислители описываются в [2] RU №98112167 (А), G06J 3/00, G06F 7/38, опубл. 10.04.2000. Устройство для обработки нечеткой информации в [3] - RU №95104234 (A1), G06F 7/00, опубл. 27.12.1996. Способ выполнения операции нечеткой логики и процессор обработки данных, а также в [4] - RU №94029322 (А1), G06F 7/00, опубл. 10.06.1996. Устройство для обработки нечеткой информации. Все они также требуют отвлечения выводов и процессорного времени управляющего процессора на организацию обмена служебной информацией из-за необходимости ввода функций принадлежности и правил при их изменении.

К нечетким вычислителям также относится устройство, описанное в [5] RU №241742 (С2), G06N 7/02, опубл. 27.06.2010. Способ построения систем нечеткой логики и устройство для его реализации. Его особенностью являются входящие в его состав дополнительный блок большой нейронной сети и устройство ее обучения для автоматического формирования базы правил нечетного вычислителя. Системы управления на основе такого устройства требуют проведения обучения нейронной сети, что занимает длительное время, требует больших вычислительных ресурсов и является нетривиальной задачей для конкретно взятых объектов управления. В связи с этим данный подход не позволяет менять закон управления и структуру нечеткого вычислителя в темпе реального времени.

К другому типу устройств управления с аппаратной поддержкой нечетких вычислений относится микроконтроллер MC68HCS12 с процессорным ядром МС68ПС11 фирмы Motorola, описанный в [6] - Барретт С.Ф., Пак Д.Дж. Встраиваемые системы. Проектирование приложений на микроконтроллерах семейства 68НС12/HCS12 с применением языка С. - М.: Издательский дом «ДМК-пресс». 2007. - 60 с. Он содержит специальные функции нечеткой обработки данных. Особенностью этого типа нечетких вычислителей является реализация нечеткого вычислителя в виде блока на одном кристалле с управляющим процессором, что не требует организации внешнего интерфейса с нечетким вычислителем и, следовательно, использования выводов управляющего процессора. Кроме того, такой подход позволяет снизить энергопотребление и ускорить обмен данными между управляющим процессором и нечетким вычислителем благодаря совместному использованию общего адресного пространства и вместе с тем упростить протокол обмена данными. Недостатком данного микроконтроллера является совместное использование блока арифметико-логического устройства (АЛУ) нечетким вычислителем и управляющим процессором, что снижает вычислительную производительность последнего, т.к. при выполнении нечетких вычислений АЛУ будет недоступно для выполнения команд программы управляющего процессора.

Другим примером нечетких вычислителей такого типа является семейство 8-битных микроконтроллеров ST5 фирмы STMicroelectronics, также содержание на одном кристалле процессорное ядро (управляющий процессор), периферийные устройства и нечеткий вычислитель. Данный микроконтроллер с блоком нечетких вычислений выбран в качестве прототипа.

Его недостатком по вышеуказанным причинам также является совместное использование блока АЛУ нечетким вычислителем и управляющим процессором.

Кроме того, в приведенных микроконтроллерах MC68HCS12 и ST5 имеются жесткие ограничения на вид функций принадлежности. Система команд упомянутых нечетких вычислителей не ориентирована на обработку функций принадлежности произвольного вида. В одних системах возможно использование функций только треугольной или трапециевидной формы, что является существенным ограничением и не позволяет реализовать целый класс нечетких систем управления - нечетких систем с нелинейными функциями принадлежности, значимых с практической точки зрения. В других системах наложено существенное ограничение на разрядность функций принадлежности.

Таким образом, существующие нечеткие вычислители можно разделить на две категории:

1. Нечеткие вычислители, выполненные в виде отдельного модуля или микросхемы и предназначенные для работы в кооперации с основным контроллером (в этом случае в англоязычной литературе для их обозначения применяется термин Fuzzy Coprocessor - нечеткий сопроцессор).

2. Системы с нечетким вычислителем, т.е. микроконтроллеры, содержащие особое периферийное устройство, связанное с АЛУ - блок нечеткого вычислителя, и представляющие собой законченную аппаратную платформу для системы управления (для их обозначения применяется термин ICU: Intelligent Controller Unit - интеллектуальный контроллер).

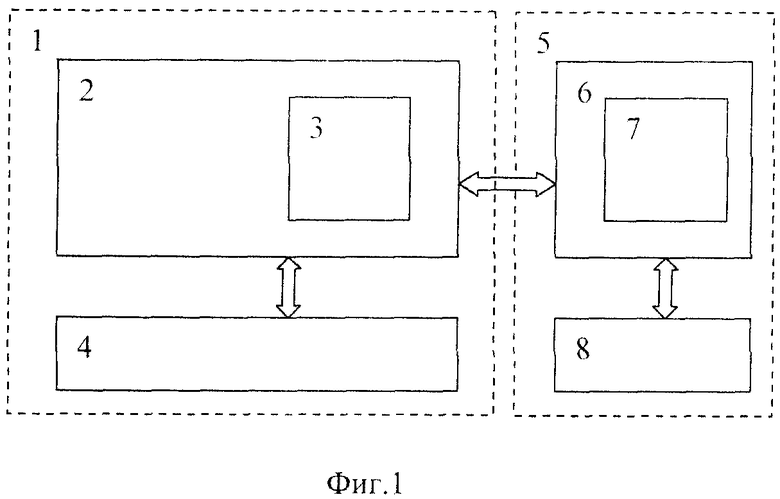

Структура системы с нечетким вычислителем первого типа представлена на фигуре 1. В данной структуре на кристалле 1 располагается процессор 2 с АЛУ 3 и памятью 4, к которым с помощью внешнего интерфейса подключается нечеткий вычислитель 6 с собственным АЛУ 7 и памятью 8, выполненный на отдельном кристалле 5. Недостатком описанной структуры является необходимость выделения выводов управляющего процессора для организации интерфейса и низкая скорость обмена данными по этому интерфейсу между управляющим процессором и нечетким вычислителем, а также увеличенные массогабаритные параметры.

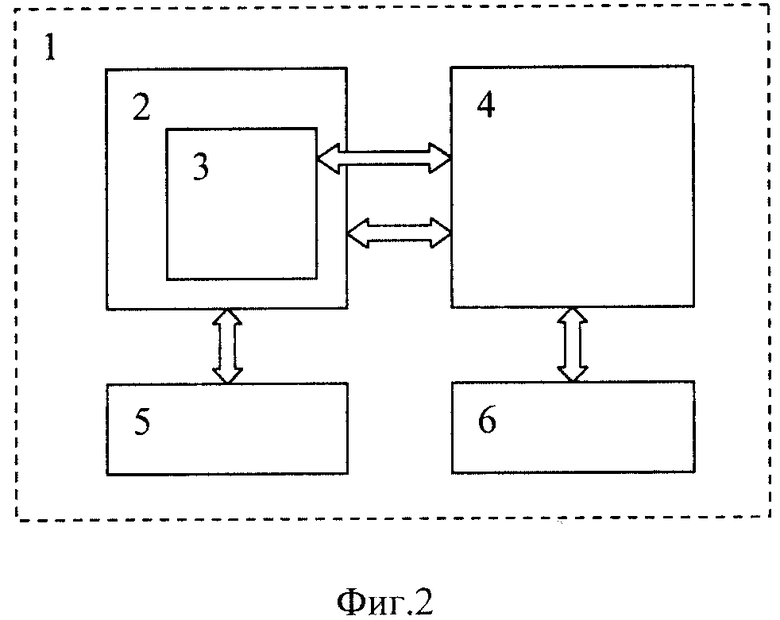

Структура системы с нечетким вычислителем второго типа представлена на фигуре 2. В данной структуре управляющий процессор 2, АЛУ 3 и блок нечетких вычислений 4, а также память 5 процессора и память 6 нечеткого вычислителя располагаются на едином кристалле 1. Недостатком описанной структуры является совместное использование блока АЛУ 3 как управляющим процессором 2, так и блоком нечетких вычислений 4, что приводит к невозможности параллельного выполнения операций управляющим процессором 2 и блоком нечетких вычислений 4.

Технической задачей, на решение которой направлено заявляемое изобретение, является разработка микроконтроллера со встроенным блоком нечеткого вычислителя, позволяющего существенно расширить многообразие реализуемых систем управления с нечеткой обработкой информации и обеспечивающего высокую скорость нечеткой обработки данных, выполняемой параллельно исполнению программы управляющего процессора и не задействующей его ресурсов.

Сущность изобретения поясняется фигурой 3 и заключается в том, что на едином кристалле 1 размещаются управляющий процессор 2 с АЛУ 3 и блок нечетких вычислений 4 с отдельным АЛУ 5, которые имеют доступ к общему адресному пространству памяти 6.

Преимущество заявляемого изобретения заключается в том, что блок нечетких вычислений содержит собственное АЛУ и не использует АЛУ управляющего процессора, что позволяет выполнять все операции по нечеткой обработке автономно и параллельно с обработкой команд и данных управляющим процессором.

Использование отдельного АЛУ блока нечетких вычислений позволяет обрабатывать функции принадлежности произвольного вида, задаваемые табличным способом, что расширяет многообразие реализуемых нечетких систем управления по сравнению с прототипом.

Доступ управляющего процессора и блока нечетких вычислений к общей памяти позволяет обеспечить высокую скорость обмена данными между ними. Это также упрощает задание функций принадлежности произвольного вида табличным способом. Кроме того, доступ к общей памяти позволяет осуществлять оперативное переключение на другую активную структуру (или базу знаний) в темпе реального времени.

Кроме того, заявляемое изобретение сохраняет все положительные свойства выбранного прототипа: позволяет создавать, аппаратные платформы нечетких систем с малыми массогабаритными параметрами и не требует задействования выводов управляющего процессора для организации служебного интерфейса.

Проектирование устройства на основе заявляемого изобретения включает следующие этапы:

- описание структур нечетких вычислителей (задание количества и разрядности входов и выходов);

- подготовку баз знаний нечетких вычислителей (описание функций принадлежности и правил);

- задание графа связей нечетких вычислителей между собой (распределение памяти для входов, выходов, функций принадлежности и правил).

Отличие от прототипа заключается в наличии этапа задания графа связей нечетких вычислителей между собой. Реализация задаваемых таким образом переходов обеспечивается возможностью оперативного переключения активной структуры в темпе реального времени. Кроме того, в отличие от прототипа, этап подготовки базы знаний допускает возможность задания функций принадлежности произвольного вида.

Функционирование заявляемого изобретения состоит из следующих этапов:

- загрузка структуры очередного нечеткого вычислителя или переключение на предварительно загруженную структуру;

- загрузка базы знаний очередного нечеткого вычислителя или переключение на предварительно загруженную базу знаний;

- ввод исходных данных для обработки блоком нечетких вычислений (запись данных в соответствующем формате в выделенные входные регистры);

- выполнение нечетких вычислений (фаззификация, нечеткий логический вывод и дефаззификация);

- считывание результата (считывание значений из выделенных выходных регистров).

Отличие от прототипа заключается в наличии возможности переключения активной структуры и базы знаний в темпе реального времени на первых двух этапах функционирования изобретения. Кроме того, на этапе осуществления нечетких логических вычислений, в отличие от прототипа, не используются ресурсы (блок АЛУ) управляющего процессора.

Примененные решения обеспечивают новые функциональные возможности заявляемого изобретения по сравнению с прототипом, а также позволяют осуществлять одновременную работу управляющего процессора и блока нечеткого вычислителя с изменяемой в процессе функционирования передаточной функцией.

Из рассмотренного следует, что заявляемое изобретение технически осуществимо и обеспечивает достижение технического результата, заключающегося в расширении многообразия воспроизводимых с его помощью нечетких систем управления и увеличении скорости нечетких вычислений при сохранении массогабаритных параметров на уровне выбранного прототипа.

Источники информации

1. Проектирование встроенных систем на микроконтроллерах STMicroelectronics / Под ред. Харченко B.C., Орехова А.А. - Министерство образования и науки Украины, Национальный аэрокосмический университет им. Н.Е. Жуковского «ХАИ», 2007. - 197 с.

2. RU №98112167 (A), G06J 7/38, G06F 7/38, опубл. 10.04.2000. Устройство для обработки нечеткой информации.

3. RU №95104234 (A1), G06F 7/00, опубл. 27.12.1996. Способ выполнения операции нечеткой логики и процессор обработки данных.

4. RU №94029322 (A1), G06F 7/00, опубл. 10.06.1996. Устройство для обработки нечеткой информации.

5. RU №241742 (С2), G06N 7/02, опубл. 27.06.2010. Способ построения систем нечеткой логики и устройство для его реализации.

6. Барретт С.Ф., Пак Д.Дж. Встраиваемые системы. Проектирование приложений на микроконтроллерах семейства 68HC12 / HCS12 с применением языка С. - М.: Издательский дом «ДМК-пресс». 2007. - 60 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| СТЕНД ДЛЯ ИЗУЧЕНИЯ МИКРОКОНТРОЛЛЕРНЫХ СИСТЕМ УПРАВЛЕНИЯ | 2008 |

|

RU2402822C2 |

| СУПЕРКОМПЬЮТЕРНЫЙ КОМПЛЕКС ДЛЯ РАЗРАБОТКИ НАНОСИСТЕМ | 2009 |

|

RU2432606C2 |

| СПОСОБ ПРОЕКТИРОВАНИЯ МНОГОРЕЖИМНОЙ ИНТЕЛЛЕКТУАЛЬНОЙ СИСТЕМЫ УПРАВЛЕНИЯ РАСПРЕДЕЛЕННОЙ СРЕДОЙ МЯГКИХ ВЫЧИСЛЕНИЙ | 2014 |

|

RU2596992C2 |

| ВЕРОЯТНОСТНЫЙ АВТОМАТ | 2021 |

|

RU2777531C1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА ПЕРСОНИФИЦИРОВАННОЙ МЕДИЦИНЫ | 2014 |

|

RU2581947C2 |

| ГИБРИДНЫЙ ПОТОКОВЫЙ МИКРОПРОЦЕССОР | 2014 |

|

RU2584470C2 |

| ИНТЕЛЛЕКТУАЛЬНАЯ ГРИД-СИСТЕМА ДЛЯ ВЫСОКОПРОИЗВОДИТЕЛЬНОЙ ОБРАБОТКИ ДАННЫХ | 2009 |

|

RU2411574C2 |

| Метод построения процессоров для вывода в сверточных нейронных сетях, основанный на потоковых вычислениях | 2020 |

|

RU2732201C1 |

| УСТРОЙСТВО МОНИТОРИНГА ИНФОРМАЦИОННОГО ТРАФИКА | 2021 |

|

RU2768543C1 |

| УСТРОЙСТВО ДЛЯ ПАРАМЕТРИЧЕСКОЙ ОЦЕНКИ ЗАКОНА РАСПРЕДЕЛЕНИЯ ПОТОКОВ СООБЩЕНИЙ | 2004 |

|

RU2281548C1 |

Изобретение относится к вычислительной технике и направлено на повышение производительности функционирования управляющих вычислительных систем, разрабатываемых с использованием логико-лингвистического подхода к описанию передаточных функций, и на расширение функциональных возможностей и многообразия реализуемых систем управления. Технический результат - повышение производительности функционирования данных вычислительных систем. Указанный результат достигается за счет включения отдельного арифметико-логического устройства в состав блока нечетких вычислений, расположенного на одном кристалле с управляющим процессором, что позволяет выполнять все операции по нечеткой обработке автономно и параллельно с обработкой команд и данных управляющим процессором. Расширение возможностей и многообразия реализуемых систем управления обеспечивается за счет возможности использования функций принадлежности произвольного вида, задаваемых табличным способом, и смены базы знаний в темпе реального времени благодаря доступу к общему адресному пространству памяти. 1 з.п. ф-лы, 3 ил.

1. Микроконтроллер, содержащий на одном кристалле процессорное ядро с арифметико-логическим устройством, блок нечетких вычислений и периферийные устройства, отличающийся тем, что блок нечетких вычислений содержит отдельное арифметико-логическое устройство для обеспечения возможности выполнения нечетких вычислений параллельно выполнению операций процессорным ядром и имеет общее с ним адресное пространство памяти, обеспечивающее возможность переключения баз знаний блока нечетких вычислений в темпе реального времени.

2. Микроконтроллер по п.1, отличающийся тем, что арифметико-логическое устройство блока нечетких вычислений обеспечивает возможность обработки функций принадлежности произвольного вида, задаваемых табличным способом.

| СПОСОБ ПОСТРОЕНИЯ СИСТЕМ НЕЧЕТКОЙ ЛОГИКИ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2008 |

|

RU2417442C2 |

| US 6766310 В1, 20.07.2004 | |||

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

Авторы

Даты

2013-03-10—Публикация

2011-06-17—Подача