Предлагаемое изобретение относится к области радиотехники и связи и может быть использовано в радиоприемных устройствах, фазовых детекторах и модуляторах, а также в системах умножения частоты или в качестве усилителя, коэффициент передачи по напряжению которого со входов канала «X» зависит от уровня сигнала управления канала «Y». Управляемый усилитель и аналоговый смеситель сигналов (УУ) являются базовыми узлами систем приема и обработки сигналов ВЧ и СВЧ-диапазонов.

В современной микроэлектронике широкое применение получили дифференциальные каскады (ДК) на составных транзисторах [1-13]. Их коэффициент усиления по напряжению зависит от величины статического тока общей эмиттерной цепи ДК (Iy=I0) и, следовательно, такие ДК являются (при электронном изменении величины тока Iy=I0) управляемыми усилителями (УУ).

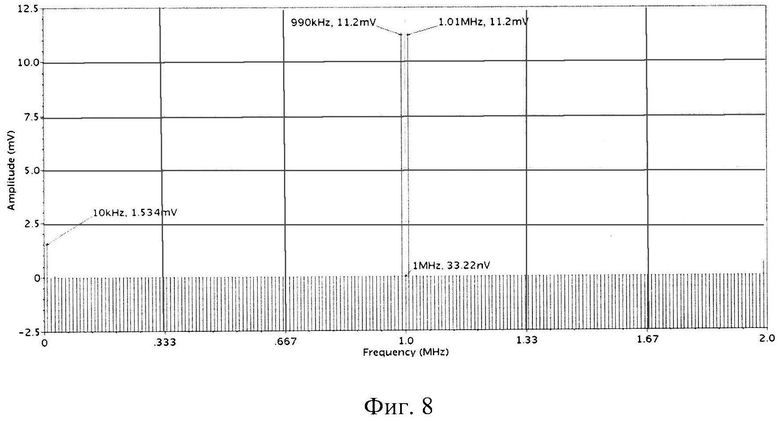

Ближайшим прототипом заявляемого устройства, архитектура которого присутствует также и в других патентах и монографиях [1-13], является управляемый усилитель на основе так называемого каскада Дарлингтона фиг.1, представленный в патентной заявке US 2009/058466, содержащий первый 1 и второй 2 источники противофазных входных напряжений, связанных с соответствующими базами первого 3 и второго 4 входных транзисторов, эмиттер первого 3 входного транзистора через первый 5 токостабилизирующий двухполюсник подключен к первому 6 источнику питания, эмиттер второго 4 входного транзистора через второй 7 токостабилизирующий двухполюсник связан с первым 6 источником питания, третий 8 входной транзистор, эмиттер которого связан с эмиттером четвертого 9 входного транзистора и через третий 10 токостабилизирующий двухполюсник соединен с первым 6 источником питания, дифференциальную цепь нагрузки 11, согласованную со вторым 12 источником питания и связанную с первым 13 и вторым 14 выходами устройства, причем эмиттер первого 3 входного транзистора соединен с базой третьего 8 входного транзистора, эмиттер второго 4 входного транзистора соединен с базой четвертого 9 входного транзистора, коллектор третьего 8 входного транзистора соединен по переменному току с коллектором второго 4 входного транзистора и связан со вторым 14 выходом устройства, коллектор четвертого 9 входного транзистора соединен по переменного току с коллектором первого 3 входного транзистора и связан с первым 13 выходом устройства.

Существенный недостаток известного устройства состоит в том, что при электронном управлении величиной коэффициента усиления (Ку) в известном УУ фаза выходного напряжения в рабочем диапазоне частот дифференциального каскада (ДК) не изменяется на 180°. Как следствие, это не позволяет использовать известный ДК в структуре ряда устройств радиотехники, например, в качестве смесителя аналоговых сигналов, фазовых детекторов и т.п.

Основная задача предлагаемого изобретения состоит в получении на выходе ДК не только амплитудных изменений выходного сигнала под действием управляющего напряжения канала «Y», но и его фазы. Как следствие, это позволяет создавать на основе предлагаемого устройства смесители аналоговых сигналов с хорошим подавлением основной гармоники.

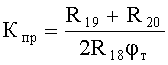

Поставленная задача решается тем, что в УУ фиг.1, содержащем первый 1 и второй 2 источники противофазных входных напряжений, связанных с соответствующими базами первого 3 и второго 4 входных транзисторов, эмиттер первого 3 входного транзистора через первый 5 токостабилизирующий двухполюсник подключен к первому 6 источнику питания, эмиттер второго 4 входного транзистора через второй 7 токостабилизирующий двухполюсник связан с первым 6 источником питания, третий 8 входной транзистор, эмиттер которого связан с эмиттером четвертого 9 входного транзистора и через третий 10 токостабилизирующий двухполюсник соединен с первым 6 источником питания, дифференциальную цепь нагрузки 11, согласованную со вторым 12 источником питания и связанную с первым 13 и вторым 14 выходами устройства, причем эмиттер первого 3 входного транзистора соединен с базой третьего 8 входного транзистора, эмиттер второго 4 входного транзистора соединен с базой четвертого 9 входного транзистора, коллектор третьего 8 входного транзистора соединен по переменному току с коллектором второго 4 входного транзистора и связан со вторым 14 выходом устройства, коллектор четвертого 9 входного транзистора соединен по переменного току с коллектором первого 3 входного транзистора и связан с первым 13 выходом устройства, предусмотрены новые элементы и связи - источник управляющего напряжения 15 связан по переменному току с объединенными эмиттерами третьего 8 и четвертого 9 входных транзисторов, причем между эмиттером первого 3 и второго 4 входных транзисторов включен дополнительный резистор 16.

На чертеже фиг.1 показана схема УУ-прототипа, а на чертеже фиг.2 - схема заявляемого УУ в соответствии с п.1 и п.2 формулы изобретения.

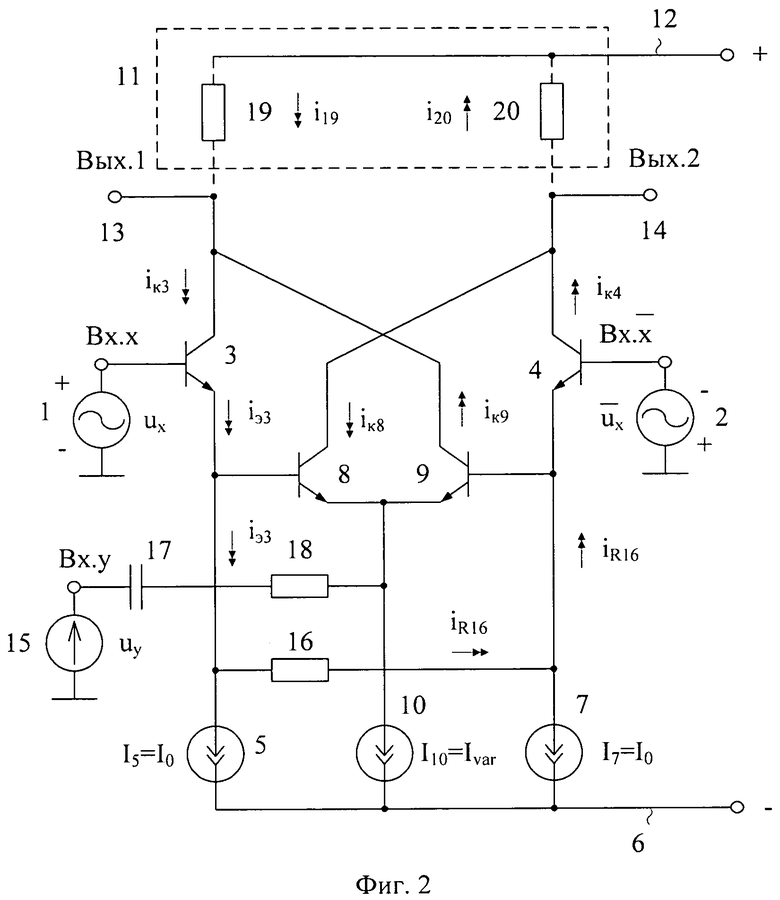

На чертеже фиг.3 показан пример применения заявляемого УУ для случая, когда источник управляющего напряжения 15 канала «Y» связан с объединенными эмиттерами третьего 8 и четвертого 9 входных транзисторов через дополнительный повторитель напряжения на транзисторах 21, 22 и дополнительный резистор 25. Данное схемотехническое решение, соответствующее п.1 формулы изобретения, иллюстрирует другие модификации заявляемого устройства. В частности, выполнение транзистора 22 в схеме фиг.3 на основе сдвоенного биполярного транзистора и подключение соответствующих коллекторов сдвоенного биполярного транзистора 22 к выходам 14 и 15 устройства способствует дальнейшему повышению уровня подавления основной гармоники смесителя фиг.3.

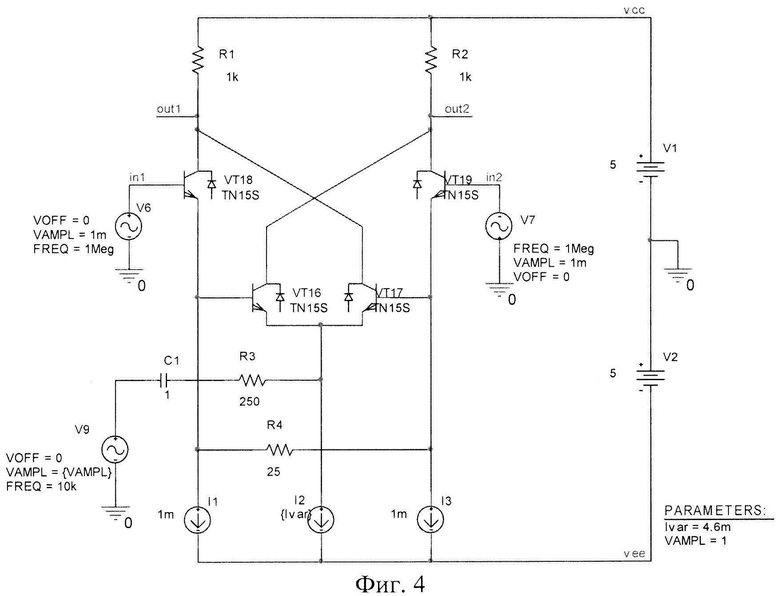

На чертеже фиг.4 представлена схема заявляемого УУ фиг.2 в среде PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

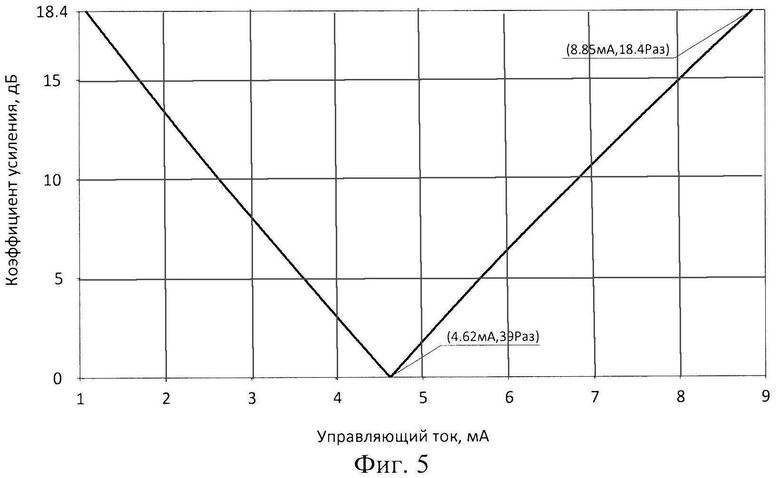

На чертеже фиг.5 показана зависимость модуля коэффициента усиления по напряжению от величины статического тока I10 третьего 10 токостабилизирующего двухполюсника схемы фиг.4. Данный график, а также анализ показывают, что при токе I10<4,6 мА выходной сигнал УУ имеет фазу, противоположную фазе входного напряжения ux=V6, а при I10>4,6 мА выходной сигнал УУ имеет фазу, совпадающую с фазой входного напряжения ux=V6.

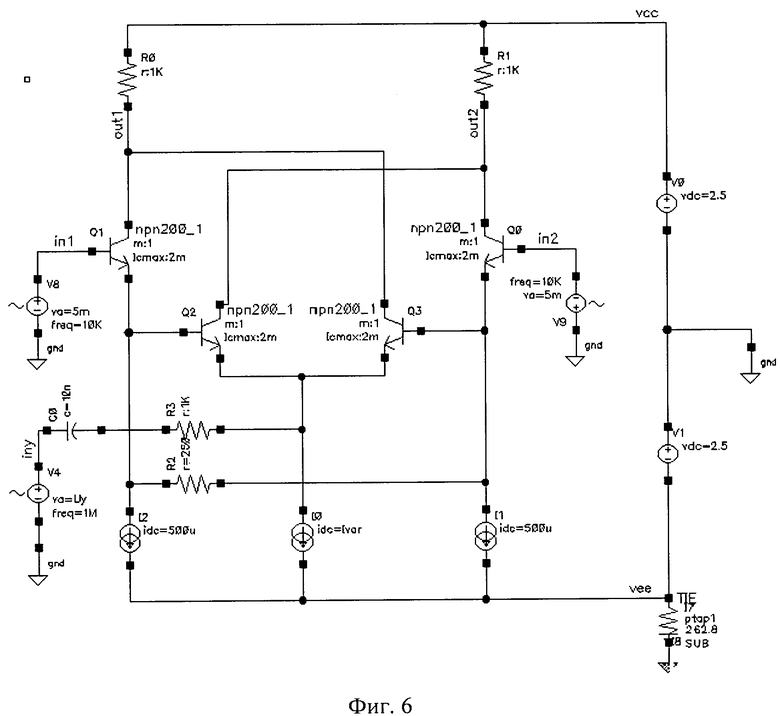

На чертеже фиг.6 представлена схема заявляемого УУ фиг.2 в среде Cadence на моделях SiGe интегральных транзисторов.

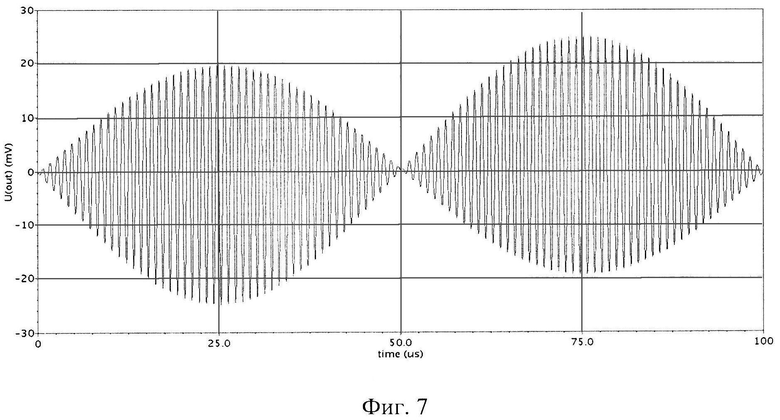

На чертеже фиг.7 показана осциллограмма выходного сигнала схемы УУ фиг.6 при напряжениях первого 1 и второго 2 источников противофазных входных напряжений (канал «X»)

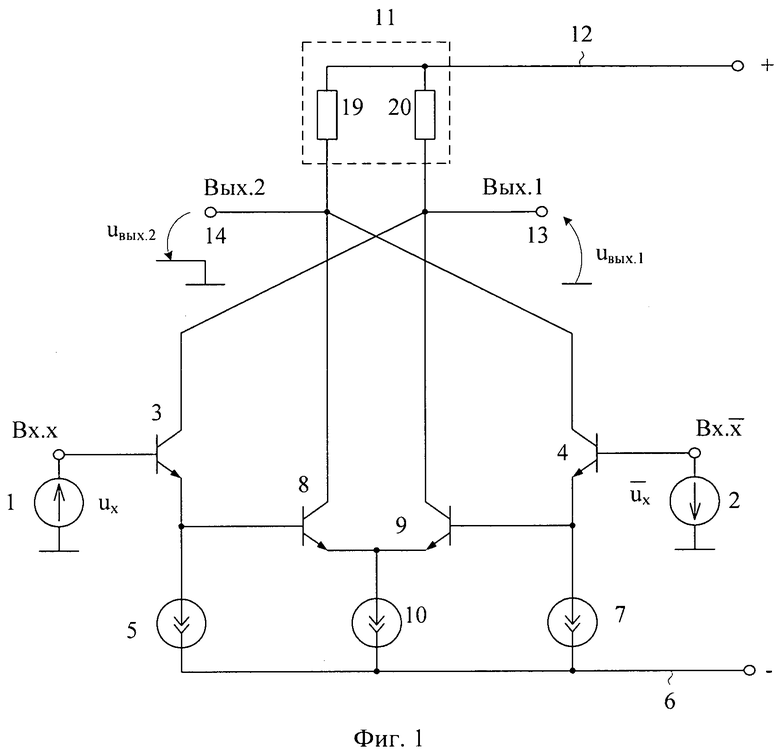

На чертеже фиг.8 показана спектрограмма выходного сигнала фиг.6 при напряжениях канала «X»

Заявляемый управляемый усилитель фиг.2, который может функционировать как смеситель аналоговых сигналов ux и uy, содержит первый 1 и второй 2 источники противофазных входных напряжений, связанных с соответствующими базами первого 3 и второго 4 входных транзисторов, эмиттер первого 3 входного транзистора через первый 5 токостабилизирующий двухполюсник подключен к первому 6 источнику питания, эмиттер второго 4 входного транзистора через второй 7 токостабилизирующий двухполюсник связан с первым 6 источником питания, третий 8 входной транзистор, эмиттер которого связан с эмиттером четвертого 9 входного транзистора и через третий 10 токостабилизирующий двухполюсник соединен с первым 6 источником питания, дифференциальную цепь нагрузки 11, согласованную со вторым 12 источником питания и связанную с первым 13 и вторым 14 выходами устройства, причем эмиттер первого 3 входного транзистора соединен с базой третьего 8 входного транзистора, эмиттер второго 4 входного транзистора соединен с базой четвертого 9 входного транзистора, коллектор третьего 8 входного транзистора соединен по переменному току с коллектором второго 4 входного транзистора и связан со вторым 14 выходом устройства, коллектор четвертого 9 входного транзистора соединен по переменного току с коллектором первого 3 входного транзистора и связан с первым 13 выходом устройства. Источник управляющего напряжения 15 связан по переменному току с объединенными эмиттерами третьего 8 и четвертого 9 входных транзисторов, причем между эмиттером первого 3 и второго 4 входных транзисторов включен дополнительный резистор 16.

Кроме этого, на чертеже фиг.2, в частном случае, в соответствии с п.2 формулы изобретения, источник управляющего напряжения 15 связан по переменному току с объединенными эмиттерами третьего 8 и четвертого 9 входных транзисторов через последовательно соединенные разделительный конденсатор 17 и согласующий резистор 18. Кроме этого, на чертеже фиг.2 дифференциальная цепь нагрузки 11 выполнена (в частном случае) на основе резисторов 19 и 20.

На чертеже фиг.3 показан пример применения заявляемого УУ фиг.2 для случая, когда источник управляющего напряжения 15 связан с объединенными эмиттерами третьего 8 и четвертого 9 входных транзисторов через дополнительный (классический) повторитель напряжения на транзисторах 21, 22 и дополнительный резистор 25. Данное схемотехническое решение, соответствующее п.1 формулы изобретения, иллюстрирует другие направления совершенствования заявляемого устройства. В частности, выполнение транзистора 22 в схеме фиг.3 на основе сдвоенного биполярного транзистора и подключение соответствующих коллекторов сдвоенного биполярного транзистора 22 к выходам 14 и 15 устройства способствует дальнейшему повышению уровня подавления основной гармоники смесителя фиг.3. Статический режим транзисторов 21 и 22 в схеме фиг.3 устанавливается источниками опорного тока 23 и 24. В частном случае, коллекторы сдвоенных транзисторов 22 могут соединяться со вторым 12 источником питания.

Рассмотрим работу УУ фиг.2 в диапазоне частот, когда влиянием конденсатора 17 можно пренебречь из-за его малого сопротивления на переменном токе в сравнении с сопротивлением резистора 18.

Входной сигнал (ux и

напряжений 1 и 2 в цепь нагрузки 11 на выходы 13 и 14 по двум каналам. Первый инвертирующий (для выхода 13 (14)) канал, образуемый каскадом с общим эмиттером на транзисторе 3 (4), инвертирует фазу сигнала ux

Второй канал передачи сигналов канала «X» к выходу 13 (14) - неинвертирующий. Он связан с наличием напряжений ux (1) и

где rэ8, rэ9 - сопротивления эмиттерных переходов соответствующих транзисторов 8 и 9:

причем суммарный ток общей эмиттерной цепи транзисторов 8 и 9 iΣ(t) зависит от управляющего напряжения uy 15:

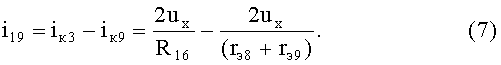

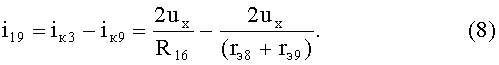

Как следствие, суммарный ток в резисторе 19 дифференциальной цепи нагрузки 11 имеет две разностные составляющие:

Таким образом, в резисторе нагрузки 19 протекают две противофазные составляющие токов, обусловленные входным сигналом ux канала «X» и напряжения uy канала «Y»:

Схема фиг.2 настраивается таким образом, чтобы при uy=0 переменный ток в резисторе 19 (20) был равен нулю, что обеспечивается соответствующим выбором резистора 16 и тока I10 двухполюсника 10:

Если суммарный ток общей эмиттерной цепи транзисторов 8 и 9 под действием источника управляющего напряжения 15 (uy) становится меньше или больше, чем статический ток I10, то происходит изменение фазы выходного сигнала ДК - в схеме преобладает либо первый инвертирующий канал передачи ux и

Таким образом, переменные токи в резисторах 19 и 20:

Поэтому переменная составляющая выходного дифференциального напряжения УУ фиг.2 является произведением напряжений ux и uy:

где

Из (11) следует, что заявляемое устройство обеспечивает смешение (перемножение) двух сигналов ux и uy, что подтверждается результатами моделирования (фиг.7, фиг.8).

В СВЧ смесителях сигналов фиг.2 резистор 18 может выполнять функцию цепи согласования источника входного напряжения канала «Y» с заданным волновым сопротивлением, например, 100 Ом.

Таким образом, предлагаемое техническое решение, являющееся альтернативным решением широко распространенного смесителя Гильберта, имеет функциональные преимущества по сравнению с прототипом.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патентная заявка US 2009/058466. fig.3.

2. Патент US №6.137.363.

3. Патент US №3.482.177, fig.3.

4. Патентная заявка US 2005/0225389, fig.3.

5. Патентная заявка US 2009/289714, fig.3.

6. Патент JP 52-139346, кл. 98(5)/А31, 1997.

7. Патент US 4.101.842, fig.1.

8. Патент US 5.006.818.

9. Патент СССР 813692.

10. Патент СССР 497713.

11. Операционные усилители с непосредственной связью каскадов / Анисимов В.И., Капитонов М.В., Прокопенко Н.Н., Соколов Ю.М. - Л., 1979. - 148 с. - стр.56, рис.2-11.

12. Полонников Д.Е. Операционные усилители: Принципы построения, теория, схемотехника. - М., 1983. - 216 с. - стр.140, рис.4.11.

13. Гальперин М.В. и др. Усилители постоянного тока / Гальперин М.В., Злобин Ю.П., Павленко В.А. - 2-е изд., перераб. и доп. - М.: Энергия, 1978, стр.78, рис.2-14.

| название | год | авторы | номер документа |

|---|---|---|---|

| УПРАВЛЯЕМЫЙ УСИЛИТЕЛЬ И АНАЛОГОВЫЙ СМЕСИТЕЛЬ СИГНАЛОВ | 2013 |

|

RU2530259C1 |

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ С НИЗКОВОЛЬТНЫМ ПИТАНИЕМ | 2010 |

|

RU2419188C1 |

| АНАЛОГОВЫЙ СМЕСИТЕЛЬ СИГНАЛОВ | 2012 |

|

RU2504072C1 |

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ С НИЗКОВОЛЬТНЫМ ПИТАНИЕМ | 2010 |

|

RU2419189C1 |

| УПРАВЛЯЕМЫЙ УСИЛИТЕЛЬ | 2010 |

|

RU2421883C1 |

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ С НИЗКОВОЛЬТНЫМ ПИТАНИЕМ | 2010 |

|

RU2419190C1 |

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ | 2010 |

|

RU2419145C1 |

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ | 2008 |

|

RU2396595C2 |

| АНАЛОГОВЫЙ СМЕСИТЕЛЬ ДВУХ СИГНАЛОВ | 2011 |

|

RU2450352C1 |

| СМЕСИТЕЛЬ СИГНАЛОВ | 2011 |

|

RU2452010C1 |

Предлагаемое изобретение относится к области радиотехники и связи и может быть использовано в радиоприемных устройствах, фазовых детекторах и модуляторах, а также в системах умножения частоты или в качестве усилителя, коэффициент передачи по напряжению которого с входов канала «X» зависит от уровня сигнала управления канала «Y». Технический результат заключается в улучшении подавления основной гармоники за счет смесителей аналоговых сигналов. Технический результат достигается за счет управляемого усилителя и смесителя аналоговых сигналов на базе дифференциального каскада Дарлингтона, который содержит первый (1) и второй (2) источники противофазных входных напряжений, базы первого (3) и второго (4) входных транзисторов, эмиттер первого (3) входного транзистора, первый (5) токостабилизирующий двухполюсник, первый (6) источник питания, эмиттер второго (4) входного транзистора, второй (7) токостабилизирующий двухполюсник, первый (6) источник питания, третий (8) входной транзистор, эмиттер четвертого (9) входного транзистора, третий (10) токостабилизирующий двухполюсник, дифференциальную цепь нагрузки (11), второй (12) источник питания, первый (13) и второй (14) выходы устройства. 1 з.п. ф-лы, 8 ил.

1. Управляемый усилитель и смеситель аналоговых сигналов на базе дифференциального каскада Дарлингтона, содержащий первый (1) и второй (2) источники противофазных входных напряжений, связанных с соответствующими базами первого (3) и второго (4) входных транзисторов, эмиттер первого (3) входного транзистора через первый (5) токостабилизирующий двухполюсник подключен к первому (6) источнику питания, эмиттер второго (4) входного транзистора через второй (7) токостабилизирующий двухполюсник связан с первым (6) источником питания, третий (8) входной транзистор, эмиттер которого связан с эмиттером четвертого (9) входного транзистора и через третий (10) токостабилизирующий двухполюсник соединен с первым (6) источником питания, дифференциальную цепь нагрузки (11), согласованную со вторым (12) источником питания и связанную с первым (13) и вторым (14) выходами устройства, причем эмиттер первого (3) входного транзистора соединен с базой третьего (8) входного транзистора, эмиттер второго (4) входного транзистора соединен с базой четвертого (9) входного транзистора, коллектор третьего (8) входного транзистора соединен по переменному току с коллектором второго (4) входного транзистора и связан со вторым (14) выходом устройства, коллектор четвертого (9) входного транзистора соединен по переменному току с коллектором первого (3) входного транзистора и связан с первым (13) выходом устройства, отличающийся тем, что источник управляющего напряжения (15) связан по переменному току с объединенными эмиттерами третьего (8) и четвертого (9) входных транзисторов, причем между эмиттером первого (3) и второго (4) входных транзисторов включен дополнительный резистор (16).

2. Управляемый усилитель и смеситель аналоговых сигналов на базе дифференциального каскада Дарлингтона по п.1, отличающийся тем, что источник управляющего напряжения (15) связан по переменному току с объединенными эмиттерами третьего (8) и четвертого (9) входных транзисторов через последовательно соединенные разделительный конденсатор (17) и согласующий резистор (18).

| Колосоуборка | 1923 |

|

SU2009A1 |

| ШИРОКОПОЛОСНЫЙ УСИЛИТЕЛЬ ТОКА | 2011 |

|

RU2467468C1 |

| УСИЛИТЕЛЬ С ПЕРЕМЕННЫМ УСИЛЕНИЕМ И ВЫСОКИМ ДИНАМИЧЕСКИМ ДИАПАЗОНОМ | 1997 |

|

RU2209504C2 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2411634C1 |

| ДВУХТАКТНЫЙ УСИЛИТЕЛЬ МОЩНОСТИ | 2002 |

|

RU2298282C2 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412535C1 |

Авторы

Даты

2014-06-10—Публикация

2013-05-14—Подача