Изобретение относится к электронике, в частности к цифровым синтезаторам прямого синтеза, и может быть использовано для генерации выходной частоты цифрового синтезатора прямого синтеза (ЦСПС) с низким уровнем нежелательных гармоник в спектре выходного сигнала синтезатора.

Традиционная схема ЦСПС состоит из регистра частоты, аккумулятора фазы, регистра фазы, преобразователя фазы в амплитуду и цифроаналогового преобразователя.

Функционирует данная схема следующим образом. В регистр частоты записывают число в двоичной системе, определяющее значение частоты выходного сигнала синтезатора и называемое кодом частоты. Код частоты поступает на один из входов аккумулятора фазы, на другой вход которого от внешнего источника опорной частоты поступает цифровой сигнал тактовой частоты fCLK. Аккумулятор фазы вычисляет адрес, соответствующий мгновенному значению фазы, и подает его на вход регистра фазы. Последний обычно представляет собой ПЗУ с табличными значениями функции синуса. На выходе регистра фазы получают текущее значение фазы, которое преобразователь фазы в амплитуду превращает в текущее значение сигнала в цифровом виде. Цифроаналоговый преобразователь преобразует это цифровое значение в соответствующее значение напряжения или тока.

Цифровые синтезаторы прямого синтеза (ЦСПС) обеспечивают высокую скорость перестройки частоты, низкий уровень фазового шума. Однако в ходе прямого цифрового синтеза возникают негармонические побочные составляющие из-за эффектов дискретизации и округления в узлах синтезатора. Ошибки, вызывающие появление побочных дискретных составляющих в спектре выходного сигнала, можно разделить на три типа. К первому типу относятся ошибки, вызванные округлением фазы при адресации ПЗУ с таблицей синтезируемой функции. Второй тип - это ошибки, связанные с конечной разрядностью шины данных. Третий тип включает ошибки, вызванные цифроаналоговым преобразователем. Наибольший вклад в ухудшение спектральных характеристик синтезатора вносят ошибки, связанные с округлением фазы, вызывая появление нежелательных дискретных составляющих в спектре выходного сигнала синтезатора.

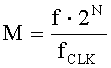

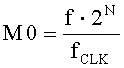

Возникновение паразитных дискретных составляющих в ближней зоне спектра выходного сигнала, соответствующей отстройке 1-150 кГц от основного сигнала, связано с необходимостью округления кода частоты до ближайшего целого числа при его расчете по формуле:

где f - синтезируемая частота; N - разрядность аккумулятора фазы (накапливающий сумматор), fCLK - тактовая частота.

Полученное число вносится в цифровом виде в регистр частоты. Из регистра частоты рассчитанный код попадает в аккумулятор фазы. В результате возникает ошибка в значениях частот расчетного и истинного выходного сигнала, которая будет постепенно накапливаться в аккумуляторе фазы. Из-за конечной разрядности аккумулятора фазы, разрядность которого обычно составляет 32 бита, скорость накопления этой ошибки будет достаточной для изменения значения первого значимого бита на единицу при адресации ПЗУ с таблицей синусов синтезируемой функции с определенным периодом, в результате чего будет наблюдаться выброс в спектре выходного сигнала. Это переполнение адреса ПЗУ будет происходить достаточно редко, вследствие чего наблюдаемые паразитные дискретные составляющие будут проявляться только в ближней зоне выходного сигнала.

Однако область отстройки выходного сигнала в диапазоне 0,1-120 кГц попадает в доплеровский диапазон изменения выходной частоты, к которому предъявляются жесткие требования по уровню дискретных паразитных составляющих, уровень которых должен быть не более минус 100-110 дБ.

Известен способ генерации выходной частоты ЦСПС, обеспечивающий подавление дискретных побочных составляющих и описанный в патенте US №4410954, при котором в дополнение к классической структурной схеме синтезатора с фазовым накопителем вводится дополнительный генератор псевдослучайного кода. Периодическое добавление псевдослучайного числа к содержимому фазового накопителя позволяет разрушить когерентность фазовой ошибки и таким образом размыть нежелательные дискретные составляющие в спектре выходного сигнала.

Однако использование данного способа требует введения дополнительных элементов в схему синтезатора, а так как большинство цифровых синтезаторов прямого синтеза выпускается в виде микросхем, то указанный способ требует изменения микросхемы, что в большинстве случаев сделать невозможно.

Наиболее близким к заявляемому изобретению является способ генерации частоты сигнала, свободного от негармонических искажений сигнала, описанный в патентной заявке ЕР №543186. В данном способе устанавливают предварительную частоту тактирования fl и задают значение кода частоты (считываемого адреса) в соответствии с выходной частотой. Затем определяют значение отношения количества ячеек памяти ПЗУ к значению кода частоты. Если результат деления является целым натуральным числом, то для синтеза выходной частоты используют предварительную частоту тактирования fl. Если отношение получается с остатком, значение кода частоты изменяют (Р), выбирая его большим значения количества ячеек памяти ПЗУ N, и делят М на него, рассчитывая результат деления M на P. На основе полученных данных вычисляют частоту тактирования f2 для обеспечения требуемой выходной частоты в зависимости от кода частоты Р. Таким образом, для генерации выходной частоты синтезатора используют код частоты Р и частоту тактирования f2. Указанный способ позволяет получить стабильную частоту выходного сигнала, независимую от разрядностей аккумулятора фазы и ПЗУ, и относительно чистый спектр выходного сигнала.

Однако, несмотря на все достоинства описанного метода, он требует изменения схемы ЦСПС и введения перестраиваемого по частоте источника сигнала, чтобы обеспечить изменяемую частоту тактирования. Часто осуществить изменение схемы ЦСПС не представляется возможным, а дополнительный перестраиваемый источник будет вносить дополнительный шум.

Задачей заявляемого изобретения является обеспечение генерации выходного сигнала с низким уровнем побочных спектральных составляющих в спектре выходного сигнала цифрового синтезатора прямого синтеза.

Сущность заявляемого изобретения состоит в том, что в способе генерации выходной частоты цифрового синтезатора прямого синтеза, включающем вычисление кода частоты в соответствии с требуемой величиной выходной частоты, запись в регистр частоты кода частоты, подачу кода частоты в аккумулятор фазы, вычисление посредством аккумулятора фазы адреса, направляемого в ПЗУ регистра фазы, вычисление посредством регистра фазы мгновенного значения выходного сигнала в цифровом виде и преобразование посредством цифроаналогового преобразователя в соответствующее значение в аналоговом виде, в случае, если вычисленное значение кода частоты является дробным, вычисляют первый код частоты, соответствующий округленному до целого числа коду частоты, и дробную часть исходного кода частоты, выбирают второй код частоты, отличающийся на единицу от первого кода частоты, записывают второй код частоты в регистр частоты, попеременно считывают из регистра частоты первый и второй коды частоты с периодичностью, определяемой дробной частью исходного кода частоты.

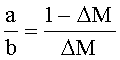

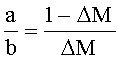

Кроме того, заявляется способ, в котором наряду с вышеперечисленными признаками используют второй код частоты, на единицу больший первого кода частоты, и считывают коды частоты с периодичностью, определяемой формулой:

где a - количество загрузок первого кода частоты из регистра частоты, b - количество загрузок второго кода частоты из регистра частоты, ΔM - дробная часть исходного кода частоты.

Технический результат заявляемого изобретения заключается в снижении уровня побочных дискретных составляющих выходного сигнала синтезатора без изменения схемы ЦСПС.

Указанный технический результат достигается за счет использования двух кодов частоты, один из которых соответствует коду частоты, рассчитанному в соответствии с требуемым значением частоты выходного сигнала и округленному до целого числа, а второй отличается от первого на единицу; и переключения между ними в процессе генерации с периодичностью, достаточной для компенсации ошибки, возникающей за счет округления кода частоты. При этом переключение на ближайший возможный код частоты обеспечивает генерацию сигнала на другой, но ближайшей к несущей частоте, которая компенсирует накопление ошибки. Благодаря компенсации накапливающейся ошибки не происходит периодических выбросов, проявляющихся в виде побочных дискретных составляющих в спектре выходного сигнала. Наряду с подавлением побочных дискретных составляющих происходит снижение фазового шума в ближней зоне от несущей при отстройке 200 кГц. Уровень подавления достигает 20 дБ. Заявляемый способ позволяет целенаправленно снижать уровень побочных дискретных составляющих без внесения дополнительного фазового шума и без изменения схемы ЦСПС.

Способ осуществляют следующим образом. На вход CLOCK ЦСПС подают сигнал с тактовой частотой, исходя из условия, что требуемая частота на выходе должна быть не более 0,4 от тактовой частоты. Для синтеза требуемой частоты рассчитывают значение сдвига фазы - кода частоты в соответствии с формулой:

где f - синтезируемая частота; N - разрядность аккумулятора фазы, fCLK - тактовая частота.

Полученное значение кода частоты округляется до целого числа. Данное округление вносит накапливаемую ошибку в выходной сигнал, которая проявляется в виде побочных спектральных составляющих в спектре выходного сигнала. При переполнении аккумулятора фазы происходит выброс накопившейся ошибки в виде побочной спектральной составляющей, расположенной вблизи несущей и которую невозможно подавить в том числе и узкополосным фильтром из-за ограничения полосы пропускания фильтра при фильтрации основного сигнала.

Для решения этой проблемы необходимо обеспечить компенсацию возникающей ошибки.

В один из регистров частоты записывают первый код частоты М, выраженный в двоичном представлении и характеризующий приращение фазы. Для каждой конкретной частоты определяют ошибку, соответствующую отбрасываемым числам после запятой, по формуле: ΔM=M0-M, где M0 - исходный неокругленный код частоты, M - первый код частоты, представляющий собой округленный до целого числа исходный код частоты.

В другой регистр частоты записывают следующее значение кода частоты M1=M+1 - второй код частоты, и переключают коды с периодичностью, зависящей от величины ошибки.

Периодичность переключения кодов частоты определяют по формуле:

где a - количество загрузок первого кода частоты из регистра частоты, b - количество загрузок второго кода частоты из регистра частоты, ΔM - дробная часть исходного кода частоты.

Такой подход, отличающийся от известных способов подавление побочных спектральных составляющих, приводит к тому, что уровень побочной дискретной составляющей снижается, переходя в фазовый шум вблизи несущей.

Пример.

Конкретная реализация заявляемого способа представлена для частоты f=336 МГц при тактовой частоте fCLK=1008 МГц и разрядности аккумулятора фазы N=32 бита для микросхемы AD9910 фирмы Analog Devices. Расчет кода частоты М0 осуществляют по формуле:

M0=1431655765,3(3) в десятичном коде.

В регистре частоты происходит перевод исходного кода частоты М0 в шестнадцатеричную систему счисления с округлением до целого числа. Таким образом, преобразованный регистром частоты код имеет вид M=55555555 в шестнадцатеричной системе счисления. В десятеричной системе счисления: М=1431655765. Затем рассчитывают второй код частоты M1, равный увеличенному на единицу первому коду частоты М: М1=М+1. Таким образом, второй код частоты равен M1=55555556 в шестнадцатеричной системе счисления и M1=1431655766 в десятеричной системе счисления.

Рассчитывают относительную ошибку ΔМ, возникающую при округлении исходного кода частоты М0 до целого числа М, по формуле:

ΔM=M0-M.

Для данного конкретного примера ΔM=1/3.

Рассчитывают относительную ошибку ΔM1, возникающую при использовании кода частоты M1, по формуле:

ΔM1=M0-М1.

Для данного конкретного примера ΔМ1=-2/3.

Для определения частоты переключения между первым кодом частоты М и вторым кодом частоты M1 составляют линейную комбинацию ΔM и ΔM1, которая необходима для компенсации ошибки, возникающей при использовании кодов частоты M и M1, отличающихся от исходного M0, по формуле:

Δ=a·ΔM+b-ΔM1.

Полная компенсация достигается, когда A стремится к 0.

Затем определяют коэффициенты a и b, которые задают частоту переключения между округленным кодом частоты M и вторым кодом частоты M1. Т.е. значение коэффициента а соответствует количеству загрузок частоты, соответствующему количеству непрерывных считываний первого кода М из регистра частоты, после чего происходит загрузка частоты, соответствующая второму коду M1, с продолжительностью, соответствующей значению коэффициента b.

Для данного конкретного примера линейная комбинация примет вид: 0=a·1/3+b·(-2/3).

Отсюда a=2, b=1.

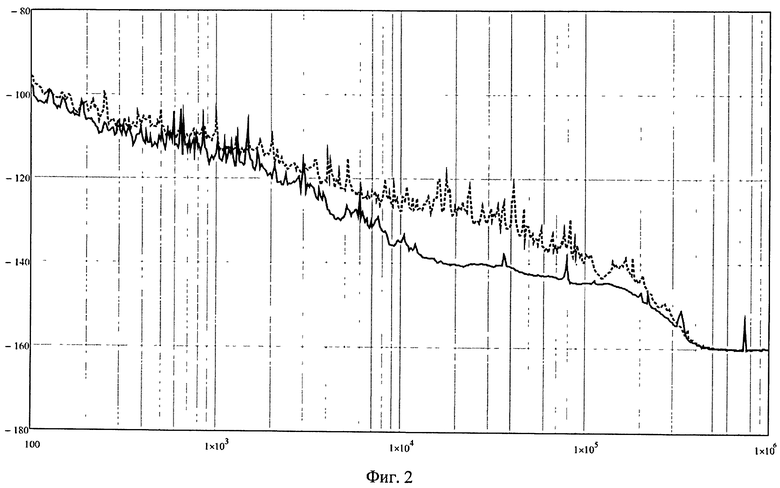

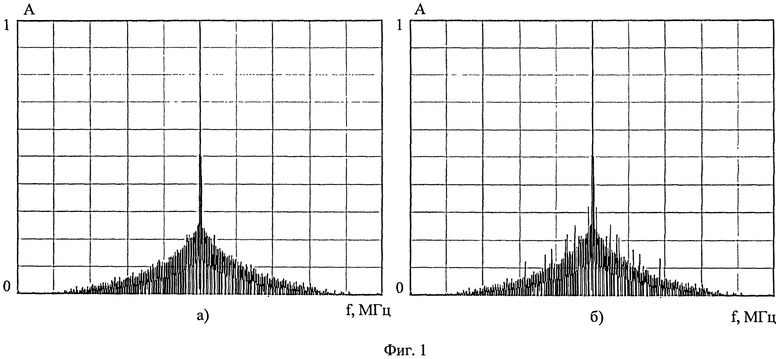

Для данного конкретного примера на Фиг.1 изображен спектр выходного сигнала ЦСПС с полосой обзора 1 МГц с использованием компенсации ошибки (а) и без нее (б). На Фиг.2 изображен фазовый шум выходного сигнала ЦСПС с частотой 336 МГц с полосой обзора 1 МГц при частоте тактового сигнала 1008 МГц с использованием компенсации ошибки (-) и без нее (--).

| название | год | авторы | номер документа |

|---|---|---|---|

| ГЕНЕРАТОР СИНУСОИДАЛЬНОГО СИГНАЛА | 2014 |

|

RU2568391C1 |

| СИНТЕЗАТОР ЧАСТОТ | 2015 |

|

RU2597477C1 |

| СПОСОБ ДИСКРЕТНОГО ЗАДАНИЯ ФАЗОВОГО СДВИГА МЕЖДУ ДВУМЯ МОНОХРОМАТИЧЕСКИМИ ГАРМОНИЧЕСКИМИ ИЗНАЧАЛЬНО СИНХРОННЫМИ СИГНАЛАМИ, И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2013 |

|

RU2534929C2 |

| АБОНЕНТСКИЙ ПУНКТ В АБОНЕНТСКОЙ СИСТЕМЕ БЕСПРОВОДНОЙ СВЯЗИ | 1990 |

|

RU2138122C1 |

| СИНТЕЗАТОР ЧАСТОТ | 2001 |

|

RU2214043C2 |

| СИСТЕМА АВТОМАТИЧЕСКОЙ ПОДСТРОЙКИ ЧАСТОТЫ ПО ЗАДЕРЖКЕ | 2005 |

|

RU2337474C2 |

| АБОНЕНТСКИЙ ПУНКТ В СИСТЕМЕ БЕСПРОВОДНОЙ ЦИФРОВОЙ ТЕЛЕФОННОЙ СВЯЗИ | 1990 |

|

RU2154360C2 |

| Цифровой синтезатор частот | 1986 |

|

SU1363423A1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ГАРМОНИЧЕСКИХ КОЛЕБАНИЙ | 2003 |

|

RU2239281C2 |

| Цифровой синтезатор сигналов | 1990 |

|

SU1720142A1 |

Изобретение относится к электронике, в частности к цифровым синтезаторам прямого синтеза. Достигаемый технический результат - снижение уровня побочных дискретных составляющих выходного сигнала. Способ генерации выходной частоты цифрового синтезатора прямого синтеза включает вычисление кода частоты в соответствии с требуемой величиной выходной частоты, запись его в регистр частоты и подачу кода частоты в аккумулятор фазы, если вычисленное значение кода частоты является дробным, вычисляют первый код частоты, соответствующий округленному до целого числа исходному коду частоты, и дробную часть исходного кода частоты, выбирают второй код частоты, отличающийся на единицу от первого кода частоты, и записывают его в регистр частоты, попеременно считывают из регистра частоты первый и второй коды частоты с периодичностью, определяемой дробной частью исходного кода частоты, код частоты поступает из регистра частоты в аккумулятор фазы, посредством аккумулятора фазы вычисляют адрес, поступающий в ПЗУ регистра фазы, с помощью регистра фазы вычисляют мгновенное значение выходного сигнала в цифровом виде, которое поступает в цифроаналоговый преобразователь и преобразуется в соответствующее значение сигнала в аналоговом виде. 1 з.п. ф-лы, 2 ил.

1. Способ генерации выходной частоты цифрового синтезатора прямого синтеза, включающий вычисление кода частоты в соответствии c требуемой величиной выходной частоты, запись в регистр частоты кода частоты, подачу кода частоты в аккумулятор фазы, вычисление посредством аккумулятора фазы адреса, направляемого в ПЗУ регистра фазы, вычисление посредством регистра фазы мгновенного значения выходного сигнала в цифровом виде и преобразование посредством цифроаналогового преобразователя в соответствующее значение в аналоговом виде, отличающийся тем, что в случае, если вычисленное значение кода частоты является дробным, вычисляют первый код частоты, соответствующий округленному до целого числа коду частоты, и дробную часть исходного кода частоты, выбирают второй код частоты, отличающийся на единицу от первого кода частоты, записывают второй код частоты в регистр частоты, попеременно считывают из регистра частоты первый и второй коды частоты с периодичностью, определяемой дробной частью исходного кода частоты.

2. Способ по п.1, отличающийся тем, что используют второй код частоты, на единицу больший первого кода частоты, и считывают коды частоты с периодичностью, определяемой формулой:

где a - количество загрузок первого кода частоты из регистра частоты,

b - количество загрузок второго кода частоты из регистра частоты,

ΔM - дробная часть исходного кода частоты.

| Устройство для контроля каналов связи | 1974 |

|

SU543186A1 |

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНЫЙ СИНТЕЗАТОР | 2005 |

|

RU2286645C1 |

| СИНТЕЗАТОР ЧАСТОТЫ С ДЕЛЕНИЕМ НА ДРОБНОЕ ЧИСЛО И КОРРЕКЦИЕЙ ОСТАТОЧНОЙ ПОГРЕШНОСТИ И СПОСОБ СИНТЕЗА ЧАСТОТЫ | 1994 |

|

RU2134930C1 |

| US 7557619 В1, 07.07.2009. | |||

Авторы

Даты

2014-01-20—Публикация

2012-11-27—Подача