Изобретение относится к радиотехнике и может использоваться в радиоприемных и радиопередающих устройствах в качестве гетеродина.

Известен синтезатор частот с фазовой автоподстройкой частоты (ФАПЧ), возбуждаемый цифровым синтезатором с прямым синтезом частот (ЦС), наиболее близкий по технической сущности к предлагаемому синтезатору и выбранный в качестве прототипа.

Синтезатор частот содержит ЦС, имеющий вход точной регулировки частоты и вход синхронизирующих сигналов для приема, соответственно, внешних фазовых данных и внешних синхросигналов, и выход, на котором образуются опорный сигнал; фильтр, имеющий вход, соединенный с выходом цифрового синтезатора, и выход; схему ФАПЧ, имеющую вход, соединенный с выходом фильтра, вход грубой регулировки частоты для приема кода, соответствующего коэффициенту деления N делителя частоты, и выход, на котором образуется сигнал синтезатора [1].

ЦС применяется для формирования мелких разрядов частоты выходного сигнала синтезатора (доли герц). При делении на дробный коэффициент из-за неравномерности выходной последовательности образуются нежелательные дискретные побочные составляющие, у которых частоты отстройки от выходного сигнала могут быть очень малыми (низкими).

Недостаток прототипа в том, что низкочастотные дискретные побочные составляющие (помехи) на выходе ЦС, попадая в полосу пропускания схемы ФАПЧ, модулируют частоту выходного сигнала. Это отражается на спектре выходного сигнала, в котором будут присутствовать дискретные побочные составляющие, обусловленные помехами на выходе ЦС.

Задача настоящего изобретения - уменьшение уровня нежелательных дискретных побочных составляющих в спектре выходного сигнала.

Использование предлагаемого технического решения позволит уменьшить уровни нежелательных дискретных побочных составляющих за счет увеличения частоты их отстройки от выходного сигнала ЦС с последующей фильтрацией схемой ФАПЧ.

Решение задачи достигается тем, что в синтезатор частот, содержащий ЦС, имеющий вход точной регулировки частоты и вход синхронизирующих сигналов для приема соответственно внешних фазовых данных и внешних синхросигналов и выход, на котором образуется опорный сигнал; фильтр, имеющий вход, соединенный с выходом цифрового синтезатора, и выход; схему ФАПЧ, состоящую из последовательно соединенных в кольцо перестраиваемого генератора (ПГ), делителя частоты с переменным коэффициентом деления (ДПКД), частотно-фазового детектора (ЧФД) и фильтра нижних частот (ФНЧ), имеющую вход, соединенный с выходом фильтра, вход грубой регулировки частоты для приема кода, соответствующего коэффициенту деления N ДПКД, и выход, на котором образуется сигнал синтезатора, введены решающее устройство, которое имеет два входа для приема кодовых данных точной и грубой регулировок частоты и два выхода, один из которых соединен со входом точной регулировки частоты ЦС; и цифровой сумматор, имеющий первый вход для приема кодовых данных грубой регулировки частоты, выход, который соединен со входом грубой регулировки частоты схемы ФАПЧ, и второй вход, который соединен со вторым выходом решающего устройства.

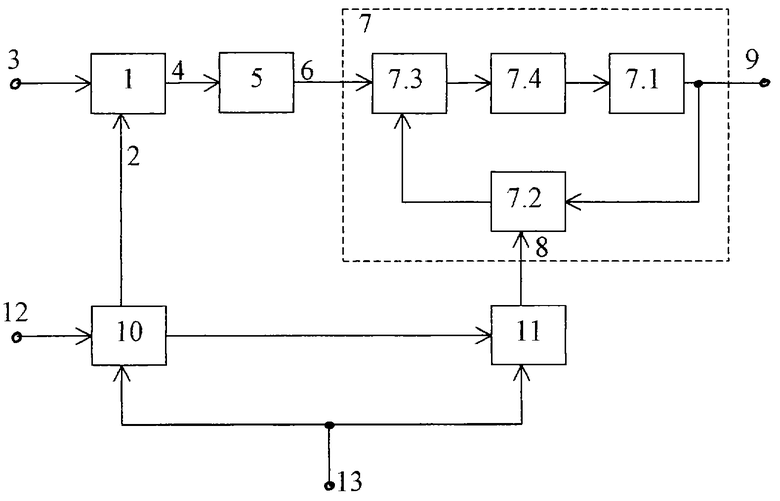

На чертеже представлена структурная схема синтезатора, которая содержит построенный на основе накапливающего сумматора ЦС 1, имеющий вход 2 точной регулировки частоты, который является информационным входом накапливающего сумматора, и вход 3 синхронизирующих сигналов для приема соответственно внешних фазовых данных и внешних синхросигналов и выход 4; фильтр 5, имеющий вход, соединенный с выходом ЦС 1, и выход 6; схему ФАПЧ 7, состоящую из последовательно соединенных в кольцо ПГ 7.1, ДПКД 7.2, ЧФД 7.3 и ФНЧ 7.4, и имеющую вход, соединенный с выходом 6 фильтра 5, вход 8 грубой регулировки частоты для приема кода, соответствующего коэффициенту деления N ДПКД, и выход 9, на котором образуется сигнал синтезатора; решающее устройство (РУ) 10, имеющее два входа и два выхода; цифровой сумматор 11 с двумя входами и одним выходом, первый - для приема кодовых данных грубой регулировки частоты, второй - для изменения выходного кода, который поступает на вход ДПКД, кроме того, первый и второй входы РУ подключены соответственно к входам 12 точной и 13 грубой регулировок частоты, первый выход соединен со входом точной регулировки частоты ЦС 1, а второй выход подключен ко второму входу цифрового сумматора 11.

РУ 10 может быть реализовано на любом устройстве, которое в своем составе имеет порты ввода/вывода данных, оперативное запоминающее устройство (ОЗУ), постоянное запоминающее устройство (ПЗУ) и может выполнять арифметические действия. Таким устройством может быть, например, микроконтроллер, микропроцессор, однокристальная микроЭВМ или персональная вычислительная машина. РУ 10 выполняет вычислительные операции по программе, предварительно в него записанной.

Так как основным узлом ЦС, формирующим частоту выходного сигнала, является накапливающий сумматор [2], то на его выходе частота будет [3, 4]:

fвых=fвх•m/n=fвх/K=fвх/(Кц+Кдр) (1)

где fвх - частота входного сигнала ЦС;

n - емкость накапливающего сумматора;

m - входной код накапливающего сумматора;

К - коэффициент деления частоты ЦС;

Кц - целая часть коэффициента деления;

Кдр - дробная часть коэффициента деления.

После прохождения через фильтр 5 сигнал подается на опорный вход ЧФД 7.3 схемы ФАПЧ 7, на второй вход которого подается сигнал с ПГ 7.1 частотой, поделенной на N в ДПКД 7.2. В результате сравнения частот в ЧФД 7.3 через ФНЧ 7.4 обеспечивается стабильность частоты выходного сигнала ПГ 7.1 и всего синтезатора, которая будет [5]:

fвых.с=fвых•N=fвх•N•m/n, (2)

где N - коэффициент деления делителя частоты схемы ФАПЧ.

Дробная часть (Кдр) в коэффициенте деления может составлять до (1/2)32, а то и менее. При делении на дробный коэффициент из-за неравномерности выходной последовательности образуются нежелательные дискретные побочные составляющие, у которых частоты отстройки от выходного сигнала равны и кратны fвых•Кдр или fвых•(1-Кдр). Наиболее опасными нежелательными дискретными побочными составляющими являются те, у которых Кдр приближается к нулю или к единице. Так как частота нежелательных дискретных побочных составляющих очень низкая, то ее труднее впоследствии фильтровать.

Для нормальной работы необходимо, чтобы отстройки нежелательных дискретных побочных составляющих в выходном сигнале ЦС 1 были за полосой пропускания схемы ФАПЧ, то есть

fвых•Кдр>>fср или fвых•(1-Кдр)>>fср (3)

где fср - полоса пропускания схемы ФАПЧ.

Из формулы (1) Кдр=n/m-Кц, (4)

где Кц=Int [n/m] - целая часть коэффициента деления ЦС 1.

Допустимое значение дробных коэффициентов деления Кдоп определяется по формулам

Кдр≥Кдоп или (1-Кдр)≥Кдоп (5)

и для которого выполняется условие (3). Кдоп записывается со значением n в ПЗУ РУ 10.

При поступлении кодов m и N на входы 12 и 13 РУ 10 вычисляет Кдр по формуле (4) и сравнивает с Кдоп. Если Кдр удовлетворяет условию (5), то код m со входа 12 поступает на вход 2 ЦС 1 без изменения и на вход цифрового сумматора 11 подается сигнал, по которому код со входа 13 без изменения подается через цифровой сумматор 11 на схему ФАПЧ 7. Если код не удовлетворяет условию (5), то РУ 10 производит вычисление нового значения входного кода ЦС 1 по формуле

m1=m•N/(N+ΔN) или ml=m•N/(N-ΔN), (6)

где ΔN - значение изменения кода грубой регулировки, и вычисления повторяются.

Если Кдр удовлетворяет условию (5), то с выхода РУ 10 код ml подается на вход 2 ЦС 1, а со второго выхода РУ 10 на цифровой сумматор 11 подается код ΔN или [-ΔN] . В результате этого код, поступающий на ДПКД 7.2, будет увеличен или уменьшен.

Алгоритм программы приведен на фиг.2.

Сопоставительный анализ показывает, что предложенное техническое решение отличается от прототипа тем, что введенные решающее устройство и цифровой сумматор обеспечивают более чистый спектр выходного сигнала синтезатора за счет изменения коэффициента деления в ДПКД схемы ФАПЧ и установления нового значения дробной части коэффициента деления цифрового синтезатора.

Поэтому данное техническое решение отвечает критерию "новизна".

Литература

1. Пат. США N4965533, Н 03 L 7/18, 901023, том 1119, N 4, 1989 г.

2. В. Лобов, В. Стешенко, Б. Шахтарин. Цифровые синтезаторы частот прямого синтеза. CHIP NEWS, 1(10), 1997 г. стр.16-21.

3. А.В. Рыжков, В.Н. Попов. Синтезаторы частот в технике радиосвязи. М.: Радио и связь. 1991. 253с.

4. Д. Н. Шапиро, А.А. Паин. Основы теории синтеза частот. М.: Радио и связь. 1981. 179с.

5. В. Манасевич. Синтезаторы частот. Теория и проектирование. М., 1979. 33-37 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ДРОБНЫМ ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 2002 |

|

RU2222101C2 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ДРОБНЫМ ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 1992 |

|

RU2041563C1 |

| Конструкция малошумящего синтезатора частот с низким уровнем побочных спектральных составляющих | 2024 |

|

RU2834405C1 |

| СИНТЕЗАТОР ЧАСТОТ | 1997 |

|

RU2137287C1 |

| Цифровой формирователь частотно-модулированных сигналов с низким уровнем искажений | 2021 |

|

RU2765273C1 |

| СЛЕДЯЩИЙ ПРИЕМНИК ШИРОКОПОЛОСНОГО СИГНАЛА | 1999 |

|

RU2157052C1 |

| Широкодиапазонный синтезатор с фазовой автоподстройкой частоты управляемого генератора с переключаемыми резонаторами | 2023 |

|

RU2804407C1 |

| СИНТЕЗАТОР ЧАСТОТ | 1995 |

|

RU2119238C1 |

| СИНТЕЗАТОР ЧАСТОТ | 2010 |

|

RU2434322C1 |

| УСТРОЙСТВО ДЛЯ СОЗДАНИЯ ПРИЦЕЛЬНЫХ ПОМЕХ РАДИОЛОКАЦИОННЫМ СТАНЦИЯМ | 2006 |

|

RU2329603C2 |

Изобретение относится к радиотехнике и может использоваться в радиоприемных и радиопередающих устройствах в качестве гетеродина. Достигаемый технический результат - уменьшение уровня побочных составляющих в спектре выходного сигнала. Синтезатор частот содержит цифровой синтезатор с прямым синтезом частот, фильтр, схему разовой автоподстройки частоты, состоящую из последовательно соединенных в кольцо перестраиваемого генератора, делителя частоты с переменным коэффициентом деления, частотно-фазового детектора и фильтра нижних частот, цифровой сумматор и решающее устройство, которое вычисляет значение дробной части коэффициента деления цифрового синтезатора с прямым синтезом частот, формирует сигнал, который изменяет код грубой регулировки частоты, и сигнал, который изменяет значение входного кода цифрового синтезатора с прямым синтезом частот. 1 ил.

Синтезатор частот, содержащий цифровой синтезатор с прямым синтезом частот (ЦС), имеющий вход точной регулировки частоты и вход синхронизирующих сигналов для приема, соответственно, внешних фазовых данных и внешних синхросигналов, и выход, на котором образуется опорный сигнал, фильтр, имеющий вход, соединенный с выходом ЦС и выход, схему фазовой автоподстройки частоты (ФАПЧ), состоящую из последовательно соединенных в кольцо перестраиваемого генератора (ПГ), делителя частоты с переменным коэффициентом деления (ДПКД), частотно-фазового детектора (ЧФД) и фильтра нижних частот (ФНЧ), имеющую вход, соединенный с выходом фильтра, вход грубой регулировки частоты для приема кода, соответствующего коэффициенту деления ДПКД, и выход, на котором образуется сигнал синтезатора, отличающийся тем, что в него введены решающее устройство (РУ), имеющее первый и второй входы и первый и второй выходы, и цифровой сумматор, который имеет первый и второй входы и выход, причем первый вход РУ соединен со входом точной регулировки частоты синтезатора, первый выход соединен со входом точной регулировки частоты ЦС, второй вход соединен со вторым входом цифрового сумматора и с входом грубой регулировки частоты синтезатора, а второй выход РУ подключен к первому входу цифрового сумматора, выход которого соединен со входом грубой регулировки частоты схемы ФАПЧ, при этом решающее устройство вычисляет значение дробной части коэффициента деления (Кдр) цифрового синтезатора с прямым синтезом частот, формирует сигнал, который изменяет код грубой регулировки частоты, и сигнал, который изменяет значение входного кода цифрового синтезатора с прямым синтезом частот.

| Устройство фазовой автоподстройки частоты | 1987 |

|

SU1518881A1 |

| Цифровой синтезатор частот | 1986 |

|

SU1483632A1 |

| Устройство цифрового сопровождения фазы периодического сигнала | 1981 |

|

SU978364A1 |

| US 5122762 A, 16.06.1992 | |||

| US 5128632 A, 07.07.1992. | |||

Авторы

Даты

2003-10-10—Публикация

2001-03-11—Подача