Изобретение относится к области радиотехники и может применяться в радиосвязи, системах радионавигации и радиолокации. В частности, предлагаемое изобретение предназначено для высокоточных бортовых радиолокационных систем (БРЛС), обладающих высоким уровнем помехозащищенности и скрытности.

Для обеспечения высокого уровня помехозащищенности и скрытности радиолокационных систем существует необходимость генерировать серии волн с различными частотами с сохранением фазовой когерентности между сериями волн одной и той же частоты, т.е. необходимость в сохранении одного и того же фазового сдвига относительно тактового сигнала. В большинстве случаев такая задача решается при помощи синтезаторов частот, обеспечивающих синтез множества когерентных частот.

Для синтеза множества когерентных частот в радиолокационных системах наиболее часто применяются синтезаторы с фазовой автоподстройкой частоты (ФАПЧ). Хотя преимуществом схем на основе ФАПЧ являются достаточно чистый спектр выходного сигнала и намного более низкий уровень сложности по сравнению с аналоговыми синтезаторами, синтезаторы на основе ФАПЧ имеют существенные недостатки. Одним из них является большое время перестройки. Другим недостатком является высокий уровень фазового шума, зависящий от коэффициента деления частотного делителя. Для уменьшения суммарного коэффициента деления в синтезатор частот можно ввести схему частотного преобразования либо использовать дробные коэффициенты деления. В первом случае требуется оптимизация отельных элементов схемы из-за высокой чувствительности к ним смесителей, а также устранение проблемы ложного захвата частоты, присущей схемам на основе частотного преобразования, что является далеко не тривиальными задачами. Во втором случае необходимо учитывать, что механизму дробного деления присущи фазовые ошибки, приводящие к повышенному содержанию негармонических спектральных составляющих.

Наиболее эффективным решением вышеописанных проблем является использование метода прямого цифрового синтеза частоты, отличающегося высоким разрешением по частоте и фазе, экстремально быстрой перестройкой по частоте без разрыва фазы и отсутствием необходимости применения точной подстройки опорной частоты.

Наиболее близким по технической сущности к предложенному техническому решению является синтезатор частот (заявка США №2014240004 A1, «Генератор фазо-когерентных сигналов», опубл. 28.08.2014 г., Н03В 21/00), который принят за прототип.

Структурная схема устройства-прототипа приведена на фиг. 1, где введены следующие обозначения:

1 - система фазовой автоподстройки частоты (ФАПЧ);

2 - ответвитель;

3 - делитель тактовой частоты;

4 - схема управления;

5 - микросхема прямого цифрового синтеза (DDS);

6 - устройство фазовой памяти;

7 - счетчик;

8 - умножитель;

9 - регистр частоты;

10 - регистр фазовой отстройки;

11 - первый мультиплексор;

12 - второй мультиплексор;

13 - регистр конфигурации DDS;

14 - формирователь данных;

15 - контроллер;

16 - аккумулятор фазы;

17 - сумматор;

18 - амплитудно-фазовый конвертер;

19 - умножитель DDS;

20 - цифроаналоговый преобразователь;

fCLK - тактовая частота DDS;

fSYS - системная частота схемы управления;

i - номер частоты;

POW - (phase offset word) - инкремент фазы;

FTW - (frequency tuning word) - значение частоты;

PTW - (phase tuning word) - значение фазовой отстройки;

CW - (configuration word) - значение конфигурации DDS;

IP - (instantaneous phase) - мгновенное значение фазы;

FOUT - выходной сигнал синтезатора частот.

Синтезатор частот содержит последовательно соединенные систему ФАПЧ 1 и ответвитель 2, один выход которого через делитель тактовой частоты 3 подключен к схеме управления 4 на базе программируемой логической схемы (ПЛИС), а другой - напрямую подключен к DDS 5. Схема управления 4 включает в себя устройство фазовой памяти 6, организованное в виде счетчика 7, умножителя 8, параллельно соединенных наборов регистров частот 9 и регистров фазовой отстройки 10, а также первого 11 и второго 12 мультиплексоров, и регистр конфигурации DDS 13, выход которого соединен с одним входом формирователя данных 14. При этом выходы регистров фазовой отстройки 10 из каждого набора подключены к входам первого мультиплексора 11, выход которого соединен с умножителем 8, а выходы регистров частоты 9 из каждого набора подключены к входам второго мультиплексора 12, выход которого соединен с одним из входов формирователя данных 14. Другой вход формирователя данных 14 соединен с выходом умножителя 8.

DDS 5 содержит последовательно соединенные контроллер 15, аккумулятор фазы 16, сумматор 17, амплитудно-фазовый конвертер 18, умножитель DDS 19 и цифроаналоговый преобразователь 20, выход которого является выходом синтезатора частот. При этом выход формирователя данных 14 схемы управления 4 подключен к входу контроллера 15 DDS 5, а выходы контроллера 15 подключены к входам аккумулятора фазы 16, сумматора 17 и умножителя DDS 19.

Устройство-прототип работает следующим образом.

На вход системы ФАПЧ 1 подается низкочастотный сигнал опорной частоты, который преобразуется в СВЧ-сигнал fCLK. С выхода системы ФАПЧ 1 сигнал fCLK поступает на ответвитель 2, который разделяет этот сигнал по мощности. Одна часть разделенного СВЧ-сигнала поступает на вход делителя тактовой частоты 3, а другая часть - на вход DDS 5, где тактовый сигнал fCLK разветвляется и подается на входы контроллера 15, аккумулятора фазы 16 и цифроаналогового преобразователя 20. При получении СВЧ-сигнала DDS 5 запускается и ожидает команд от схемы управления 4. В то же время делитель тактовой частоты 3 перестраивает полученный СВЧ-сигнал по частоте и подает последовательность тактовых импульсов системной частоты fSYS (fSYS= fCLK/K, где fSYS - системная частота, K - коэффициент деления), на счетчик 7 устройства фазовой памяти 6 и на один из входов формирователя данных 14, запуская схему управления 4. Счетчик 7 начинает накапливать тактовые импульсы и через каждый такт (1 такт = 1 период сигнала fSYS) выдает накопленное значение в виде двоичного кода на умножитель 8. В это же время на входы первого 11 и второго 12 мультиплексоров подается сигнал выбора частоты (i - порядковый номер частоты).

Первый мультиплексор 11 обрабатывает полученный сигнал и «выбирает» из набора регистров нужный регистр фазовой отстройки 10 в соответствии со значением номера частоты i. Соответствующее значение инкремента фазы POWi в виде двоичного кода с выхода выбранного регистра фазовой отстройки 10 поступает на один из входов первого мультиплексора 11, а затем подается на умножитель 8, где и перемножается с накопленным в счетчике 7 значением. В результате перемножения формируется значение фазовой отстройки PTWi для заданной частоты, которое поступает на вход формирователя данных 14.

Второй мультиплексор 12 также обрабатывает полученный сигнал и «выбирает» из набора регистров нужный регистр частоты 9 в соответствии со значением номера частоты i. Соответствующее значение частоты FTWi в виде двоичного кода с выхода выбранного регистра частоты 9 поступает на один из входов второго мультиплексора 12, а затем подается на другой вход формирователя данных 14.

На свободный вход формирователя данных 14 из регистра конфигурации DDS 13 подается значение конфигурации DDS CW (начальные условия работы DDS: форма выходного сигнала, режим генерации сигнала и т.д.) в виде двоичного кода.

Формирователь данных 14 обрабатывает полученные данные (PTWi, FTWi и CW) и выдает сигнал сброса (RESET) на вход контроллера 15, обнуляя все регистры DDS 5, в целях исключения наложения записываемых данных на остаточные. После этого формирователь данных 14 отправляет накопленные данные о значениях фазовой отстройки, частоты и конфигурации DDS на контроллер 15 DDS 5.

Контроллер 15 анализирует полученные кодовые последовательности (значения фазовой отстройки, частоты и конфигурации DDS) и записывает эти данные во внутренние регистры аккумулятора фазы 16 по фронту тактовой частоты fCLK.

Аккумулятор фазы 16 складывает соответствующее значение частоты FTWi с собственным внутренним значением (в двоичном коде) и в каждый такт выдает результат сложения IP, являющийся мгновенным значением фазы в двоичном коде, на сумматор 17. При этом этот же результат сложения IP посредством обратной связи подается на второй вход аккумулятора фазы 16 и вновь складывается с тем же заданным соответствующим значением частоты FTWi. Процесс сложения длится непрерывно, пока работает синтезатор частот. На другой вход сумматора 17 контроллером 15 подается значение фазовой отстройки PTWi, которое складывается с мгновенным значением фазы IP.

С выхода сумматора 17 отстроенное значение фазы в виде двоичного кода подается на вход амплитудно-фазового конвертера 18. Конвертер 18 выбирает значение функции синуса в соответствии с полученным значением фазы и выдает амплитудное значение синуса на вход умножителя DDS 19, на другой вход которого с выхода контроллера 15 подается масштабирующий коэффициент амплитуды ATW.

С выхода умножителя DDS 19 отмасштабированное по амплитуде значение сигнала в цифровом виде поступает на цифроаналоговый преобразователь 20, который преобразует это значение в аналоговый вид и выдает на выход DDS 5 сигнал FOUT синусоидальной формы.

Недостатком вышеописанного синтезатора частот является сложный алгоритм тактирования применяемых микросхем, требующий применения дополнительных схемных компонентов - ответвителя и делителя тактовой частоты. Плата синтезатора частот прототипа имеет достаточно большие размеры.

Недостатком также является финитный (конечный) характер когерентности синтезируемых частот, определяемый разрядностью используемого в устройстве фазовой памяти счетчика. По достижении заданного разрядностью значения счетчик обнуляется, происходит потеря полезной информации в виде значений фазовой отстройки, что приводит к рассогласованности частот на выходе синтезатора. Отсутствие когерентности частот на выходе синтезатора приведет к тому, что при дальнейшей обработке сигнала в приемопередающем тракте бортовой РЛС будет накапливаться ошибка. В результате точность определения параметров целевых объектов бортовой РЛС снизится.

Недостатком вышеописанного синтезатора также является применение аппаратного сброса всех регистров микросхемы DDS, вследствие которого процесс синтеза частоты прекращается на время перезаписи необходимых регистров. Т.е. происходит молчание схемы на некоторый период и, таким образом, уменьшается время полезной работы всего синтезатора частот, что также приводит к снижению точности определения параметров целевых объектов бортовой РЛС.

Предлагаемое техническое решение направлено на устранение вышеперечисленных недостатков. Технический результат заключается в обеспечении высокой точности определения параметров целевых объектов бортовыми РЛС и уменьшении массогабаритных характеристик приемопередающего тракта всей бортовой РЛС за счет оптимизации структуры синтезатора частот.

Технический результат достигается тем, что синтезатор частот, содержащий систему фазовой автоподстройки частоты, микросхему прямого цифрового синтеза (DDS), состоящую из последовательно подключенных контроллера, аккумулятора фазы с обратной связью, сумматора, амплитудно-фазового конвертера, умножителя DDS и цифроаналогового преобразователя, при этом выходы контроллера подключены к аккумулятору фазы, сумматору и умножителю DDS соответственно, и схему управления, включающую в себя устройство фазовой памяти, состоящее из параллельно включенных наборов регистров фазовой отстройки и регистров частоты и первого и второго мультиплексоров, свободные входы которых предназначены для приема значений порядкового номера частоты, а выход каждого регистра частоты подключен к соответствующим входам второго мультиплексора, формирователь данных, один вход которого соединен с выходом первого мультиплексора, а другой его вход соединен с регистром конфигурации DDS, при этом выход формирователя данных является выходом схемы управления и подключен к входу контроллера DDS, отличается тем, что устройство фазовой памяти содержит параллельно соединенные сумматоры с обратной связью, входы которых подключены к соответствующим регистрам фазовой отстройки, а выход каждого сумматора подключен к соответствующим входам первого мультиплексора, при этом DDS содержит генератор синхроимпульсов, подключенный к тактовому входу схемы управления, и сообщается с каждым сумматором устройства фазовой памяти.

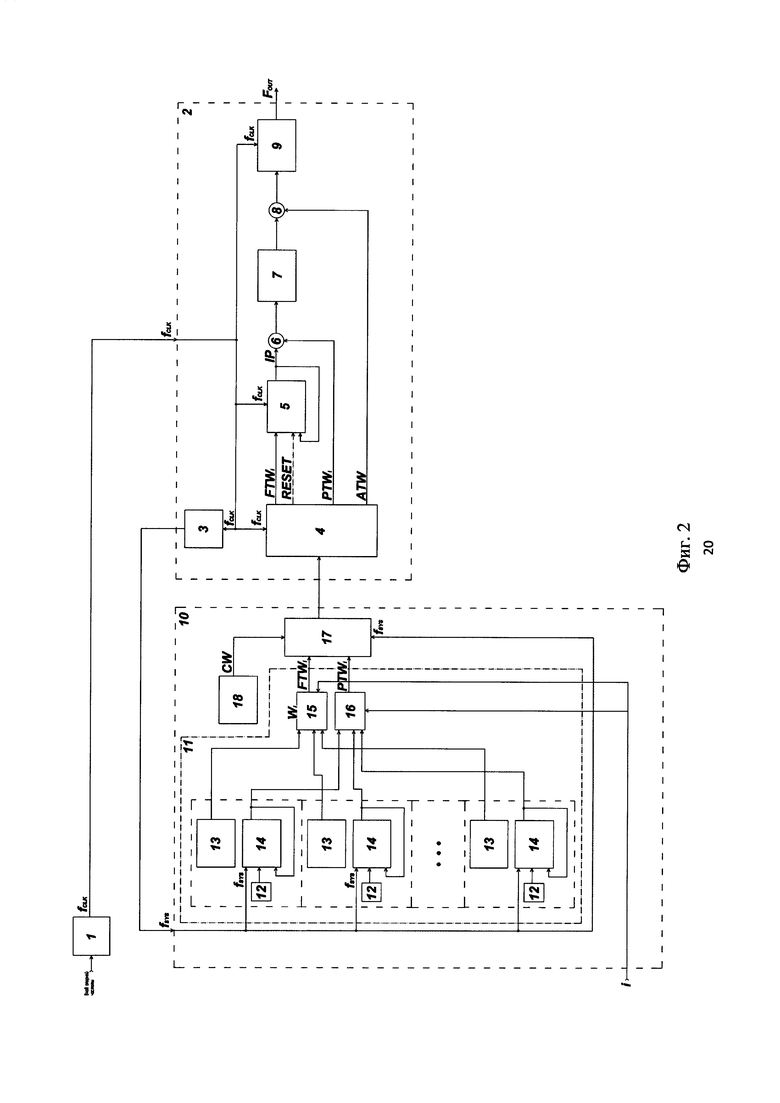

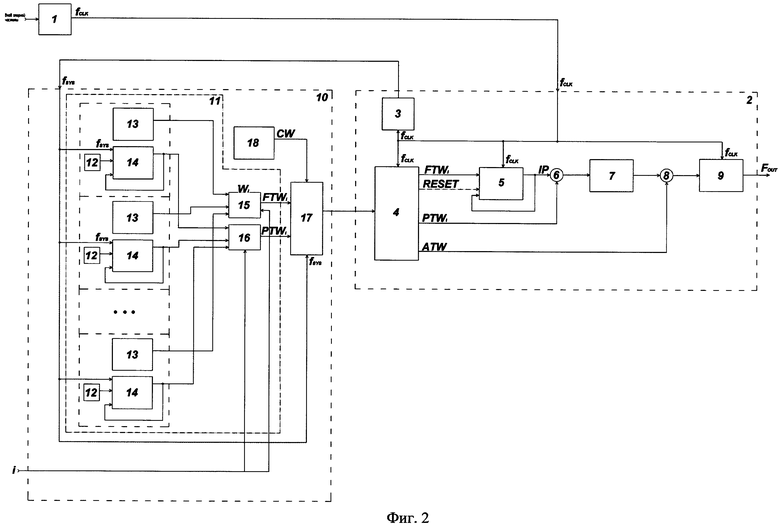

Структурная схема предлагаемого синтезатора частот приведена на фиг. 2, где введены следующие обозначения:

1 - система фазовой автоподстройки частоты (ФАПЧ);

2 - микросхема прямого цифрового синтеза (DDS);

3 - генератор синхроимпульсов;

4 - контроллер;

5 - аккумулятор фазы;

6 - сумматор;

7 - амплитудно-фазовый конвертер;

8 - умножитель DDS;

9 - цифроаналоговый преобразователь

10 - схема управления;

11 - устройство фазовой памяти;

12 - регистр фазовой отстройки;

13 - регистр частоты;

14 - сумматор;

15 - первый мультиплексор;

16 - второй мультиплексор;

17 - формирователь данных;

18 - регистр конфигурации DDS.

fCLK - тактовая частота DDS;

fSYS - системная частота схемы управления; i - номер частоты;

POW - (phase offset word) - инкремент фазы;

FTW - (frequency timing word) - значение частоты;

PTW - (phase tuning word) - значение фазовой отстройки;

CW - (configuration word) - значение конфигурации DDS;

IP - (instantaneous phase) - мгновенное значение фазы;

FOUT - выходной сигнал синтезатора частот.

Синтезатор частот содержит систему фазовой автоподстройки частоты (ФАПЧ) 1, выход которой подключен к тактовому входу микросхемы прямого цифрового синтеза (DDS) 2.

DDS 2 включает в себя генератор синхроимпульсов 3, последовательно подключенные контроллер 4, аккумулятор фазы 5 в виде накапливающего сумматора с обратной связью, сумматор 6, амплитудно-фазовый конвертер 7, представляющий собой постоянное запоминающее устройство (ПЗУ), в котором записаны табличные значения одного периода функции синуса, и предусмотренный для обработки кода фазы, умножитель DDS 8 и цифроаналоговый преобразователь 9 для преобразования выбранного по амплитуде значения сигнала из цифрового вида в аналоговый и выдачи преобразованного сигнала FOUT синусоидальной формы на выход DDS, являющийся выходом всего синтезатора частот.

Синтезатор частот также содержит схему управления 10, организованную на базе ПЛИС. Схема управления 10 включает в себя устройство фазовой памяти 11, представляющее собой параллельно включенные наборы регистров фазовой отстройки 12, регистров частоты 13 и сумматоров 14 с обратной связью для каждой частоты, при этом выход каждого регистра фазовой отстройки 12 соединен с входом соответствующего сумматора 14, и первый 15 и второй 16 мультиплексоры, формирователь данных 17 и регистр конфигурации DDS 18, задающий начальные условия работы DDS 2. Выходы каждого регистра частоты 13 подключены к соответствующим входам первого 15 мультиплексора, а выходы каждого сумматора 14 подключены к соответствующим входам второго 16 мультиплексора. Выходы мультиплексоров 15 и 16 подключены к входам формирователя данных 17. Выход формирователя данных 17 является выходом схемы управления 10 и подключен к входу контроллера 4 DDS 2. Тактовый вход схемы управления 10 подключен к выходу генератора синхроимпульсов 3 DDS 2.

Устройство работает следующим образом.

На вход системы ФАПЧ 1 подается низкочастотный сигнал опорной частоты, который преобразуется в СВЧ-сигнал fCLK. С выхода системы ФАПЧ 1 сигнал fCLK подается на тактовый вход схемы DDS 2 и, разветвляясь, поступает на входы контроллера 4, аккумулятора фазы 5, цифроаналогового преобразователя 9 и генератора синхроимпульсов 3. При получении сигнала fCLK генератор синхроимпульсов 3 формирует системную тактовую частоту fSYS и подает последовательность импульсов на тактовый вход схемы управления 10, запуская ее. Системная частота fSYS подается на входы каждого сумматора 14 устройства фазовой памяти 11 и на один из входов формирователя данных 17. На другие входы сумматоров 14 подаются соответствующие данному набору значения инкрементов фазы POWi в виде двоичных кодов.

Значения инкрементов фазы POWi являются заранее вычисленными по формуле значениями для каждого значения частоты FTWi и хранятся в соответствующих регистрах фазовой отстройки 12:

где

i - порядковый номер частоты, соответствующий значению частоты, записанной в регистре частоты (i=1, 2 …, N);

POWi - значение инкремента фазы соответствующего регистра фазовой отстройки в двоичном коде;

FTWi - значение частоты соответствующего регистра частоты в двоичном коде;

fCLK - значение тактовой частоты, подаваемой на DDS;

fSYS - значение системной частоты, подаваемой на схему управления.

Значения FTWi регистров частоты являются программно заданными и вычисленными по формуле исходя из значений частот FOUT, синтезируемых DDS:

где

FOUTi- значение i-й частоты, синтезируемой DDS.

Каждый сумматор 14 складывает соответствующее значение инкремента фазы POWi с собственным внутренним значением и в каждый такт выдает результат сложения PTWi, являющийся значением фазовой отстройки в виде двоичного кода, на соответствующий выход второго мультиплексора 16. При этом результат сложения PTWi посредством обратной связи подается на другой вход сумматора 14 и вновь складывается с тем же заданным соответствующим значением инкремента фазы POWi. Процесс сложения длится непрерывно, пока работает синтезатор частот.

На свободный вход второго мультиплексора 16 подается сигнал выбора частоты (i - порядковый номер частоты), на основании которого мультиплексор 16 выбирает соответствующий набор регистров фазовой отстройки 12 и сумматоров 14 (например, i=1, выбирается 1-й набор) и подает значение фазовой отстройки PTWi из выбранного набора на вход формирователя данных 17.

На свободный вход первого мультиплексора 15 также подается сигнал выбора частоты, на основании которого мультиплексор 15 выбирает соответствующий набор регистров частоты 13 и подает значение частоты FTWi из выбранного набора на вход формирователя данных 17.

На свободный вход формирователя данных 17 поступает значение конфигурации DDS CW (начальные условия работы DDS: форма выходного сигнала, режим генерации сигнала и т.д.), хранящееся в регистре конфигурации DDS 18.

Формирователь данных 17 обрабатывает полученные данные (PTWi, FTWi и CW) и посылает накопленные значения фазовой отстройки PTWi, частоты FTWi и конфигурации DDS CW на вход контроллера 4 DDS 2. Отправка данных формирователем 17 осуществляется по фронту системной частоты fSYS.

Контроллер 4 анализирует полученные значения, посылает сигнал сброса (RESET) на аккумулятор фазы 5, обнуляя его внутренние регистры, задает условия работы DDS 2 и затем записывает во внутренние регистры аккумулятора фазы 5, сумматора 6 и умножителя DDS 8 значения частоты FTWi, фазовой отстройки PTWi и амплитуды ATW соответственно.

Аккумулятор фазы 5 складывает полученное значение частоты FTWi с собственным внутренним значением и в каждый такт выдает результат сложения IP, являющийся мгновенным значением фазы в виде двоичного кода, на сумматор 6. При этом мгновенное значение фазы IP посредством обратной связи подается на другой вход аккумулятора фазы 5 и вновь складывается со значением частоты FTWi. Процесс сложения длится непрерывно, пока работает синтезатор частот. На другой вход сумматора 6 с выхода контроллера 4 подается значение фазовой отстройки PTWi, которое складывается с мгновенным значением фазы IP.

С выхода сумматора 6 отстроенное значение фазы в виде двоичного кода подается на вход амплитудно-фазового конвертера 7. Конвертер 7 выбирает значение функции синуса в соответствии с полученным значением фазы и выдает амплитудное значение синуса на вход умножителя DDS 8, на другой вход которого с выхода контроллера 4 подается масштабирующий коэффициент амплитуды ATW.

С выхода амплитудно-фазового конвертера 7 отмасштабированное значение сигнала в цифровом виде поступает на цифроаналоговый преобразователь 9, который преобразует это значение в аналоговый вид и выдает на выход DDS 2, являющийся выходом синтезатора частот, сигнал FOUT синусоидальной формы.

Для построения схемы управления возможно использование ПЛИС фирм Altera и Xilinx (к примеру, EP3C5E144I7N, EP3C25E144I7N, EP3C120F484I7N, EP4CE115F23I7N, EP4CGX150CF23I7N и т.д.). Для построения микросхемы прямого цифрового синтеза (DDS) возможно использование микросхем фирмы Analog Devices (к примеру, AD9914BCPZ, AD9915BCPZ). В качестве системы ФАПЧ возможно использование микросхем фирм Analog Devices, Hittite (к примеру, HMC440QS16G, HMC830PL6GE, HMC833LP6GE, ADF4350BCPZ и т.д.).

Для реализации настоящего изобретения применяется схема прямого цифрового синтеза частот серии AD9914, содержащая генератор синхроимпульсов. Генератор синхроимпульсов необходим для синхронизации момента запуска нескольких микросхем, используемых в синтезаторе частот. В заявленном синтезаторе применяется всего одна схема DDS, а выход генератора синхроимпульсов подключается к тактовому входу схемы управления. Тактовые импульсы генератора запускают схему управления. Такое подключение позволяет отказаться от использования дополнительных электронных компонентов в схеме синтезатора частот (в частности, ответвителя и делителя тактовых импульсов) и, тем самым, уменьшить массогабаритные параметры платы синтезатора частот и приемопередающего тракта всей БРЛС соответственно.

Организация устройства фазовой памяти схемы управления в виде набора сумматоров с обратной связью позволяет избежать потери полезной информации в виде значений фазовой отстройки. Это достигается тем, что сумматор свободен от обнуления, т.е. он может складывать значения фазовой отстройки для каждой частоты бесконечно долго без потери информации об остатке фазы. Таким образом, синтез частоты на протяжении всего времени работы устройства происходит непрерывно без разрыва фазы, что способствует улучшению когерентности сигнала в синтезаторе частот. Благодаря этому качество обработки сигнала в приемопередающем тракте БРЛС повышается, и БРЛС может определять различные параметры целевых объектов БРЛС с высокой точностью.

Также высокая точность определения параметров целевых объектов БРЛС достигается применением программного сброса в микросхеме DDS. В отличие от аппаратного сброса, применяемого в прототипе и обнуляющего все регистры микросхемы, программный сброс при появлении сигнала об обновлении данных обнуляет только аккумулятор фазы DDS, т.к. для синтеза когерентных частот необходимо контролировать только значение фазы, т.е. обнуление всех регистров DDS не требуется. Это позволяет DDS синтезировать старую частоту во время записи в него новых данных. Таким образом, время переключения синтезатора между частотами сокращается из-за отсутствия периода молчания схемы после сброса, что позволяет непрерывно обрабатывать сигнал в приемопередающем тракте БРЛС.

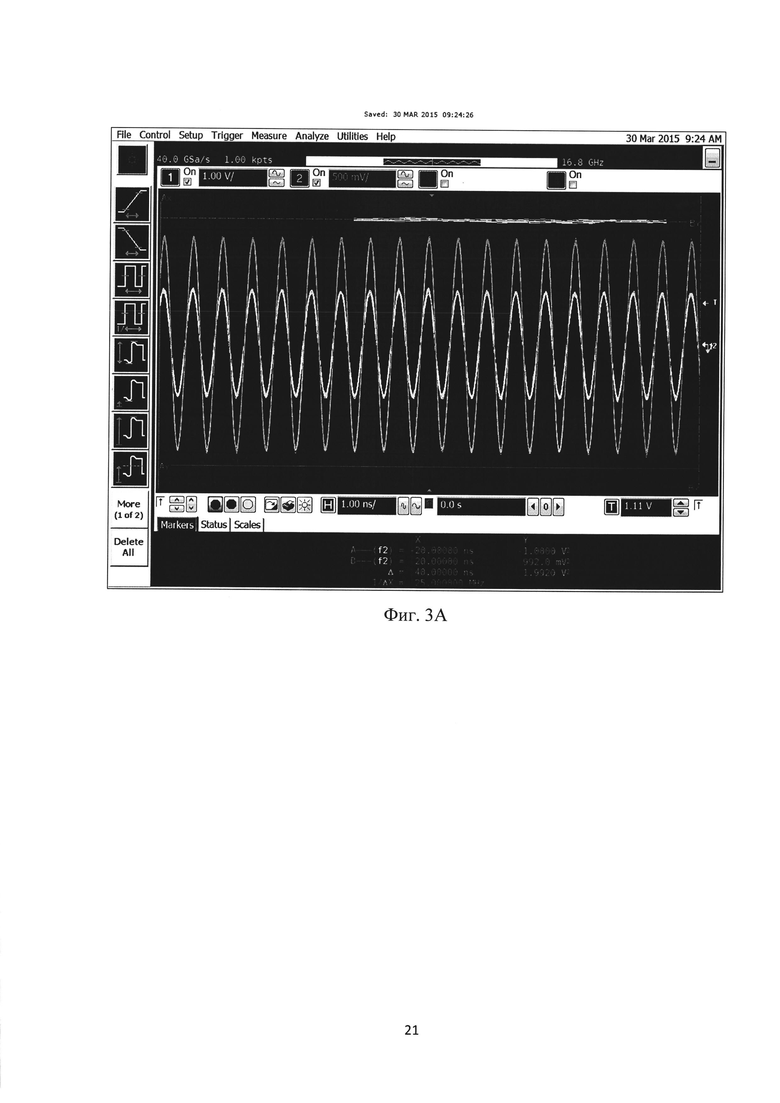

На фиг. 3 приведены графики выходных сигналов эталонного и испытуемого синтезаторов частот. При проверке синтезатора частот производился одновременный запуск двух синтезаторов на одинаковых частотах. Каждый синтезатор подключался к одному из каналов осциллографа, синхронизированного по фронту одного из синтезаторов (эталонного), относительно которого измерялась начальная фаза «испытуемого» синтезатора. Развертку осциллографа настроили так, чтобы можно было различать сигналы двух синтезаторов: поменяли амплитудную развертку испытуемого синтезатора (график большей амплитуды) относительно эталонного (график меньшей амплитуды) так, чтобы его амплитуда была в два раза больше амплитуды другого (фиг. 3А, время операции 09:24:56). Затем меняли частоту испытуемого синтезатора, при этом, поскольку осциллограф синхронизирован по фронту сигнала от другого синтезатора, график начинал «дрожать» (фиг. 3Б, время операции 09:25:24). После этого частоту испытуемого синтезатора снова переключали на прежнюю. Сигнал синтезатора при этом «вставал» на прежние значения начальной фазы относительно сигнала эталонного синтезатора (фиг. 3В, время операции 09:25:56).

Испытания показали, что при переключении частот сигналы синтезатора частот в разные моменты времени остаются когерентными. Благодаря этому качество обработки сигнала в приемопередающем тракте БРЛС повышается, и БРЛС может определять различные параметры целевых объектов БРЛС с высокой точностью.

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор с низким уровнем фазовых шумов | 2024 |

|

RU2830675C1 |

| СПОСОБ ГЕНЕРАЦИИ ВЫХОДНОЙ ЧАСТОТЫ ЦИФРОВОГО СИНТЕЗАТОРА ПРЯМОГО СИНТЕЗА | 2012 |

|

RU2504891C1 |

| ЦИФРОВОЙ МОДЕМ КОМАНДНОЙ РАДИОЛИНИИ ЦМ КРЛ | 2013 |

|

RU2548173C2 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ СЛОЖНЫХ СИГНАЛОВ | 2020 |

|

RU2749996C1 |

| ГЕНЕРАТОР СИНУСОИДАЛЬНОГО СИГНАЛА | 2014 |

|

RU2568391C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТЫ | 2022 |

|

RU2793776C1 |

| ЦИФРОВОЙ ПРИЕМНИК СПУТНИКОВОЙ НАВИГАЦИИ | 1995 |

|

RU2090902C1 |

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ЗАЩИТЫ ИНФОРМАЦИИ В СЕТЯХ СВЯЗИ | 2005 |

|

RU2295195C1 |

| РАДИОТЕЛЕФОННАЯ СИСТЕМА ДЛЯ ГРУПП УДАЛЕННЫХ АБОНЕНТОВ | 2004 |

|

RU2341038C2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

Изобретение относится к синтезатору частот. Технический результат заключается в повышении точности определения параметров целевых объектов бортовыми РЛС и в уменьшении массогабаритных характеристик приемопередающего тракта всей бортовой РЛС за счет оптимизации структуры синтезатора частот. Синтезатор содержит систему фазовой автоподстройки частоты, микросхему прямого цифрового синтеза (DDS), состоящую из последовательно подключенных контроллера, аккумулятора фазы с обратной связью, сумматора, амплитудно-фазового конвертера, умножителя DDS и цифроаналогового преобразователя, схему управления, включающую в себя устройство фазовой памяти, состоящее из параллельно включенных наборов регистров фазовой отстройки и регистров частоты и первого и второго мультиплексоров, формирователь данных, при этом устройство фазовой памяти содержит параллельно соединенные сумматоры с обратной связью, а DDS содержит генератор синхроимпульсов. 5 ил.

Синтезатор частот, содержащий систему фазовой автоподстройки частоты, микросхему прямого цифрового синтеза (DDS), состоящую из последовательно подключенных контроллера, аккумулятора фазы с обратной связью, сумматора, амплитудно-фазового конвертера, умножителя DDS и цифро-аналогового преобразователя, при этом выходы контроллера подключены к аккумулятору фазы, сумматору и умножителю DDS соответственно, и схему управления, включающую в себя устройство фазовой памяти, состоящее из параллельно включенных наборов регистров фазовой отстройки и регистров частоты и первого и второго мультиплексоров, свободные входы которых предназначены для приема значений порядкового номера частоты, а выход каждого регистра частоты подключен к соответствующим входам второго мультиплексора, формирователь данных, один вход которого соединен с выходом первого мультиплексора, а другой его вход соединен с регистром конфигурации DDS, при этом выход формирователя данных является выходом схемы управления и подключен к входу контроллера DDS, отличающийся тем, что устройство фазовой памяти содержит параллельно соединенные сумматоры с обратной связью, входы которых подключены к соответствующим регистрам фазовой отстройки, а выход каждого сумматора подключен к соответствующим входам первого мультиплексора, при этом DDS содержит генератор синхроимпульсов, подключенный к тактовому входу схемы управления, и сообщается с каждым сумматором устройства фазовой памяти.

| СПОСОБ ГЕНЕРАЦИИ ВЫХОДНОЙ ЧАСТОТЫ ЦИФРОВОГО СИНТЕЗАТОРА ПРЯМОГО СИНТЕЗА | 2012 |

|

RU2504891C1 |

| Устройство для защиты машин постоянного тока | 1950 |

|

SU90915A1 |

| US 5467294 A1, 14.11.1995 | |||

| Способ защиты переносных электрических установок от опасностей, связанных с заземлением одной из фаз | 1924 |

|

SU2014A1 |

| US 4951004 A1, 21.08.1990. | |||

Авторы

Даты

2016-09-10—Публикация

2015-05-13—Подача