ОБЛАСТЬ ТЕХНИКИ

[0001] Настоящее изобретение относится к области создания запоминающих устройств и взаимодействию с ними, в частности к способу и системе чтения состояния ячейки магниторезистивной памяти с переносом спина (STT-MRAM, англ. Spin-Transfer Torque RAM).

УРОВЕНЬ ТЕХНИКИ

[0002] Для чтения состояния ячеек памяти STT-RAM прилагают небольшое напряжение и/или задают небольшой ток чтения через ячейку. При этом сравнивают значение полученного тока и/или падения напряжения на ячейке с опорным уровнем, устанавливая, таким образом, состояние ячейки «0» или «1». Аналогичным способом происходит запись или стирание ячейки, но с большим значением прилагаемого напряжения и/или тока. Вероятность переключения ячейки при напряжениях много меньших напряжения записи мала, но отлична от нуля и экспоненциально зависит от величины напряжения. Таким образом, существует конечная вероятность, что ячейка переключится при напряжении чтения. Это нежелательное событие называется «возмущение чтением» (англ. Read Disturb), вероятность соответствующего события при однократном чтении называется вероятностью возмущения чтением (Read Disturb Rate). Для функционирования памяти необходимо уменьшить вероятность возмущения чтением до 10-24 или, при применении схем коррекции ошибок, до 10-12. В реальных структурах, однако она может принимать большие значения (A.V. Khvalkovskiy et al., J. Phys. D: Appl. Phys. 46 (2013) 074001).

[0003] Из патента US 8107280 (Qualcomm Inc, 31.01.2012) известен классический подход к построению схем считывания состояния ячеек хранения. В данной схеме считывания присутствует усилитель считывания и блок опорного сигнала. При считывании через MTJ (магнитный туннельный переход) ячейки памяти задается ток смещения i_rd. К примеру, при номинальных состояниях высокого и низкого уровней сопротивления 1 кОм и 3 кОм может быть необходимо задать ток i_rd около 100 мкА для достижения напряжений 100 и 300 мВ, необходимые для стабильного усиления до логических уровней усилителем считывания. Для многих ячеек такие значения приложенных напряжений и токов приводят к высокому значению вероятности возмущения чтением в 10-5-10-3, для коррекции которой может потребоваться занимающая значительные ресурсы памяти и логики схема коррекции ошибки. Это обуславливает необходимость создания новых схем и приемов считывания ячеек памяти таким образом, чтобы не приводить к переключению состояния ячейки памяти.

РАСКРЫТИЕ ИЗОБРЕТЕНИЯ

[0004] Для решения вышеуказанной технической проблемы предлагается принцип схемы считывания ячеек памяти, который базируется на нескольких факторах, изложенных ниже.

[0005] Во-первых, для магнитной ячейки памяти STT-MRAM существует так называемое время термической релаксации намагниченности t0 - характерное время, за которое магнитное состояние ячейки возвращается к равновесному состоянию при возмущении. Оно составляет, в зависимости от параметров материала, от долей до единиц наносекунды (A.V. Khvalkovskiy et al., J. Phys. D: Appl. Phys. 46 (2013) 074001). При длительности напряжения чтения через ячейку trd значительно превышающим t0 (как правило, больше чем 10t0), вероятность возмущения чтением линейно зависит от времени trd; например при некоторых параметрах ячейки, при уменьшении trd с 60 нс до 50 нс вероятность возмущения чтением может упасть в 1.2 раза. Этот режим называется «чтением в термо-активированном режиме». Однако если время чтения заметно меньше 10t0, то вероятность возмущения чтением экспоненциально зависит от времени trd; например, при некоторых параметрах ячейки, при уменьшении trd с 6 нс до 5 нс вероятность возмущения чтением может упасть больше чем в 10 раз. Этот режим называется «чтением в прецессионном режиме». Таким образом, для минимизации вероятности переключения ячейки желательно прикладывать как можно более короткий импульс считывания, чтобы чтение происходило в прецессионном режиме.

[0006] С другой стороны, для увеличения отношения сигнал-шум и надежного определения состояний high (логической единицы) - low (логического нуля) необходимо, приложить как можно более длинный импульс чтения через MTJ ячейки. В противном случае шумы схемы чтения могут привести к неправильному определению логических состояний ячейки high-low (ошибка схемы).

[0007] Наконец, для каждого логического состояния ячейки, только импульс одной полярности будет приводить к возмущению чтением, а импульс противоположной полярности, наоборот, стабилизирует состояние ячейки.

[0008] В данном изобретении предлагается подход, который, в наиболее полной реализации, использует преимущества всех трех указанных выше технологических особенностей.

[0009] Для этого, в качестве одного решения, предлагается разбить операцию чтения полной длительностью trd на несколько последовательных импульсов, для каждого из которых происходит чтение в прецессионном режиме с последующим коротким импульсом релаксации (в течении которого, на ячейку подается либо нулевое, либо заметно меньшее чем при чтении значение напряжения).

[0010] В качестве развития этого решения, предлагается в качестве импульсов релаксации подавать импульсы с противоположной амплитудой сигнала, при этом интегрировать полученные падения напряжения, учитывая знак прикладываемого воздействия.

[0011] Достигаемый при реализации заявленного изобретения технический результат заключается в значительном уменьшении вероятности возмущения чтением и, таким образом, повышении надежности определения состояний ячеек памяти STT-MRAM, за счет того, что в каждый момент времени на ячейку действует либо импульс чтения с очень малой вероятностью возмущения чтением («чтение в прецессионном» режиме), либо импульс, стабилизирующий исходное магнитное состояние.

[0012] Заявленный результат достигается за счет способа чтения состояния ячейки магниторезистивной памяти с переносом спина STT-MRAM, заключающийся в генерировании сигнала считывания Vrd во время Trd считывания ячейки памяти, причем напряжение сигнала Vrd периодически опускается ниже заданного значения стабилизационного импульса Vlo в заданном временном диапазоне Т2, и выше Vlo, достигая значения Vhi в заданном временном диапазоне T1.

[0013] В одном из частных примеров реализации способа, уровень сигнала Vlo отличается от уровня Vhi по меньшей мере в 1,25 раза.

[0014] В другом частном примере реализации способа Vlo является нулевым сигналом.

[0015] В другом частном примере реализации способа длительность времени нахождения сигнала считывания Vrd ниже значения стабилизационного импульса Vlo приблизительно равно времени термической релаксации Т0.

[0016] В другом частном примере реализации способа T1 составляет от 0.1 нс до 20 нс.

[0017] В другом частном примере реализации способа Т2 составляет от 0.3 нс до 10 нс.

[0018] В другом частном примере реализации способа уровень сигнала Vlo имеет противоположный знак от знака Vhi и отличается по амплитуде.

[0019] Заявленное изобретение также осуществляется с помощью системы чтения состояния ячейки магниторезистивной памяти с переносом спина STT-MRAM, при этом система содержит:

- считываемую ячейку памяти, соединенную с первым и вторым ключами, обеспечивающих переключение знака воздействия на считываемую ячейку;

- генератор сигнала управления знаком воздействия на считываемую ячейку, обеспечивающий формирование управляющих сигналов, определяющих период чтения ячейки памяти с изменяющимся знаком воздействия;

- источник напряжения, соединенный с первым ключом;

- интегратор, соединенный со вторым ключом;

- источник опорного напряжения, обеспечивающий формирование напряжения считывания;

- компаратор, обеспечивающий сравнение напряжения, накопленного на интеграторе, с напряжением источника опорного напряжения;

причем

- генератор сигнала управления знаком воздействия на считываемую ячейку обеспечивает формирование управляющих сигналов, формирующих период чтения ячейки памяти с изменяющимся знаком воздействия за счет переключения первого и второго ключей по сигналу тока воздействия на ячейку памяти.

[0020] В одном из частных примеров реализации система дополнительно содержит шунтирующий ключ, обеспечивающий перевод состояние верхнего контакта ячейки в нулевой уровень.

[0021] В другом частном примере реализации системы источник опорного напряжения содержит группу ключей, обеспечивающих переключение знака воздействия на считываемую ячейку, и ячейки памяти формирующие набор сопротивлений с предопределенными состояниями.

[0022] Заявленное изобретение также осуществляется с помощью еще одного варианта системы чтения состояния ячейки магниторезистивной памяти с переносом спина STT-MRAM, при этом система содержит:

- считываемую ячейку памяти, соединенную с первой и второй группой ключей, обеспечивающих переключение знака воздействия на считываемую ячейку;

- генератор сигнала управления знаком воздействия на считываемую ячейку, обеспечивающий формирование управляющих сигналов, определяющих период чтения ячейки памяти с изменяющимся знаком воздействия;

- источник напряжения, соединенный с первой группой ключей;

- интегратор, соединенный со второй группой ключей;

- источник опорного напряжения, обеспечивающий формирование напряжения считывания;

- компаратор, обеспечивающий сравнение напряжения, накопленного на интеграторе, с напряжением источника опорного напряжения;

причем

- генератор сигнала управления знаком воздействия на считываемую ячейку обеспечивает формирование управляющих сигналов, формирующих период чтения ячейки памяти с изменяющимся знаком воздействия за счет переключения первой и второй группы ключей по сигналу тока воздействия на ячейку памяти.

[0023] В одном из частных примеров реализации системы каждая группа ключей содержит четыре ключа.

[0024] В другом частном примере реализации системы в каждой из группы ключей одна пара ключей замыкается по высокому состоянию управляющего сигнала, а вторая пара - по низкому.

[0025] В другом частном примере реализации системы источник опорного напряжения содержит две группы ключей, обеспечивающих переключение знака воздействия на считываемую ячейку, и ячейки памяти, формирующие набор сопротивлений с предопределенными состояниями.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

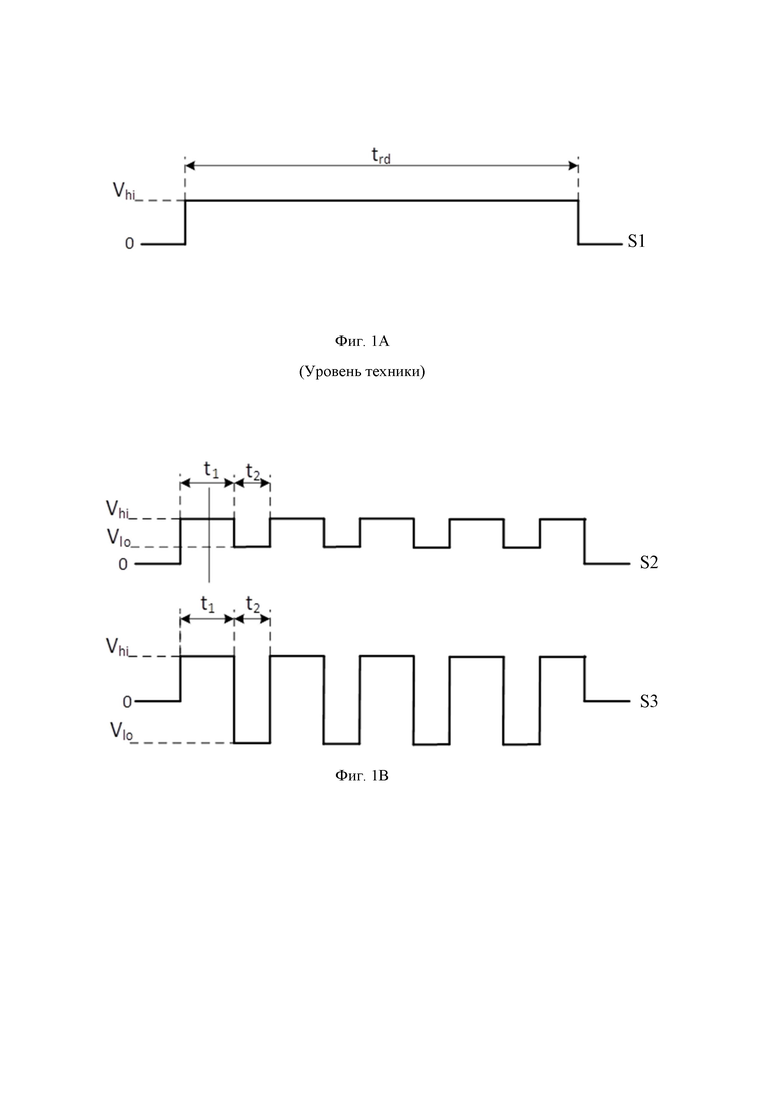

[0026] Фиг. 1А иллюстрирует известную из уровня техники диаграмму сигнала чтения.

[0027] Фиг. 1В иллюстрирует диаграммы сигналов чтения согласно заявленному изобретению.

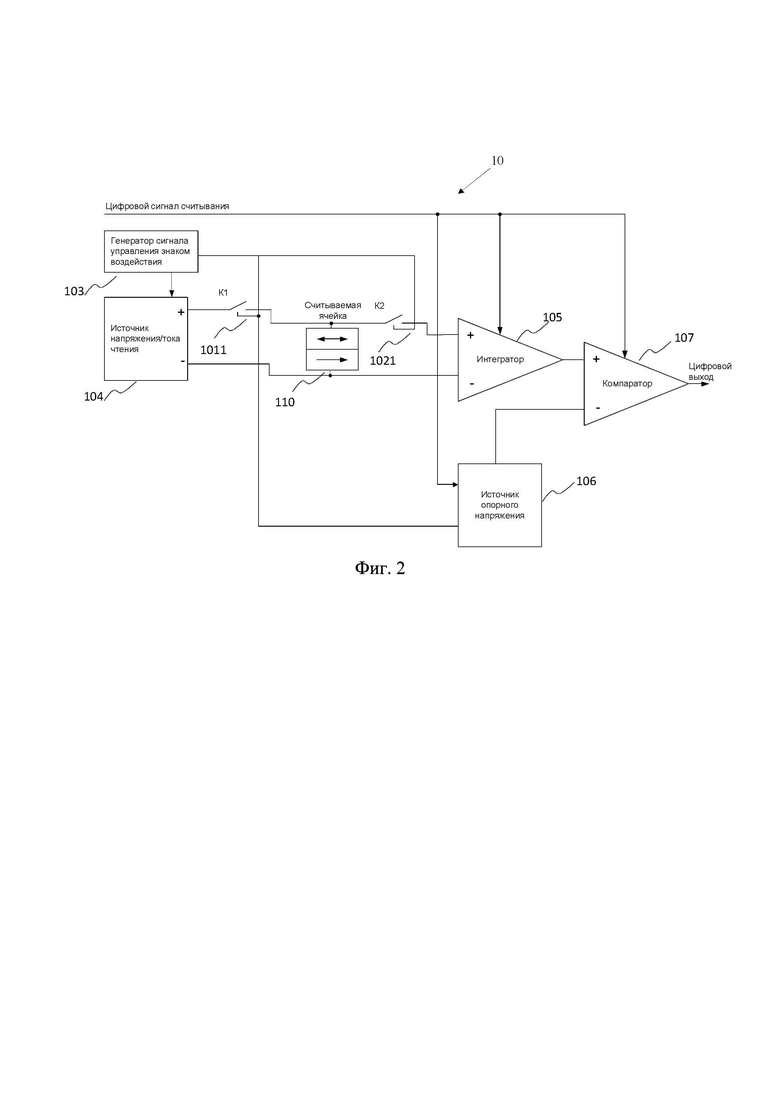

[0028] Фиг. 2 иллюстрирует заявленную схему считывания ячеек памяти.

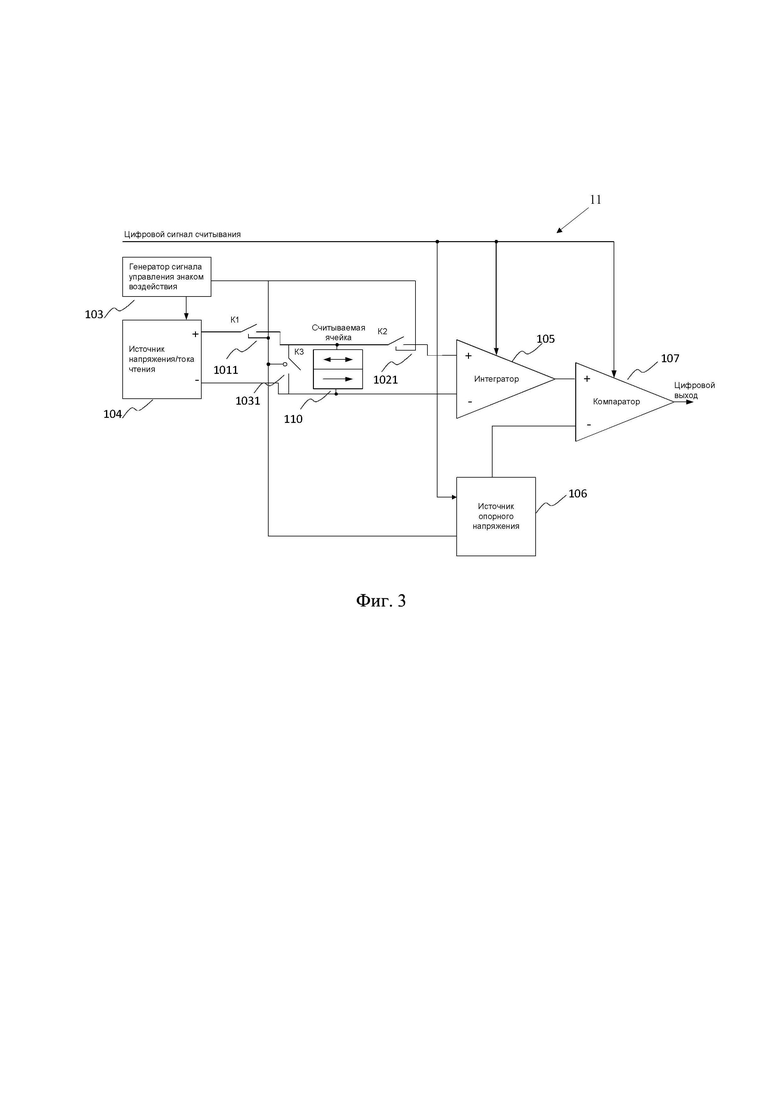

[0029] Фиг. 3 иллюстрирует схему считывания с шунтирующим ключом.

[0030] Фиг. 4 иллюстрирует схему считывания с импульсами релаксации противоположного знака относительно импульсов чтения.

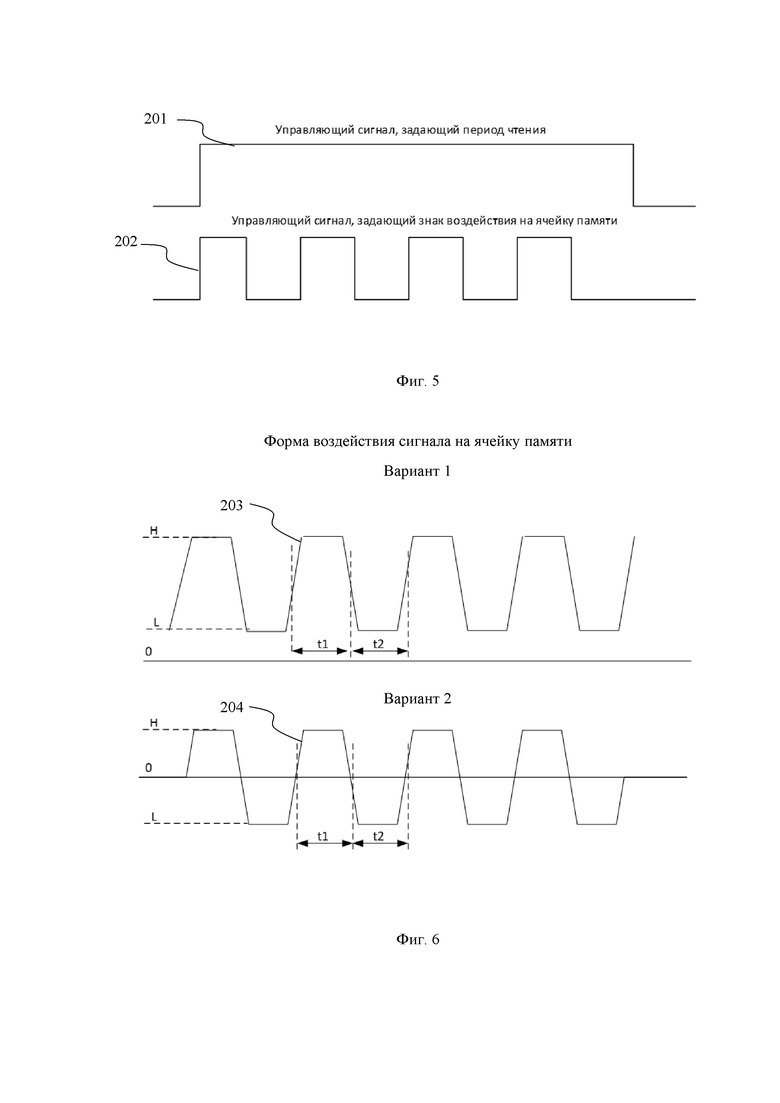

[0031] Фиг. 5 - Фиг. 6 иллюстрируют диаграммы сигналов управления схемой считывания.

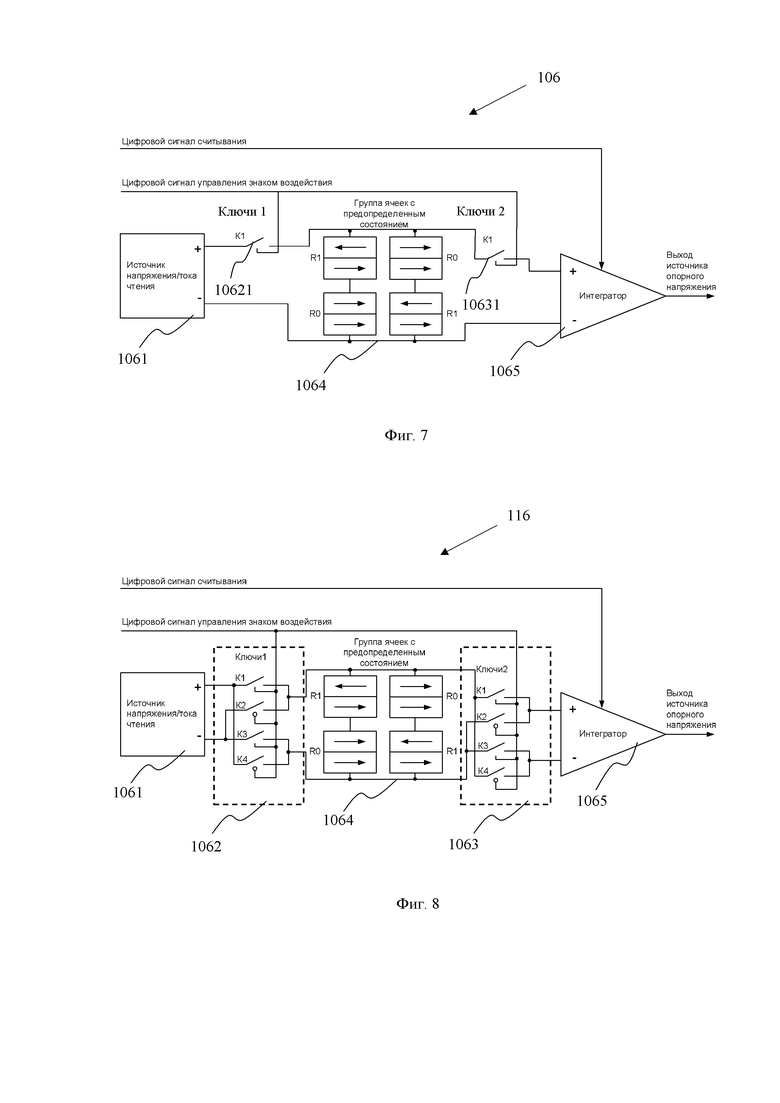

[0032] Фиг. 7 иллюстрирует схему источника опорного напряжения для схемы считывания.

[0033] Фиг. 8 иллюстрирует схему источника опорного напряжения для схемы считывания с импульсами релаксации противоположной амплитуды.

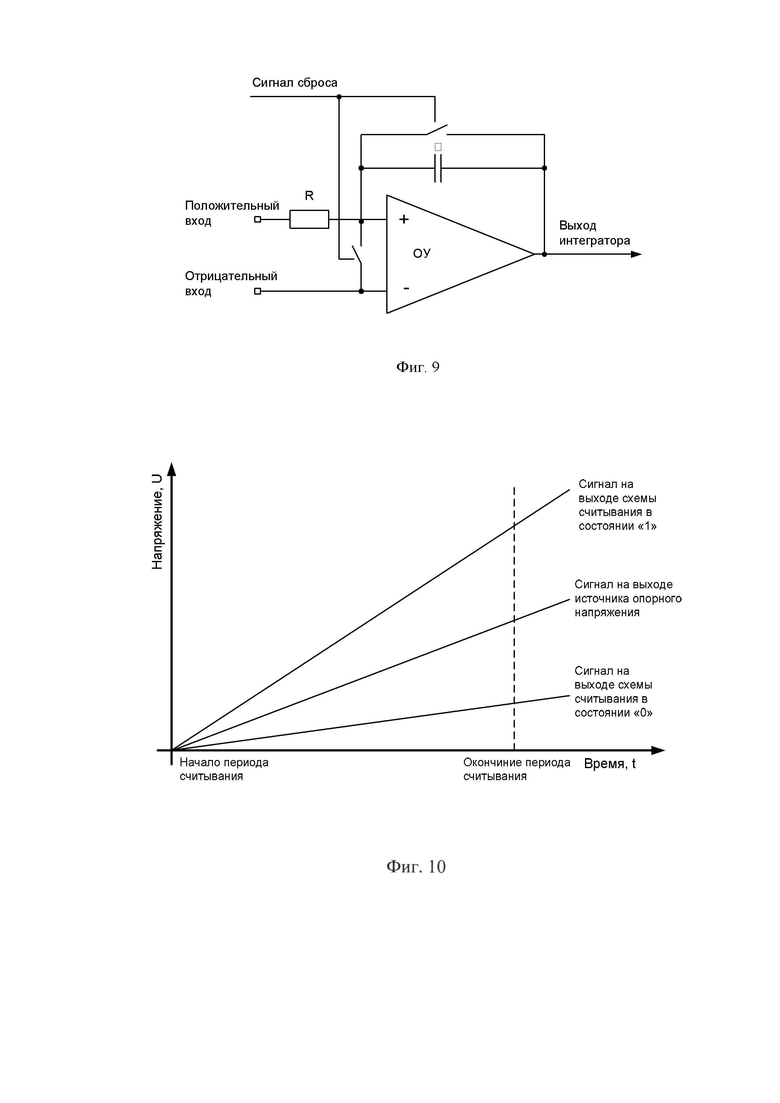

[0034] Фиг. 9 иллюстрирует схему интегратора.

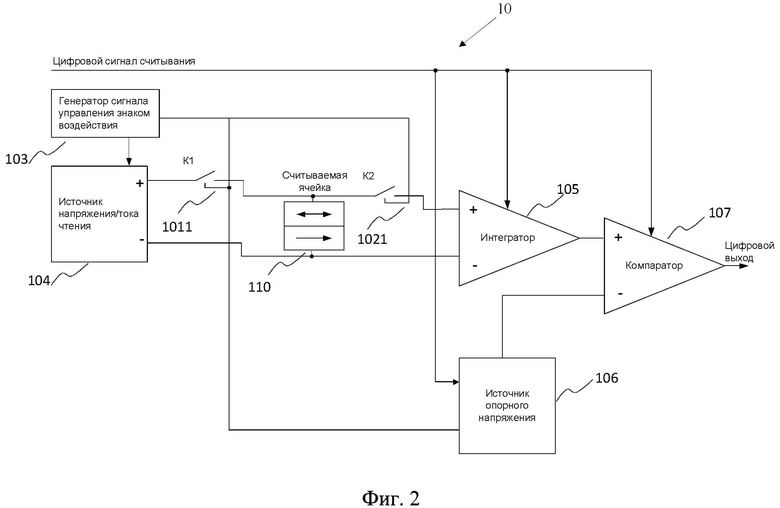

[0035] Фиг. 10 иллюстрирует диаграммы сигналов на выходах интеграторов схемы чтения и источника опорного напряжения.

ОСУЩЕСТВЛЕНИЕ ИЗОБРЕТЕНИЯ

[0036] На Фиг. 1А - Фиг. 1В представлены примеры диаграмм сигналов чтения Vrd. В существующем подходе, известном из уровня техники, представленным на Фиг. 1А, используется непрерывный уровень сигнала S1, равный некоторому постоянному значению Vhi в течении всей длительности операции чтения trd.

[0037] При реализации заявленного изобретения, отображенного на Фиг. 1В, предлагается для сигнала считывания S2 в течение времени считывания состояния ячейки trd, варьировать форму сигнала считывания таким образом, чтобы:

- периодически уровень сигнала Vrd опускался бы ниже некоторого уровня Vlo («стабилизационный импульс»);

- при этом уровень сигнала Vlo стабилизационного импульса являлся бы меньшим, чем уровень сигнала при импульсе чтения Vhi, по крайней мере в 1.25 раз, а иногда и значительно больше (в 2 раза или больше), или же примерно равнялся бы нулевому сигналу;

- длительность импульса чтения tl, в течении которого уровень сигнала чтения достигает уровня сигнала чтения Vhi (выше уровня Vlo), было бы значительно меньше времени 10t0, так, чтобы внутри этого интервала чтение происходило бы в «прецессионном режиме»;

- при этом длительность стабилизационного импульса t2, в течении которого сигнал чтения находится ниже уровня Vlo, было бы порядка времени термической релаксации t0, с тем, чтобы намагниченность успела бы релаксировать до состояния, близкого к равновесному.

[0038] Для большинства материалов, длительность импульса чтения t1 может находиться в диапазоне от 0.5 нс до 10 нс, при этом в некоторых приложениях он может находится в диапазоне от 0.1 нс до 20 нс. При этом чем меньше t1, тем больше выигрыш от применения данной схемы, однако, тем более сложная ее реализация.

[0039] Длительность стабилизационного импульса t2 для большинства материалов должна быть порядка 1-3 нс, при этом в некоторых системах она может варьироваться в диапазоне от 0.3 нс до 10 нс. При этом для слишком коротких стабилизирующих импульсов может не наступить эффект стабилизации магнитного состояния ячейки и упадет эффективность схемы (намагниченность не успевает релаксировать к равновесному значению), а для слишком больших значениях t2 увеличивается шум схемы при фиксированном полном времени операции trd, т.о. также падает ее эффективность.

[0040] В качестве одной из реализаций заявленного изобретения - сигнал S3, уровень сигнала Vlo в стабилизирующем импульсе может иметь знак, противоположный Vhi, а по модулю он не превышает Vhi более чем в 1.25 раз, при этом данный сигнал через ячейку интегрируется, учитывая знак прикладываемого воздействия. Таким образом, ток, текущий в течении стабилизационного импульса, дает такой же вклад в сигнал компаратора, как и ток в течении импульса чтения, как это описывается подробнее ниже.

[0041] Нужно отметить, что полное время считывания trd для сигналов S1, S2, S3 в общем случае разное. Также, в общем случае, значения Vhi и Vlo тоже могут быть разные для сигналов типа S1, S2, S3.

[0042] На Фиг. 2 представлен пример реализации схемы считывания (10) ячейки памяти (110). Источник напряжения/тока считывания (104) используется для формирования напряжения считывания на ячейке (110). Генератор (103) сигнала управления знаком воздействия на считываемую ячейку (110) обеспечивает формирование управляющих сигналов, определяющих период чтения ячейки памяти (110) с изменяющимся знаком воздействия, за счет подключения к источнику напряжения/тока считывания (104). Источник напряжения/тока считывания (104) соединен по одному своему входу с ключом К1 (1011). Второй ключ К2 (1021) присоединен к одному входу интегратора (105). Источник (104) по второму выходу подключен к второму входу интегратора (105) без использования ключей. Компаратор (107) обеспечивает сравнение напряжения, накопленного на интеграторе (105), с напряжением источника опорного напряжения (106). Состояние ячейки (110) определяется фактом превышения накопленного уровня напряжения на входе «+» компаратора (107) над уровнем опорного сигнала на его входе «-».

[0043] На Фиг. 3 представлен вариант реализации схемы считывания (11) с шунтирующим ключом К3 (1031). Ключ К3 замыкается в момент размыкания ключей К1 (1011) и К2 (1021), таким образом переводя состояние верхнего контакта ячейки в нулевой уровень.

[0044] На Фиг. 4 представлен вариант схемы (12) считывания ячейки памяти (110), реализующая сигнал S3 с импульсами релаксации противоположного знака относительно импульсов чтения. В отличии от схем (10) и (11), сигнал генератора управления знаком воздействия (103) переключает группы ключей «Ключи 1» (1071) и «Ключи 2» (1081). Ключи К1 и К3 в каждой из групп Ключей (1071) и (1081) замыкаются по высокому состоянию управляющего сигнала, К2 и К4 - по низкому. Группа ключей «Ключи 2» (1081) соединена с интегратором (105). Группа ключей «Ключи 2» (1081) необходима для того, чтобы на интегратор (105) поступал сигнал положительного знака.

[0045] Компаратор (107) обеспечивает сравнение напряжения, накопленного на интеграторе (105), с напряжением источника опорного напряжения (116). Состояние ячейки (110) определяется фактом превышения накопленного уровня напряжения на входе «+» компаратора (107) над уровнем опорного сигнала на его входе «-».

[0046] На Фиг. 5 представлены формы управляющих сигналов, а на Фиг. 6 - результирующие формы сигнала воздействия на ячейку (110). Сигнал (201) задает полную длительность изменяющегося воздействия (203/204) на ячейку (110), таким образом, он определяет период чтения (trd). Генератор (103) формирует сигнал (202). Сигнал (202) управляет ключами К1, К2 в схеме (10) (Фиг. 2) и другими представленными схемами ключей, задавая импульсы чтения (t1) и релаксации (t2) на ячейку памяти (110). Сигналы (203) и (204) являются примерами результирующей формы воздействия на считываемую ячейку (110). Отличием сигнала (203) от сигнала (204) является переход сигнала (203) в отрицательную область напряжений, тогда как сигнал (204) имеет существенно отличные от нуля значения только одного знака (положительные для сигнала (204), изображенного на Фиг. 6).

[0047] На Фиг. 7 приведена схема источника опорного напряжения (106). Источник (106) построен на аналогичном принципе воздействия на считываемые ячейки памяти (110). В представленном на Фиг. 7 примере в состав источника опорного напряжения (106) входит четыре ячейки (1064) с предопределенным состоянием «1» и «0». За счет последовательно-параллельного подключения общее сопротивление группы ячеек составляет:

Однако необходимо отметить, что количество ячеек может быть и другим, при условии сохранения их количества кратного двум, например, 2, 4, 8, 10, 20 и т.п. Ячейки необходимы для формирования набора сопротивлений с предопределенными состояниями.

[0048] В состав источника опорного напряжения (106) входит интегратор (1065) (аналогичный интегратору (105)), сигнал на выходе которого возрастает за время считывания одновременно с сигналом на выходе интегратора (105) схемы считывания (100). Ключи (10621) и (10631) схемы источника опорного напряжения на Фиг. 6 работают аналогичным образом ключам (1011) и (1021), представленным в схемах (10) и (11) (Фиг. 2 и Фиг. 3).

[0049] На Фиг. 8 представлена схема источника опорного напряжения (116), содержащего группы ключей (1062) и (1063), которые работают аналогично группам ключей (1071), (1081) схемы источника опорного напряжения в схеме (12) (Фиг. 4). Также как и для источника опорного напряжения (106), источник (116) содержит ячейки памяти, формирующие набор сопротивлений с предопределенными состояниями.

[0050] На Фиг. 9 представлена типовая схема интегратора, в частности интеграторов схемы считывания (105) и интегратора источника опорного напряжения (1065). В состав интегратора входит операционный усилитель (ОУ), резистор R, конденсатор С и ключи для сброса состояния в режиме ожидания. Скорость нарастания напряжения на выходе интегратора определяется значением сопротивления, конденсатора и величиной входного сигнала.

[0051] На Фиг. 10 приведена временная диаграмма сигналов на выходе интеграторов схемы считывания (105) и интегратора схемы источника опорных напряжений (1065). В начале периода считывания с интеграторов (105), (1065) снимается сигнал сброса, и напряжение на выходе интеграторов начинает возрастать монотонно со временем и пропорционально входному сигналу. Сигнал на выходе источника опорного напряжения пропорционален усредненному значению сопротивлений ячеек (1064) в состоянии «1» и «0», поэтому весь период чтения значение напряжение на выходе источника опорного напряжения (106) отстоит на одинаковую величину от сигнала схемы считывания (100) независимо от состояния считываемой ячейки (110). По окончании периода считывания на компаратор (107) схемы считывания (100) подается стробирующий сигнал управления. По стробирующему сигналу управления компаратор (107) усиливает разность входных сигналов до логических состояний «1» и «0».

[0052] Представленное описание заявленного решения раскрывает лишь предпочтительные примеры его реализации и не должно трактоваться как ограничивающее иные, частные примеры его осуществления, не выходящие за рамки объема правовой охраны, которые являются очевидными для специалиста соответствующей области техники.

Изобретение относится к вычислительной технике. Технический результат заключается в уменьшении вероятности возмущения чтением. Способ чтения состояния ячейки магниторезистивной памяти с переносом спина STT-MRAM, заключающийся в генерировании сигнала считывания Vrd во время Trd считывания ячейки памяти, причем напряжение сигнала Vrd в заданном временном диапазоне T2 периодически опускается ниже заданного значения стабилизационного импульса Vlo, и в заданном временном диапазоне T1 достигает значения Vhi, которое является выше значения Vlo. 3 н. и 11 з.п. ф-лы, 11 ил.

1. Способ чтения состояния ячейки магниторезистивной памяти с переносом спина STT-MRAM, заключающийся в генерировании сигнала считывания Vrd во время Trd считывания ячейки памяти, причем напряжение сигнала Vrd в заданном временном диапазоне T2 периодически опускается ниже заданного значения стабилизационного импульса Vlo, и в заданном временном диапазоне T1 достигает значения Vhi, которое является выше значения Vlo.

2. Способ по п. 1, характеризующийся тем, что уровень сигнала Vlo отличается от уровня Vhi по меньшей мере в 1,25 раза.

3. Способ по п. 1, характеризующийся тем, что Vlo является нулевым сигналом.

4. Способ по п. 1, характеризующийся тем, что длительность времени нахождения сигнала считывания Vrd ниже значения стабилизационного импульса Vlo приблизительно равно времени термической релаксации T0.

5. Способ по п. 1, характеризующийся тем, что T1 составляет от 0.1 нс до 20 нс.

6. Способ по п. 1, характеризующийся тем, что T2 составляет от 0.3 нс до 10 нс.

7. Способ по п. 1, характеризующийся тем, что уровень сигнала Vlo имеет противоположный знак от знака Vhi и отличается по амплитуде.

8. Система чтения состояния ячейки магниторезистивной памяти с переносом спина STT-MRAM, содержащая

− считываемую ячейку памяти, соединенную с первым и вторым ключами, обеспечивающими переключение знака воздействия на считываемую ячейку;

− генератор сигнала управления знаком воздействия на считываемую ячейку, обеспечивающий формирование управляющих сигналов, определяющих период чтения ячейки памяти с изменяющимся знаком воздействия;

− источник напряжения, соединенный с первым ключом;

− интегратор, соединенный со вторым ключом;

− источник опорного напряжения, обеспечивающий формирование напряжения считывания;

− компаратор, обеспечивающий сравнение напряжения, накопленного на интеграторе, с напряжением источника опорного напряжения;

причем

− генератор сигнала управления знаком воздействия на считываемую ячейку обеспечивает формирование управляющих сигналов, формирующих период чтения ячейки памяти с изменяющимся знаком воздействия за счет переключения первого и второго ключей по сигналу тока воздействия на ячейку памяти, при котором осуществляется генерирование сигнала считывания Vrd, таким образом, что сигнал Vrd в заданном временном диапазоне T2 периодически опускается ниже заданного значения стабилизационного импульса Vlo, и в заданном временном диапазоне T1 достигает значения значения Vhi, которое является выше значения Vlo.

9. Система по п. 8, характеризующаяся тем, что дополнительно содержит шунтирующий ключ, обеспечивающий перевод состояние верхнего контакта ячейки в нулевой уровень.

10. Система по п. 8, характеризующаяся тем, что источник опорного напряжения содержит группу ключей, обеспечивающих переключение знака воздействия на считываемую ячейку, и ячейки памяти, формирующие набор сопротивлений с предопределенными состояниями.

11. Система чтения состояния ячейки магниторезистивной памяти с переносом спина STT-MRAM, содержащая

− считываемую ячейку памяти, соединенную с первой и второй группами ключей, обеспечивающих переключение знака воздействия на считываемую ячейку;

− генератор сигнала управления знаком воздействия на считываемую ячейку, обеспечивающий формирование управляющих сигналов, определяющих период чтения ячейки памяти с изменяющимся знаком воздействия;

− источник напряжения, соединенный с первой группой ключей;

− интегратор, соединенный со второй группой ключей;

− источник опорного напряжения, обеспечивающий формирование напряжения считывания;

− компаратор, обеспечивающий сравнение напряжения, накопленного на интеграторе, с напряжением источника опорного напряжения;

причем

− генератор сигнала управления знаком воздействия на считываемую ячейку обеспечивает формирование управляющих сигналов, формирующих период чтения ячейки памяти с изменяющимся знаком воздействия за счет переключения первой и второй групп ключей по сигналу тока воздействия на ячейку памяти, при котором осуществляется генерирование сигнала считывания Vrd, таким образом, что сигнал Vrd в заданном временном диапазоне T2 периодически опускается ниже заданного значения стабилизационного импульса Vlo, и в заданном временном диапазоне T1 достигает значения Vhi, которое является выше значения Vlo.

12. Система по п. 11, характеризующаяся тем, что каждая группа ключей содержит четыре ключа.

13. Система по п. 12, характеризующаяся тем, что в каждой из групп ключей одна пара ключей замыкается по высокому состоянию управляющего сигнала, а вторая пара – по низкому.

14. Система по п. 11, характеризующаяся тем, что источник опорного напряжения содержит две группы ключей, обеспечивающих переключение знака воздействия на считываемую ячейку, и ячейки памяти, формирующие набор сопротивлений с предопределенными состояниями.

| R | |||

| BISHNOI et al | |||

| "Read disturb fault detection in STT-MRAM", опубл | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| A.V | |||

| KHVALKOVSKIY et al | |||

| "Basic principles of STT-MRAM cell operation in memory arrays", опубл | |||

| Видоизменение прибора с двумя приемами для рассматривания проекционные увеличенных и удаленных от зрителя стереограмм | 1919 |

|

SU28A1 |

Авторы

Даты

2021-04-09—Публикация

2020-06-30—Подача