ОБЛАСТЬ ТЕХНИКИ

Настоящее изобретение в целом относится к устройству магниторезистивной оперативной памяти с произвольным доступом, имеющему совместно используемую линию истока.

УРОВЕНЬ ТЕХНИКИ

Обычные битовые ячейки магниторезистивной оперативной памяти с переносом спинового момента (STT-MRAM) содержат транзистор и структуру магнитного туннельного перехода (MTJ). Базовая структура MTJ состоит из двух магнитных электродов, размещенных по сторонам от туннельного барьерного слоя. Магнитный момент каждого магнитного электрода ориентирован вдоль длинной оси вытянутого элемента. Параллельная и встречно-параллельная ориентация магнитного момента между двумя магнитными слоями на каждой стороне туннельного барьера вызывает два различных сопротивления на концах барьера, приводящих к двум состояниям памяти. Один из магнитных электродов имеет направление магнитного момента, которое может переключаться (меняться) на основе приложенной плотности тока и направления. Другой магнитный электрод имеет намагниченность, закрепленную в конкретном направлении.

Обычные битовые ячейки STT-MRAM в матрице памяти скомпонованы в колонки, с отдельными битовыми линиями и линиями истока для каждой колонки. Битовая линия и линия истока конкретной колонки создают двунаправленный путь тока для чтения и записи значений данных в одну или более битовых ячеек колонки. Числовая шина присоединяется к каждому ряду битовых ячеек с целью обеспечения возможности выбора конкретного ряда битовых ячеек для операций чтения и записи данных.

Одним ограничением обычных устройств STT-MRAM является низкая матричная плотность, проистекающая из расположения битовой линии и линии истока с интервалами по причине конфигурации линии истока в матрице памяти. Поскольку STT-MRAM использует двунаправленный ток для записи комплементарных данных, линии истока не могут быть ни присоединены к заземлению, ни совместно использоваться по всей матрице, как это возможно в других типах памяти. Вместо этого обычные матрицы памяти MRAM имеют одну линию истока на колонку, с соответствующей увеличенной областью по сравнению с другими типами памяти по причине увеличенного числа плотных металлических линий в матрице памяти.

РАСКРЫТИЕ ИЗОБРЕТЕНИЯ

В определенном варианте осуществления раскрывается устройство памяти. Данное устройство памяти содержит первую ячейку памяти и вторую ячейку памяти. Устройство памяти содержит первую битовую линию, соединенную с первой ячейкой памяти, и вторую битовую линию, соединенную со второй ячейкой памяти. Устройство памяти также содержит совместно используемую линию истока, соединенную с первой ячейкой памяти и со второй ячейкой памяти.

В другом варианте осуществления устройство памяти содержит первую ячейку памяти, содержащую первое устройство магнитного туннельного перехода (MTJ) и первый транзистор. Устройство памяти также содержит вторую ячейку памяти, содержащую второе устройство MTJ и второй транзистор. Устройство памяти содержит первый проводник, соединенный с первым терминалом затвора первого транзистора и соединенный со вторым терминалом затвора второго транзистора. Устройство памяти также содержит второй проводник, соединенный с первым терминалом истока первого транзистора и соединенный со вторым терминалом истока второго транзистора.

В другом варианте осуществления устройство памяти содержит первую ячейку памяти, содержащую первое устройство MTJ и второе устройство MTJ. Устройство памяти также содержит вторую ячейку памяти, содержащую третье устройство MTJ и четвертое устройство MTJ. Устройство памяти содержит первую битовую линию, соединенную с первой ячейкой памяти, и вторую битовую линию, соединенную со второй ячейкой памяти. Устройство памяти также содержит линию истока, соединенную с первой ячейкой памяти и соединенную со второй ячейкой памяти.

В другом варианте осуществления раскрывается способ использования совместно используемой линии истока, соединенной с множеством блоков устройства памяти. Данный способ содержит подачу тока на линию истока в течение операции с данными устройства памяти. Линия истока соединяется с первым блоком хранения данных и со вторым блоком хранения данных устройства памяти.

Одним конкретным преимуществом, создаваемым настоящими раскрываемыми вариантами осуществления, является уменьшенная область (площадь) устройства. Требуется меньшее количество линий для доступа к ячейкам матрицы памяти MTJ, и, таким образом, для разделения между линиями резервируется меньшая область (площадь) устройства. Матричная плотность может быть увеличена, поскольку требуется меньшее количество линий. Другим преимуществом является упрощенная маршрутизация линии истока по причине уменьшенного числа линий истока. Устройства MRAM согласно настоящим раскрываемым вариантам осуществления могут быть меньше сопоставимых устройств SRAM и могут быть менее дорогими в производстве. В дополнение, устройства MRAM согласно настоящим раскрываемым вариантам осуществления могут обладать более высоким быстродействием, чем сопоставимые устройства флэш-памяти.

Другие аспекты, преимущества и признаки по настоящему изобретению станут очевидны после анализа всей заявки, содержащей разделы: «Краткое описание чертежей», «Осуществление изобретения» и «Формула изобретения».

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

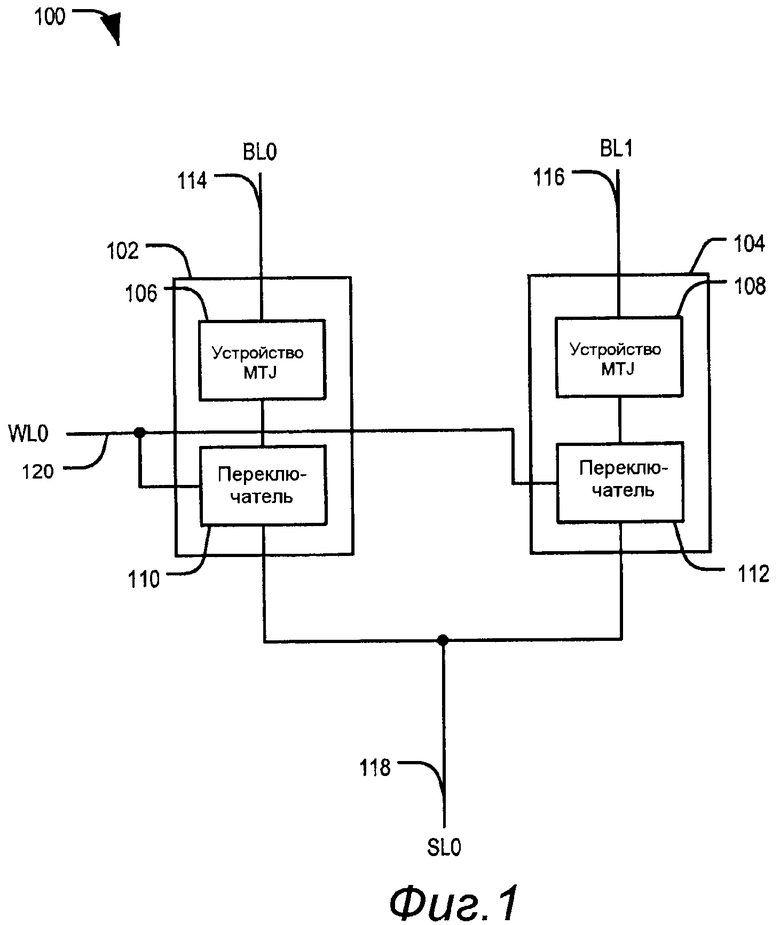

Фиг.1 представляет собой структурную диаграмму конкретного иллюстративного варианта осуществления устройства MRAM с совместно используемой линией истока;

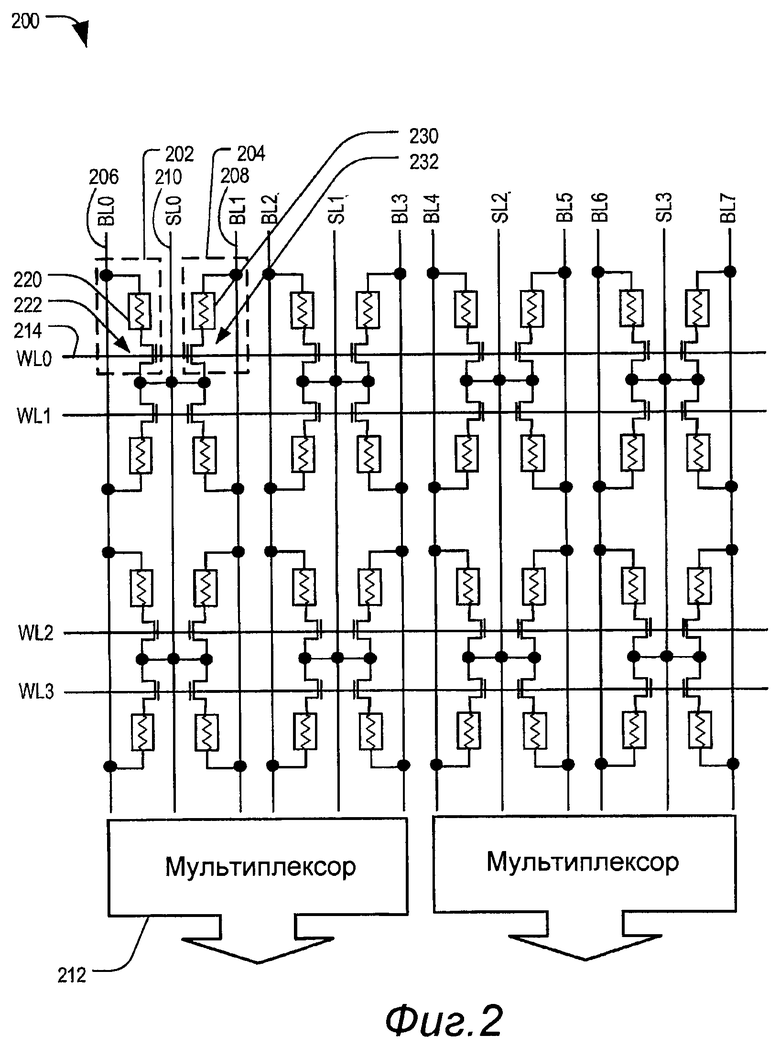

фиг.2 представляет собой диаграмму второго иллюстративного варианта осуществления устройства MRAM с совместно используемой линией истока;

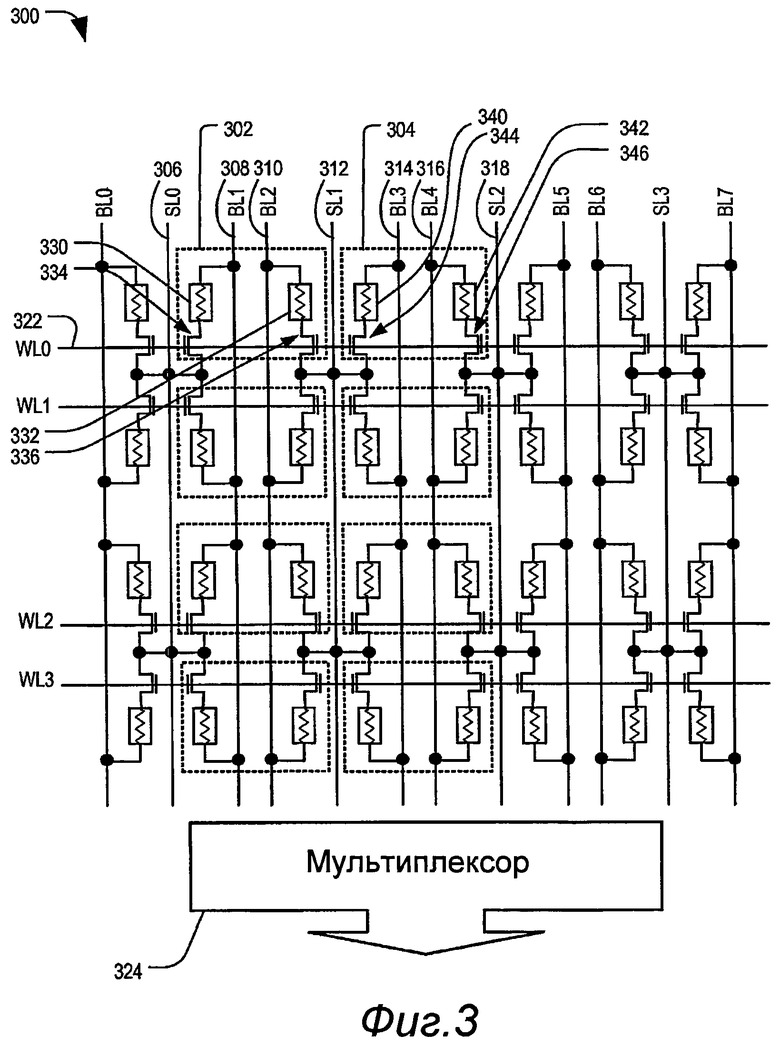

фиг.3 представляет собой диаграмму третьего иллюстративного варианта осуществления устройства MRAM с совместно используемой линией истока;

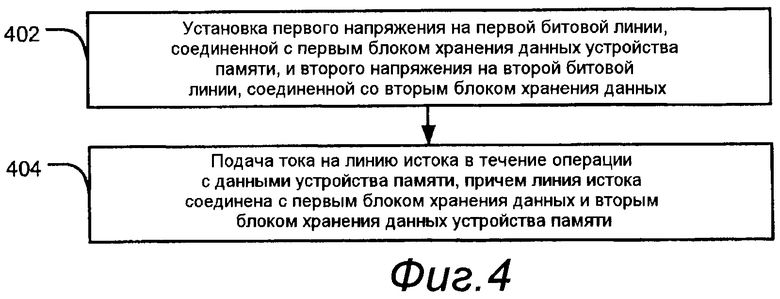

фиг.4 представляет собой блок-схему последовательности операций конкретного иллюстративного варианта осуществления способа использования совместно используемой линии истока, соединенной с множеством блоков устройства памяти; и

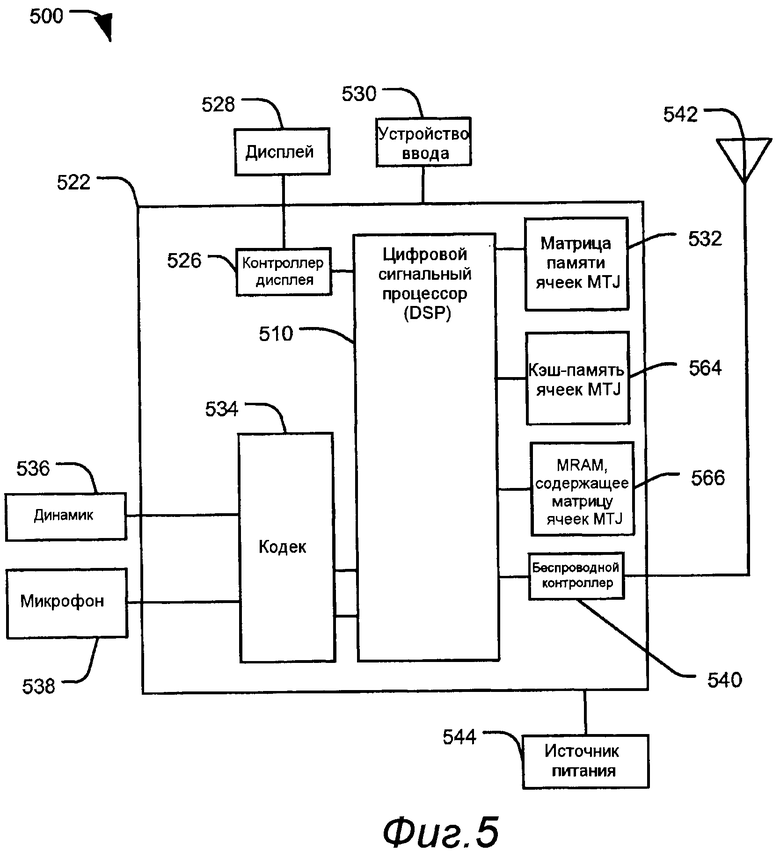

фиг.5 представляет собой структурную диаграмму устройства связи, содержащего устройство памяти, которое содержит множество ячеек магнитного туннельного перехода (MTJ).

ОСУЩЕСТВЛЕНИЕ ИЗОБРЕТЕНИЯ

На фиг.1 изображена структурная диаграмма конкретного иллюстративного варианта осуществления устройства MRAM с совместно используемой линией истока, которое обозначено в общем ссылочной позицией 100. Устройство 100 содержит первую репрезентативную ячейку памяти 102 и вторую репрезентативную ячейку памяти 104. Первая битовая линия (BL0) 114 соединена с первой ячейкой памяти 102. Вторая битовая линия (BL1) 116, являющаяся отличной от первой битовой линии 114, соединена со второй ячейкой памяти 104. Совместно используемая линия (SL0) 118 истока соединена с первой ячейкой памяти 102 и со второй ячейкой памяти 104. Числовая шина (WL0) 120 соединена с первой ячейкой памяти 102 и со второй ячейкой памяти 104.

Первая ячейка памяти 102 содержит устройство магнитного туннельного перехода (MTJ) 106, соединенное с первой битовой линией 114. Устройство MTJ 106 также соединено с переключателем 110, таким как транзистор. Переключатель 110 сконфигурирован с возможностью выборочно соединять устройство MTJ 106 с совместно используемой линией 118 истока в зависимости от управляющего сигнала, получаемого через числовую шину 120.

В конкретном варианте осуществления устройство MTJ 106 представляет собой устройство переноса спинового момента (STT), выполненное с возможностью сохранять программируемое магнитное поле в направлении, параллельном или встречно-параллельном по отношению к эталонному полю. В случае, когда магнитные поля являются параллельными, устройство MTJ 106 демонстрирует более низкое сопротивление, чем в случае, когда магнитные поля являются встречно-параллельными. Значение данных (например, «0» или «1»), сохраняемых на устройстве MTJ 106, соответствует параллельному или встречно-параллельному состоянию магнитных полей, которое можно определять посредством результирующего сопротивления устройства MTJ 106.

Вторая ячейка памяти 104 содержит устройство магнитного туннельного перехода (MTJ) 108, соединенное со второй битовой линией 116. Устройство MTJ 108 также соединено с переключателем 112, таким как транзистор. Переключатель 112 сконфигурирован с возможностью выборочно соединять устройство MTJ 108 с совместно используемой линией 118 истока в зависимости от управляющего сигнала, получаемого через числовую шину 120.

В конкретном варианте осуществления устройство MTJ 108 представляет собой устройство STT, выполненное с возможностью сохранять программируемое магнитное поле в направлении, параллельном или встречно-параллельном по отношению к эталонному полю. Значение данных (например, «0» или «1»), которые могут быть сохранены на устройстве MTJ 108, соответствует параллельному или встречно-параллельному состоянию магнитных полей, которое можно определять посредством результирующего сопротивления устройства MTJ 108.

В процессе работы данные могут считываться с или записываться в первую ячейку памяти 102 или вторую ячейку памяти 104 с использованием соединенных битовых линий 114, 116 и общей (то есть совместно используемой) линии 118 истока. Данные могут считываться путем приложения разности потенциалов между линией 118 истока и соответствующей битовой линией 114 или 116, соединенной с выбранной ячейкой памяти 102 или 104. Управляющий сигнал может посылаться через числовую шину 120 с целью обеспечения возможности протекания тока через переключатели 110, 112. Результирующий ток через линию 118 истока или через соединенную битовую линию 114 или 116 может сравниваться с эталонным током с целью определения значения данных в выбранной ячейке памяти 102 или 104. Данные могут также сохраняться в ячейке памяти 102 или 104 путем применения тока, достаточно большого для того, чтобы изменить направление программируемого магнитного поля соответствующего устройства MTJ 106 или 108 выбранной ячейки памяти 102 или 104.

В течение операции чтения первой ячейки памяти 102 первая битовая линия 114 несет первое напряжение, вторая битовая линия 116 несет второе напряжение, и линия 118 истока несет третье напряжение. Чтобы избежать подачи тока со стороны второй ячейки памяти 104 на линию 118 истока, второе напряжение на второй битовой линии 116 может быть таким же, что и третье напряжение на линии 118 истока. В конкретном варианте осуществления вторая битовая линия 116 и линия 118 истока смещены так, чтобы разница между вторым напряжением и третьим напряжением не была достаточно большой для того, чтобы разрушить вторую ячейку памяти 104.

В альтернативном варианте осуществления отдельные числовые шины (не показаны) могут быть соединены с первой ячейкой памяти 102 и второй ячейкой памяти 104 с целью независимого управления переключателями 110, 112 и выборочной активации или деактивации операций с данными в ячейках памяти 102, 104. Ток может подаваться на линию 118 истока, и результирующее напряжение на битовой линии 114 или 116 активированной ячейки памяти 102 или 104 может сравниваться с эталонным напряжением с целью определения значения данных, сохраненных в активированной (то есть выбранной) ячейке памяти 102 или 104.

На фиг.2 изображена диаграмма второго иллюстративного варианта осуществления устройства MRAM с совместно используемой линией истока, которое обозначено в общем ссылочной позицией 200. Устройство 200 содержит первую репрезентативную ячейку памяти 202 и вторую репрезентативную ячейку памяти 204. Ячейки памяти выбираются, и операции памяти выполняются посредством сигналов в различных проводниках, таких как репрезентативная первая битовая линия (BL0) 206, вторая битовая линия (BL1) 208, линия (SL0) 210 истока и числовая шина (WL0) 214. Первая колонка ячеек памяти, содержащая первую ячейку памяти 202, использует линию 210 истока совместно со второй колонкой ячеек памяти, содержащей вторую ячейку памяти 204. Один или более мультиплексоров, таких как репрезентативный мультиплексор 212, соединены с битовыми линиями и линиями истока.

Первая ячейка памяти 202 содержит первое устройство магнитного туннельного перехода (MTJ) 220, соединенное с первой битовой линией 206 и первым транзистором 222. Вторая ячейка памяти 204 содержит второе устройство MTJ 230, соединенное со второй битовой линией 208 и вторым транзистором 232. Первый вывод истока первого транзистора 222 и второй вывод истока второго транзистора 232, каждый, соединены с линией 210 истока. Первый вывод затвора первого транзистора 222 и второй вывод затвора второго транзистора 232, каждый, соединены с числовой шиной 214.

Операция чтения или записи может быть выполнена в выбранной ячейке, такой как первая ячейка памяти 202, соединенной с первой битовой линией 206 и линией 210 истока. Мультиплексор 212 соединяет первую битовую линию 206 и линию 210 истока в схемы чтения и записи (не показаны). Поскольку первая ячейка памяти 202 использует линию 210 истока совместно со второй ячейкой памяти 204, когда выполняется операция чтения, схема чтения может привязать вторую битовую линию 208 к тому же уровню напряжения, что и на линии 210 истока, с целью предотвращения нежелательной операции во второй ячейке памяти 204. Например, схема чтения может соединять первую битовую линию 206 с напряжением питания и может соединять как линию 210 истока, так и вторую битовую линию 208 перед отправкой сигнала активации на числовую шину 214.

Для выполнения операции чтения в первой ячейке памяти 202 первая битовая линия 206 может быть смещена по уровню напряжения чтения, и линия 210 истока и вторая битовая линия 208 могут быть привязаны к разному уровню напряжения. Управляющее напряжение может быть приложено к числовой шине 214 с целью активации соответствующего ряда ячеек памяти, содержащего ячейки памяти 202 и 204. Разность напряжения между первой битовой линией 206 и линией 210 истока заставляет ток протекать через первую битовую линию 206, первое устройство MTJ 220, первый переключатель 222 и линию 210 истока. Ток может сравниваться с эталонным током для определения, сохранено ли значение «0» или значение «1» в первой ячейке памяти 202.

Для выполнения операции чтения во второй ячейке памяти 204 первая битовая линия 206 может быть смещена по существу на тот же уровень напряжения, что и линия 210 истока, и вторая битовая линия 208 может быть смещена на уровень напряжения чтения. Результирующий ток во второй битовой линии 208 или линии 210 истока может сравниваться с эталонным током с целью определения значения данных, сохраненных во второй ячейке памяти 204.

Операции записи могут быть выполнены путем выбора ряда через числовую шину и подачи тока записи на выбранную битовую линию. Например, операция записи может быть выполнена в первой ячейке памяти 202 путем выбора числовой шины 214 и подачи тока в первую битовую линию 206 с обратным путем через линию 210 истока. Направление тока между первой битовой линией 206 и линией 210 истока определяет значение данных, записанных в выбранную ячейку 202. Линия 210 истока является активной в течение операций чтения и в течение операций записи как в первой колонке ячеек памяти, содержащей первую ячейку памяти 202, так и во второй колонке ячеек памяти, содержащей вторую ячейку памяти 204.

На фиг.3 изображена диаграмма третьего иллюстративного варианта осуществления устройства MRAM с совместно используемой линией истока, которое обозначено в общем ссылочной позицией 300. Устройство 300 содержит матрицу ячеек памяти, таких как первая репрезентативная ячейка памяти 302 и вторая репрезентативная ячейка памяти 304. Первая линия (SL0) 306 истока, первая битовая линия (BL1) 308 и вторая битовая линия (BL2) 310 соединены с первой ячейкой памяти 302. Вторая линия (SL1) 312 истока соединена с первой ячейкой памяти 302 и со второй ячейкой памяти 304. Третья битовая линия (BL3) 314, четвертая битовая линия (BL4) 316 и третья линия (SL2) 318 истока соединены со второй ячейкой памяти 304. Первая ячейка памяти 302 и вторая ячейка памяти 304, каждая, соединены с числовой шиной (WL0) 322. Мультиплексор 324 соединен с битовыми линиями и линиями истока, соединенными с множеством ячеек памяти матрицы.

Первая ячейка памяти 302 содержит первое устройство магнитного туннельного перехода (MTJ) 330 и второе устройство MTJ 332. Первый транзистор 334 соединен с первым устройством MTJ 330, и второй транзистор 336 соединен со вторым устройством MTJ 332. По меньшей мере один из транзисторов 334 и 336 соединен со второй линией 312 истока, которая совместно используется со второй ячейкой памяти 304. Как изображено, первая линия 306 истока соединена с первым транзистором 334, и вторая линия 312 истока соединена со вторым транзистором 336. Числовая шина 322 соединена с управляющим выводом каждого из первого и второго транзисторов 334, 336. В конкретном варианте осуществления первая ячейка памяти 302 работает как ячейка комплементарного устройства, с первым устройством MTJ 330 и вторым устройством MTJ 332, сохраняющими значения комплементарных данных.

Вторая ячейка памяти 304 содержит третье устройство MTJ 340 и четвертое устройство MTJ 342. Третий транзистор 344 соединен с третьим устройством MTJ 340, и четвертый транзистор 346 соединен с четвертым устройством MTJ 342. По меньшей мере один из транзисторов 344 и 346 соединен со второй линией 312 истока, совместно используемой с первой ячейкой памяти 302. Как изображено, вторая линия 312 истока соединена с третьим транзистором 344, и третья линия 318 истока соединена с четвертым транзистором 346. Числовая шина 322 соединена с управляющим выводом каждого из третьего и четвертого транзисторов 344, 346. В конкретном варианте осуществления вторая ячейка памяти 304 работает как ячейка комплементарного устройства, с третьим устройством MTJ 340 и четвертым устройством MTJ 342, сохраняющими значения комплементарных данных.

В конкретном варианте осуществления операция чтения может быть выполнена в первой ячейке памяти 302 путем выбора первого ряда ячеек памяти через числовую шину 322. Управляющий сигнал, подаваемый на числовую шину 322, обеспечивает возможность прохождения тока через каждое из устройств MTJ в соединенном ряду, содержащем устройства MTJ 330, 332, 340 и 342. Схема чтения (не показана) на мультиплексоре 324 подает первый набор сигналов чтения на первую линию 306 истока и первую битовую линию 308 с целью чтения первого значения данных, сохраненных на устройстве MTJ 330. Схема чтения мультиплексора 324 также подает второй набор сигналов чтения на вторую линию 312 истока и вторую битовую линию 310 с целью чтения второго значения данных, сохраненных на втором устройстве MTJ 332.

В конкретном варианте осуществления сигналы чтения могут содержать разность напряжения, поданного на концах битовых линий и линий истока. Поскольку вторая ячейка памяти 304 использует вторую линию 312 истока совместно с первой ячейкой памяти 302, по меньшей мере третья битовая линия 314 устанавливается на то же напряжение, что и вторая линия 312 истока, с целью предотвращения дополнительного пути тока на и от второй линии 312 истока через третье устройство MTJ 340.

В конкретном варианте осуществления схема чтения сравнивает ток, проходящий через первую битовую линию 308, с током, проходящим через вторую битовую линию 310, с целью определения значения данных, сохраненных в первой ячейке памяти 302. Использование комплементарных устройств MTJ 330 и 332 в первой ячейке памяти 302 обеспечивает возможность определения значения сохраненных данных без генерирования эталонного тока или напряжения для сравнения.

В конкретном варианте осуществления операция записи может быть выполнена в первой ячейке памяти 302 путем подачи управляющего сигнала на числовую шину 322 с целью обеспечения возможности прохождения тока через каждое из устройств MTJ в соединенном ряду, содержащем устройства MTJ 330, 332, 340 и 342. Схема записи (не показана) на мультиплексоре 324 подает первый набор сигналов записи на первую линию 306 истока и на первую битовую линию 308 с целью записи первого значения данных на первое устройство MTJ 330. Схема записи также подает второй набор сигналов записи на вторую линию 312 истока и вторую битовую линию 310 с целью записи значения комплементарных данных на второе устройство MTJ 332. По меньшей мере третья битовая линия 314 устанавливается на то же напряжение, что и вторая линия 312 истока, с целью предотвращения дополнительного прохождения тока на и от второй линии 312 истока через третье устройство MTJ 340.

На фиг.4 изображена блок-схема последовательности операций конкретного иллюстративного варианта осуществления способа использования совместно используемой линии истока с множеством блоков устройства памяти. На этапе 402 в конкретном варианте осуществления устанавливается первое напряжение на первой битовой линии, соединенной с первым блоком хранения данных устройства памяти, и устанавливается второе напряжение на второй битовой линии, соединенной со вторым блоком хранения данных устройства памяти. В иллюстративном варианте осуществления первый и второй блоки хранения данных могут представлять собой ячейки памяти устройств, проиллюстрированных на фиг.1-3.

Переходя к этапу 404, ток подается на линию истока в течение операции с данными устройства памяти. Линия истока соединяется с первым блоком хранения данных и со вторым блоком хранения данных устройства памяти. Ток может подаваться на линию истока через источник тока или может генерироваться на линии истока в зависимости от разности потенциалов между линией истока и битовой линией устройства памяти. В конкретном варианте осуществления операция с данными представляет собой операцию чтения или операцию записи данных. Выходные данные первого блока хранения данных и второго блока хранения данных могут подаваться на мультиплексор.

В конкретном варианте осуществления первый блок хранения данных представляет собой первую ячейку памяти, содержащую одиночное устройство магнитного туннельного перехода (MTJ). В другом конкретном варианте осуществления первый блок хранения данных представляет собой объединенную ячейку, содержащую множество комплементарных устройств MTJ. Множество комплементарных устройств MTJ содержит первое устройство MTJ для хранения первого элемента данных и второе устройство MTJ для хранения второго элемента данных.

Фиг.5 представляет собой структурную диаграмму устройства связи 500, содержащего устройство памяти, которое содержит множество ячеек магнитного туннельного перехода (MTJ). Данное устройство связи 500 содержит матрицу памяти ячеек MTJ 532 и кэш-память ячеек MTJ 564, соединенных с процессором, таким как цифровой сигнальный процессор (DSP) 510. Устройство связи 500 также содержит устройство магниторезистивной оперативной памяти с произвольным доступом (MRAM) 566, соединенное с процессором DSP 510. В конкретном примере одна или более матриц памяти ячеек MTJ 532, кэш-память ячеек MTJ 564 и устройство MRAM 566 выполнены в виде устройств, содержащих множество ячеек MTJ, совместно использующих линии истока для уменьшения матричной области MRAM, как описано со ссылкой на фиг.1-4.

Фиг.5 также демонстрирует контроллер дисплея 526, соединенный с цифровым сигнальным процессором 510 и дисплеем 528. Кодер/декодер (CODEC) 534 также может быть соединен с цифровым сигнальным процессором 510. Динамик 536 и микрофон 538 могут быть соединены с кодером/декодером 534.

Фиг.5 также показывает, что беспроводной контроллер 540 может быть соединен с цифровым сигнальным процессором 510 и с беспроводной антенной 542. В конкретном варианте осуществления устройство ввода 530 и источник питания 544 соединены с системой на кристалле 522. Более того, в конкретном варианте осуществления, как проиллюстрировано на фиг.5, дисплей 528, устройство ввода 530, динамик 536, микрофон 538, беспроводная антенна 542 и источник питания 544 являются внешними относительно системы на кристалле 522. Однако каждое из устройств может быть соединено с компонентом системы на кристалле 522, таким как интерфейс или контроллер.

Специалистам в данной области техники должно быть понятно, что различные иллюстративные логические блоки, конфигурации, модули, схемы и алгоритмические этапы, описанные в связи с вариантами осуществления настоящего изобретения, могут быть выполнены в виде электронного аппаратного оборудования, компьютерного программного обеспечения или комбинации того и другого. Для ясной иллюстрации этой взаимозаменяемости аппаратного оборудования и программного обеспечения выше были в общих чертах описаны различные иллюстративные компоненты, блоки, конфигурации, модули, схемы и этапы с точки зрения их функциональности. Будет ли такая функциональность выполнена в виде аппаратного оборудования или программного обеспечения, зависит от конкретного варианта осуществления и ограничений по конструкции, накладываемых на всю систему. Специалисты могут выполнить описанную функциональность различными способами для каждого конкретного варианта осуществления, но такие решения по реализации не должны рассматриваться как выходящие за рамки описываемого изобретения.

Этапы способа или алгоритма, описанные в связи с вариантами осуществления настоящего изобретения, могут быть осуществлены непосредственно в аппаратном оборудовании, в модуле программного обеспечения, выполняемого процессором, или в комбинации того и другого. Модуль программного обеспечения может храниться в памяти RAM, флэш-памяти, памяти ROM, памяти PROM, памяти EPROM, памяти EEPROM, регистрах, на жестком диске, съемном диске, на CD-ROM или в любой другой форме среды хранения, известной в уровне техники. Иллюстративная среда хранения (носитель) связана с процессором, причем такой процессор может считывать информацию с и записывать информацию на носитель. В качестве альтернативы носитель может быть встроенным в процессор. Процессор и носитель могут постоянно храниться в ASIC. ASIC может постоянно находиться в вычислительном устройстве или в терминале пользователя. В качестве альтернативы процессор и носитель могут постоянно находиться как дискретные компоненты в вычислительном устройстве или в терминале пользователя.

Приведенное описание раскрытых вариантов осуществления настоящего изобретения призвано обеспечить специалисту в области техники возможность выполнения или использования раскрытых вариантов осуществления настоящего изобретения. Различные модификации данных вариантов осуществления будут явно очевидны для специалистов, и основные принципы, описанные в настоящем изобретении, могут быть применены к другим вариантам осуществления, без изменения объема настоящего изобретения. Таким образом, настоящее изобретение не предназначено быть ограниченным описанными вариантами осуществления, но должно соответствовать самому широкому объему, согласующемуся с принципами и новыми признаками, раскрытыми в нижеследующей формуле изобретения.

Изобретение относится к вычислительной технике. Технический результат заключается в уменьшении области (площади) устройства, увеличении матричной плотности и упрощении маршрутизации линии истока за счет уменьшения числа линий истока. Устройство памяти содержит первую колонку ячеек памяти включающую в себя первую ячейку памяти; вторую колонку ячеек памяти, включающую в себя вторую ячейку памяти; первую битовую линию, связанную с первой колонкой ячеек памяти; вторую битовую линию, связанную со второй колонкой ячеек памяти; и линию истока, совместно используемую первой колонкой ячеек памяти и второй колонкой ячеек памяти, причем в течение чтения первой ячейки памяти первая битовая линия несет первое напряжение, вторая битовая линия несет второе напряжение, и линия истока несет третье напряжение, причем второе напряжение и третье напряжение являются по существу одинаковыми. 3 н. и 17 з.п. ф-лы, 5 ил.

1. Устройство памяти, содержащее:

первую колонку ячеек памяти, включающую в себя первую ячейку памяти;

вторую колонку ячеек памяти, включающую в себя вторую ячейку памяти;

первую битовую линию, связанную с первой колонкой ячеек памяти;

вторую битовую линию, связанную со второй колонкой ячеек памяти; и линию истока, совместно используемую первой колонкой ячеек памяти и второй колонкой ячеек памяти,

причем в течение чтения первой ячейки памяти, первая битовая линия несет первое напряжение, вторая битовая линия несет второе напряжение, и линия истока несет третье напряжение, причем второе напряжение и третье напряжение являются по существу одинаковыми.

2. Устройство памяти по п.1, в котором первая ячейка памяти и вторая ячейка памяти содержат устройства магнитного туннельного перехода (MTJ).

3. Устройство памяти по п.1, дополнительно содержащее числовую шину, соединенную с по меньшей мере одной из первой ячейки памяти и второй ячейки памяти.

4. Устройство памяти по п.1, в котором любая разница между вторым напряжением и третьим напряжением имеет величину, недостаточную для разрушения второй ячейки памяти.

5. Устройство памяти по п.1, в котором первая битовая линия является отличной от второй битовой линии.

6. Устройство памяти по п.1, в котором:

первая ячейку памяти содержит первое устройство магнитного туннельного перехода (MTJ) и первый транзистор;

вторая ячейку памяти содержит второе устройство MTJ и второй транзистор;

причем устройство дополнительно содержит:

первый проводник, соединенный с первым выводом затвора первого транзистора и соединенный со вторым выводом затвора второго транзистора; и

второй проводник, соединенный с первым выводом истока первого транзистора и соединенный со вторым выводом истока второго транзистора.

7. Устройство памяти по п.6, дополнительно содержащее:

третий проводник, соединенный с первым устройством MTJ; и четвертый проводник, соединенный со вторым устройством MTJ.

8. Устройство памяти по п.7, в котором третий проводник представляет собой первую битовую линию и в котором четвертый проводник представляет собой вторую битовую линию.

9. Устройство памяти по п.6, в котором первый проводник представляет собой числовую шину.

10. Устройство памяти по п.9, в котором второй проводник представляет собой линию истока.

11. Устройство памяти по п.10, в котором линия истока является активной в течение операций чтения и в течение операций записи.

12. Устройство памяти, содержащее:

первую ячейку памяти, содержащую первое устройство магнитного туннельного перехода (MTJ) и второе устройство MTJ;

вторую ячейку памяти, содержащую третье устройство MTJ и четвертое устройство MTJ;

первую битовую линию, связанную с первой ячейкой памяти;

вторую битовую линию, связанную со второй ячейкой памяти; и

линию истока, соединенную с первой ячейкой памяти и соединенную со второй ячейкой памяти.

13. Устройство памяти по п.12, в котором первая ячейка памяти содержит первый транзистор, соединенный с первым устройством MTJ, и второй транзистор, соединенный со вторым устройством MTJ, и в котором линия истока соединена с по меньшей мере одним из первого транзистора и второго транзистора.

14. Устройство памяти по п.13, в котором вторая ячейка памяти содержит третий транзистор, соединенный с третьим устройством MTJ, и четвертый транзистор, соединенный с четвертым устройством MTJ, и в котором линия истока соединена с по меньшей мере одним из третьего транзистора и четвертого транзистора.

15. Устройство памяти по п.14, в котором первая ячейка памяти и вторая ячейка памяти, каждая, соединены с числовой шиной.

16. Устройство памяти по п.15, в котором числовая шина соединена с управляющим выводом каждого из первого, второго, третьего и четвертого транзисторов.

17. Способ использования линии истока с множеством блоков хранения данных устройства памяти, причем способ содержит:

подачу тока в линию истока в течение операции считывания данных устройства памяти, причем линия истока соединена с первым блоком хранения данных и вторым блоком хранения данных устройства памяти.

18. Способ по п.17, в котором первая ячейка памяти содержит одно устройство магнитного туннельного перехода (MTJ).

19. Способ по п.17, в котором первый блок хранения данных представляет собой объединенную ячейку, содержащую множество комплементарных устройств магнитного туннельного перехода (MTJ), причем множество комплементарных устройств MTJ, каждое, содержат первое устройство MTJ для хранения первого элемента данных и второе устройство MTJ для хранения второго элемента данных.

20. Способ по п.17, в котором выходные данные первого блока хранения данных и второго блока хранения данных подаются на мультиплексор.

| US 7187577 B1, 06.03.2007 | |||

| Пресс для выдавливания из деревянных дисков заготовок для ниточных катушек | 1923 |

|

SU2007A1 |

| US 7272035 B1, 18.09.2007 | |||

| Пресс для выдавливания из деревянных дисков заготовок для ниточных катушек | 1923 |

|

SU2007A1 |

| US 7286378 B2, 23.10.2007 | |||

| Топчак-трактор для канатной вспашки | 1923 |

|

SU2002A1 |

| Низколегированная сталь | 1976 |

|

SU616332A1 |

| УСОВЕРШЕНСТВОВАННОЕ МНОГОРАЗРЯДНОЕ МАГНИТНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ПРОИЗВОЛЬНОЙ ВЫБОРКОЙ И СПОСОБЫ ЕГО ФУНКЦИОНИРОВАНИЯ И ПРОИЗВОДСТВА | 2005 |

|

RU2310928C2 |

Авторы

Даты

2012-07-10—Публикация

2008-12-19—Подача