ПЕРЕКРЕСТНАЯ ССЫЛКА НА РОДСТВЕННЫЕ ЗАЯВКИ

Эта заявка испрашивает приоритет по предварительной заявке США, номер 61/873,798, поданной 4 сентября, 2013, и заявке США, номер 14/201,613, поданной 7 марта, 2014, полное содержание каждой из которых включено сюда путем ссылки.

ОБЛАСТЬ ТЕХНИКИ

Варианты осуществления, здесь описанные, относятся, в общем, к магнитной памяти и способу управления магнитной памятью.

УРОВЕНЬ ТЕХНИКИ

В последние годы, в качестве полупроводниковой памяти предлагается магниторезистивная оперативная память типа переноса спинового момента (STT-MRAM). MRAM содержит элемент с магниторезистивным эффектом в ячейке памяти. Элемент с магниторезистивным эффектом включает в себя два магнитных слоя (ферромагнитных слоя) и немагнитный слой, обеспеченный между ними. Данные "1" или "0" хранятся в ячейке памяти в зависимости от намагниченного состояния упомянутых двух магнитных слоев элемента с магниторезистивным эффектом, то есть, являются ли спиновые ориентации упомянутых двух магнитных слоев параллельными или антипараллельными.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

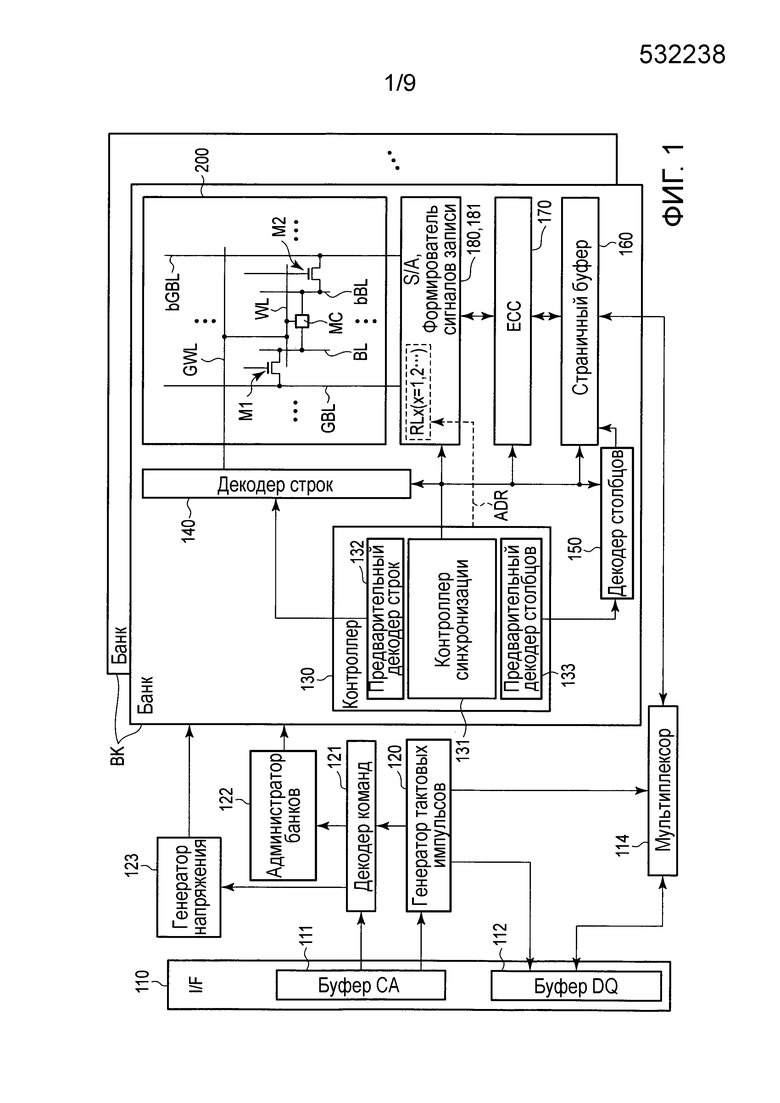

Фиг.1 является блок-схемой, показывающей общий пример конфигурации магнитной памяти;

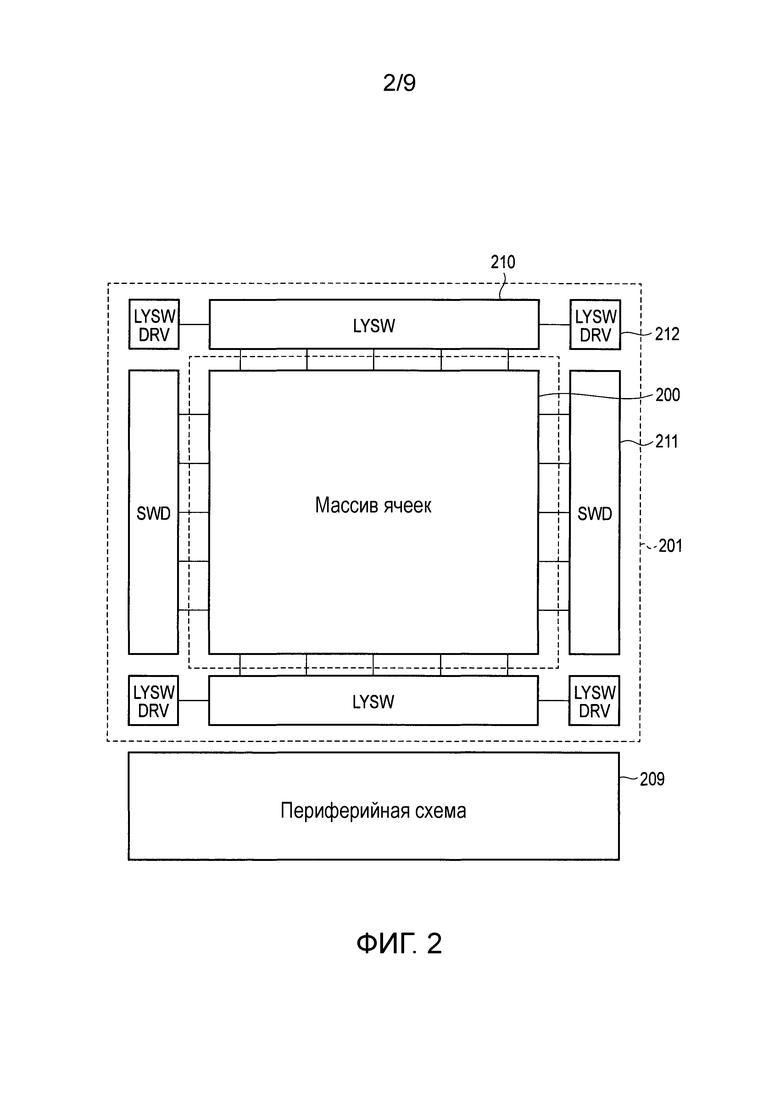

Фиг.2 является видом, показывающим пример конфигурации рядом с массивом ячеек магнитной памяти;

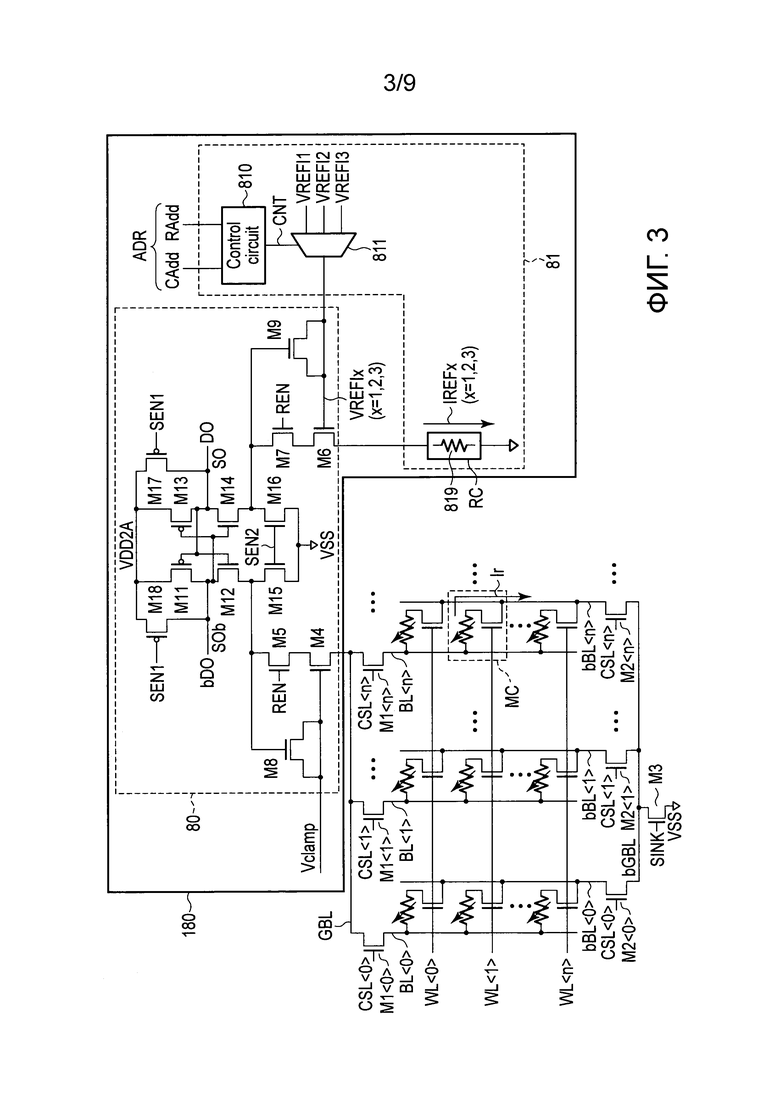

Фиг.3 является схематической диаграммой, показывающей пример конфигурации магнитной памяти в одном варианте осуществления;

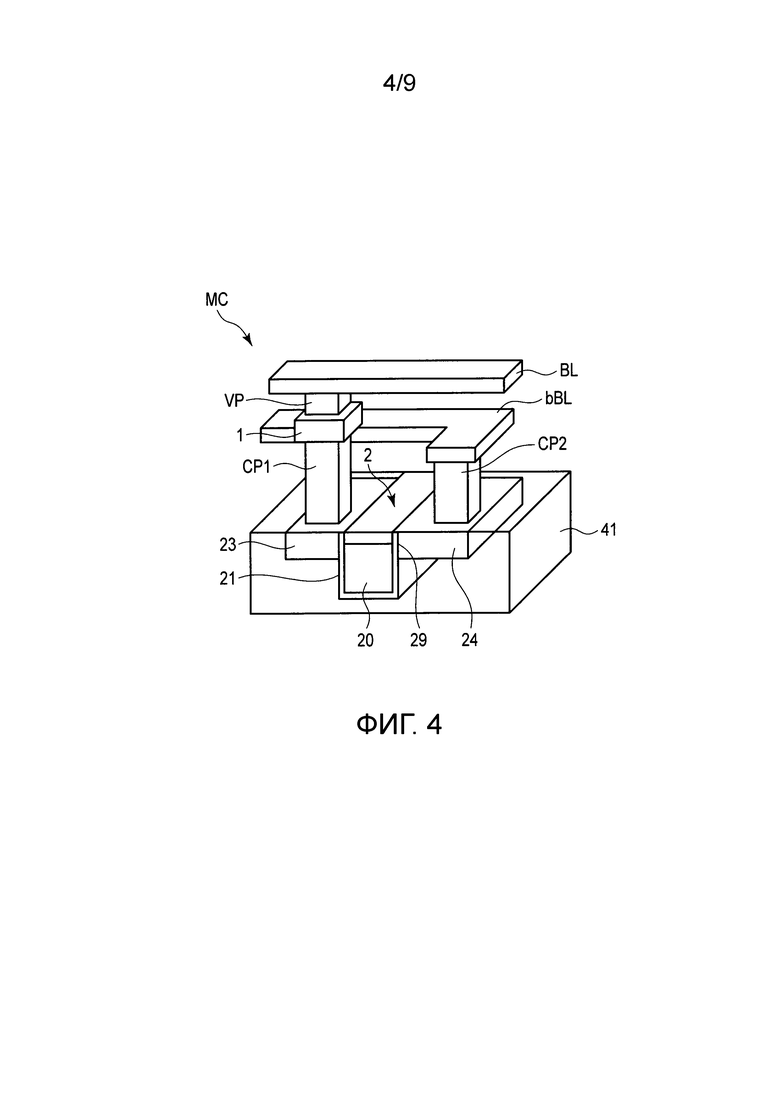

Фиг.4 является видом, показывающим пример структуры ячейки памяти магнитной памяти;

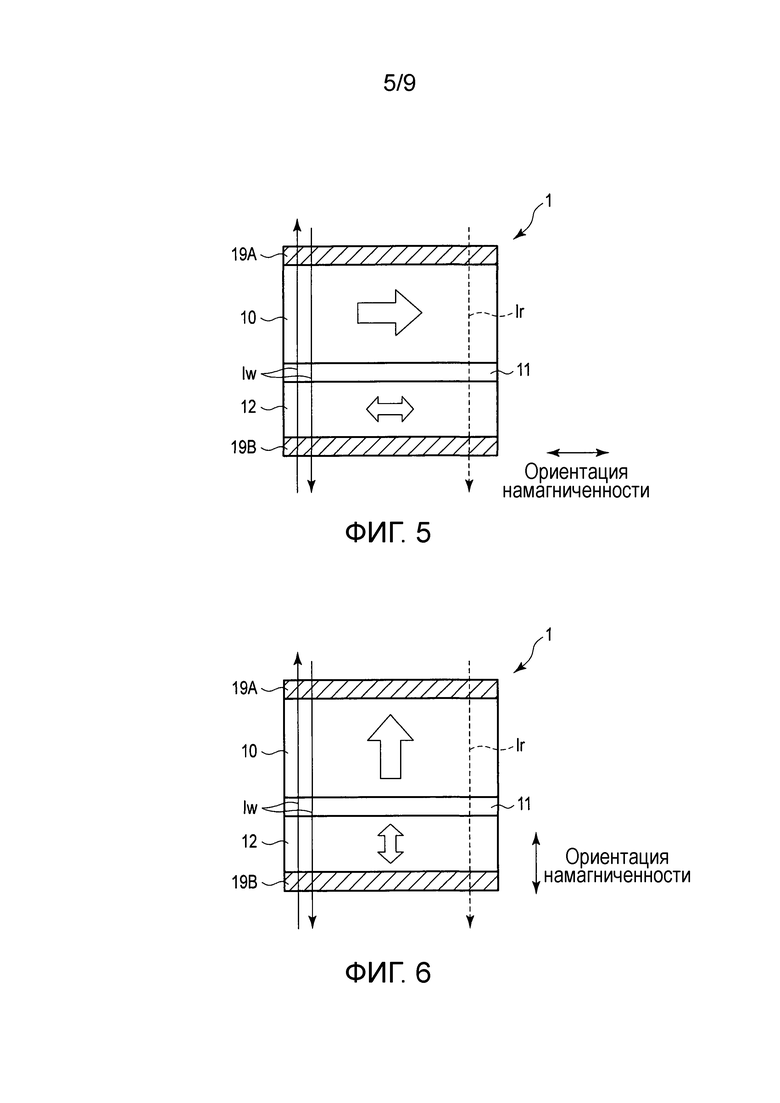

Фиг.5 является схематическим видом, показывающим пример структуры элемента с магниторезистивным эффектом;

Фиг.6 является схематическим видом, показывающим пример структуры элемента с магниторезистивным эффектом;

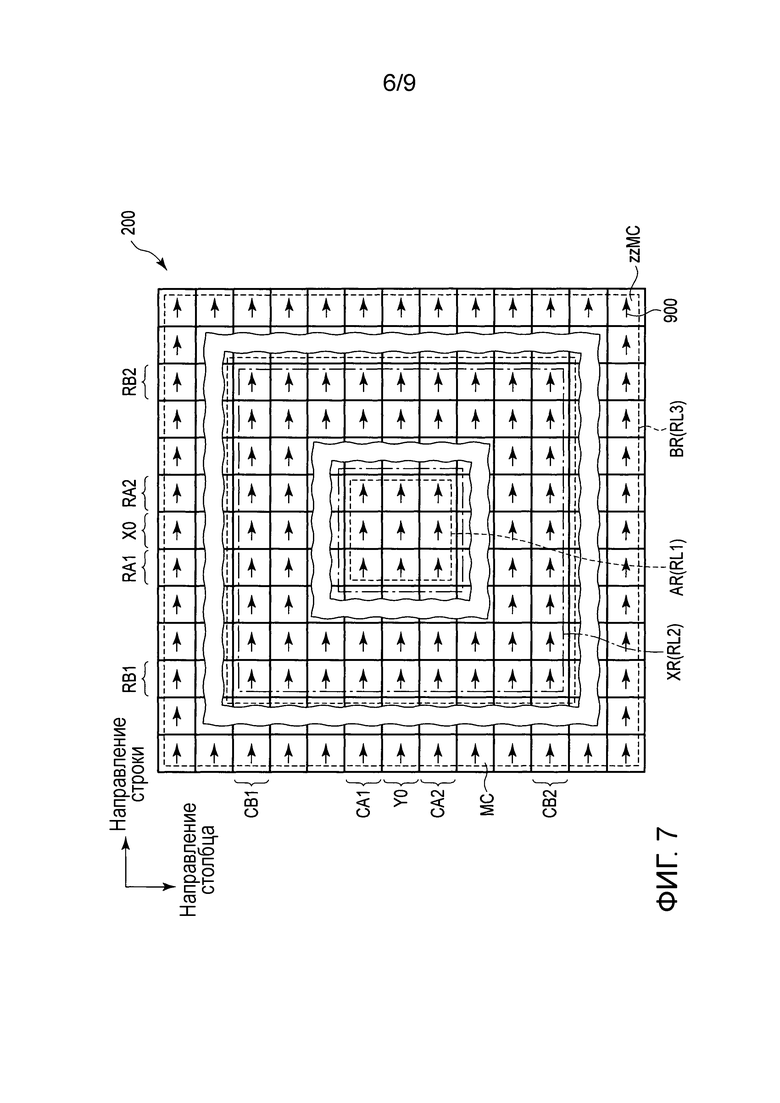

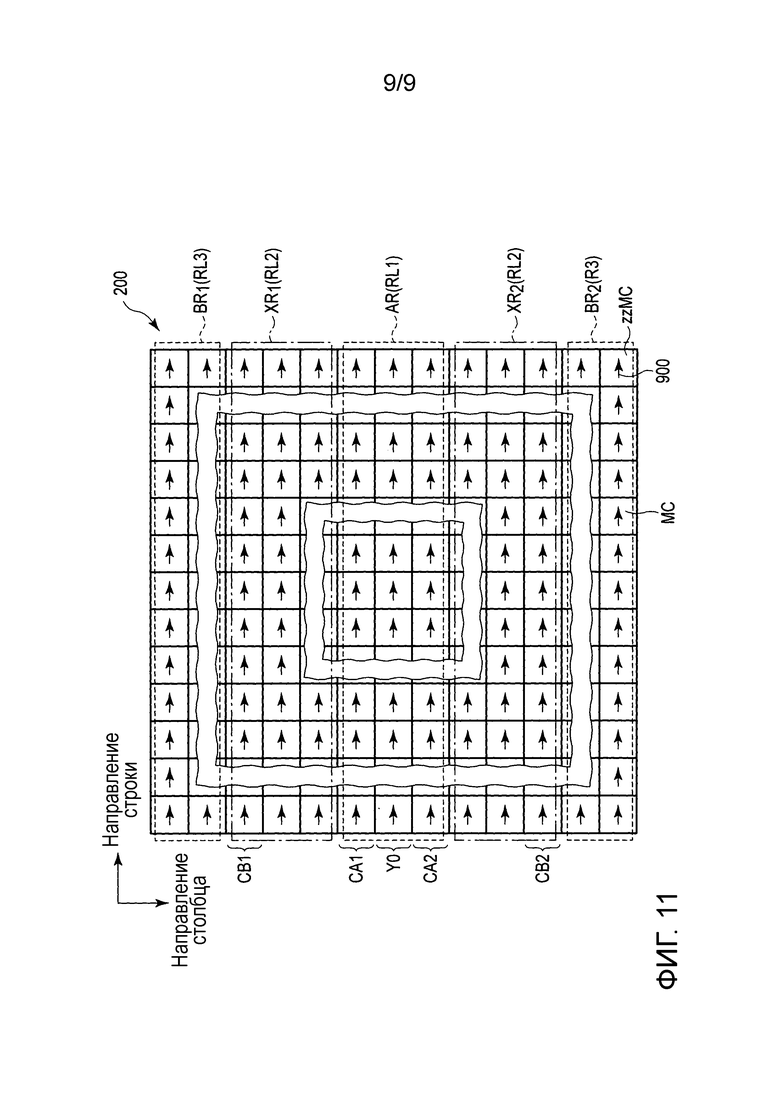

Фиг.7 является схематическим видом для описания магнитной памяти в одном варианте осуществления;

Фиг.8 является схематическим видом для описания магнитной памяти в одном варианте осуществления;

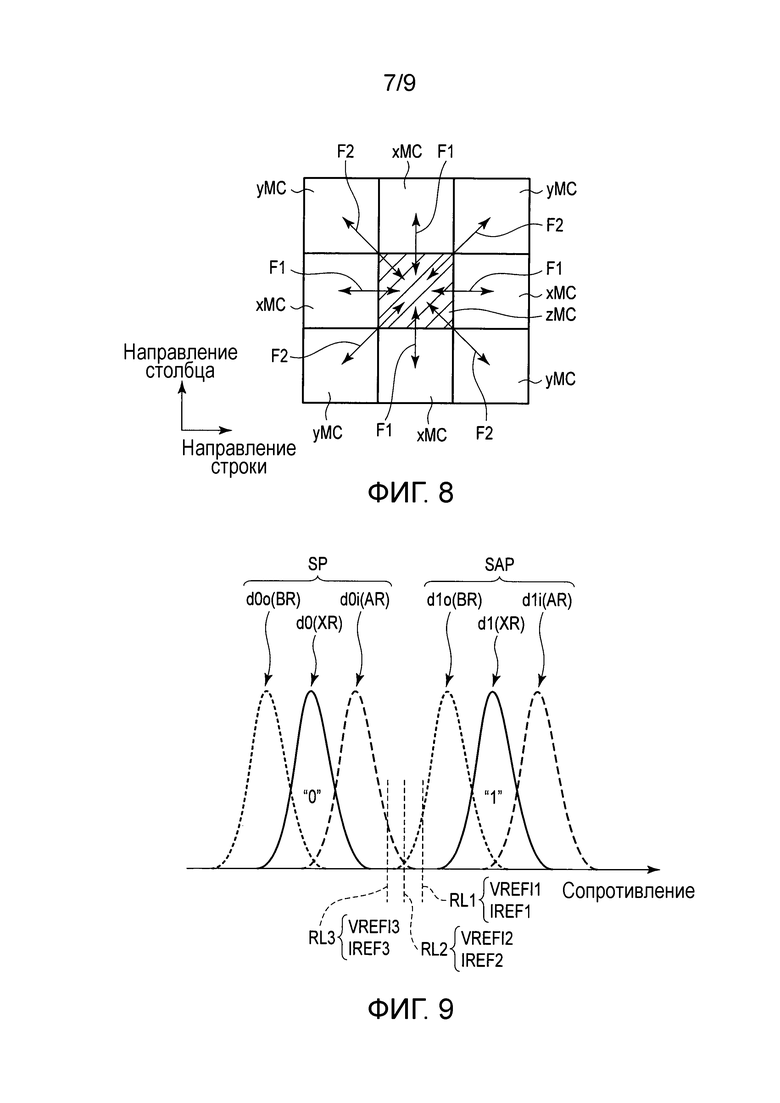

Фиг.9 является схематической диаграммой для описания магнитной памяти в одном варианте осуществления;

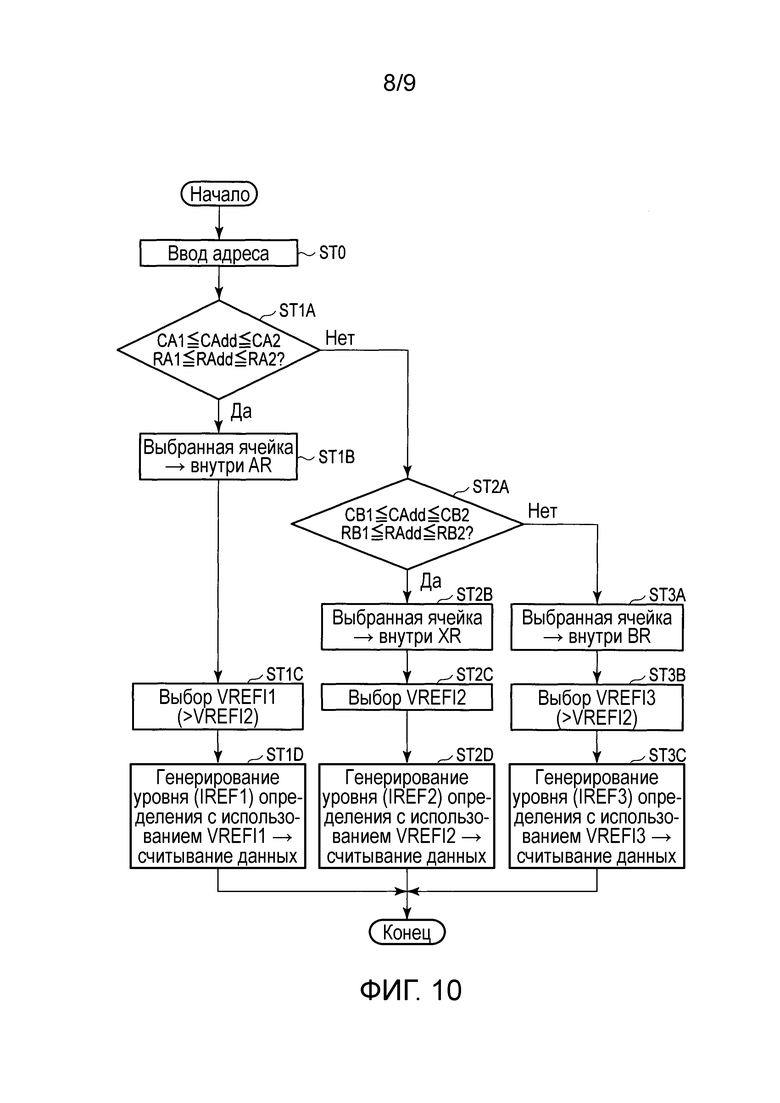

Фиг.10 является диаграммой для описания примера работы магнитной памяти в одном варианте осуществления; и

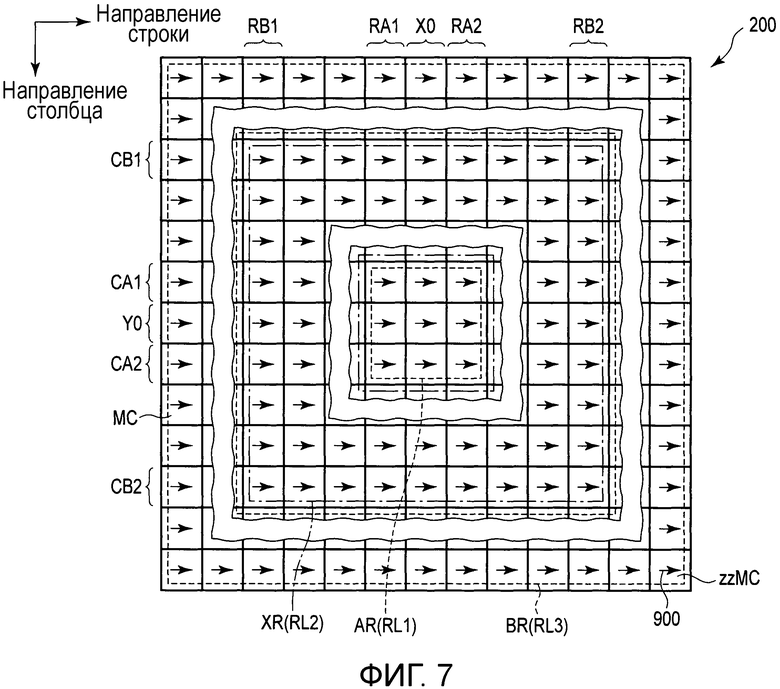

Фиг.11 является видом для описания модификации магнитной памяти в одном варианте осуществления.

ПОДРОБНОЕ ОПИСАНИЕ

Настоящий вариант осуществления будет описываться подробно ниже со ссылкой на чертежи. В описании, которое следует, одинаковые ссылочные позиции присоединены к элементам, имеющим одинаковую функцию и конфигурацию, и повторное описание будет обеспечиваться, когда необходимо.

В общем, согласно одному варианту осуществления, магнитная память включает в себя массив ячеек, содержащий множество ячеек памяти, расположенных вдоль первого и второго направлений, при этом каждая ячейка памяти включает в себя элемент с магниторезистивным эффектом в качестве элемента памяти; и схему чтения, чтобы считывать данные из ячейки памяти, выбранной на основе сигнала адреса из числа множества ячеек памяти. Схема чтения выбирает один уровень определения из множества уровней определения, соответствующих положению элемента с магниторезистивным эффектом в массиве ячеек, и использует выбранный уровень определения, чтобы выполнять считывание данных из выбранной ячейки памяти.

[ВАРИАНТ ОСУЩЕСТВЛЕНИЯ]

Конфигурация и работа магнитной памяти в одном варианте осуществления будет описываться со ссылкой на Фиг.1 по 11.

(1) КОНФИГУРАЦИЯ

Конфигурация магнитной памяти в одном варианте осуществления будет описываться со ссылкой на Фиг. 1-9.

Фиг.1 является блок-схемой, показывающей пример общего примера конфигурации магнитной памяти в одном варианте осуществления.

Как показано на Фиг.1, магнитная память в одном варианте осуществления включает в себя массив 200 ячеек и множество схем, чтобы управлять работой массива ячеек.

В магнитной памяти, элемент с магниторезистивным эффектом используется в качестве элемента памяти в массиве 200 ячеек. Магнитная память в настоящем варианте осуществления является, например, магниторезистивной оперативной памятью (MRAM).

MRAM в одном варианте осуществления включает в себя схему 110 интерфейса для передачи/приема данных между MRAM (например, модулем MRAM) и внешним устройством (например, контроллером памяти или хостовым устройством) и передачи/приема сигнала управления (команды/состояния). Буфер 111 CA и буфер 112 DQ обеспечиваются внутри схемы 110 интерфейса.

Буфер 111 CA принимает сигнал команды/адреса, сигнал активирования тактовых импульсов, сигнал выбора банка, внешний тактовый сигнал и подобное от внешнего устройства. Буфер 112 DQ передает или принимает сигнал ввода/вывода данных (данные), сигнал стробирования данных, и сигнал маски данных.

Генератор 120 тактовых импульсов генерирует внутренний тактовый импульс памяти MRAM на основе сигнала от буфера 111 CA на основе сигнала активирования тактовых импульсов. Сгенерированный внутренний тактовый импульс обеспечивается в предварительно определенные схемы в MRAM, такие как декодер 121 команд, мультиплексор 114, и буфер 112 DQ. Каждая схема в MRAM работает с синхронизацией операций на основе внутреннего тактового импульса, генерируемого посредством генератора 120 тактовых импульсов.

Декодер 121 команд декодирует команду на основе сигнала команды/адреса, переданного от буфера 111 CA. Декодированная команда передается в администратор 122 банков и генератор 123 напряжения.

Чтобы выполнять операцию, соответствующую сигналу команды/адреса, администратор 122 банков передает различные типы информации, такой как адреса в массиве 200 ячеек и сигналы управления для каждой схемы в банке BK, в банк BK, выбранный посредством сигнала выбора банка.

Генератор 123 напряжения генерирует различные напряжения, используемые для операции, соответствующей команде, и обеспечивает сгенерированные напряжения в предварительно определенные схемы в банке BK.

Например, в MRAM обеспечено множество банков BK.

Массив 200 ячеек обеспечен в банке BK. Глобальные разрядные шины GBL, bGBL, разрядные шины BL, bBL, глобальная числовая шина GWL, и числовая шина WL обеспечены в массиве ячеек. Множество ячеек MC памяти обеспечены в массиве 200 ячеек так, что соединены с проводниками GBL, bGBL, BL, bBL, GWL, WL.

Контроллер 130 обеспечен в банке BK. Контроллер 130 управляет работой каждой схемы в банке BK. Контроллер 130 включает в себя контроллер 131 синхронизации, предварительный декодер 132 строк, предварительный декодер 133 столбцов и подобное.

Контроллер 131 синхронизации управляет синхронизацией операций каждой схемы 140, 150, 160, 170, 180 в банке BK.

Предварительный декодер 132 строк выполняет, например, предварительное декодирование для адреса строки сигнала адреса от администратора 122 банков. Предварительный декодер 133 столбцов выполняет, например, предварительное декодирование для адреса столбца сигнала адреса от администратора 122 банков.

Декодер 140 строк декодирует адрес строки от предварительного декодера 132 строк. Декодер 140 строк управляет активацией глобальной числовой шины GWL и числовой шины (также называемой числовой подшиной) WL в массиве 200 ячеек на основе декодированного адреса строки.

Декодер 150 столбцов декодирует адрес столбца от предварительного декодера 133 столбцов. Декодер 150 столбцов управляет активацией глобальных разрядных шин GBL, bGBL и разрядных шин (также называемых разрядные подшины) BL, bBL в массиве 200 ячеек на основе декодированного адреса столбца.

Перевод ячейки MC памяти в массиве 200 ячеек в состояние доступа осуществляется посредством декодера 140 строк и декодера 150 столбцов.

Схема 180 чтения (усилитель считывания) и схема 181 записи (формирователь сигналов записи) возбуждаются, когда данные считываются/записываются из/в массив 200 ячеек соответственно.

Схема 180 чтения возбуждается для считывания данных под управлением контроллера 130. Схема 180 чтения обеспечивает ток считывания (или напряжение считывания) в ячейку MC памяти в массиве 200 ячеек, выбранную на основе сигнала адреса, посредством глобальных разрядных шин GBL, bGBL и разрядных шин BL, bBL. Схема 180 чтения считывает данные, сохраненные в ячейке MC памяти, посредством обнаружения значения тока для тока считывания или потенциала разрядной шины.

Схема 181 записи возбуждается для записи данных под управлением контроллера 130. Схема 181 записи обеспечивает ток записи в ячейку памяти в массиве 200 ячеек, выбранную на основе адреса, посредством глобальных разрядных шин GBL, bGBL и разрядных шин BL, bBL.

Например, когда данные памяти MRAM записываются посредством способа записи на основе переноса спинового момента (STT), ток записи течет через элемент с магниторезистивным эффектом в ячейке памяти. В STT-MRAM, направление, в котором ток записи протекает через элемент с магниторезистивным эффектом, управляется в соответствии с данными (например, "0" или "1"), подлежащими записи в ячейку памяти.

Схема 170 проверки и коррекции ошибок (ECC) выполняет обработку ECC над данными, подлежащими записи в массив 200 ячеек, и данными, считанными из массива 200 ячеек.

Страничный буфер 160 временно хранит данные, подлежащие записи в массив 200 ячеек, и данные, считанные из массива 200 ячеек, в блоках данных, называемых "страницы".

Мультиплексор 114 регулирует синхронизацию передачи данных между банком BK и буфером 112 (или между MRAM и внешним устройством) в синхронизации на основе внутреннего тактового импульса.

Фиг.2 является видом, показывающим пример компоновки схемы рядом с массивом ячеек памяти MRAM.

Как показано на Фиг.2, MRAM имеет базовую схему 201 и периферийную схему 209, обеспеченную рядом с массивом 200 ячеек.

В массиве 200 ячеек, множество ячеек памяти расположены в форме матрицы. Данные хранятся в каждой ячейке памяти.

Базовая схема 201 электрически соединена с массивом 200 ячеек. Данные вводятся и выводятся между базовой схемой 201 и массивом 200 ячеек. Базовая схема 201 включает в себя схему 210 локальных переключателей столбцов (LYSW), декодер 211 числовых подшин (SWD), и формирователь 212 сигналов управления локальными переключателями столбцов (LYSWDRV).

Схема 210 локальных переключателей столбцов избирательно соединяет разрядные шины BL и bBL, и глобальные разрядные шины в соответствии с адресом столбца в магнитной памяти с использованием иерархической системы разрядных шин. Декодер 211 числовых подшин активирует числовую шину и избирательно соединяет числовую шину и глобальную числовую шину в соответствии с адресом строки. Формирователь 212 сигналов управления локальными переключателями столбцов управляет включением/выключением локальных переключателей столбцов (например, транзисторов M1, M2 на Фиг.1) в схеме 210 локальных переключателей столбцов.

Например, схема 210 локальных переключателей столбцов включает в себя транзистор, имеющий заглубленный электрод затвора, декодер 211 числовых подшин включает в себя транзистор, имеющий планарный электрод затвора, и формирователь 212 сигналов управления локальными переключателями столбцов включает в себя оба из заглубленного и планарного транзисторов.

Периферийная схема (группа периферийной схемы, область периферийной схемы) 209 электрически соединена с массивом 200 ячеек посредством базовой схемы 201. Периферийная схема 209 включает в себя, например, схему управления, которая управляет базовой схемой 201 и массивом 200 ячеек, схему чтения (формирователь сигналов считывания) 180, схему записи (формирователь сигналов записи) 181 и подобное. Периферийная схема главным образом включает в себя планарные транзисторы.

Массив 200 ячеек, базовая схема 201, и периферийная схема 209 сформированы на одной и той же полупроводниковой подложке. Таким образом, базовая схема 201 и периферийная схема 209 являются смежными с массивом 200 ячеек. В этой связи, множество массивов 200 ячеек и множество базовых схем 201 могут обеспечиваться в одной полупроводниковой подложке. В этом случае, например, в полупроводниковой подложке обеспечивается одна периферийная схема (область периферийной схемы), которая является общей для множества массивов 200 ячеек и множества базовых схем 201.

Фиг.3 является эквивалентной диаграммой схемы, показывающей пример внутренней конфигурации массива ячеек памяти MRAM и пример внутренней конфигурации схемы, используемой для считывания данных.

Как показано на Фиг.3, массив 200 ячеек включает в себя множество ячеек MC памяти.

Внутри массива 200 ячеек, обеспечиваются множество разрядных шин BL<0>, BL<1>, BL<n>, bBL<0>, bBL<1>, bBL<n> и множество числовых шин WL<0>, WL<1>, WL<n>. Когда каждая из разрядной шины BL<0>, BL<1>, BL<n> не должна различаться ниже, каждая разрядная шина обозначается просто как разрядная шина BL, и когда каждая из разрядной шины bBL<0>, bBL<1>, bBL<n> не должна различаться ниже, каждая разрядная шина обозначается просто как разрядная шина bBL. Когда множество числовых шин WL<0>, WL<1>, WL<n> не должны различаться, каждая числовая шина обозначается просто как числовая шина WL.

Разрядные шины BL, bBL простираются в направлении столбца и числовая шина WL простирается в направлении строки. Упомянутые две разрядные шины BL, bBL формируют одну пару разрядных шин.

Ячейка MC памяти соединена с разрядными шинами BL, bBL и числовой шиной WL.

Множество ячеек MC памяти, расположенных в направлении столбца, соединены с одной парой разрядных шин BL, bBL. Множество ячеек MC памяти, расположенных в направлении строки, соединены с общей числовой шиной WL.

В иерархической системе разрядных шин, множество разрядных шин BL<0>, BL<1>, BL<n> соединены с одной глобальной разрядной шиной GBL посредством локальных переключателей M1<0>, M1<1>, M1<n> столбцов и множество разрядных шин bBL<0>, bBL<1>, bBL<n> соединены с другой глобальной разрядной шиной bGBL посредством локальных переключателей M2<0>, M2<1>, M2<n> столбцов.

Включение/выключение локальных переключателей M1<0>, M1<1>, M1<n>, M2<0>, M2<1>, M2<n> столбцов, соединенных с одной из разрядных шин BL, bBL соответственно, управляется посредством сигналов CSL<0>, CSL<1>, CSL<n> управления соответственно.

Когда каждый из локальных переключателей M1<0>, M1<1>, M1<n>, M2<0>, M2<1>, M2<n> столбцов не должен различаться ниже, каждый локальный переключатель столбцов обозначается просто как локальный переключатель M1 или M2 столбцов.

В иерархической системе числовых шин, например, множество числовых шин WL соединены с глобальной числовой шиной GWL посредством формирователь сигналов управления числовой подшиной или локальным переключателем строк (не показан).

Фиг.4 является видом, показывающим пример структуры ячейки MC памяти для памяти MRAM.

Ячейка MC памяти включает в себя, например, один элемент 1 с магниторезистивным эффектом в качестве элемента памяти и один переключатель 2 выбора. Переключатель 2 выбора является полевым транзистором (например, n-канальным MOS транзистором). В дальнейшем, полевой транзистор как переключатель 2 выбора в ячейке MC памяти будет называться транзистором 2 ячейки (или транзистором выбора).

Один конец элемента 1 MTJ соединен с разрядной шиной BL и другой конец элемента 1 MTJ соединен с одним концом пути тока, истоком/стоком, транзистора 2 ячейки. Другой конец пути тока, сток/исток, транзистора 2 ячейки соединен с разрядной шиной bBL. Контактный вывод управления (затвор) транзистора 2 ячейки соединен с числовой шиной WL.

Транзистор 2 ячейки обеспечен на полупроводниковой подложке 41. Транзистор 2 ячейки является, например, n-канальным MOS транзистором.

Транзистор 2 ячейки включает в себя электрод 20 затвора, заглубленный в углублении в полупроводниковой подложке 41. Диэлектрическая пленка 21 затвора обеспечивается между полупроводниковой подложкой 41 и электродом 20 затвора. В настоящем варианте осуществления, структура, в которой электрод транзистора заглублен в полупроводниковую подложку, называется заглубленной структурой затвора.

Диэлектрическая пленка 21 затвора сформирована на внутренней поверхности углубления. Электрод 20 затвора сформирован на внутренней поверхности диэлектрической пленки 21 затвора, так что нижняя сторона углубления покрыта. Электрод 20 затвора сформирован так, что простирается в направлении строки. Электрод 20 затвора используется в качестве числовой шины WL.

Изолирующий слой 29, сделанный, например, из SiN, обеспечен на диэлектрической пленке 21 затвора и верхней поверхности электрода 20 затвора, чтобы покрывать верхнюю сторону углубления. Верхняя поверхность изолирующего слоя 29 располагается приблизительно на такой же высоте, что и верхняя поверхность полупроводниковой подложки 41.

Диффузионные слои (в дальнейшем, называемые диффузионные слои истока/стока) 23, 24 как исток/сток транзистора 2 ячейки сформированы в поверхности полупроводниковой подложки 41, так что диэлектрическая пленка 21 затвора, электрод 20 затвора, и изолирующий слой 29 помещены между ними. Диффузионные слои 23, 24 транзисторов 2 ячеек для двух ячеек памяти, смежных вдоль направления столбца, совместно используются двумя ячейками памяти, смежными в направлении столбца.

Диффузионные слои 23, 24 истока/стока каждого из транзисторов 2 ячеек изолированы посредством области изоляции устройства (диэлектрической пленки изоляции устройства) в ячейках памяти, расположенных в направлении строки.

Как показано на Фиг.4, контактные столбики CP1, CP2 обеспечены в межслойной диэлектрической пленке (не показана) на полупроводниковой подложке 41 так, что соединены с диффузионными слоями 23, 24 истока/стока транзистора 2 ячейки соответственно.

Элемент 1 с магниторезистивным эффектом обеспечен на контактном столбике CP1 и элемент 1 с магниторезистивным эффектом соединен с диффузионным слоем 23 истока/стока транзистора 2 ячейки посредством контактного столбика CP1. Сквозной столбик VP обеспечен на элементе 1 с магниторезистивным эффектом и элемент с магниторезистивным эффектом соединен с разрядной шиной BL посредством сквозного столбика VP. Разрядная шина bBL соединена с диффузионным слоем 24 истока/стока транзистора 2 ячейки посредством контактного столбик CP2. В этой связи, две разрядных шины BL, bBL, формирующих пару разрядных шин, могут обеспечиваться на одном и том же уровне проводника.

Структура элемента с магниторезистивным эффектом памяти MRAM в настоящем варианте осуществления будет описываться с использованием Фиг. 5 и 6.

Фиг. 5 и 6 являются видами в разрезе, схематически показывающими структуру элемента с магниторезистивным эффектом.

Элемент с магниторезистивным эффектом, используемый для элемента 1 памяти, является элементом MTJ, содержащим магнитный туннельный переход.

Элемент 1 MTJ включает в себя первый магнитный слой 10, чья ориентация намагниченности является неизменной (фиксированной), второй магнитный слой 12, чья ориентация намагниченности является переменной, и немагнитный слой 11 между упомянутыми двумя магнитными слоями 10, 12. Слоистая структура, включающая в себя упомянутые два магнитных слоя 10, 12 и немагнитный слой 11, формирует магнитный туннельный переход. Слоистая структура 10, 11, 12, формирующая магнитный туннельный переход обеспечена, например, между двумя электродами 19A, 19B.

В настоящем варианте осуществления, магнитный слой 10, чья ориентация намагниченности является неизменной, вызывается опорным слоем 10, и магнитный слой 12, чья ориентация намагниченности является переменной, называется хранящим слоем 12. Опорный слой 10 также вызывается неизменным слоем намагниченности, фиксированным слоем, или зафиксированным слоем. Хранящий слой 12 также вызывается записывающим слоем, свободным слоем намагниченности, или свободным слоем.

Фиг.5 показывает элемент 1 MTJ плоской намагниченности (горизонтальной намагниченности). В элементе 1 MTJ плоской намагниченности, ориентация намагниченности магнитных слоев 10, 12 является параллельной поверхности пленки магнитных слоев 10, 12. Например, элемент 1 MTJ плоской намагниченности сформирован таким образом, что намагниченность магнитных слоев 10, 12 ориентирована в направлении, параллельном поверхности пленки магнитных слоев 10, 12, вследствие формы магнитной анизотропии магнитного тела. Например, элемент 1 MTJ плоской намагниченности имеет эллиптическую плоскую форму.

Фиг.6 показывает элемент 1 MTJ вертикальной намагниченности. В элементе 1 MTJ вертикальной намагниченности, ориентации намагниченности магнитных слоев 10, 12 является перпендикулярной к поверхности пленки магнитных слоев 10, 12. Элемент 1 MTJ вертикальной намагниченности сформирован таким образом, что намагниченность магнитных слоев 10, 12 ориентирована в направлении, перпендикулярном к поверхности пленки магнитных слоев 10, 12, вследствие кристальной магнитной анизотропии или поверхностной магнитной анизотропии магнитного тела. Например, элемент MTJ вертикальной намагниченности имеет круговую плоскую форму.

Когда данные записываются, ориентация намагниченности хранящего слоя 12 элемента MTJ изменяется посредством способа STT. Ориентация намагниченности хранящего слоя 12 изменяется посредством воздействия спин-поляризованных электронов, содержащихся в токе Iw, текущем через элемент 1, и равном порогу перемагничивания или более хранящего слоя 12, на намагниченность (спин) хранящего слоя 12.

"Ориентация намагниченности опорного слоя 10 является неизменной" или "ориентация намагниченности опорного слоя 10 является фиксированной" означает, что ориентация намагниченности опорного слоя 10 не изменяется, когда ток записи (ток перемагничивания) Iw, используемый, чтобы обращать ориентацию намагниченности хранящего слоя 12, течет в опорный слой 10. Таким образом, в элементе 1 MTJ, магнитный слой, имеющий большой порог перемагничивания, используется для опорного слоя 10 и магнитный слой, имеющий более малый порог перемагничивания, чем порог перемагничивания опорного слоя 10, используется для хранящего слоя 12. Соответственно, формируется элемент 1 MTJ, включающий в себя хранящий слой 12, чья ориентация намагниченности является переменной, и опорный слой 10, чья ориентация намагниченности является неизменной.

Когда ориентация намагниченности хранящего слоя 12 и ориентация намагниченности опорного слоя 10 делаются параллельными друг другу посредством способа STT, то есть, когда ориентация намагниченности хранящего слоя 12 делается такой же как ориентация намагниченности опорного слоя 10, ток Iw, текущий из хранящего слоя 12 к опорному слою 10, обеспечивается в элемент 1 MTJ. В этом случае, электроны перемещаются из опорного слоя 10 к хранящему слою 12 через туннельный барьерный слой 11. Большинство электронов (спин-поляризованных электронов) из электронов, прошедших через опорный слой 10 и туннельный барьерный слой 11, имеют такую же ориентацию, что и ориентация намагниченности (спина) опорного слоя 10. Угловой момент спина (крутящий момент спина) спин-поляризованных электронов применяется к намагниченности хранящего слоя 12 и ориентация намагниченности хранящего слоя 12 обращается на такую же ориентацию, что и ориентация опорного слоя 10. Когда ориентации намагниченности упомянутых двух магнитных слоев 10, 12 являются параллельными ориентациями, значение сопротивления элемента 1 MTJ является наименьшим. Например, данные, равные "0", назначаются элементу 1 MTJ, в котором ориентации намагниченности являются параллельными ориентациями.

Когда ориентация намагниченности хранящего слоя 12 и ориентация намагниченности опорного слоя 10 делаются антипараллельными, то есть, когда ориентация намагниченности хранящего слоя 12 делается противоположной ориентации намагниченности опорного слоя 10, ток Iw, текущий из опорного слоя 10 к хранящему слою 12, обеспечивается в элемент 1 MTJ. В этом случае, электроны перемещаются из хранящего слоя 12 к опорному слою 10. Электроны, имеющие спин, антипараллельный ориентации намагниченности опорного слоя 10, отражаются опорным слоем 10. Отраженные электроны инжектируются в хранящий слой 12 как спин-поляризованные электроны. Угловой момент спина спин-поляризованных электронов (отраженных электронов) применяется к намагниченности хранящего слоя 12 и ориентация намагниченности хранящего слоя 12 обращается на противоположную ориентацию по отношению к ориентации опорного слоя 10. Когда наборы намагниченности упомянутых двух магнитных слоев 10, 12 являются антипараллельными наборами, значение сопротивления элемента 1 MTJ является наибольшим. Например, данные, равные "1", назначаются элементу 1 MTJ, в котором наборы намагниченности являются антипараллельными наборами.

В STT-MRAM, схема 181 записи включает в себя схему источника (например, источник тока), чтобы генерировать ток Iw записи, и схему поглощения, чтобы поглощать ток Iw записи. Когда данные записываются в STT-MRAM, одна из двух разрядных шин, формирующих пару разрядных шин, соединяется со схемой источника и другая из упомянутых двух разрядных шин соединяется со схемой поглощения.

Когда данные считываются, ток Ir считывания, более малый, чем порог перемагничивания хранящего слоя 12, обеспечивается в элемент 1 MTJ. Данные, сохраненные в ячейке памяти, считываются посредством обнаружения изменений в величине тока Ir считывания в соответствии с состоянием сопротивления элемента MTJ.

Фиг.3 показывает пример конфигурации схемы для схемы 180 чтения, используемой, когда данные считываются из MRAM, в настоящем варианте осуществления.

Как показано на Фиг.3, схема 180 чтения соединяется с массивом 200 ячеек, когда данные считываются. Схема 180 чтения включает в себя усилитель 80 считывания и генератор 81 опорного уровня. Усилитель 80 считывания, показанный на Фиг.3, является усилителем считывания типа обнаружения тока. Однако усилитель считывания схемы чтения памяти MRAM в настоящем варианте осуществления может быть усилителем считывания типа обнаружения напряжения.

Усилитель 80 считывания на Фиг.3 включает в себя первый инвертор, второй инвертор, n-канальные полевые транзисторы (в дальнейшем, обозначаемые как n транзисторы) M4, M5, M6, M7, M8, M9, M15, M16, и p-канальные полевые транзисторы MOS (в дальнейшем, обозначаемые как p транзисторы) M17, M18.

Первый инвертор включает в себя p транзистор M11 и n транзистор M12. Первый инвертор включает в себя первый входной контактный вывод, первый выходной контактный вывод, и первый и второй контактные выводы напряжения. Второй инвертор включает в себя p транзистор M13 и n транзистор M14. Второй инвертор включает в себя второй входной контактный вывод, второй выходной контактный вывод, и третий и четвертый контактные выводы напряжения. Второй входной контактный вывод соединен с первым выходным контактным выводом и второй выходной контактный вывод соединен с первым входным контактным выводом.

Сток p транзистора (транзистора активации считывания) M17 соединен с первым выходным контактным выводом первого инвертора и исток p транзистора M17 соединен с контактным выводом VDD2A источника питания. Сток p транзистора (транзистора активации считывания) M18 соединен со вторым выходным контактным выводом второго инвертора и исток p транзистора M18 соединен с контактным выводом VDD2A источника питания. Сигнал SEN1 активации считывания обеспечивается из контроллера 130 в затворы p транзисторов M17, M18. Сигнал SEN1 активации считывания L (низкого) уровня обеспечивается перед считыванием данных из MRAM, чтобы включать транзисторы M17, M18 активации считывания. Узлы SO, SOb, тем самым, предварительно заряжаются. Сигнал SEN1 активации считывания H (высокого) уровня обеспечивается при считывании данных из MRAM, чтобы выключать транзисторы M17, M18 активации считывания.

Сток n транзистора M15 соединен с первым контактным выводом напряжения (истоком транзистора M12) первого инвертора и исток n транзистора M15 соединен с контактным выводом VSS заземления. Сток n транзистора M16 соединен с третьим контактным выводом напряжения (истоком транзистора M14) второго инвертора и исток n MOS транзистора M16 соединен с контактным выводом VSS заземления. Сигнал SEN2 активации считывания обеспечивается из контроллера 130 на Фиг.1 в затворы n транзисторов M15, M16. Сигнал SEN2 активации считывания H (высокого) уровня обеспечивается при считывании данных из MRAM, чтобы включать транзисторы M15, M16 активации считывания.

Первый контактный вывод напряжения (исток транзистора M12) первого инвертора соединен со стоком n транзистора (транзистора активации чтения) M5. Исток n транзистора M5 соединен с глобальной разрядной шиной GBL через n транзистор M4. Сигнал REN активации чтения обеспечивается из контроллера 130 в затвор n транзистора M5. Включение и выключение n транзистора M5 управляется посредством сигнала REN активации чтения.

Напряжение Vclamp фиксации обеспечивается в затвор n транзистора (транзистора фиксации) M4. Напряжение Vclamp фиксации L уровня обеспечивается в затвор транзистора M4 фиксации во время режима ожидания (или перед считыванием данных) памяти MRAM, чтобы выключать (отключать) транзистор M4 фиксации. При считывании данных, напряжение Vclamp фиксации предварительно определенного значения напряжения (например, 0.1 по 0.6 В) обеспечивается в затвор транзистора M4 фиксации. Соответственно, ток, текущий в выбранную ячейку MC, ограничивается так, чтобы не превосходить верхний предел (порог перемагничивания хранящего слоя), чтобы предохранять данные, сохраненные в выбранной ячейке MC, от уничтожения.

Третий контактный вывод напряжения (исток транзистора M14) второго инвертора соединен со стоком n транзистора (транзистора активации чтения) M7. Сигнал REN активации чтения обеспечивается из контроллера 130 в затвор n транзистора M7. Включение и выключение n транзистора M7 управляется посредством сигнала REN активации чтения.

Исток n транзистора (транзистора активации чтения) M7 соединен с опорной ячейкой RC генератора 81 опорного уровня через n транзистор (опорный транзистор) M6. Опорная ячейка RC включает в себя элемент 819 сопротивления предварительно определенного значения сопротивления. В этой связи, элемент 819 сопротивления может быть элементом сопротивления, сделанным из поликристаллического кремния и диффузионного слоя или элемента MTJ.

Затвор n транзистора M8 соединен со стоком n транзистора M5 и первым контактным выводом напряжения (истоком транзистора M12) первого инвертора. Исток и сток n транзистора M8 соединены с затвором n транзистора (транзистора фиксации) M4. Напряжение Vclamp фиксации обеспечивается в исток и сток n транзистора M8.

Затвор n транзистора M9 соединен со стоком n транзистора M7 и третьим контактным выводом напряжения (истоком транзистора M14) второго инвертора. Исток и сток n транзистора M9 соединены с затвором n транзистора (транзистора фиксации) M6. Опорный потенциал VREFIx от генератора 81 опорного уровня обеспечивается в исток и сток n транзистора M9.

Генератор 81 опорного уровня генерирует опорный уровень, чтобы считывать данные. Когда данные ячейки памяти выделяются посредством усилителя считывания типа обнаружения тока, опорный ток IREFx, который должен быть опорным значением, чтобы выделять данные, генерируется посредством генератора 81 опорного уровня.

Опорный потенциал VREFIx из генератора 81 опорного уровня обеспечивается в затвор n транзистора M6 как опорного транзистора M6. Опорный транзистор M6 возбуждается с помощью силы возбуждения в соответствии с величиной обеспечиваемого опорного потенциала VREFIx. Опорный ток IREFx генерируется посредством опорного транзистора M6, возбуждаемого на опорном потенциале VREFIx, и опорной ячейки RC. Таким образом, генерируется опорный ток IREFx значения тока в соответствии с величиной обеспеченного опорного потенциала VREFIx.

Величина опорного тока IREFx управляется посредством элемента 819 сопротивления и опорного транзистора M6 в опорной ячейке таким образом, что опорный ток IREFx является промежуточным значением тока считывания, текущего через ячейку памяти, в которой сохранены данные, равные "1", (элемент MTJ состояния высокого сопротивления), и тока считывания, текущего через ячейку памяти, в которой сохранены данные, равные "0", (элемент MTJ состояния низкого сопротивления).

В усилителе считывания типа обнаружения тока, транзистор M4 фиксации функционирует как элемент управления на стороне входного контактного вывода данных усилителя 80 считывания и опорный транзистор M6 функционирует как элемент управления на стороне опорного контактного вывода усилителя считывания.

Разрядная шина (шина истока) bBL и глобальная разрядная шина (глобальная шина истока) bGBL, которые становятся стороной более низкого потенциала, когда данные считываются, соединены с контактным выводом заземления через n транзистор M3 в схеме поглощения. Включение и выключение n транзистора M3 управляется посредством сигнала SINK управления.

Когда данные считываются из MRAM, ток считывания (ток ячейки) Ir, текущий через выбранную ячейку, и опорный ток IREFx сравниваются посредством усилителя 80 считывания и сигнал H уровня или L уровня в соответствии с результатом сравнения токов Ir, IREFx удерживается посредством схемы защелки, сформированной из первого и второго инверторов (p транзисторов M11, M13 и n транзисторов M12, M14).

Сигнал, удерживаемый посредством схемы защелки в усилителе 80 считывания, выводится из узлов SO, SOb в последующую схему (например, схему ECC или буфер) в качестве выходных сигналов DO, bDO.

Например, чтобы улучшать плотность хранения для памяти, осуществляется попытка уменьшения размеров ячейки памяти и элемента MTJ в MRAM, интервала между ячейками памяти, и интервала между элементами MTJ. Как результат, имеется вероятность увеличения помех между элементами MTJ, смежными друг с другом, вызываемыми магнитными полями, генерируемыми посредством элементов MTJ.

Фиг.7 является видом, схематически показывающим ориентацию намагниченности опорного слоя элемента с магниторезистивным эффектом (элемента MTJ) в массиве ячеек памяти MRAM.

В примере, показанном на Фиг.7, один четырехугольник (квадрат) в массиве 200 ячеек соответствует одной ячейке памяти (или одному элементу MTJ). На Фиг.7, стрелка 900 в четырехугольнике указывает ориентацию намагниченности опорного слоя в элементе MTJ в каждой ячейке памяти. Фиг.7 показывает ориентацию намагниченности опорного слоя в элементе MTJ плоской намагниченности.

Как показано на Фиг.7, элемент 1 MTJ сформирован таким образом, что намагниченность опорного слоя 10 всех элементов 1 MTJ в массиве 200 ячеек ориентирована в одном и том же направлении, посредством обработки (например, приложения магнитного поля) во время процесса производства памяти MRAM.

Как описано выше, вокруг массива 200 ячеек обеспечена область формирования базовой схемы и периферийной схемы.

Фиг.8 является схематическим видом, иллюстрирующим магнитные помехи между ячейками памяти (элементами MTJ) памяти MRAM. Чтобы упростить описание, внимание сосредоточивается на одной ячейке памяти (элементе MTJ) в массиве ячеек и будут описываться магнитные помехи, возникающие между ячейкой памяти и другими ячейками, смежными с ячейкой памяти.

Восемь ячеек памяти являются непосредственно смежными с некоторой ячейкой zMC памяти. Четыре ячейки xMC памяти из этих восьми ячеек памяти являются смежными с некоторой ячейкой zMC памяти в направлении строки или направлении столбца. Оставшиеся четыре ячейки yMC памяти из этих восьми ячеек памяти являются смежными с некоторой ячейкой zMC памяти в диагональном направлении.

Чтобы упростить описание, предполагается, что плоская форма ячейки памяти является квадратом, и предполагается, что расстояние между центрами каждой ячейки памяти является интервалом между ячейками памяти. В этом случае, интервал двух ячеек памяти, смежных в направлении строки, и интервал двух ячеек памяти, смежных в направлении столбца, обозначаются как "L1". В дополнение, интервал двух ячеек памяти, смежных в диагональном направлении, обозначается как "L2". Если плоская форма ячейки памяти является квадратом, интервал L1 и интервал L2 соотносятся как L2=(√2)×L1.

В элементе MTJ, магнитный полюс хранящего слоя обозначается как "mp1" и магнитный полюс опорного слоя обозначается как "mp2". Чтобы упростить описание, предполагается, что величина магнитного полюса mp1 и величина магнитного полюса mp2 являются равными и обозначаются как магнитный полюс mp.

Когда, как показано на Фиг.7, ориентации намагниченности опорного слоя элементов MTJ восьми ячеек памяти, смежных друг с другом, являются одинаковыми направлениями, магнитная сила F1, возникающая между ячейками zMC памяти и одной ячейкой xMC памяти, смежными друг с другом в направлении столбца (или направлении строки), задается посредством mp2/(4πμ×L12) на основе закона Кулона. Магнитная сила F2, возникающая между ячейками zMC памяти и одной ячейкой xMC памяти, смежными друг с другом в диагональном направлении, задается посредством mp2/(4πμ×L22).

Когда ориентации намагниченности опорного слоя элементов MTJ ячеек памяти, смежных друг с другом, являются одинаковыми направлениями, магнитные помехи возникают между некоторой ячейкой zMC памяти и восемью ячейками xMC, yMC памяти вокруг посредством магнитных сил F1, F2 между смежными ячейками xMC, yMC, zMC памяти. Сумма магнитных сил, прикладываемых к некоторой ячейке zMC памяти от ячеек xMC, yMC памяти вокруг, приблизительно дается посредством 4×F1+4×F2.

Если, как описано выше, шаги (интервалы) L1, L2 между ячейками памяти уменьшаются с уменьшенным размером ячеек, магнитные силы F1, F2, возникающие между ячейками памяти, увеличиваются. Как результат, если шаг между ячейками памяти уменьшается, чтобы улучшать плотность хранения памяти, влияние магнитных помех между ячейками памяти увеличивается.

Как показано на Фиг.7, ячейка памяти, расположенная на краю (стороне базовой схемы/периферийной схемы) в массиве 200 ячеек, имеет более малое количество ячеек памяти, смежных с ячейкой памяти. Например, ячейка zzMC памяти, расположенная в углу массива 200 ячеек, является смежной с одной ячейкой памяти в направлении строки, смежной с одной ячейкой памяти в направлении столбца, и смежной с одной ячейкой памяти в диагональным направлением. В ячейке zzMC памяти в углу массива 200 ячеек, величина магнитной силы между ячейкой zzMC памяти и упомянутыми тремя смежными ячейками равняется приблизительно 2×F1+F2 и в ячейке zzMC памяти в соответствии с величиной магнитной силы возникают магнитные помехи.

Таким образом, магнитные помехи, возникающие в ячейке zzMC памяти в углу массива 200 ячеек, являются более малыми, чем магнитные помехи ячейки MC памяти, расположенной в центре массива 200 ячеек.

Дополнительно, ячейка памяти в центральной стороне массива 200 ячеек окружена множеством ячеек памяти многообразно, и, таким образом, влияние магнитных помех на ячейку памяти в центральной стороне массива 200 ячеек является более большим, чем влияние магнитных помех на ячейку памяти на внешней периферической стороне массива 200 ячеек.

Как описано выше, когда ориентации намагниченности опорного слоя элементов MTJ ячеек памяти, смежных друг с другом, являются одинаковыми направлениями, как показано на Фиг.7, элемент MTJ в ячейках памяти подвергается магнитным полям элементов MTJ в окружающих ячейках памяти. Влияние взаимных помех между ячейками памяти проявляет себя явным образом в ячейках памяти в центральной стороне массива ячеек, где количество ячеек памяти, расположенных в окружающей области, является большим. С другой стороны, влияние взаимных помех между ячейками памяти является малым для ячеек памяти на внешней периферической (краевой) стороне массива ячеек, где количество ячеек памяти, расположенных в окружающей области, является малым.

Даже если ячейки памяти и элементы MTJ формируются одновременно посредством общей обработки в одном и том же массиве 200 ячеек, величина магнитных помех ячейки памяти (элемента MTJ) может быть разной в соответствии с координатами (адресом) в массиве 200 ячеек вследствие магнитных помех между ячейками памяти и наблюдаемые характеристики элементов MTJ являются разными.

Отношение между положением элемента MTJ в массиве 200 ячеек и характеристиками элемента MTJ будет описываться с использованием Фиг.9.

Фиг.9 является диаграммой, иллюстрирующей отношение между положением элемента MTJ в массиве ячеек и характеристиками элемента MTJ.

Горизонтальная ось на Фиг.9 соответствует величине значения сопротивления (магнитного сопротивления) элемента MTJ и вертикальная ось на Фиг.9 показывает вероятность присутствия элемента MTJ, количество элементов, некоторого сопротивления в массиве 200 ячеек.

Как описано выше, данные, равные "0", назначаются элементу MTJ, чья ориентация намагниченности является параллельным состоянием (состоянием низкого сопротивления) SP, и данные, равные "1", назначаются элементу MTJ, чья ориентация намагниченности является антипараллельным состоянием (состоянием высокого сопротивления) SAP.

Тенденции положения в массиве ячеек и характеристик элемента MTJ будут описываться с использованием элемента MTJ между центральной частью массива 200 ячеек и внешней периферией массива ячеек (в дальнейшем, называемой промежуточной областью или опорной областью) в качестве ссылки.

Значение сопротивления элемента MTJ, расположенного на центральной стороне массива ячеек, больше затрагивается магнитными помехами между элементами MTJ, чем элемента MTJ в промежуточной области в таком же состоянии ориентации намагниченности, и, таким образом, может определяться как более большое, чем значение сопротивления элемента MTJ в промежуточной области. С другой стороны, значение сопротивления элемента MTJ, расположенного на внешней периферии массива ячеек, меньше затрагивается магнитными помехами между элементами MTJ, чем элемента MTJ в промежуточной области в таком же состоянии набора намагниченности, и, таким образом, может определяться как более малое, чем значение сопротивления элемента MTJ в промежуточной области.

При сравнении с распределением d0 элементов MTJ в состоянии удержания данных "0", расположенных в промежуточной области, распределение d0o элементов MTJ в состоянии удержания данных "0", расположенных на внешней периферической стороне (стороне базовой схемы/периферийной схемы) массива ячеек, сдвигается к стороне более низкого сопротивления. Также при сравнении с распределением d1 элементов MTJ в состоянии удержания данных "1", расположенных в промежуточной области, распределение d1o элементов MTJ в состоянии удержания данных "1", расположенных на внешней периферической стороне массива ячеек, сдвигается к стороне более низкого сопротивления.

В противоположность, при сравнении с распределением d0 элементов MTJ в состоянии удержания данных "0", расположенных в промежуточной области, распределение d0i элементов MTJ в состоянии удержания данных "0", расположенных на центральной стороне массива ячеек, сдвигается к стороне более высокого сопротивления. При сравнении с распределением d1 элементов MTJ в состоянии удержания данных "1", расположенных в промежуточной области, распределение d1i элементов MTJ в состоянии удержания данных "1", расположенных на центральной стороне массива ячеек, сдвигается к стороне более высокого сопротивления.

Таким образом, значение сопротивления (наблюдаемое значение сопротивления) элемента MTJ имеет тенденцию измеряться более высоким, чем фактическое значение сопротивления элемента MTJ вследствие магнитных помех между соседними ячейками. В этой связи, значение сопротивления элемента MTJ на внешней периферической стороне массива ячеек, где влияние магнитных помех является малым, является более близким к фактическому значению сопротивления элемента MTJ. Вследствие магнитных помех между ячейками памяти в массиве ячеек, конец распределения d0i элементов MTJ в состоянии удержания данных "0", расположенных на центральной стороне массива ячеек, может перекрываться с концом распределения d1o элементов MTJ в состоянии удержания данных "1", расположенных на внешней периферической стороне массива ячеек, между распределением d0 данных "0" и распределением d1 данных "1" элементов MTJ, расположенных в промежуточной области.

Когда уровень считывания для определения состояния сопротивления элемента MTJ устанавливается между распределением d0 данных "0" и распределением d1 данных "1" элементов MTJ, расположенных в промежуточной области массива ячеек, данные "0", сохраненные в элементе MTJ, расположенном на центральной стороне массива ячеек, и данные "1", сохраненные в элементе MTJ, расположенном на внешней периферической стороне массива ячеек, могут не определяться посредством уровня определения.

Аналогично, ошибка определения данных может возникать, когда промежуточное значение высокого сопротивления и низкого сопротивления элементов MTJ на внешней периферической стороне и центральной стороне массива ячеек используется в качестве уровня определения, общего для всех ячеек памяти.

Как результат, надежность считывания данных памяти MRAM может уменьшаться вследствие магнитных помех между ячейками памяти.

Влияние магнитных помех между ячейками памяти было описано посредством рассмотрения элемента MTJ плоской намагниченности в качестве примера, но такое влияние магнитных помех также происходит в элементе MTJ вертикальной намагниченности.

MRAM в настоящем варианте осуществления изменяет, как показано на Фиг.1, уровень определения (уровень считывания) RLx (x=1, 2, 3, ...) для считывания данных на основе величины магнитных помех между ячейками памяти в массиве ячеек. Например, MRAM в настоящем варианте осуществления выбирает один уровень определения из множества уровней определения, установленных, чтобы соответствовать величине магнитных помех между ячейками памяти в массиве ячеек, на основе величины магнитных помех между ячейками памяти в массиве ячеек и использует уровень определения при учете величины магнитных помех, чтобы выполнять операцию считывания данных из ячеек памяти, затрагиваемых магнитными помехами.

Как показано на Фиг.7, при учете сдвигов значения сопротивления элементов MTJ, вызываемых магнитными помехами между ячейками памяти, MRAM в настоящем варианте осуществления выполняет операцию считывания данных памяти MRAM посредством использования множества уровней RL1, RL2, RL3 определения, чтобы считывать данные.

Так как, как описано посредством использования Фиг.7 по 9, величина магнитных помех в массиве ячеек памяти MRAM и положение ячейки памяти могут быть связаны, MRAM в настоящем варианте осуществления выбирает один уровень определения из множества уровней RL1, RL2, RL3 определения на основе сигнала адреса, указывающего положение ячейки памяти, из которой данные должны считываться, и использует уровень определения в соответствии с координатами (величиной магнитных помех) элемента MTJ в массиве ячеек, чтобы считывать данные.

Соответственно, MRAM в настоящем варианте осуществления может препятствовать уменьшению в надежности памяти MRAM вследствие магнитных помех между элементами MTJ.

В настоящем варианте осуществления, множество областей AR, BR, XR, связанных с величиной магнитных помех, устанавливаются в массиве 200 ячеек посредством учета различий в величине магнитных помех между соседними ячейками в массиве ячеек.

В примере, показанном на Фиг.7, устанавливаются упомянутые три области AR, BR, XR. В настоящем варианте осуществления, в массиве 200 ячеек обеспечиваются область AR (в дальнейшем, называемая центральная область AR) рядом с центром массива 200 ячеек, область BR (в дальнейшем, называемая внешняя периферическая область BR) на краевой стороне (стороне базовой схемы/периферийной схемы) массива 200 ячеек, и область XR (промежуточная область XR) между областью AR рядом с центром массива ячеек и областью BR на краевой стороне.

Влияние магнитных помех с элементом 1 MTJ зависит, как описано выше, от расстояния между ячейками памяти (элементами MTJ) и количества ячеек памяти, окружающих некоторую ячейку памяти. Таким образом, на основе моделирований или экспериментальных результатов, величина магнитных помех с элементом MTJ в массиве 200 ячеек может связываться с координатами ячейки памяти массива ячеек.

Каждая область AR, BR, XR, установленная в массиве 200 ячеек, может идентифицироваться на основе диапазона, указываемого посредством адреса строки и адреса столбца, содержащихся в сигнале адреса.

Медиана между первым адресом и последним адресом из адресов столбцов в массиве 200 ячеек устанавливается как "Y0" и медиана между первым адресом и последним адресом из адресов строк в массиве 200 ячеек устанавливается как "X0". Ячейка памяти, указанная посредством адреса столбца, равного Y0, и адреса строки, равного X0, является ячейкой памяти, расположенной, по существу, в центре в массиве 200 ячеек.

Например, промежуточная область XR является областью, указываемой посредством диапазона значений адресов от "CB1" до "CA1" (в качестве более конкретного примера, CB1≤CAdd<CA1) и диапазона значений адресов от "CA2" до "CB2" (в качестве более конкретного примера, CA2<CAdd≤CB2) в отношении адреса CAdd столбца и диапазона значений адресов от "RB1" до "RA1" (в качестве более конкретного примера, RB1≤RAdd<RA1) и диапазона значений адресов от "RA2" до "RB2" (в качестве более конкретного примера, RA2<RAdd≤RB2) в отношении адреса RAdd строки.

Центральная область AR на центральной стороне массива ячеек от промежуточной области XR является областью, указываемой посредством диапазона значений адресов от "CA1" до "CA2" (в качестве более конкретного примера, CA1≤CAdd≤CA2) в отношении адреса CAdd столбца и диапазона значений адресов от "RA1" до "RA2" (в качестве более конкретного примера, RA1≤RAdd≤RA2) в отношении адреса RAdd строки.

Внешняя периферическая область (периферийная область) BR на внешней стороне массива ячеек от промежуточной области XR указывается посредством диапазона значений адресов, других, нежели адреса столбцов/строк, указывающие промежуточную область XR и центральную область AR (в качестве более конкретного примера, CAdd<CB1, CB2<CAdd, RAdd<RB1, RB2<RAdd).

В массиве 200 ячеек, например, промежуточная область XR является областью кольцевой формы, окружающей центральную область AR. Внешняя периферическая область BR является областью кольцевой формы, окружающей промежуточную область XR в массиве 200 ячеек.

Эти области AR, BR, XR, установленные в массиве 200 ячеек, не являются физически отдельными областями и вместо этого, логическими областями (виртуальными областями), идентифицируемыми посредством адреса столбца и адреса строки.

Таким образом, на основе адреса строки и адреса столбца, указывающих ячейку памяти, выбранную из внешнего устройства, чтобы из нее считывать данные, может выделяться ячейка памяти, область которой из множества областей AR, BR, XR, установленных в массиве 200 ячеек, предназначена для операции.

Пример, в котором в массиве 200 ячеек устанавливаются три области, показан в настоящем варианте осуществления, но могут устанавливаться две области или могут устанавливаться четыре или более областей в соответствии с плотностью хранения массива ячеек.

В MRAM в настоящем варианте осуществления, например, генератор 81 опорного уровня выбирает один опорный потенциал VREFIx (x=1, 2, 3) из множества опорных потенциалов VREFI1, VREFI2, VREFI3 на основе обеспеченного сигнала адреса, чтобы генерировать уровни RL1, RL2, RL3 определения, соответствующие областям AR, XR, BR, установленным в массиве 200 ячеек, соответственно. Генератор 81 опорного уровня генерирует опорный ток IREF в качестве уровней RL1, RL2, RL3 определения каждой области AR, XR, BR в массиве 200 ячеек на основе выбранного опорного потенциала VREFI. В дальнейшем, когда опорные потенциалы VREFI1, VREFI2, VREFI3 не должны различаться, опорный потенциал просто записывается как VREFI или VREFIx.

Как показано на Фиг.3, генератор 81 опорного уровня памяти MRAM в настоящем варианте осуществления включает в себя, например, множество контактных выводов напряжения, в которые вводится каждый опорный потенциал VREFI1, VREFI2, VREFI3, схему выбора (например, селектор) 811, чтобы выбирать каждый опорный потенциал VREFI1, VREFI2, VREFI3, и схему 810 управления (схему определения области), чтобы управлять работой схемы выбора.

Схема 810 управления принимает сигнал ADR адреса от контроллера 130. Схема 810 управления генерирует сигнал CNT управления схемы 811 выбора на основе сигнала ADR адреса. Схема 810 управления управляет уровнем сигнала для сигнала CNT управления на основе обработки вычисления (например, сравнения значений адресов) адреса CAdd столбца и адреса RAdd строки, содержащихся в сигнале ADR адреса.

Опорные потенциалы VREFI1, VREFI2, VREFI3, установленные, чтобы соответствовать областям AR, XR, BR, установленным в массиве 200 ячеек, вводятся во входные контактные выводы схемы 811 выбора соответственно. Например, количество опорных потенциалов соответствует количеству областей, установленных в массиве ячеек.

Сигнал CNT управления из схемы 810 управления обеспечивается в контактный вывод управления схемы 811 выбора. Схема 811 выбора выбирает один из множества опорных потенциалов VREFI на основе сигнала CNT управления и обеспечивает выбранный опорный потенциал VREFI в элемент управления входного контактного вывода на стороне опорного уровня усилителя 80 считывания.

Если сигнал ADR адреса, обеспеченный в схему 810 управления, содержит адрес строки и адрес столбца, указывающие промежуточную область XR, схема 810 управления обеспечивает сигнал CNT управления в схему 811 выбора, так что опорный потенциал VREFI2 промежуточной величины среди упомянутых трех опорных потенциалов VREFI обеспечивается в усилитель 80 считывания. На основе сигнала CNT управления от схемы 810 управления, схема 811 выбора выбирает опорный потенциал VREFI2 промежуточной величины среди упомянутых трех опорных потенциалов VREFI. Выбранный опорный потенциал VREFI2 обеспечивается в затвор опорного транзистора M6 усилителя 80 считывания в качестве напряжения управления входного контактного вывода на опорной стороне усилителя 80 считывания.

Соответственно, опорный ток IREF2 генерируется в качестве уровня RL2 определения, чтобы выделять данные ячейки памяти в промежуточной области XR посредством опорного транзистора M6, в который обеспечивается опорный потенциал VREFI2, и опорной ячейки RC.

Как описано с использованием Фиг.9, вследствие магнитных помех между ячейками памяти (элементами MTJ), значение сопротивления (наблюдаемое значение сопротивления) элемента MTJ в центральной области AR сдвигается к более высокому уровню, чем значение сопротивления (наблюдаемое значение сопротивления) элемента MTJ в промежуточной области XR. Таким образом, уровень RL1, более высокий, чем уровень RL2 определения, используемый для элемента MTJ в промежуточной области XR, используется в качестве уровня RL1 определения значения сопротивления элемента MTJ (данных ячейки памяти) в центральной области AR.

Если сигнал ADR адреса содержит адрес строки и адрес столбца, указывающие центральную область AR, схема 810 управления обеспечивает сигнал CNT управления в схему 811 выбора, так что опорный потенциал VREFI1, более большой, чем промежуточный опорный потенциал VREFI2 среди упомянутых трех опорных потенциалов VREFI, обеспечивается в усилитель 80 считывания. На основе сигнала CNT управления, схема 811 выбора выбирает наибольший опорный потенциал VREFI1 среди упомянутых трех опорных потенциалов VREFI.

Выбранный опорный потенциал VREFI1 обеспечивается в затвор опорного транзистора M6 усилителя 80 считывания и опорный ток IREF1 генерируется в качестве уровня RL1 определения, чтобы выделять данные ячейки памяти в центральной области AR посредством опорного транзистора M6, в который обеспечивается опорный потенциал VREFI1, и опорной ячейки RC.

В дополнение, вследствие магнитных помех между ячейками памяти (элементами MTJ), значение сопротивления (наблюдаемое значение сопротивления) элемента MTJ во внешней периферической области BR сдвигается к более низкому уровню, чем значение сопротивления элемента MTJ в промежуточной области XR. Таким образом, уровень, более низкий, чем уровень RL2 определения, используемый для элемента MTJ в промежуточной области XR, используется в качестве уровня RL3 определения значения сопротивления элемента MTJ (данных ячейки памяти) во внешней периферической области BR.

Если сигнал ADR адреса содержит адрес строки и адрес столбца, указывающие внешнюю периферическую область BR, схема 810 управления обеспечивает сигнал CNT управления в схему 811 выбора, так что опорный потенциал VREFI3, более малый, чем промежуточный опорный потенциал VREFI2 среди упомянутых трех опорных потенциалов VREFI, обеспечивается в усилитель 80 считывания. На основе сигнала CNT управления, схема 811 выбора выбирает наименьший опорный потенциал VREFI3 среди упомянутых трех опорных потенциалов VREFI.

Выбранный опорный потенциал VREFI3 обеспечивается в затвор опорного транзистора M6 усилителя 80 считывания и опорный ток IREF3 генерируется в качестве уровня RL3 определения, чтобы выделять данные ячейки MC памяти во внешней периферической области BR посредством опорного транзистора M6, в который обеспечивается опорный потенциал VREFI3, и опорной ячейки RC.

Таким образом, один опорный потенциал, выбранный из множества опорных потенциалов VREFI, имеющих разные величины, на основе сигнала ADR адреса, обеспечивается в качестве напряжения управления на опорной стороне входного контактного вывода усилителя 80 считывания в затвор (контактный вывод управления) опорного транзистора M6 как элемент управления. Опорный транзистор M6 возбуждается на основе величины выбранного опорного потенциала VREFI. Опорный ток IREF величины, соответствующей величине опорного потенциала VREFI, генерируется посредством опорной ячейки RC и опорного транзистора M6, возбуждаемого на опорном потенциале VREFI.

Например, опорный ток IREF1, когда используется опорный потенциал VREFI1, соответствующий центральной области AR, является более большим, чем опорный ток IREF2, когда используется опорный потенциал VREFI2, соответствующий промежуточной области XR. Опорный ток IREF3, когда используется опорный потенциал VREFI3, соответствующий внешней периферической области BR, является более малым, чем опорный ток IREF2, когда используется опорный потенциал VREFI2, соответствующий промежуточной области XR.

Таким образом, соответственно генерируются опорные токи IREF1, IREF2, IREF3, имеющие разные величины в качестве уровней определения (уровней считывания) RL, в соответствии с областями AR, XR, BR, выбираемыми на основе сигнала ADR адреса.

В этой связи, выделение сигнала ADR адреса посредством схемы 810 управления в генераторе 81 опорного уровня и выбор опорного потенциала VREFI посредством схемы 811 выбора могут выполняться контроллером 130 на Фиг.1. Каждый опорный потенциал VREFI может использоваться в качестве уровня определения считывания данных каждой области в соответствии с конфигурацией схемы для схемы 180 чтения и усилителя 80 считывания.

В MRAM в настоящем варианте осуществления, если величина магнитных помех между соседними ячейками (элементами MTJ) в каждой области AR, XR, BR, установленной в массиве 200 ячеек, является разной, и значение сопротивления (наблюдаемое значение сопротивления) элемента MTJ сдвигается, опорный ток IREFx, имеющий величину, которая отличается от положения (области) к положению (области) в массиве 200 ячеек, используется в качестве уровня RL определения, чтобы считывать данные на основе сигнала адреса, указывающего положение выбранной ячейки памяти в массиве 200 ячеек, чтобы выделять данные, сохраненные в выбранной ячейке MC памяти.

Согласно настоящему варианту осуществления, можно предотвращать неудачу выделения данных вследствие магнитных помех между ячейками памяти/элементами MTJ посредством того, что при считывании данных выбирается/генерируется опорный уровень, который является опорным для определения данных, в соответствии с адресом выбранной ячейки памяти.

Поэтому, согласно магнитной памяти в настоящем варианте осуществления, надежность магнитной памяти может улучшаться.

(b) ПРИМЕР РАБОТЫ

Работа магнитной памяти (например, MRAM) в одном варианте осуществления будет описываться со ссылкой на Фиг.10. Здесь, Фиг.1 по 9 также используются, когда уместно, чтобы описывать работу магнитной памяти в одном варианте осуществления.

Фиг.10 является блок-схемой последовательности операций, описывающей работу памяти MRAM в настоящем варианте осуществления.

Считывание данных из MRAM в одном варианте осуществления будет описываться с использованием Фиг.10.

Как показано на Фиг.10, считывание данных из MRAM в одном варианте осуществления начинается, когда передача данных запрашивается внешним устройством (контроллером памяти или хостовым устройством) из MRAM.

Каждая схема в MRAM возбуждается на основе команды (здесь, команды считывания) от внешнего устройства. Например, сигналы SEN1, SEN2 активации считывания и сигнал REN активации чтения обеспечиваются в усилитель 80 считывания в схеме 180 чтения, показанной на Фиг.3, чтобы активировать усилитель 80 считывания.

Сигнал ADR адреса ячейки памяти (выбранной ячейки), в которой сохранены данные, которые должны считываться, обеспечивается от внешнего устройства в MRAM (этап ST0). Сигнал ADR адреса содержит адрес CAdd столбца и адрес RAdd строки, указывающие положение выбранной ячейки в массиве ячеек.

Сигнал ADR адреса обеспечивается от контроллера 130 в MRAM в каждый декодер 132, 133, 140, 150 и также в схему 810 управления генератора 81 опорного уровня в схеме 180 чтения.

Схема 810 управления определяет, в какой области из множества областей AR, BR, XR, установленных в массиве 200 ячеек, содержатся адрес CAdd столбца и адрес RAdd строки, содержащиеся в сигнале ADR адреса (этапы ST1A, ST2A).

Например, как показано на Фиг.7, центральная область AR массива 200 ячеек является областью, указываемой посредством адреса CAdd столбца из значений адресов в диапазоне от "CA1" до "CA2" и адреса RAdd строки из значений адресов в диапазоне от "RA1" до "RA2".

То, равняется ли адрес CAdd столбца обеспеченного сигнала ADR адреса "CA1" или больше и "CA2" или меньше и адрес RAdd строки обеспеченного сигнала адреса равняется "RA1" или больше и "RA2" или меньше, определяется посредством схемы 810 управления в генераторе 81 опорного уровня (этап ST1A).

На этапе ST1A, если значение адреса RAdd столбца в сигнале ADR адреса равняется "CA1" или больше и "CA2" или меньше и значение адреса CAdd строки в сигнале ADR адреса равняется "RA1" или больше и "RA2" или меньше, схема 810 управления определяет, что выбранная ячейка, указанная посредством сигнала ADR адреса, присутствует в центральной области AR в массиве 200 ячеек (этап ST1B).

Сигнал CNT управления на основе результата определения адреса (координат) выбранной ячейки в массиве 200 ячеек обеспечивается из схемы 810 управления в схему 811 выбора. Среди множества опорных потенциалов VREFI, установленных на области AR, BR, XR в массиве 200 ячеек, опорный потенциал VREFI1, соответствующий центральной области AR, выбирается посредством сигнала CNT управления (этап ST1C).

Считывание данных с использованием уровня RL1 определения, сгенерированного из выбранного опорного потенциала VREFI1, выполняется из выбранной ячейки в центральной области AR (этап ST1D).

Например, выбранный опорный потенциал VREFI1 обеспечивается в затвор опорного транзистора M6 в качестве напряжения управления входного контактного вывода на опорной стороне усилителя 80 считывания типа обнаружения тока схемы 180 чтения и опорный транзистор M6 возбуждается посредством силы возбуждения в соответствии с величиной выбранного опорного потенциала VREFI1.

Опорный ток IREF1 в качестве уровня RL1 определения для считывания данных генерируется посредством опорной ячейки RC и опорного транзистора M6, в который обеспечивается опорный потенциал VREFI1.

Параллельно с генерированием опорного тока IREF1, разрядная шина BL и числовая шина WL активируются на основе сигнала ADR адреса под управлением контроллера 130 и декодера и ток Ir считывания обеспечивается в выбранную ячейку MC в центральной области AR, указанной посредством сигнала ADR адреса.

Величина тока Ir считывания сравнивается с величиной опорного тока IREF1 в качестве уровня RL1 определения для ячейки MC памяти в центральной области AR. Тем самым, выделяется то, являются ли данные, сохраненные в выбранной ячейке, "0" или "1". Как результат, данные считываются из выбранной ячейки в центральной области AR.

На этапе ST1A, если значение адреса CAdd столбца в сигнале ADR адреса является более малым, чем "CA1" или более большим, чем "CA2" и/или значение адреса RAdd строки в сигнале ADR адреса является более малым, чем "RA1" или более большим, чем "RA2", схема 810 управления определяет, что выбранная ячейка, указанная посредством сигнала ADR адреса, присутствует в области, другой, нежели центральная область AR в массиве 200 ячеек.

Когда выбранная ячейка не обеспечивается в центральной области AR, схема 810 управления в генераторе 81 опорного уровня определяет, равняется ли адрес CAdd столбца в сигнале ADR адреса "CB1(<CA1)" или больше и "CB2(>CA2)" или меньше и/или адрес RAdd строки обеспеченного сигнала адреса равняется "RB1(<RA1)" или больше и "RB2(>RA2)" или меньше (этап ST2A).

Если, в обработке определения сигнала адреса на этапе ST2A после этапа ST1A, значение адреса CAdd столбца в сигнале ADR адреса равняется "CB1" или больше и "CB2" или меньше и/или значение адреса RAdd строки в сигнале ADR адреса равняется "RB1" или больше и "RB2" или меньше, схема 810 управления определяет, что выбранная ячейка, указанная посредством сигнала ADR адреса, присутствует в промежуточной области XR в массиве 200 ячеек (этап ST2B).

Сигнал CNT управления на основе результата определения адреса (координат) выбранной ячейки в массиве 200 ячеек обеспечивается из схемы 810 управления в схему 811 выбора. Схема 811 выбора, принявшая сигнал CNT управления, выбирает, среди множества опорных потенциалов VREFI, установленных на области AR, BR, XR в массиве 200 ячеек, опорный потенциал VREFI2 (<VREFI1), соответствующий промежуточной области XR (этап ST2C).

Затем, считывание данных с использованием опорного тока IREF2, сгенерированного в качестве уровня RL2 определения посредством использования выбранного опорного потенциала VREFI2, выполняется из выбранной ячейки в промежуточной области XR посредством, по существу, такой же операции как на этапе ST1D (этап ST2D).

Значение сопротивления (наблюдаемое значение сопротивления) элемента MTJ в промежуточной области XR больше сдвигается к стороне более низкого сопротивления, чем значение сопротивления (наблюдаемое значение сопротивления) элемента MTJ в центральной области AR. Таким образом, опорный ток IREF2, сгенерированный посредством использования опорного потенциала VREFI2, является более малым, чем опорный ток IREF1, сгенерированный посредством использования опорного потенциала VREFI1.

Если, в обработке определения сигнала ADR адреса на этапах ST1A, ST2A, выбранная ячейка определяется как не присутствующая в центральной области AR или промежуточной области XR, схема 810 управления в генераторе 81 опорного уровня определяет, что выбранная ячейка присутствует во внешней периферической области BR в массиве 200 ячеек (этап ST3A).

Схема 811 выбора, принявшая сигнал CNT управления, соответствующий внешней периферической области BR, выбирает, среди множества опорных потенциалов VREFI, опорный потенциал VREFI3 (<VREFI2), соответствующий внешней периферической области BR (этап ST3B).

Затем, считывание данных с использованием опорного тока IREF3 в качестве уровня RL3 определения, сгенерированного посредством использования выбранного опорного потенциала VREFI3, выполняется из выбранной ячейки во внешней периферической области BR посредством, по существу, такой же операции как на этапе ST1D или ST2D (этап ST3C).

Значение сопротивления (наблюдаемое значение сопротивления) элемента MTJ во внешней периферической области BR больше сдвигается к стороне более низкого сопротивления, чем значение сопротивления (наблюдаемое значение сопротивления) элемента MTJ в центральной области AR или промежуточной области XR. Таким образом, опорный ток IREF3, сгенерированный посредством использования опорного потенциала VREFI3, является более малым, чем опорный ток IREF2, сгенерированный посредством использования опорного потенциала VREFI2.

Данные, считанные из ячейки памяти с использованием уровня определения (здесь, опорного тока IREF) в соответствии с каждой областью AR, XR, BR в массиве 200 ячеек посредством вышеописанной операции, подвергаются предварительно определенной обработке, такой как обработка ECC, перед передачей из MRAM во внешнее устройство.

В примере, показанном на Фиг.10, координаты в массиве ячеек выбранной ячейки, указанной посредством сигнала адреса, определяются от внешнего устройства в порядке: центральная область AR, промежуточная область XR, и внешняя периферическая область BR, - но настоящий вариант осуществления не ограничен таким примером. Например, координаты в массиве ячеек выбранной ячейки могут определяться на основе сигнала адреса в порядке: внешняя периферическая область BR, промежуточная область XR, и центральная область AR.

Считывание данных из MRAM в одном варианте осуществления выполняется, как описано выше.

Запись данных в MRAM в настоящем варианте осуществления выполняется посредством записи данных с использованием STT. То есть, ячейка памяти, указанная посредством сигнала адреса извне, активируется, одна разрядная шина из двух разрядных шин из пары разрядных шин устанавливается на сторону высокого потенциала в соответствии с данными, подлежащими записи, и оставшаяся разрядная шина устанавливается на сторону низкого потенциала. Ток Iw записи, текущий в направлении в соответствии с данными, подлежащими записи, обеспечивается в элемент 1 MTJ в выбранной ячейке, чтобы записывать данные посредством перемагничивания хранящего слоя.

Как описано с использованием Фиг.10, когда данные считываются из MRAM в настоящем варианте осуществления, один уровень определения выбирается из множества уровней RL определения (например, опорных токов IREF) посредством учета влияния магнитных помех между ячейками памяти, например, сдвига значения сопротивления элементов MTJ, чтобы выполнять считывание данных из MRAM.

Так как величина магнитных помех в массиве ячеек памяти MRAM и положение ячейки памяти могут быть связаны, когда данные считываются из MRAM в настоящем варианте осуществления, один уровень определения выбирается из множества уровней RL1, RL2, RL3 определения на основе сигнала адреса, указывающего положение ячейки памяти, из которой данные должны считываться.

Соответственно, выполняется считывание данных с использованием уровня определения при учете влияния магнитных помех между ячейками памяти/элементами MTJ (величины магнитных помех и различий магнитных помех от области к области).

Согласно настоящему варианту осуществления, поэтому, считывание данных из ячейки памяти, затрагиваемой магнитными помехами, выполняется с высокой точностью с использованием уровня определения при учете магнитных помех в массиве ячеек посредством того, что при считывании данных выбирается/генерируется опорный уровень, который является опорным для определения данных, в соответствии с адресом выбранной ячейки памяти, и можно предотвращать неудачу выделения данных вследствие магнитных помех между ячейками памяти/элементами MTJ.

Поэтому, согласно магнитной памяти в настоящем варианте осуществления, надежность магнитной памяти может улучшаться.

(c) МОДИФИКАЦИЯ

Модификация магнитной памяти (например, MRAM) в настоящем варианте осуществления будет описываться со ссылкой на Фиг.11.

В MRAM в одном варианте осуществления, область в массиве 200 ячеек, устанавливаемая посредством учета взаимных помех магнитных полей между ячейками памяти, устанавливается посредством диапазона, показанного посредством как адреса строки, так и адреса столбца. Затем, в MRAM в одном варианте осуществления, один уровень определения, используемый для считывания данных, выбирается из множества уровней определения (например, опорных токов) на основе адреса строки и адреса столбца, содержащихся в сигнале ADR адреса, обеспеченном извне.

Однако множество областей могут устанавливаться в массиве ячеек с использованием одного из адреса строки и адреса столбца из массива ячеек, чтобы устанавливать уровень определения (опорный потенциал и опорный ток), при учете величины магнитных помех в каждой области (различия магнитных помех от области к области) для каждой области.

Фиг.11 является схематическим видом, иллюстрирующим модификацию памяти MRAM в настоящем варианте осуществления.

Если, например, плотность хранения массива ячеек является низкой и количество ячеек памяти в массиве ячеек является малым, как показано на Фиг.11, может использоваться только адрес столбца, содержащийся в сигнале адреса, чтобы устанавливать область в массиве 200 ячеек, связанную с величиной магнитных помех.

Если, например, значение адреса для адреса CAdd столбца находится в диапазоне "CA1≤CAdd≤CA2", в массиве 200 ячеек устанавливается первая область (центральная область) AR. Например, уровень RL1 определения (опорный ток IREF1) на Фиг.7 устанавливается в качестве уровня определения для считывания данных из ячейки памяти в центральной области.

Если значение адреса для адреса CAdd столбца находится в диапазоне "CB1>CAdd" и/или "CAdd>CB2", в массиве 200 ячеек устанавливаются вторые области (внешние периферические области) BR1, BR2. Уровень RL3 определения (опорный ток IREF3) на Фиг.7 устанавливается в качестве уровня определения для считывания данных из ячейки памяти во внешних периферических областях BR1, BR2. Опорный ток IREF3 в качестве уровня RL3 определения является более малым, чем опорный ток IREF1 в качестве уровня RL1 определения.

Если значение адреса для адреса CAdd столбца находится в диапазоне "CB1≤CAdd<CA1" и/или "CA2<CAdd≤CB2", устанавливаются третьи области (промежуточные области) XR1, XR2. Уровень RL2 определения (опорный ток IREF2) на Фиг.7 устанавливается в качестве уровня определения для считывания данных из ячейки памяти в промежуточных областях XR1, XR2. Опорный ток IREF2 в качестве уровня RL2 определения является более малым, чем опорный ток IREF1 в качестве уровня RL1 определения и более большим, чем опорный ток IREF3 в качестве уровня RL3 определения.

Таким образом, множество областей (логических областей) AR, BR1, BR2, XR1, XR2, разделенных в направлении столбца, устанавливаются в массиве 200 ячеек. В дополнение, уровни RL1, RL2, RL3 определения при учете величины магнитных помех между ячейками памяти/элементами MTJ устанавливаются на области AR, BR1, BR2, XR1, XR2.

Здесь, описывается пример, в котором области в массиве ячеек устанавливаются только на основе адреса столбца и опорный ток в качестве уровня определения генерируется на основе адреса столбца, но аналогичная операция также может выполняться, когда каждая область в массиве ячеек устанавливается и идентифицируется только посредством адреса строки.

Таким образом, даже если каждая область в массиве ячеек устанавливается на основе одного из адреса строки и адреса столбца из массива ячеек и выбирается уровень определения (опорный потенциал/опорный ток) при учете величины магнитных помех для ячейки памяти (элемента MTJ), как MRAM, описанной с использованием Фиг.1 по 10, можно предотвращать неудачу выделения данных вследствие взаимных помех магнитных полей между ячейками памяти.

Поэтому, согласно магнитной памяти в настоящем варианте осуществления, надежность магнитной памяти может улучшаться.

В то время как были описаны некоторые варианты осуществления, эти варианты осуществления были представлены только в качестве примера, и не предполагается, что они ограничивают объем изобретения. В самом деле, новые способы и системы, здесь описанные, могут осуществляться в многообразии других форм; дополнительно, различные пропуски, подстановки и изменения в форме способов и систем, здесь описанных, могут делаться без отхода от сущности изобретения. Предполагается, что сопровождающие пункты формулы изобретения и их эквиваленты охватывают такие формы или модификации, которые попадают в пределы объема и сущности изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ПАМЯТИ И СПОСОБ УПРАВЛЕНИЯ ИМ | 2016 |

|

RU2669872C1 |

| ОПЕРАЦИЯ ЗАПИСИ ДЛЯ МАГНИТОРЕЗИСТИВНОГО ОПЕРАТИВНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА С ПЕРЕНОСОМ СПИНОВОГО МОМЕНТА С УМЕНЬШЕННЫМ РАЗМЕРОМ ЯЧЕЙКИ БИТА | 2009 |

|

RU2471260C2 |

| СПОСОБ ЗАПИСИ В ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, ОСНОВАННОЕ НА MRAM, ПРИ УМЕНЬШЕННОЙ ПОТРЕБЛЯЕМОЙ МОЩНОСТИ | 2011 |

|

RU2546572C2 |

| ИНТЕГРИРОВАННАЯ В СБИС ТЕХНОЛОГИИ КМОП/КНИ С n+ - И p+ - ПОЛИКРЕМНИЕВЫМИ ЗАТВОРАМИ МАТРИЦА ПАМЯТИ MRAM С МАГНИТОРЕЗИСТИВНЫМИ УСТРОЙСТВАМИ С ПЕРЕДАЧЕЙ СПИНОВОГО ВРАЩЕНИЯ | 2012 |

|

RU2515461C2 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ИЗМЕНЕНИЕМ СОПРОТИВЛЕНИЯ | 2016 |

|

RU2702271C2 |

| ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2015 |

|

RU2682387C1 |

| УСТРОЙСТВО ПАМЯТИ И СИСТЕМА ПАМЯТИ | 2015 |

|

RU2682843C1 |

| ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2014 |

|

RU2642960C2 |

| ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2015 |

|

RU2681344C1 |

| ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2014 |

|

RU2618368C2 |

Группа изобретений относится к магнитной памяти и способу управления магнитной памятью. Магнитная память содержит массив ячеек, включающий в себя множество ячеек памяти, расположенных вдоль первого и второго направлений, при этом массив ячеек включает в себя первую область и вторую область вокруг первой области, и каждая ячейка памяти включает в себя элемент с магниторезистивным эффектом в качестве элемента памяти; и схему чтения, чтобы считывать данные из ячейки памяти, выбранной на основе сигнала адреса из числа ячеек памяти, при этом схема чтения выбирает один уровень определения из множества уровней определения на основе области из числа первой и второй областей, в которой расположена выбранная ячейка памяти и использует выбранный уровень определения, чтобы выполнять считывание данных из выбранной ячейки памяти. Технический результат – повышение надежности магнитной памяти. 3 н. и 17 з.п. ф-лы, 11 ил.

1. Магнитная память, содержащая:

массив ячеек, включающий в себя множество ячеек памяти, расположенных вдоль первого и второго направлений, при этом массив ячеек включает в себя первую область и вторую область вокруг первой области, и каждая ячейка памяти включает в себя элемент с магниторезистивным эффектом в качестве элемента памяти; и

схему чтения, чтобы считывать данные из ячейки памяти, выбранной на основе сигнала адреса из числа ячеек памяти, при этом схема чтения выбирает один уровень определения из множества уровней определения на основе области из числа первой и второй областей, в которой расположена выбранная ячейка памяти, и использует выбранный уровень определения, чтобы выполнять считывание данных из выбранной ячейки памяти.

2. Магнитная память по п. 1, в которой

каждый из элементов с магниторезистивным эффектом включает в себя первый магнитный слой, в котором ориентация намагниченности является неизменной, второй магнитный слой, в котором ориентация намагниченности является переменной, и немагнитный слой между первым и вторым магнитными слоями, и