Изобретение относится к радиотехнике и может быть использовано для формирования сетки стабильных частот с равномерным шагом в приемных устройствах с повышенной помехозащищенностью, а также в приемопередающих устройствах с быстрой перестройкой рабочих частот.

В современной связной аппаратуре в качестве переносчиков спектра и гетеродинов используются прецизионные быстродействующие синтезаторы частот. Требования, предъявляемые к синтезаторам, содержат: диапазон рабочих частот, шаг перестройки по частоте, время перестройки по частоте, уровень фазовых шумов выходного сигнала, уровень паразитных спектральных составляющих. Существует множество вариантов построения синтезаторов частот, среди них: синтезатор пассивного синтеза [1], цифровой вычислительный синтезатор (или Direct Digital Synthesizer - DDS), синтезатор с импульсно-фазовой автоподстройкой частоты (ИФАПЧ) с делителем в цепи обратной связи [2], а также различные их комбинации (патенты СА 2442721, US 7579916, US 7250823). Синтезаторы пассивного синтеза обеспечивают требуемый уровень фазовых шумов выходного сигнала, но не могут обеспечить шаг перестройки по частоте, а также диапазон рабочих частот. Цифровые вычислительные синтезаторы обеспечивают требования по времени перестройки по частоте, а также уровень фазовых шумов выходного сигнала, но в выходном сигнале такого синтезатора высокий уровень паразитных спектральных составляющих, а диапазон рабочих частот ограничен. В синтезаторах частот с ИФАПЧ достигается требуемый диапазон рабочих частот и шаг перестройки по частоте, но необходимое время перестройки по частоте в сочетании с необходимым уровнем фазовых шумов выходного сигнала не выполняется.

Для удовлетворения противоречивых требований по уровню фазовых шумов выходного сигнала, времени перестройки по частоте, а также уровню побочных спектральных составляющих выходного сигнала, с сохранением диапазона рабочих частот и шага перестройки по частоте применяют комбинированные синтезаторы частот. Так в [3] описана схема построения такого синтезатора частот, в состав которого входит генератор с резонатором из сферы железо-иттриевого граната. В такой схеме в цепи обратной связи присутствует тракт приведения частоты выходного генератора к частоте сравнения на основе смесителя (или группы смесителей в общем случае), на который подается сигнал с низкими фазовыми шумами. За счет использования такого способа приведения частоты выходного сигнала синтезатора к частоте сравнения в цепи обратной связи, исключается умножение фазовых шумов в полосе пропускания системы фазовой автоподстройки, присущее синтезаторам с ИФАПЧ с делителем в цепи обратной связи.

Наиболее близким по технической сущности к предлагаемому устройству можно считать комбинированный синтезатор частот с коммутируемыми трактами приведения частоты, описанный в патенте 1187701299, принятый за прототип.

Укрупненная функциональная схема устройства-прототипа представлена на фиг.1, на которой группа смесителей заменена одним смесителем без нарушения функциональности.

На фиг.1 введены следующие обозначения:

1 - частотно-фазовый детектор (ЧФД);

2 - фильтр нижних частот (ФНЧ);

3 - генератор, управляемый напряжением (ГУН);

4 - расщепитель мощности (РМ);

5 - делитель частоты (ДЧ);

7 - смеситель;

8 - формирователь опорных частот (ФОЧ);

11 - высокочастотный коммутатор (ВК).

Устройство-прототип содержит последовательно соединенные частотно-фазовый детектор (ЧФД) 1, фильтр нижних частот (ФНЧ) 2, генератор, управляемый напряжением (ГУН) 3, и расщепитель мощности (РМ) 4, первый выход которого является выходом устройства; второй выход РМ 4 через делитель частоты (ДЧ) 5 соединен с первым входом высокочастотного коммутатора (ВК) 11, третий выход РМ 4 соединен с первым входом смесителя 7, второй вход которого соединен с первым выходом формирователя опорных частот (ФОЧ) 8, а выход смесителя 7 соединен со вторым входом ВК 11, выход которого соединен со вторым входом ЧФД 1, на первый вход которого подается сигнал со второго выхода формирователя опорных частот (ФОЧ) 8, вход которого соединен с опорным генератором (ОГ).

Устройство-прототип работает следующим образом.

Сигнал ОГ подается на вход ФОЧ 8, в котором формируются (например, с помощью набора умножителей и делителей частоты) на обоих выходах сигналы с необходимыми частотами. Со второго выхода ФОЧ 8 сигнал с частотой fог подается на первый вход ЧФД 1, на второй вход которого через блоки ВК 11, ДЧ 5 и РМ 4 поступает сигнал ГУН 3. В блоке ДЧ 5 частота fвых выходного сигнала ГУН 3 делится в N раз с целью приведения ее значения к частоте ОГ fог. Сигнал ошибки с выхода ЧФД 1 через ФНЧ 2 подается на управляющий вход ГУН 3, частота выходного сигнала которого fвых меняется до тех пор, пока, поделенная в N раз (N в общем случае может быть как целое, так и дробное) в блоке ДЧ 5, она не будет равной частоте сигнала ОГ fог. В этом случае, выходное напряжение на выходе блока ЧФД 1 перестает меняться, а частота выходного сигнала блока ГУН 3 fвых становится равной частоте ОГ fог, умноженной в N раз.

Такое состояние системы фазовой автоподстройки называется синхронизмом [2]. Выходной сигнал ГУН 3 с заданной частотой подается на вход РМ 4, с первого выхода которого подается на внешнюю нагрузку. Таким образом, частота выходного сигнала устройства определяется выражением fвых=N-fог. За счет умножения частоты выходного сигнала ГУН 3 фазовые шумы выходного сигнала устройства в полосе пропускания системы ФАПЧ представляют собой умноженные фазовые шумы опорного сигнала со второго выхода ФОЧ 8 (суммированные с шумами детектора и т.д.) [2], которые определяются фазовыми шумами сигнала опорного генератора. После наступления синхронизма происходит коммутация сигнала на втором входе ЧФД 1, на который через смеситель 7 и РМ 4 подается выходной сигнал ГУН 3. На второй вход смесителя 7 подается выходной сигнал с первого выхода ФОЧ 8, частота этого сигнала выбирается равной fфоч=fвых-fог. В смесителе 7 происходит умножение выходного сигнала ГУН 3 с сигналом первого выхода ФОЧ 8, за счет чего на выходе смесителя 7 формируется сигнал с частотой, равной разнице частот выходного сигнала блока ГУН 3 и блока ФОЧ 8 fвых-fфоч (либо fфoч-fвых, в зависимости от выбранного частотообразования устройства. В дальнейшем для простоты описания будем полагать требуемым выходной сигнал смесителя с частотой fвых-fфон). Так осуществляется приведение частоты выходного сигнала блока ГУН 3 к частоте fог. За счет выполнения равенства fог=fвых-fфоч или fог=fвых-(fвых-fог) исключается умножение частоты ОГ и, следовательно, умножение фазовых шумов выходного сигнала в полосе пропускания системы фазовой автоподстройки, которые в данном случае определяются суммой фазовых шумов опорного сигнала со второго выхода ФОЧ 8 и фазовых шумов выходного сигнала ФОЧ 8. За счет возможности использования ФНЧ 2 с широкой полосой пропускания реализуется требуемое «малое» время перестройки по частоте.

Учитывая вышесказанное, недостатком устройства-прототипа является необходимость коммутации полосы пропускания блока ФНЧ 2 ввиду изменения коэффициента умножения К, что в случае больших значений N представляет собой трудноразрешимую проблему.

Задача, на решение которой направлено заявляемое изобретение, заключается в снижении уровня фазовых шумов выходного сигнала синтезатора частот, времени перестройки по частоте, а также уровня паразитных спектральных составляющих.

Достигаемый технический результат - объединение в одном устройстве преимуществ синтезаторов частот с широкополосной ИФАПЧ с делителем в цепи обратной связи в части быстродействия, с преимуществами синтезатора частот со смесителем и аналоговым трактом приведения частоты в цепи обратной связи в части уровня фазовых шумов выходного сигнала. При этом реализуется возможность автономной работы синтезатора частот с ИФАПЧ с делителем в случае выхода из строя аналогового тракта приведения частоты.

Для решения поставленной задачи в синтезатор частот, содержащий последовательно соединенные первый частотно-фазовый детектор (ЧФД1) и первый фильтр нижних частот (ФНЧ1); последовательно соединенные генератор, управляемый напряжением (ГУН), и расщепитель мощности (РМ), первый выход которого является выходом устройства; делитель частоты (ДЧ), вход которого соединен со вторым выходом РМ; смеситель, первый вход которого соединен с третьим выходом РМ; формирователь опорных частот (ФОЧ), на вход которого подается сигнал опорного генератора (ОГ), первый выход ФОЧ соединен со вторым входом смесителя, а второй выход ФОЧ соединен с первым входом ЧФД1, согласно изобретению, дополнительно введены низкочастотный коммутатор (НК), блок управления (БУ) и последовательно соединенные второй частотно-фазовый детектор (ЧФД2) и второй фильтр нижних частот (ФНЧ2); при этом выход ДЧ соединен со вторым входом ЧФД1, второй выход которого соединен с одиночным входом БУ, группа входов которого шиной соединена с внешним управляющим устройством, а группа выходов БУ посредством шины управления соединена с группами управляющих входов ФОЧ, ДЧ и НК, первый и второй входы которого соединены соответственно с выходами ФНЧ1 и ФНЧ2, а выход НК соединен с входом ГУН; выход смесителя соединен со вторым входом ЧФД2, первый вход которого соединен с третьим выходом ФОЧ.

Блок-схема заявляемого устройства приведена на фиг.2, где введены следующие обозначения:

1 - первый частотно-фазовый детектор (ЧФД1);

2 - первый фильтр нижних частот (ФНЧ1);

3 - генератор, управляемый напряжением (ГУН);

4 - расщепитель мощности (РМ);

5 - делитель частоты (ДЧ);

6 - низкочастотный коммутатор (НК);

7 - смеситель;

8 - формирователь опорных частот (ФОЧ);

9 - второй частотно-фазовый детектор (ЧФД2);

10 - второй фильтр нижних частот (ФНЧ2);

12 - блок управления;

13 - шина управления.

Заявляемое устройство содержит последовательно соединенные первый частотно-фазовый детектор (ЧФД1) 1 и первый фильтр нижних частот (ФНЧ1) 2, выход которого соединен с первым входом низкочастотного коммутатора (НК) 6; последовательно соединенные второй частотно-фазовый детектор (ЧФД2) 9 и второй фильтр нижних частот (ФНЧ2) 10, выход которого соединен со вторым входом НК 6, выход которого через генератор, управляемый напряжением (ГУН) 3, соединен с входом расщепителя мощности (РМ) 4, первый выход которого является выходом устройства, второй выход через делитель частоты (ДЧ) 5 соединен со вторым входом ЧФД1 1, а третий выход РМ 4 соединен с первым входом смесителя 7, выход которого соединен со вторым входом ЧФД2 9, а второй вход - с первым выходом формирователя опорных частот (ФОЧ) 8. Кроме того, устройство содержит блок управления (БУ) 12, группа выходов которого соединена посредством шины управления (ШУ) 13 с группами управляющих входов НК 6, ДЧ 5 и ФОЧ 8, на одиночный вход которого поступает сигнал от опорного генератора (ОГ). При этом, группа входов БУ 12 соединена посредством шины (стандартной шины SPI или USB) с внешним управляющим устройством (ВУУ), а одиночный вход БУ 12 соединен со вторым выходом ЧФД1 1, первый вход которого соединен со вторым выходом ФОЧ 8, третий выход которого соединен с первым входом ЧФД2 9.

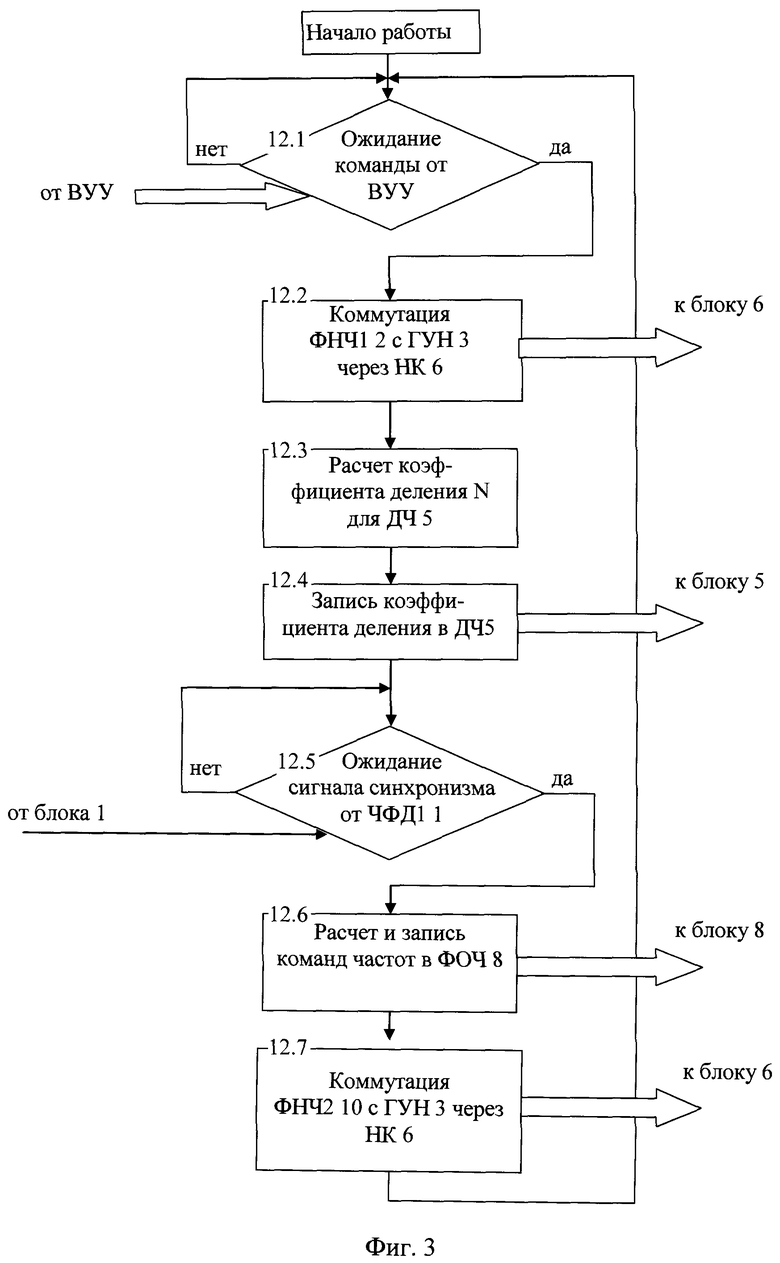

БУ 12 может быть реализован на базе микроконтроллера (например, микроконтроллера C8051Fxxx фирмы Silicon Laboratories). Алгоритм функционирования блока 12 представлен на фиг.3.

Заявляемое устройство работает следующим образом.

В исходном состоянии БУ 12 находится в режиме ожидания команды от ВУУ (блок 12.1 на фиг.3). После поступления в БУ 12 от ВУУ посредством стандартного протокола обмена (например, Serial Peripheral Interface - SPI, либо Universal Serial Bus - USB) команды записи частоты выходного сигнала синтезатора частот, в блоке 12.2 формируется сигнал коммутации, который по ШУ 13 подается в НК 6, который коммутирует выход ФНЧ1 2 с входом ГУН 3. Коммутатором в данном случае может выступать электронный ключ, например микросхема ADG713 Analog Devices, в которой переключение осуществляется логическим сигналом «0» или «1» на соответствующем управляющем выводе. Далее в блоке 12.3 происходит расчет коэффициента деления N согласно соотношению:

где fвых - частота выходного сигнала устройства;

fог1 - частота сигнала на втором выходе ФОЧ 8.

Полученное значение N посредством ШУ 13 через блок 12.4 записывается в блок ДЧ 5.

На первый вход ЧФД1 1 поступает сигнал со второго выхода ФОЧ 8 (в общем случае, на первый вход ЧФД1 1 может поступать сигнал опорного генератора без преобразования его частоты в ФОЧ 8. Таким образом, здесь и далее для простоты описания будем полагать, что сигнал опорного генератора проходит через ФОЧ 8 с преобразованием частоты в R раз, где R, помимо целых и дробных значений, может принимать значение «1»), а на второй вход ЧФД1 1 через РМ 4 поступает сигнал с выхода ГУН 3, частота которого делится в N раз в блоке ДЧ 5. Сигнал рассогласования частот сигналов, поступающих на первый и второй входы ЧФД1 1, с выхода ЧФД1 1 подается на вход ФНЧ1 2, где выделяется его постоянная составляющая, которая через НК 6 подается на управляющий вход ГУН 3, частота выходного сигнала которого fвых меняется до тех пор, пока, поделенная в N раз (N в общем случае может быть как целое, так и дробное) в блоке ДЧ 5, она не будет равной частоте fог сигнала со второго выхода ФОЧ 8. В этом случае, выходное напряжение на выходе ЧФД1 1 перестает меняться, а частота выходного сигнала ГУН 3 fвых становится равной частоте ОГ1 fог1, умноженной в N раз, т.е. система фазовой автоподстройки входит в состояние синхронизма (блок 12.5). Выходной сигнал ГУН 3 с заданной частотой подается на вход РМ 4, с первого выхода которого подается на внешнюю нагрузку. Таким образом, частота выходного сигнала устройства определяется выражением fвых=N·fог1. Аналогично с устройством-прототипом, фазовые шумы выходного сигнала устройства представляют собой умноженные фазовые шумы сигнала со второго выхода ФОЧ 8, которые определяются шумами опорного генератора.

После наступления синхронизма, на втором выходе ЧФД1 1 формируется сигнал синхронизма. Во многих современных микросхемах (например: ADF4158 Analog Devices, HMC704LP4E Hittite и т.д.) существует цифровой выход «LockDetect», показывающий логическим сигналом («0» или «1» в зависимости от микросхемы) наличие синхронизма в синтезаторе частот. После поступления сигнала синхронизма на одиночный вход БУ 12 в блоке 12.6 происходит расчет частот и необходимых для их формирования кодограмм выходных сигналов первого fог2 и третьего fфоч=fвых-fог2 выходов ФОЧ 8 (сигнал на первом выходе ФОЧ 8 может быть сформирован с помощью набора умножителей и делителей частоты, генератора гармоник, цифровых вычислительных синтезаторов и т.д.) и запись необходимых команд посредством ШУ 13 в ФОЧ 8. Затем в блоке 12.7 формируется сигнал коммутации, который по ШУ 13 подается в НК 6, посредством чего сигнал с выхода ФНЧ2 10 поступает на управляющий вход ГУН 3. При этом на первый вход блока ЧФД2 9 поступает сигнал с третьего выхода ФОЧ 8, а на второй вход блока ЧФД2 9 поступает выходной сигнал смесителя 7, в котором происходит приведение частоты выходного сигнала ГУН 3 fвых, поступающего на вход смесителя 7 через блок РМ 4, за счет смешения его с выходным сигналом блока ФОЧ 8 fфоч=fвых-fог2, к частоте сигнала с третьего выхода ФОЧ 8 fог2. Сигнал рассогласования частот, поступающих на оба входа ЧФД2 9 сигналов, подается на вход ФНЧ2, где выделяется его постоянная составляющая, которая подается на управляющий вход ГУН 3. Частота выходного сигнала меняется до тех пор, пока не выполняется равенство fог2= fвых-fфоч или fог2= fвых-(fвых- fог2). После наступления равенства fог2= fвых-fфоч напряжение на выходе ЧФД2 9 перестает меняться, и частота выходного сигнала устройства становится равной fвых= fвых + fфоч.

Таким образом, за счет использования двух частотно-фазовых детекторов и, следовательно, за счет выбора высокой частоты fог возможно уменьшить значение коэффициента N, а за счет выбора более низкой частоты fог1 возможно выбрать источник опорного сигнала с более низкими фазовыми шумами выходного сигнала. При этом за счет снижения N упрощается задача коммутации фильтров нижних частот в канале управления системы фазовой автоподстройки.

Таким образом, реализация изобретения дает возможность объединения в одном устройстве преимуществ синтезаторов частот с ИФАПЧ с делителем в цепи обратной связи в части быстродействия, с преимуществами синтезатора частот со смесителем и аналоговым трактом приведения частоты в цепи обратной связи в части уровня фазовых шумов выходного сигнала. При этом возможно реализовать автономную работу синтезатора частот с ИФАПЧ с незначительным ухудшением спектральных характеристик в случае выхода из строя аналогового тракта приведения частоты, что повышает надежность и применимость устройства.

Источники информации

1. Манассевич В. Синтезаторы частот. Теория и проектирование. Перевод с английского В.А.Повзнера, под ред. А.С.Галина. - М.: Связь, 1979 г.

2. Синтезаторы частот с системой импульсно-фазовой автоподстройки // Левин В.А., Малиновский В.Н., Романов С.К. - М.: Радио и связь, 1989 г.

3. Бельчиков С.А. Фазовый шум: как спуститься ниже -120 дБ/Гц на отстройке 10 кГц в диапазоне частот до 14 ГГц, или Борьба за децибелы // Компоненты и технологии, №5, 2009 г., с.139-146.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИНТЕЗАТОР ЧАСТОТ | 2009 |

|

RU2394367C1 |

| Синтезатор частот с широкополосной модуляцией | 2019 |

|

RU2713569C1 |

| Синтезатор частот с частотной модуляцией в SDR приложениях | 2018 |

|

RU2688243C1 |

| СИНТЕЗАТОР ЧАСТОТ | 2009 |

|

RU2395899C1 |

| Цифровой формирователь частотно-модулированных сигналов с низким уровнем искажений | 2021 |

|

RU2765273C1 |

| Гибридный многокольцевой синтезатор частот | 2021 |

|

RU2774401C1 |

| СИНТЕЗАТОР ЧАСТОТ СВЕРХВЫСОКОЧАСТОТНОГО ДИАПАЗОНА | 2006 |

|

RU2332787C1 |

| СИНТЕЗАТОР ЧАСТОТ | 2010 |

|

RU2434322C1 |

| СИНТЕЗАТОР ЧАСТОТ | 2007 |

|

RU2329594C1 |

| СИНТЕЗАТОР ЧАСТОТ | 2007 |

|

RU2329595C1 |

Синтезатор частот с коммутируемыми трактами приведения частоты относится к радиотехнике и может быть использован для формирования сетки стабильных частот с равномерным шагом в приемных устройствах с повышенной помехозащищенностью, а также в приемопередающих устройствах с быстрой перестройкой рабочих частот. Достигаемый технический результат - уменьшение уровня фазовых шумов выходного сигнала, времени перестройки по частоте, уровня паразитных спектральных составляющих. Устройство содержит два частотно-фазовых детектора (1 и 9); два фильтра нижних частот (2 и 10), генератор, управляемый напряжением (3), расщепитель мощности (4), делитель частоты (5), низкочастотный коммутатор (6), смеситель (7), формирователь опорных частот (8), блок управления (12). 3 ил.

Синтезатор частот, содержащий последовательно соединенные первый частотно-фазовый детектор (ЧФД1) и первый фильтр нижних частот (ФНЧ1); последовательно соединенные генератор, управляемый напряжением (ГУН), и расщепитель мощности (РМ), первый выход которого является выходом устройства; делитель частоты (ДЧ), вход которого соединен со вторым выходом РМ; смеситель, первый вход которого соединен с третьим выходом РМ; формирователь опорных частот (ФОЧ), на вход которого подается сигнал опорного генератора (ОГ), первый выход ФОЧ соединен со вторым входом смесителя, а второй выход ФОЧ соединен с первым входом ЧФД1, отличающийся тем, что в него дополнительно введены низкочастотный коммутатор (НК), блок управления (БУ) и последовательно соединенные второй частотно-фазовый детектор (ЧФД2) и второй фильтр нижних частот (ФНЧ2); при этом выход ДЧ соединен со вторым входом ЧФД1, второй выход которого соединен с одиночным входом БУ, группа входов которого шиной соединена с внешним управляющим устройством, а группа выходов БУ посредством шины управления соединена с группами управляющих входов ФОЧ, ДЧ и НК, первый и второй входы которого соединены соответственно с выходами ФНЧ1 и ФНЧ2, а выход НК соединен с входом ГУН; выход смесителя соединен со вторым входом ЧФД2, первый вход которого соединен с третьим выходом ФОЧ.

| СИНТЕЗАТОР ЧАСТОТЫ | 2001 |

|

RU2273952C2 |

| Приспособление для срезания излишка материала в образованных фрезом шиповых гнездах, в целях оформления их и углубления в виде ласточкина хвоста, отвечающие шипу такой же формы | 1927 |

|

SU8522A1 |

| Прозрачные каше для киносъемки | 1928 |

|

SU18032A1 |

| ТЕЛЕФОН | 1928 |

|

SU9104A1 |

| US 6765977 B1, 20.07.2004 | |||

Авторы

Даты

2014-05-27—Публикация

2013-02-05—Подача