Предлагаемое изобретение относится к области измерительной и вычислительной техники, радиотехники, связи и может использоваться в структуре различных устройств обработки аналоговой информации, измерительных приборах, системах телекоммуникаций и т.п.

В современной технике широкое применение находят параллельные аналого-цифровые преобразователи (АЦП), обеспечивающие наибольшую скорость преобразования аналоговых сигналов (uвх) в цифровые сигналы [1-27]. С повышением частоты входного напряжения uвх в таких микроэлектронных АЦП возникают существенные погрешности преобразования, обусловленные влиянием паразитных конденсаторов, образуемых емкостями на подложку активных и пассивных компонентов [28-29]. Дальнейшее повышение быстродействия параллельных АЦП - одна из проблем современной информационно-измерительной техники, решение которой позволит осуществить практическую реализацию новых систем связи и телекоммуникаций с более высокими качественными показателями.

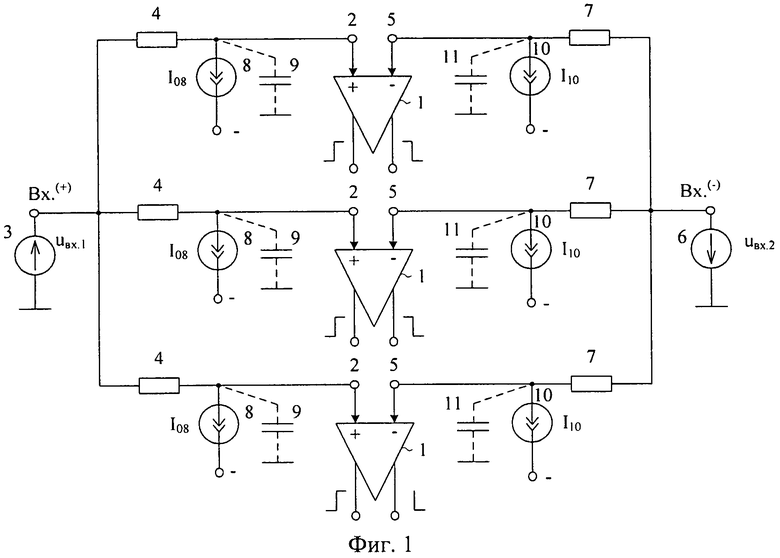

Наиболее близким по технической сущности заявляемому устройству является параллельный АЦП фиг. 1, описанный в патенте US 7.394.420, fig.3, fig.4. Анализу его предельного частотного диапазона (fв.max), а также попыткам увеличения fв.max за счет оптимизации абсолютных значений сопротивлений эталонных резисторов, посвящены статьи [28-29], в том числе соавтора настоящей заявки [29].

АЦП-прототип содержит N идентичных по архитектуре секций (фиг.1). Каждая из секций содержит компаратор напряжения 1, первый 2 вход которого соединен с первым 3 источником входного напряжения через первый 4 эталонный резистор, а второй 5 вход компаратора напряжения 1 подключен ко второму 6 источнику входного противофазного напряжения через второй 7 эталонный резистор, причем первый 2 вход компаратора напряжения 1 связан с первым 8 источником опорного тока и первым 9 паразитным конденсатором, второй 5 вход компаратора напряжения 1 связан со вторым 10 источником опорного тока и вторым 11 паразитным конденсатором.

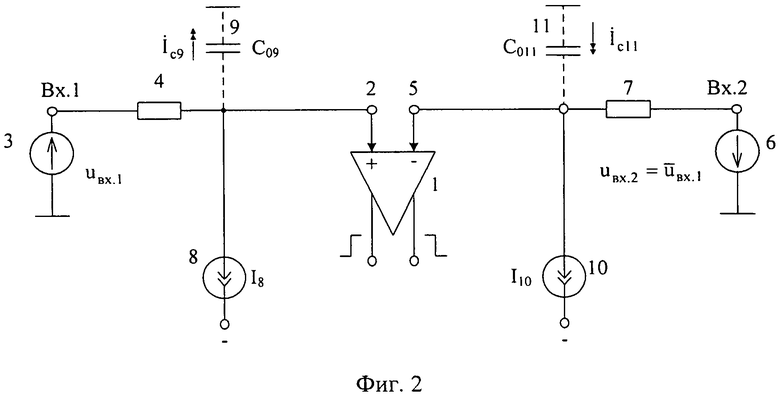

Существенный недостаток АЦП-прототипа (фиг.1), схема одной из секций которого показана на фиг. 2, состоит в том, что его предельный частотный диапазон преобразования входных аналоговых сигналов в цифру (даже при реализации на сверхвысокочастотных транзисторах с fmax=200 ГГц техпроцесса SGB25H1, IHP, Германия [28, 29]) ограничен из-за уменьшения на высоких частотах коэффициента передачи сигнала со входов АЦП до входов компараторов напряжения.

Основная задача предлагаемого изобретения состоит в расширении в несколько раз частотного диапазона обрабатываемых сигналов АЦП за счет снижения погрешности передачи входных дифференциальных напряжений от источников входных напряжений 3 и 6 ко входам компараторов напряжения 1.

Поставленная задача достигается тем, что в параллельном аналого-цифровом преобразователе с дифференциальным входом (фиг.1), каждая из N-секций которого (фиг.2) содержит компаратор напряжения 1, первый 2 вход которого соединен с первым 3 источником входного напряжения через первый 4 эталонный резистор, а второй 5 вход компаратора напряжения 1 подключен ко второму 6 источнику входного противофазного напряжения через второй 7 эталонный резистор, причем первый 2 вход компаратора напряжения 1 связан с первым 8 источником опорного тока и первым 9 паразитным конденсатором, второй 5 вход компаратора напряжения 1 связан со вторым 10 источником опорного тока и вторым 11 паразитным конденсатором, предусмотрены новые элементы и связи - первый 8 источник опорного тока выполнен в виде первого 12 токового зеркала, согласованного с первой 13 шиной источника питания, и первого 14 вспомогательного источника опорного тока, соединенного со входом первого 12 токового зеркала, причем выход первого 12 токового зеркала является выходом первого 8 источника опорного тока, а второй 6 источник входного противофазного напряжения связан со входом первого 12 токового зеркала через первый 15 корректирующий конденсатор.

На фиг.1 приведена схема АЦП - прототипа, который содержит N-параллельно включенных секций с одинаковой архитектурой (фиг.2), но разными абсолютными значениями сопротивлений эталонных резисторов 4 (7) и токов I8 (I10) источников опорных токов 8 (10).

На фиг. 2 приведена эквивалентная схема одной из секции АЦП фиг. 1, соответствующая АЦП-прототипу.

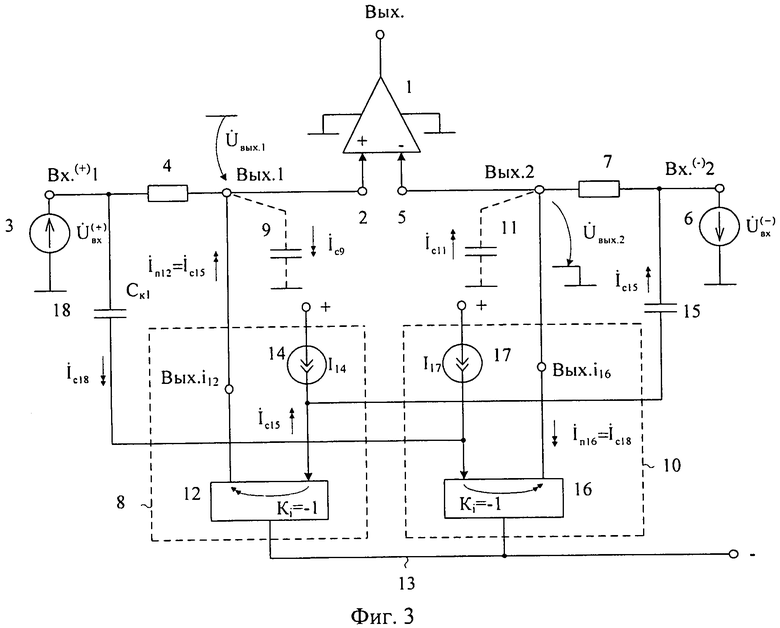

На фиг. 3 показана схема одной из секций предлагаемого АЦП, соответствующая пп. 1, 2 формулы изобретения.

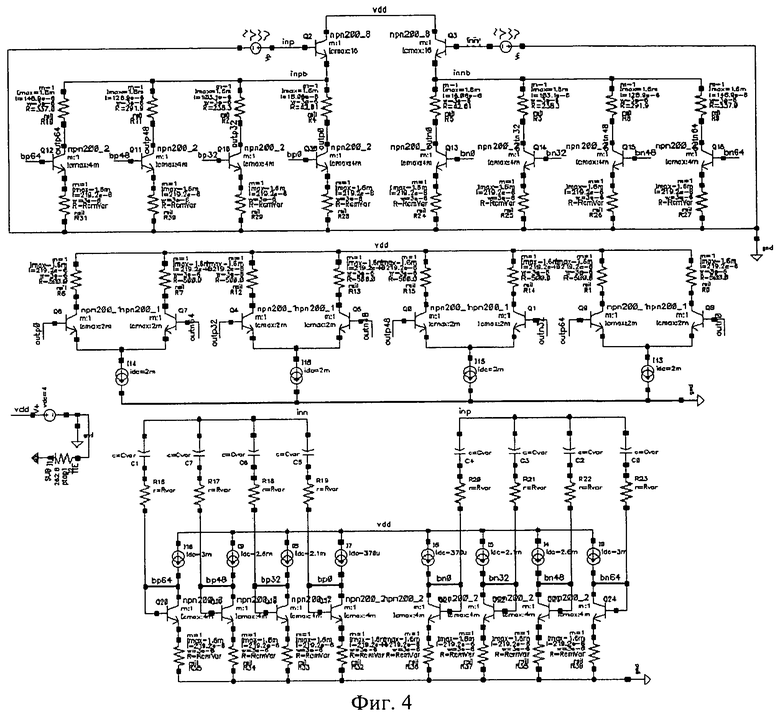

На фиг. 4 приведена эквивалентная схема заявляемого АЦП в среде Cadence на моделях SiGe транзисторов (npn 200-n; техпроцесс SG25H1, IHP, Iк.тах = 4 мА. A high-performance 0.25 µm technology with npn-HBTs up to fT/fmax=180/220 GHz.), в которой учитываются паразитные емкости реальных токовых зеркал, емкости на подложку пассивных компонентов и входные емкости компараторов напряжения 1 на основе реальных дифференциальных каскадов.

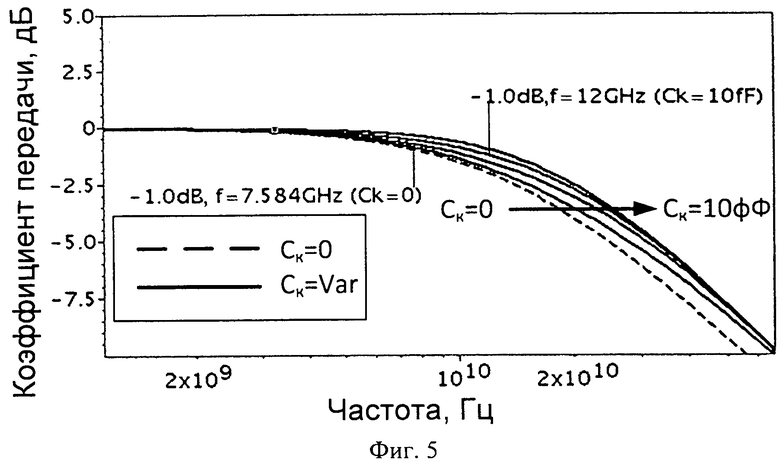

На фиг. 5 показана логарифмическая амплитудно-частотная характеристика коэффициента передачи от источников входных напряжений 3 и 6 к дифференциальному входу компаратора №2 (каналы: 32, 48) схемы АЦП фиг. 4.

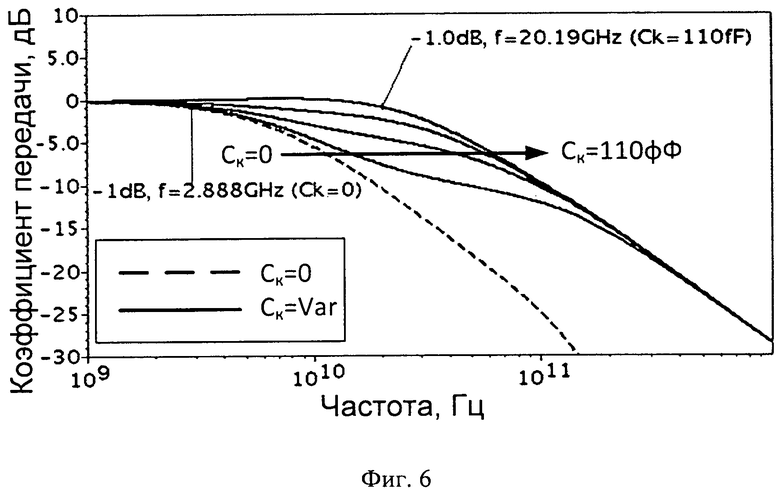

На фиг. 6 показана логарифмическая амплитудно-частотная характеристика коэффициента передачи от источников входных напряжений 3 и 6 к дифференциальному входу компаратора №2 (каналы: 32, 48) схемы АЦП фиг. 4. При этом в данной схеме:

- учитывается емкость на подложку эталонных резисторов 4 и 7;

- последовательно с каждым корректирующим конденсатором 15 и 18 Ск, включены дополнительные резисторы R=50 Ом;

- паразитная выходная емкость токовых зеркал 12 и 16 имеет сравнительно малое значение Сn=70 фФ;

- в схеме использованы реальные компараторы напряжения 1 (дифференциальные каскады) с паразитными емкостями их транзисторов.

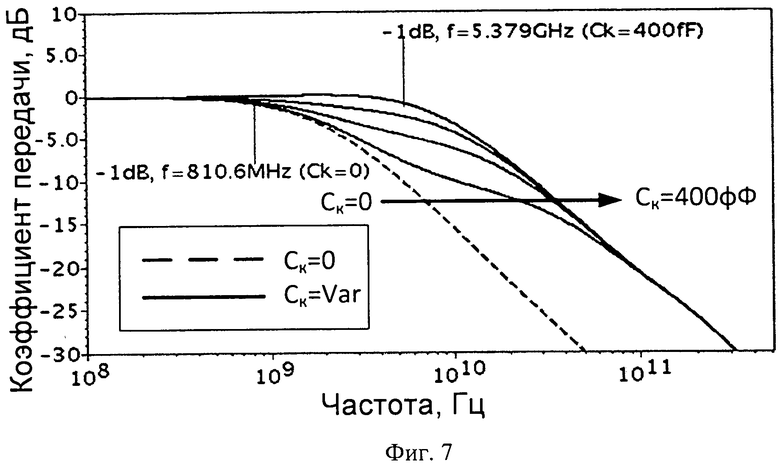

На фиг. 7 показана логарифмическая амплитудно-частотная характеристика коэффициента передачи от источников напряжений 3 и 6 к дифференциальному входу компаратора №2 (каналы: 32, 48) схемы АЦП фиг. 4. При этом в схеме фиг. 4:

- учитывается емкость на подложку эталонных резисторов 4 и 7;

- последовательно с емкостью каждого корректирующего конденсаторов 15 и 18 (Ск) включены дополнительные резисторы R=50 Ом;

- паразитная выходная емкость токовых зеркал 12 и 16 имеет повышенное значение Сn=300 фФ;

- использованы реальные компараторы напряжений 1 (дифференциальные каскады) с паразитными емкостями его транзисторов.

Сверхбыстродействующий параллельный аналого-цифровой преобразователь с дифференциальным входом содержит N идентичных по архитектуре секций фиг. 3. Каждая из секций включает компаратор напряжения 1, первый 2 вход которого соединен с первым 3 источником входного напряжения через первый 4 эталонный резистор, а второй 5 вход компаратора напряжения 1 подключен ко второму 6 источнику входного противофазного напряжения через второй 7 эталонный резистор, причем первый 2 вход компаратора напряжения 1 связан с первым 8 источником опорного тока и первым 9 паразитным конденсатором, второй 5 вход компаратора напряжения 1 связан со вторым 10 источником опорного тока и вторым 11 паразитным конденсатором. Первый 8 источник опорного тока выполнен в виде первого 12 токового зеркала, согласованного с первой 13 шиной источника питания, и первого 14 вспомогательного источника опорного тока, соединенного со входом первого 12 токового зеркала, причем выход первого 12 токового зеркала является выходом первого 8 источника опорного тока, а второй 6 источник входного противофазного напряжения связан со входом первого 12 токового зеркала через первый 15 корректирующий конденсатор. По состоянию выходов компараторов напряжения судят о цифровом эквиваленте входного сигнала.

На фиг.3, в соответствии с п.2 формулы изобретения, второй 10 источник опорного тока выполнен в виде второго 16 токового зеркала, согласованного с первой 13 шиной источника питания, и второго 17 вспомогательного источника опорного тока, соединенного со входом второго 16 токового зеркала, причем выход второго 16 токового зеркала является выходом второго 10 источника опорного тока, а первый 3 источник входного напряжения связан со входом второго 16 токового зеркала через второй 18 корректирующий конденсатор.

На фиг.4, в соответствии с п.3 формулы изобретения, последовательно с каждым корректирующим конденсатором 15 и 18 включены дополнительные резисторы.

Рассмотрим работу аналоговых секций АЦП фиг.1, фиг.2 и фиг.3, включающих эталонные резисторы 4, 7, источники опорного тока 8, 10, компаратор напряжений 1.

В АЦП-прототипе фиг.1 быстродействие аналоговой секции фиг.2 (ее предельный частотный диапазон fв.max) определяется паразитными конденсаторами 9 и 11. Практически верхняя граничная частота (по уровню - 1 дБ) АЦП-прототипа при его реализации по SiGe технологии не превышает 2-7 ГГц (фиг.5, фиг.6), в то время как быстродействие компаратора 1, реализованного на СВЧ SiGe транзисторах [28, 29] с fT=200 ГГц, позволяет работать в более широком частотном диапазоне (20÷50 ГГц).

В заявляемом устройстве фиг. 3 за счет введения новых связей предельный диапазон рабочих частот аналоговой секции АЦП расширяется в 2-6 раз (фиг.5-фиг.7). Это позволяет обеспечить аналого-цифровое преобразование более высокочастотных сигналов.

Введение последовательно с корректирующими конденсаторами 18 и 15 корректирующих резисторов (фиг.4) позволяет оптимизировать неравномерность амплитудно-частотной характеристики аналоговой части секции АЦП, что создает условия для дальнейшего расширения частотного диапазона (фиг.6, фиг.7).

Таким образом, заявляемое устройство характеризуется существенными преимуществами в сравнении с прототипом по частотном диапазону обрабатываемых сигналов.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 6.437.724 fig.4

2. Патент US 6.882.294

3. Патент US 4.229.729 fig.1

4. Патент US 4.058.806 fig.2a

5. Патент US 4.831.379 fig.8

6. Патент US 5.598.161 fig.9

7. Патентная заявка US 2010/0231430 fig.11

8. Патент US 4.912.469 fig.5, fig.6

9. Патент US 6.437.724 fig.4

10. Патент US 5.175.550 fig.2

11. Патент US 6.847.320 fig.2

12. Патент US 6.882.294 fig.3

13. Патент DE 2009/002062 fig.3

14. Патент US 5.307.067 fig.1

15. Патент US 4.745.393 fig.1

16. Патент US 5.204.679 fig.1

17. Патент US 4.719.447 fig.1

18. Патент US 4.774.498 fig.13

19. Патент US 4.768.016 fig.1

20. Патент US 7.196.649 fig.1

21. Патент US 4.752.766 fig.5

22. Патент DE 2009/002062 fig.1

23. Патент US 5.231.399 fig.2

24. Патент US 4.578.715 fig.4

25. Патент US 4.831.379 fig.4

26. Патентная заявка US 2008/036536

27. Патент US 4.763.106 fig.1

28. Y.Borokhovych. 4-bit, 16 GS/s ADC with new Parallel Reference Network. / Y.Borokhovych, H.Gustat, C.Scheytt // COMCAS 2009-2009 IEEE International Conference on Microwaves, Communications, Antennas and Electronic Systems

29. Серебряков А.И. Метод повышения быстродействия параллельных АЦП. / А.И.Серебряков, Е.Б.Борохович. // Твердотельная электроника. Сложные функциональные блоки РЭА: Материалы научно-технической конференции. - М.: МНТОРЭС им. А.С.Попова, 2012. - С.150-155.

| название | год | авторы | номер документа |

|---|---|---|---|

| СВЕРХБЫСТРОДЕЙСТВУЮЩИЙ ПАРАЛЛЕЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С ДИФФЕРЕНЦИАЛЬНЫМ ВХОДОМ | 2013 |

|

RU2523960C1 |

| СВЕРХБЫСТРОДЕЙСТВУЮЩИЙ ПАРАЛЛЕЛЬНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2013 |

|

RU2535458C1 |

| СВЕРХБЫСТРОДЕЙСТВУЮЩИЙ ПАРАЛЛЕЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С ДИФФЕРЕНЦИАЛЬНЫМ ВХОДОМ | 2013 |

|

RU2536377C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С ДИФФЕРЕНЦИАЛЬНЫМ ВХОДОМ | 2013 |

|

RU2513716C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ АТТЕНЮАТОР С РАСШИРЕННЫМ ДИАПАЗОНОМ РАБОЧИХ ЧАСТОТ | 2013 |

|

RU2535180C1 |

| ШИРОКОПОЛОСНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ АТТЕНЮАТОР | 2013 |

|

RU2523951C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ДИФФЕРЕНЦИРУЮЩИМИ ЦЕПЯМИ КОРРЕКЦИИ В МОСТОВОМ ВХОДНОМ ДИФФЕРЕНЦИАЛЬНОМ КАСКАДЕ | 2023 |

|

RU2797168C1 |

| КАСКОДНЫЙ ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ С НЕЛИНЕЙНОЙ КОРРЕКЦИЕЙ ПЕРЕХОДНОГО ПРОЦЕССА | 2023 |

|

RU2797566C1 |

| ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ДИФФЕРЕНЦИАЛЬНОГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ С НЕЛИНЕЙНОЙ КОРРЕКЦИЕЙ ПЕРЕХОДНОГО ПРОЦЕССА | 2023 |

|

RU2797043C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ДИФФЕРЕНЦИРУЮЩИМИ ЦЕПЯМИ КОРРЕКЦИИ ПЕРЕХОДНОГО ПРОЦЕССА | 2022 |

|

RU2784706C1 |

Изобретение относится к области измерительной и вычислительной техники, радиотехники и связи. Технический результат: расширение в несколько раз частотного диапазона обрабатываемых сигналов АЦП за счет снижения погрешности передачи входных дифференциальных напряжений от источников входных напряжений ко входам компараторов напряжения. Для этого предложен сверхбыстродействующий параллельный аналого-цифровой преобразователь с дифференциальным входом, который содержит N идентичных по архитектуре секций. Каждая из секций включает компаратор напряжения, первый вход которого соединен с первым источником входного напряжения через первый эталонный резистор, а второй вход компаратора напряжения подключен ко второму источнику входного противофазного напряжения через второй эталонный резистор, причем первый вход компаратора напряжения связан с первым источником опорного тока и первым паразитным конденсатором, второй вход компаратора напряжения связан со вторым источником опорного тока и вторым паразитным конденсатором. Первый источник опорного тока выполнен в виде первого токового зеркала, согласованного с первой шиной источника питания, и первого вспомогательного источника опорного тока, соединенного со входом первого токового зеркала, причем выход первого токового зеркала является выходом первого источника опорного тока, а второй источник входного противофазного напряжения связан со входом первого токового зеркала через первый корректирующий конденсатор. 2 з.п. ф-лы, 7 ил.

1. Сверхбыстродействующий параллельный аналого-цифровой преобразователь с дифференциальным входом, каждая из N секций которого содержит компаратор напряжения (1), первый (2) вход которого соединен с первым (3) источником входного напряжения через первый (4) эталонный резистор, а второй (5) вход компаратора напряжения (1) подключен ко второму (6) источнику входного противофазного напряжения через второй (7) эталонный резистор, причем первый (2) вход компаратора напряжения (1) связан с первым (8) источником опорного тока и первым (9) паразитным конденсатором, второй (5) вход компаратора напряжения (1) связан со вторым (10) источником опорного тока и вторым (11) паразитным конденсатором, отличающийся тем, что первый (8) источник опорного тока выполнен в виде первого (12) токового зеркала, согласованного с первой (13) шиной источника питания, и первого (14) вспомогательного источника опорного тока, соединенного со входом первого (12) токового зеркала, причем выход первого (12) токового зеркала является выходом первого (8) источника опорного тока, а второй (6) источник входного противофазного напряжения связан со входом первого (12) токового зеркала через первый (15) корректирующий конденсатор.

2. Сверхбыстродействующий параллельный аналого-цифровой преобразователь с дифференциальным входом по п.1, отличающийся тем, что второй (10) источник опорного тока выполнен в виде второго (16) токового зеркала, согласованного с первой (13) шиной источника питания, и второго (17) вспомогательного источника опорного тока, соединенного со входом второго (16) токового зеркала, причем выход второго (16) токового зеркала является выходом второго (10) источника опорного тока, а первый (3) источник входного напряжения связан со входом второго (16) токового зеркала через второй (18) корректирующий конденсатор.

3. Сверхбыстродействующий параллельный аналого-цифровой преобразователь с дифференциальным входом по п.2, отличающийся тем, что последовательно с каждым корректирующим конденсатором (15) и (18) включены дополнительные резисторы.

| US 7394420 B2, 01.07.2008 | |||

| DE 102009002062 A1, 07.10.2010 | |||

| БЫСТРОДЕЙСТВУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ И СПОСОБ ЕГО КАЛИБРОВКИ | 2006 |

|

RU2341017C2 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ И СПОСОБ ЕГО КАЛИБРОВКИ | 2006 |

|

RU2335844C2 |

| Аналого цифровой преобразователь | 1987 |

|

SU1550622A1 |

Авторы

Даты

2014-06-10—Публикация

2013-04-30—Подача