Изобретение относится к области радиотехники и микроэлектроники и может быть использовано в различных аналоговых и аналого-цифровых устройствах для обработки сигналов датчиков.

В радиоэлектронной аппаратуре, приборостроении и измерительной технике находят применение быстродействующие операционные усилители (ОУ), которые определяют динамические параметры многих аналоговых интерфейсов, АЦП, драйверов линий связи и т.п. Методам повышения максимальной скорости нарастания выходного напряжения (SR) ОУ с различной архитектурой и различными входными каскадами посвящено значительное количество патентов, монографий и статей, в т.ч. [1-22].

В современной микроэлектронике широкое распространение получили входные каскады быстродействующих ОУ с цепями нелинейной коррекции [20-22], которые обеспечивают некоторое повышение SR. Предлагаемое изобретение относится к данному классу входных каскадов и решает проблему существенного увеличения SR ОУ для обеих полярностей входного сигнала за счет устранения так называемой динамической асимметрии [21]. Как показано в монографии [21, с. 118], типовой входной каскад ОУ с цепью нелинейной коррекции обеспечивает существенное повышение максимальной скорости нарастания выходного напряжения только для одной из полярностей входного импульсного напряжения.

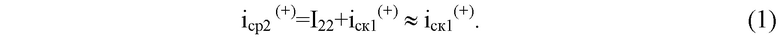

Ближайшим прототипом (фиг. 1) заявляемого устройства является схема входного дифференциального каскада, представленная в монографии «Полонников Д.Е. Операционные усилители: Принципы построения, теория, схемотехника. – М.: Энергоатомиздат, 1983. – С. 117, рис. 3.28», также в статье «Прокопенко Н.Н. Дифференциальный операционный усилитель с повышенным быстродействием // Приборы и техника эксперимента, № 2, 1978. – С. 153, рис. 1». Операционный усилитель - прототип (фиг. 1) содержит первый 1 вход устройства, соединенный с базами первого 2 и второго 3 входных транзисторов, второй 4 вход устройства, соединенный с базами третьего 5 и четвертого 6 входных транзисторов, источник опорного тока 7, включённый между объединенными эмиттерами первого 2 и третьего 5 входных транзисторов и первой 8 шиной источника питания, первый 9 и второй 10 токовые выходы устройства, согласованные со второй 11 шиной источника питания, первый 12 выходной транзистор, коллектор которого соединен с первым 9 токовым выходом устройства, второй 13 выходной транзистор, коллектор которого связан со вторым 10 токовым выходом устройства, первый 14 резистор цепи нелинейной коррекции, включенный между эмиттером второго 3 входного транзистора и эмиттером второго 13 выходного транзистора, который соединен с коллектором третьего 5 входного транзистора, второй 15 резистор цепи нелинейной коррекции, включенный между эмиттером четвертого 6 входного транзистора и эмиттером первого 12 выходного транзистора, который соединен с коллектором первого 2 входного транзистора, третий 16 токовый выход устройства, согласованный с первой 8 шиной источника питания, который подключен к коллектору второго 3 входного транзистор, четвертый 17 токовый выход устройства, согласованный с первой 8 шиной источника питания, который подключен к коллектору четвертого 6 входного транзистора.

Следует отметить, что входные дифференциальные каскады с цепями нелинейной коррекции переходных процессов достаточно популярны в современных микроэлектронных ОУ и являются основой многих быстродействующих микросхем [20,21]. Однако из-за наличия паразитной емкости Ср1 в цепи следящей связи по синфазному сигналу известные ДК фиг. 1 обеспечивают существенное повышение SR только для одной из полярностей входного сигнала. Данный недостаток подробно описан в монографии Полонникова Д.Е. [21, с. 118], подготовленной по результатам научных исследований Института проблем управления РАН (г. Москва).

Таким образом, существенный недостаток известного входного каскада быстродействующего дифференциального ОУ фиг. 1 состоит в том, что для одной из полярностей входного импульсного сигнала большой амплитуды он обеспечивает повышение SR в несколько раз, в то время как для другой полярности импульсного сигнала SR ОУ с данным входным каскадом увеличивается в десятки-сотни раз [21]. Это ограничивает применение известного схемотехнического решения в универсальных ОУ и обусловлено малыми значениями токов перезаряда паразитного конденсатора Ср1 в цепи следящей связи по синфазному сигналу, устанавливающей статический режим первого 12 и второго 13 выходных транзисторов. По многим причинам этот ток не может выбираться большим.

Основная задача предлагаемого изобретения состоит в повышении предельных значений SR в ОУ с предлагаемым входным каскадом как для положительной, так и для отрицательной полярностей входного импульсного сигнала без ухудшения энергетических параметров ОУ в статическом режиме, а также без использования дорогостоящих СВЧ технологических процессов его изготовления, обеспечивающих уменьшение паразитных емкостей схемы ОУ (Ср1, С0).

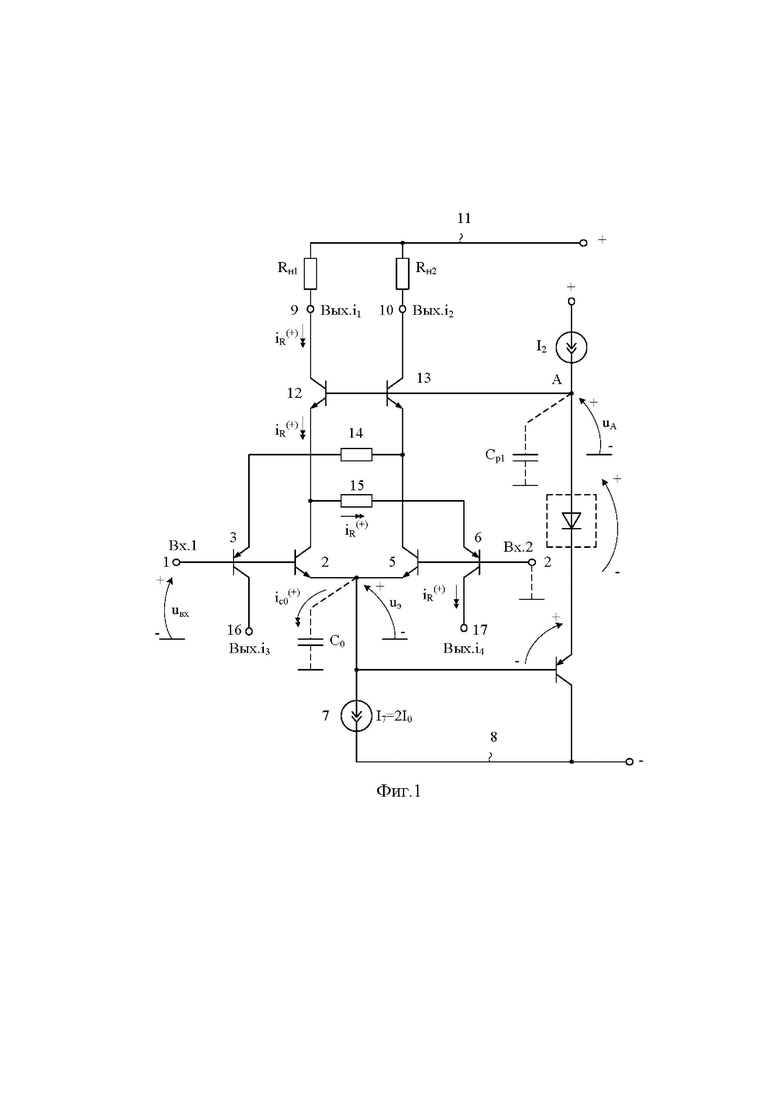

Поставленная задача достигается тем, что во входном каскаде операционного усилителя фиг.1, содержащем первый 1 вход устройства, соединенный с базами первого 2 и второго 3 входных транзисторов, второй 4 вход устройства, соединенный с базами третьего 5 и четвертого 6 входных транзисторов, источник опорного тока 7, включённый между объединенными эмиттерами первого 2 и третьего 5 входных транзисторов и первой 8 шиной источника питания, первый 9 и второй 10 токовые выходы устройства, согласованные со второй 11 шиной источника питания, первый 12 выходной транзистор, коллектор которого соединен с первым 9 токовым выходом устройства, второй 13 выходной транзистор, коллектор которого связан со вторым 10 токовым выходом устройства, первый 14 резистор цепи нелинейной коррекции, включенный между эмиттером второго 3 входного транзистора и эмиттером второго 13 выходного транзистора, который соединен с коллектором третьего 5 входного транзистора, второй 15 резистор цепи нелинейной коррекции, включенный между эмиттером четвертого 6 входного транзистора и эмиттером первого 12 выходного транзистора, который соединен с коллектором первого 2 входного транзистора, третий 16 токовый выход устройства, согласованный с первой 8 шиной источника питания, который подключен к коллектору второго 3 входного транзистор, четвертый 17 токовый выход устройства, согласованный с первой 8 шиной источника питания, который подключен к коллектору четвертого 6 входного транзистора, предусмотрены новые элементы и связи – в схему введены первый 18 и второй 19 дополнительные транзисторы, коллекторы которых согласованы со второй 11 шиной источника питания, база первого 18 дополнительного транзистора соединена со входом 1 устройства, а эмиттер через первый 20 дополнительный источник опорного тока соединен с первой 8 шиной источника питания, база второго 19 дополнительного транзистора соединена со вторым 4 входом устройства, а эмиттер через второй 21 дополнительный источник опорного тока связан с первой 8 шиной источника питания, база первого 12 выходного транзистора соединена со второй 11 шиной источника питания через третий 22 дополнительный источник опорного тока и подключена к эмиттеру второго 3 входного транзистора через первую 23 цепь согласования потенциалов, база второго 13 выходного транзистора соединена со второй 11 шиной источника питания через четвертый 24 дополнительный источник опорного тока и подключена к эмиттеру четвертого 6 входного транзистора через вторую 25 цепь согласования потенциалов, причем между базой первого 12 выходного транзистора и эмиттером первого 18 дополнительного транзистора включен первый 26 дополнительный корректирующий конденсатор, а между базой второго 13 выходного транзистора и эмиттером второго 19 дополнительного транзистора включен второй 27 дополнительный корректирующий конденсатор.

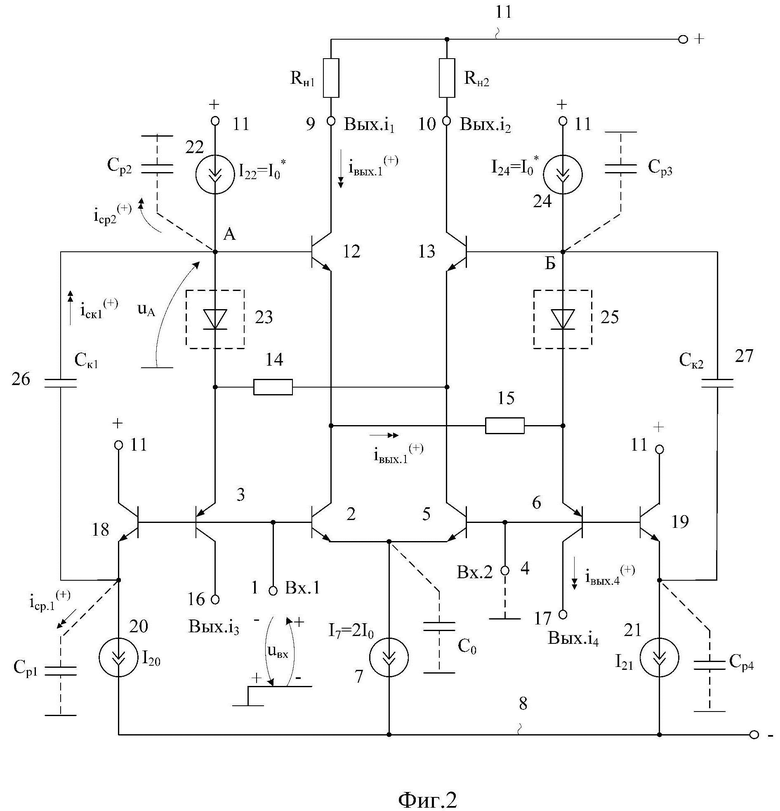

На чертеже фиг. 1 представлена схема ДК-прототипа, а на чертеже фиг.2 - схема входного дифференциального каскада быстродействующего ОУ в соответствии с формулой изобретения.

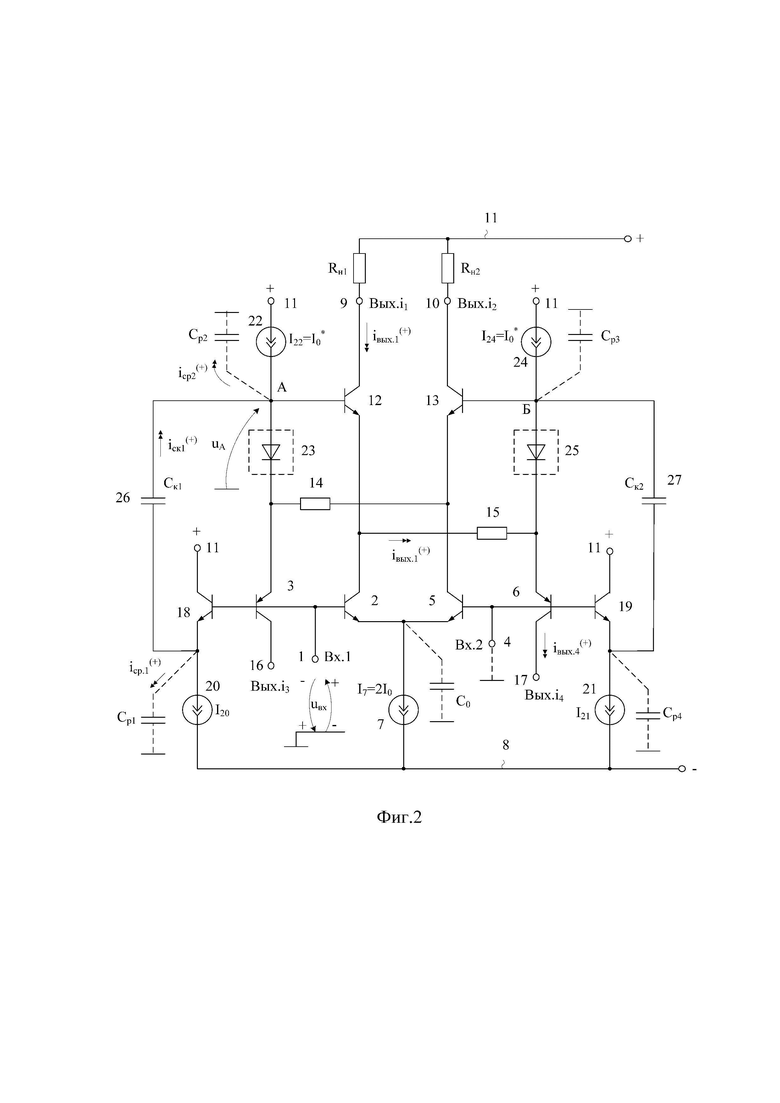

На чертеже фиг. 3 приведен первый пример построения заявляемого входного дифференциального каскада для случая, когда в его схеме вместо биполярных транзисторов используются КМОП полевые транзисторы с p- и n-каналами, имеющими аналогичные биполярным транзисторам соответствующие полярности напряжений между затвором и истоком.

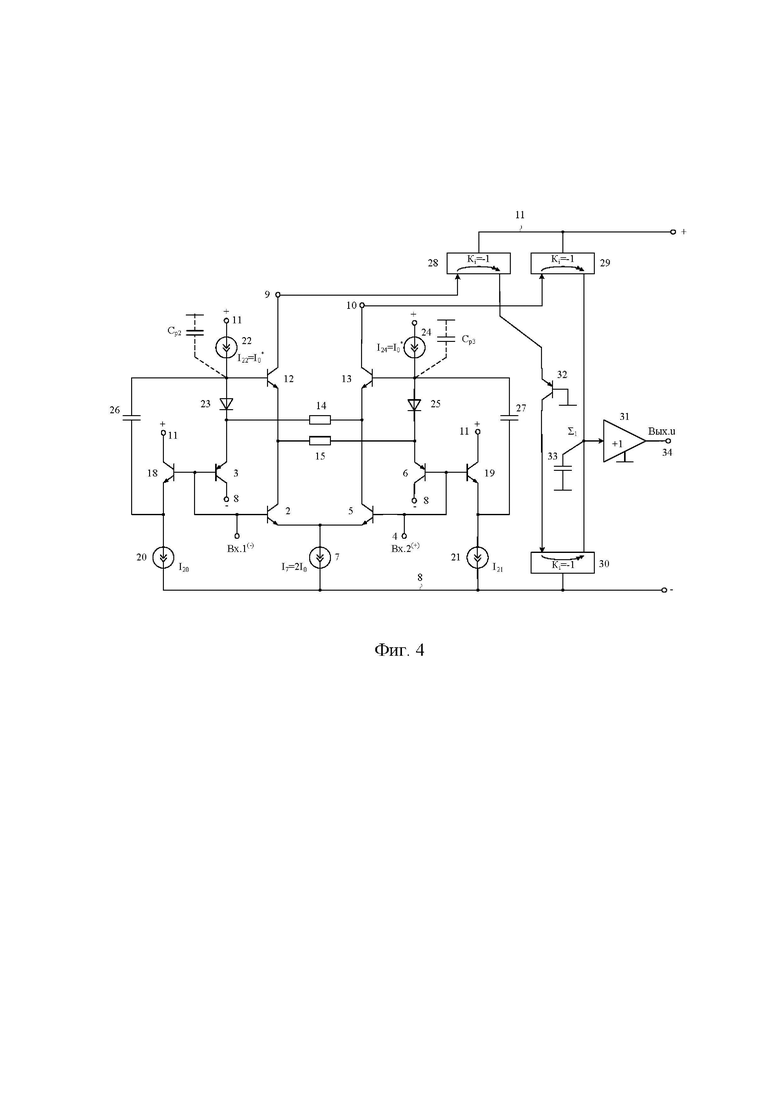

На чертеже фиг. 4 показан первый пример применения заявляемого входного дифференциального каскада в схеме быстродействующего ОУ на основе трех токовых зеркал 28, 29, 30, буферного усилителя 31, цепи согласования потенциалов на транзисторе 32, корректирующем конденсаторе 33. При этом выход 34 буферного усилителя 31 является потенциальным выходом ОУ.

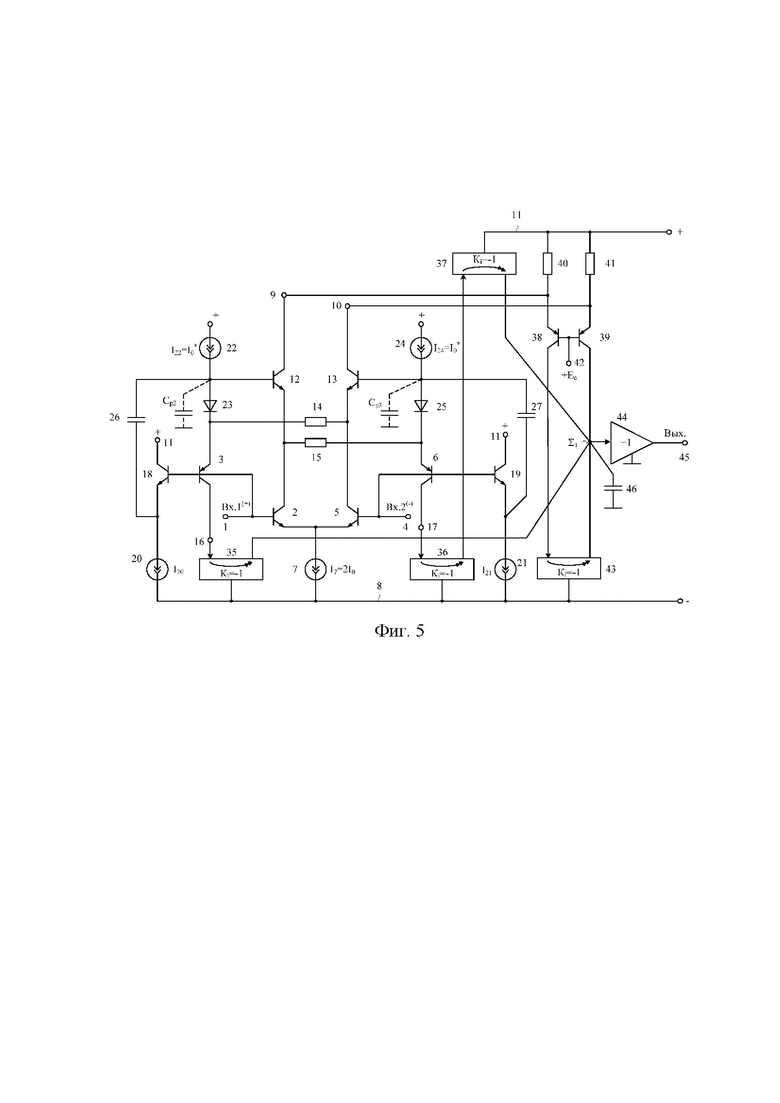

На чертеже фиг. 5 представлен второй пример применения заявляемого входного каскада фиг. 2 в схеме быстродействующего ОУ на основе трех токовых зеркал 35, 36, 37 и промежуточного «перегнутого» каскода на транзисторах 38, 39 и токовом зеркале 43. При этом статический потенциал на базах транзисторов 38 и 39 устанавливается напряжением смещения Ес (42). Резисторы 40 и 41 определяют статический режим по току транзисторов 38 и 39. Высокоимпедансный узел ОУ ∑1 связан со входом буферного усилителя 44, выход которого 45 является потенциальным выходом ОУ. Коррекция АЧХ ОУ обеспечивается корректирующим конденсатором 46.

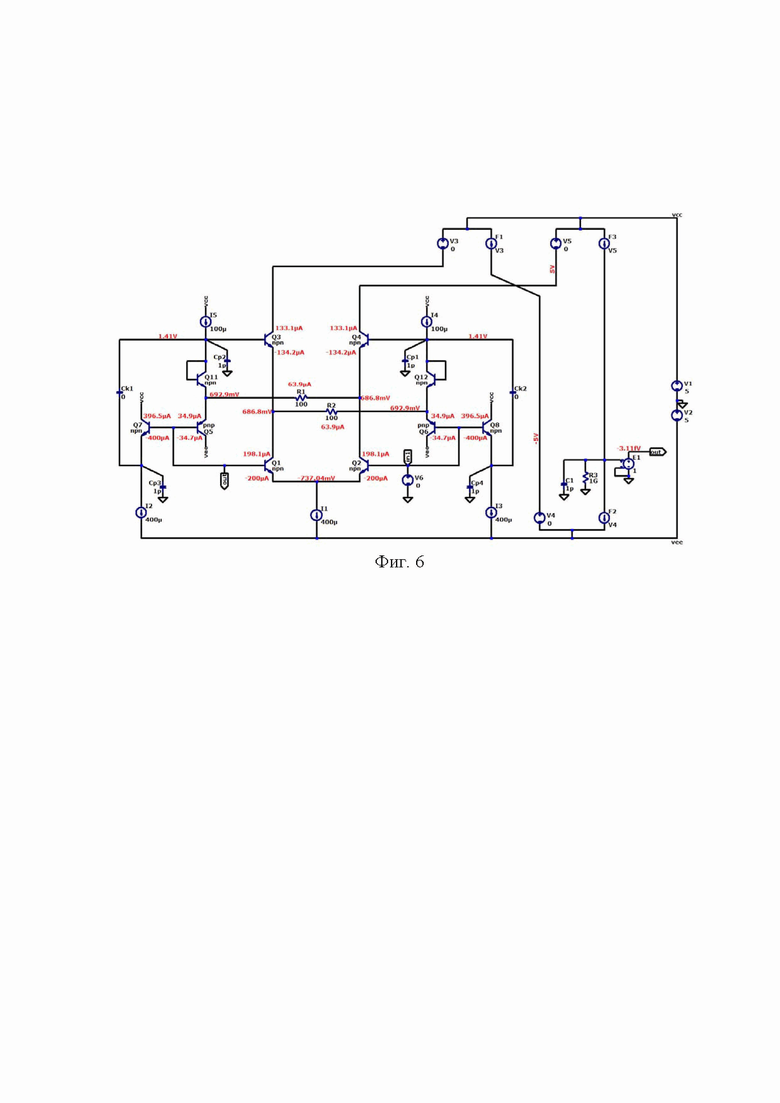

На чертеже фиг. 6 показан статический режим ОУ фиг. 4 в среде LTSpice на моделях MH2XA031_25.01.21 транзисторов АО «Интеграл» (г. Минск) при 27°С, резисторах R1=R2=100 Ом, R3=1ГОм, источниках опорного тока I1=I2=I3=400мкА, I4=I5=100мкА, конденсаторах С1=1пФ, Сk1=Сk2=0пФ, Cp1=Cp2=Cp3=Cp4=1пФ, шинах питания V1=V2=±5В.

На чертеже фиг. 7 приведена логарифмическая амплитудно-частотная характеристика коэффициент усиления по напряжению схемы ОУ фиг. 6 при С1=4пФ, Сk1=Сk2=1пФ.

На чертеже фиг. 8 показан передний фронт переходного процесса в ОУ фиг. 6 при большом импульсном входном сигнале для разных значений емкости первого 26 и второго 27 дополнительных корректирующих конденсаторов (Ск1, Ск2).

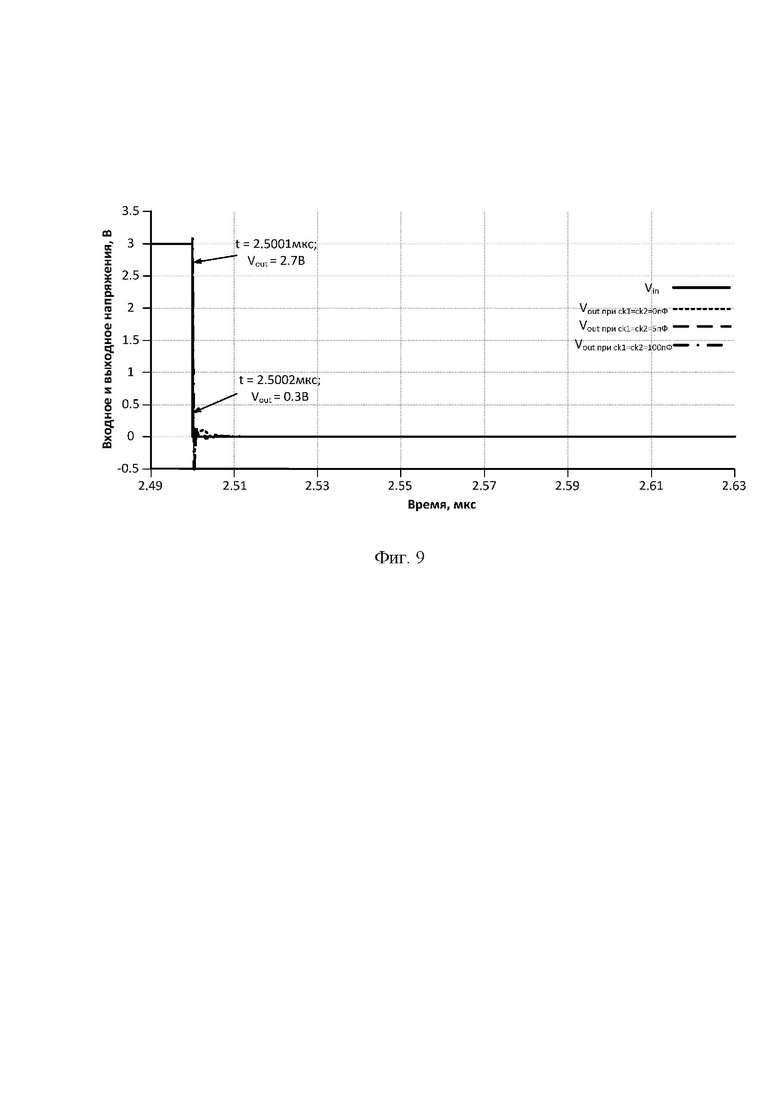

На чертеже фиг. 9 показан задний фронт переходного процесса в ОУ фиг. 6.

Входной каскад быстродействующего дифференциального операционного усилителя с нелинейной коррекцией переходного процесса фиг. 2 содержит первый 1 вход устройства, соединенный с базами первого 2 и второго 3 входных транзисторов, второй 4 вход устройства, соединенный с базами третьего 5 и четвертого 6 входных транзисторов, источник опорного тока 7, включённый между объединенными эмиттерами первого 2 и третьего 5 входных транзисторов и первой 8 шиной источника питания, первый 9 и второй 10 токовые выходы устройства, согласованные со второй 11 шиной источника питания, первый 12 выходной транзистор, коллектор которого соединен с первым 9 токовым выходом устройства, второй 13 выходной транзистор, коллектор которого связан со вторым 10 токовым выходом устройства, первый 14 резистор цепи нелинейной коррекции, включенный между эмиттером второго 3 входного транзистора и эмиттером второго 13 выходного транзистора, который соединен с коллектором третьего 5 входного транзистора, второй 15 резистор цепи нелинейной коррекции, включенный между эмиттером четвертого 6 входного транзистора и эмиттером первого 12 выходного транзистора, который соединен с коллектором первого 2 входного транзистора, третий 16 токовый выход устройства, согласованный с первой 8 шиной источника питания, который подключен к коллектору второго 3 входного транзистор, четвертый 17 токовый выход устройства, согласованный с первой 8 шиной источника питания, который подключен к коллектору четвертого 6 входного транзистора. В схему введены первый 18 и второй 19 дополнительные транзисторы, коллекторы которых согласованы со второй 11 шиной источника питания, база первого 18 дополнительного транзистора соединена со входом 1 устройства, а эмиттер через первый 20 дополнительный источник опорного тока соединен с первой 8 шиной источника питания, база второго 19 дополнительного транзистора соединена со вторым 4 входом устройства, а эмиттер через второй 21 дополнительный источник опорного тока связан с первой 8 шиной источника питания, база первого 12 выходного транзистора соединена со второй 11 шиной источника питания через третий 22 дополнительный источник опорного тока и подключена к эмиттеру второго 3 входного транзистора через первую 23 цепь согласования потенциалов, база второго 13 выходного транзистора соединена со второй 11 шиной источника питания через четвертый 24 дополнительный источник опорного тока и подключена к эмиттеру четвертого 6 входного транзистора через вторую 25 цепь согласования потенциалов, причем между базой первого 12 выходного транзистора и эмиттером первого 18 дополнительного транзистора включен первый 26 дополнительный корректирующий конденсатор, а между базой второго 13 выходного транзистора и эмиттером второго 19 дополнительного транзистора включен второй 27 дополнительный корректирующий конденсатор.

На чертеже фиг. 4 показан первый пример применения заявляемого входного дифференциального каскада в схеме быстродействующего ОУ на основе трех токовых зеркал 28, 29, 30, буферном усилителе 31, потенциальный выход которого 34 является основным выходом ОУ. В данной схеме используется цепь симметрирования статического режима токовых зеркал 28, 29, выполненная на транзисторе 32, а устойчивость в ОУ обеспечивается интегрирующим корректирующим конденсатором 33.

На чертеже фиг. 5 представлен второй пример применения заявляемого входного каскада в схеме быстродействующего ОУ на основе трех токовых зеркал 35, 36, 37 и промежуточного «перегнутого» каскода на транзисторах 38, 39, токостаблизирующих резисторах 40, 41, источнике напряжения смещения 42 на базах транзисторов 38, 39, токовом зеркале 43, буферном усилителе 44, потенциальный выход 45 которого является основным выходом ОУ, а корректирующий конденсатор 46 обеспечивает устойчивость ОУ.

Рассмотрим работу предлагаемого входного каскада быстродействующего ОУ фиг. 2.

При большом импульсном сигнале на первом 1 входе входного дифференциального каскада (фиг. 2) его второй 3 входной транзистор практически мгновенно запирается, а паразитный конденсатор Ср2 в цепи базы первого 12 выходного транзистора заряжается током третьего 22 дополнительного источника опорного тока, к которому добавляется значительный импульсный ток icк1(+)>>I22 через первый 26 дополнительный корректирующий конденсатор:

Как следствие, потенциал на базе первого 12 выходного транзистора uA имеет «более крутой фронт», что приводит к быстрому изменению его тока эмиттера через второй 15 резистор цепи нелинейной коррекции и, как следствие, тока эмиттера четвертого 6 входного транзистора и выходного тока четвертого 17 токового выхода устройства. В результате формируется достаточно крутой фронт выходного тока iвых.1(+) в цепи первого 9 токового выхода, что способствует повышению быстродействию входного каскада по первому 9 токовому выходу и четвертому 17 токовому выходу. К данным токовым выходам могут подключаться токовые зеркала, обеспечивающие передачу сигналов в выходной высокоимпедансный узел ОУ (см. например, фиг. 5).

О высоком быстродействии предлагаемого входного каскада в структуре ОУ свидетельствуют графики переходных процессов на чертеже фиг. 8, из которых можно определить, что максимальная скорость нарастания выходного напряжения ОУ увеличивается за счет нового входного каскада до 2085 В/мкс. Это более чем в 5,7 раз превышает SR ОУ с классическим входным каскадом – прототипом.

Таким образом, предлагаемый входной дифференциальный каскад в структуре, например, операционного усилителя, обладает существенными преимуществами по динамическим параметрам в режиме большого сигнала.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 5.399.991, fig. 2, 1995 г.

2. Патентная заявка US 2005/0024149, fig. 4, 2005 г.

3. Патент US 6.492.870, fig. 2, 2002 г.

4. Патент US 6.278.326, fig.11, 2001 г.

5. Патент US 6.294.958, 2001 г.

6. Патентная заявка US 2004/0232968, fig. 12, 2004 г.

7. Патент US 6.429.744, 2002 г.

8. Патент US 5.510.754, fig. 2, 1996 г.

9. Патентная заявка US 2004/0212430, fig. 2, 2004 г.

10. Патентная заявка US 2002/0011875, fig. 1, 2002 г.

11. Патент US 6.542.032, fig.2, fig.3, 2003 г.

12. Патент US 5.150.074, fig. 1, 1992 г.

13. Патент US 5.374.897, fig. 4, 1994 г.

14. Патент US 5.512.859, fig. 4, 1996 г.

15. Патент US 6.459.338, fig. 2, 2002 г.

16. Патент US 6.262.633, fig. 2a, 2001 г.

17. Патентная заявка US 2005/0128000, fig. 2, 2005 г.

18. Патент US 6.710.655, fig. 3, 2004 г.

19. Патентная заявка US 2010/0225393, fig. 1B, 2010 г.

20. Операционные усилители с непосредственной связью каскадов : монография / Анисимов В.И., Капитонов М.В., Прокопенко Н.Н., Соколов Ю.М. - Л.: «Энергия», 1979. - 148 с.

21. Полонников Д.Е. Операционные усилители: Принципы построения, теория, схемотехника. – М.: Энергоатомиздат, 1983. – С. 117, рис. 3.28

22. Прокопенко Н.Н. Дифференциальный операционный усилитель с повышенным быстродействием // Приборы и техника эксперимента, № 2, 1978. – С. 153, рис. 1

| название | год | авторы | номер документа |

|---|---|---|---|

| КАСКОДНЫЙ ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ С НЕЛИНЕЙНОЙ КОРРЕКЦИЕЙ ПЕРЕХОДНОГО ПРОЦЕССА | 2023 |

|

RU2797566C1 |

| Быстродействующий операционный усилитель на основе комплементарных «перегнутых» каскодов | 2023 |

|

RU2813010C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ БУФЕРНЫЙ УСИЛИТЕЛЬ С НЕЛИНЕЙНОЙ КОРРЕКЦИЕЙ КЛАССА АВ | 2022 |

|

RU2790615C1 |

| Быстродействующий дифференциальный операционный усилитель | 2018 |

|

RU2688227C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ "НАПРЯЖЕНИЕ-ТОК" С ШИРОКИМ ДИАПАЗОНОМ ЛИНЕЙНОЙ РАБОТЫ | 2017 |

|

RU2658818C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ДИФФЕРЕНЦИРУЮЩИМИ ЦЕПЯМИ КОРРЕКЦИИ В МОСТОВОМ ВХОДНОМ ДИФФЕРЕНЦИАЛЬНОМ КАСКАДЕ | 2023 |

|

RU2797168C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2016 |

|

RU2640744C1 |

| Многоканальный быстродействующий операционный усилитель | 2018 |

|

RU2683851C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ДИФФЕРЕНЦИРУЮЩИМИ ЦЕПЯМИ КОРРЕКЦИИ | 2018 |

|

RU2684500C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДВУХТАКТНЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2022 |

|

RU2784047C1 |

Изобретение относится к области радиотехники и микроэлектроники и может быть использовано в различных устройствах для обработки сигналов датчиков. Технический результат: повышение предельных значений максимальной скорости нарастания выходного напряжения в операционном усилителе (ОУ) с предлагаемым входным каскадом как для положительной, так и для отрицательной полярностей входного импульсного сигнала без ухудшения энергетических параметров ОУ в статическом режиме. Указанный результат достигается тем, что во входной каскад быстродействующего дифференциального операционного усилителя введены два дополнительных транзистора, коллекторы которых согласованы со второй шиной источника питания, базы - со входами устройства, а эмиттеры через дополнительные источники опорного тока соединены с первой шиной источника питания. Базы первого и второго выходных транзисторов соединены со второй шиной источника питания через дополнительные источники опорного тока, подключены соответственно к эмиттерам второго и третьего входных транзисторов через цепи согласования потенциалов, а также соединены соответственно с эмиттерами первого и второго дополнительных транзисторов через корректирующие конденсаторы. 9 ил.

Входной каскад быстродействующего дифференциального операционного усилителя с нелинейной коррекцией переходного процесса, содержащий первый (1) вход устройства, соединенный с базами первого (2) и второго (3) входных транзисторов, второй (4) вход устройства, соединенный с базами третьего (5) и четвертого (6) входных транзисторов, источник опорного тока (7), включённый между объединенными эмиттерами первого (2) и третьего (5) входных транзисторов и первой (8) шиной источника питания, первый (9) и второй (10) токовые выходы устройства, согласованные со второй (11) шиной источника питания, первый (12) выходной транзистор, коллектор которого соединен с первым (9) токовым выходом устройства, второй (13) выходной транзистор, коллектор которого связан со вторым (10) токовым выходом устройства, первый (14) резистор цепи нелинейной коррекции, включенный между эмиттером второго (3) входного транзистора и эмиттером второго (13) выходного транзистора, который соединен с коллектором третьего (5) входного транзистора, второй (15) резистор цепи нелинейной коррекции, включенный между эмиттером четвертого (6) входного транзистора и эмиттером первого (12) выходного транзистора, который соединен с коллектором первого (2) входного транзистора, третий (16) токовый выход устройства, согласованный с первой (8) шиной источника питания, который подключен к коллектору второго (3) входного транзистора, четвертый (17) токовый выход устройства, согласованный с первой (8) шиной источника питания, который подключен к коллектору четвертого (6) входного транзистора, отличающийся тем, что в схему введены первый (18) и второй (19) дополнительные транзисторы, коллекторы которых согласованы со второй (11) шиной источника питания, база первого (18) дополнительного транзистора соединена со входом (1) устройства, а эмиттер через первый (20) дополнительный источник опорного тока соединен с первой (8) шиной источника питания, база второго (19) дополнительного транзистора соединена со вторым (4) входом устройства, а эмиттер через второй (21) дополнительный источник опорного тока связан с первой (8) шиной источника питания, база первого (12) выходного транзистора соединена со второй (11) шиной источника питания через третий (22) дополнительный источник опорного тока и подключена к эмиттеру второго (3) входного транзистора через первую (23) цепь согласования потенциалов, база второго (13) выходного транзистора соединена со второй (11) шиной источника питания через четвертый (24) дополнительный источник опорного тока и подключена к эмиттеру четвертого (6) входного транзистора через вторую (25) цепь согласования потенциалов, причем между базой первого (12) выходного транзистора и эмиттером первого (18) дополнительного транзистора включен первый (26) дополнительный корректирующий конденсатор, а между базой второго (13) выходного транзистора и эмиттером второго (19) дополнительного транзистора включен второй (27) дополнительный корректирующий конденсатор.

| Н.Н | |||

| Прокопенко, А.С | |||

| Будяков "Архитектура и схемотехника быстродействующих операционных усилителей", Шахты, "ЮРГУЭС", 2006, стр.231 | |||

| Дифференциальный усилитель на комплементарных полевых транзисторах с управляемым напряжением ограничения проходной характеристики | 2018 |

|

RU2679970C1 |

| МОСТОВОЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2005 |

|

RU2277753C1 |

| US 7358807 B2, 15.04.2008 | |||

| US 10355655 B2, 16.07.2019. | |||

Авторы

Даты

2023-05-31—Публикация

2023-02-22—Подача