(риг 1

вычисления кодов. Быстродействие повышается за счет анализа совокупности импульсных последовательностей и определения группы кодов, внутри которой расположен код, соответствующий входному сигналу. Это позволяет сократить число кодов, определяемых непосредственно при анализе

импульсных последовательностей, в результате чегд сокращаются время преобразования и объем постоянной памя-, ти, в котором размещаются информация о положении импульсов и сами коды. Точные значения кодов определяются в блоке 14 вычисления кодов. 5 з.п. ф-лы, 11 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1990 |

|

SU1839258A1 |

| Устройство для контроля хода программы | 1988 |

|

SU1663612A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для контроля цифровых интегральных микросхем | 1987 |

|

SU1501062A2 |

| Устройство для тестового контроля цифровых узлов | 1987 |

|

SU1425682A1 |

| Устройство для контроля цифровых интегральных микросхем | 1986 |

|

SU1354142A1 |

| Устройство для формирования изображения на экране телевизионного приемника | 1987 |

|

SU1474727A1 |

| Устройство для формирования изображения на экране телевизионного приемника | 1985 |

|

SU1288751A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1681297A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

Изобретение относится к информационно-измерительной технике и может быть использовано в системах сбора данных для контроля параметров образцовых источников. Изобретение позволяет повысить быстродействие. Это достигается путем введения преобразователей 3, 4, 5 напряжения в частоту, включенных параллельно с основными со сдвигом шкалы на несколько квантов амплитуды, и блока 14 вычисления кодов. Быстродействие повышается за счет анализа совокупности импульсных последовательностей и определения группы кодов, внутри которой расположен код, соответствующий входному сигналу. Это позволяет сократить число кодов, определяемых непосредственно при анализе импульсных последовательностей, в результате чего сокращается время преобразования и объем постоянной памяти, в котором размещается информация о положении импульсов и сами коды. Точные значения кодов определяются в блоке 14 вычисления кодов. 5 з.п. ф-лы, 11 ил.

Изобретение относится к информационно-измерительной технике и пред- назначено для использования в системах сбора и обработки информации различного назначения в системах автоматического управления и регулирования .

Целью изобретения является повышение быстродействия.

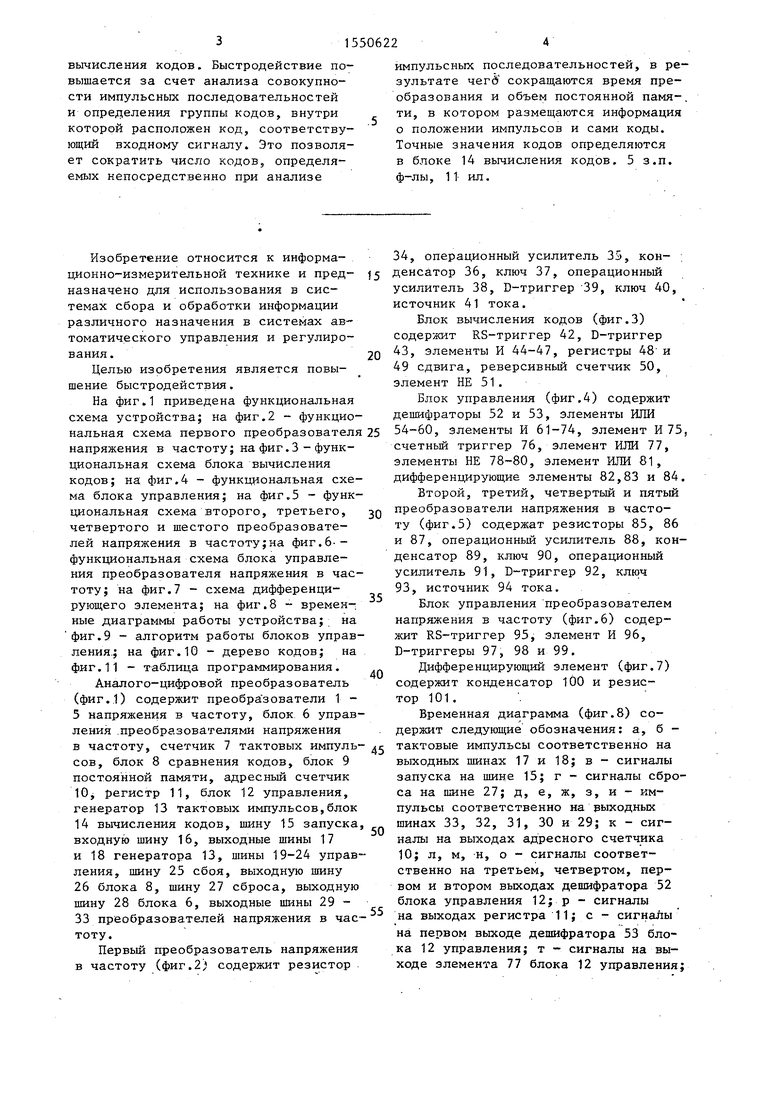

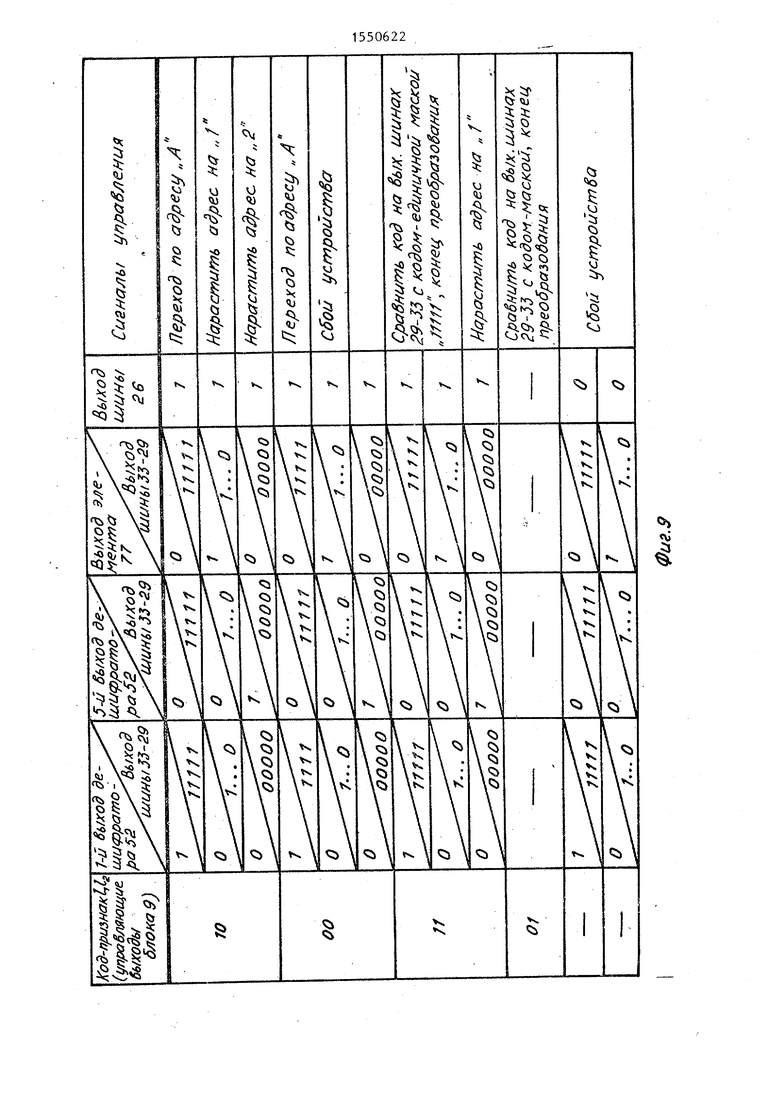

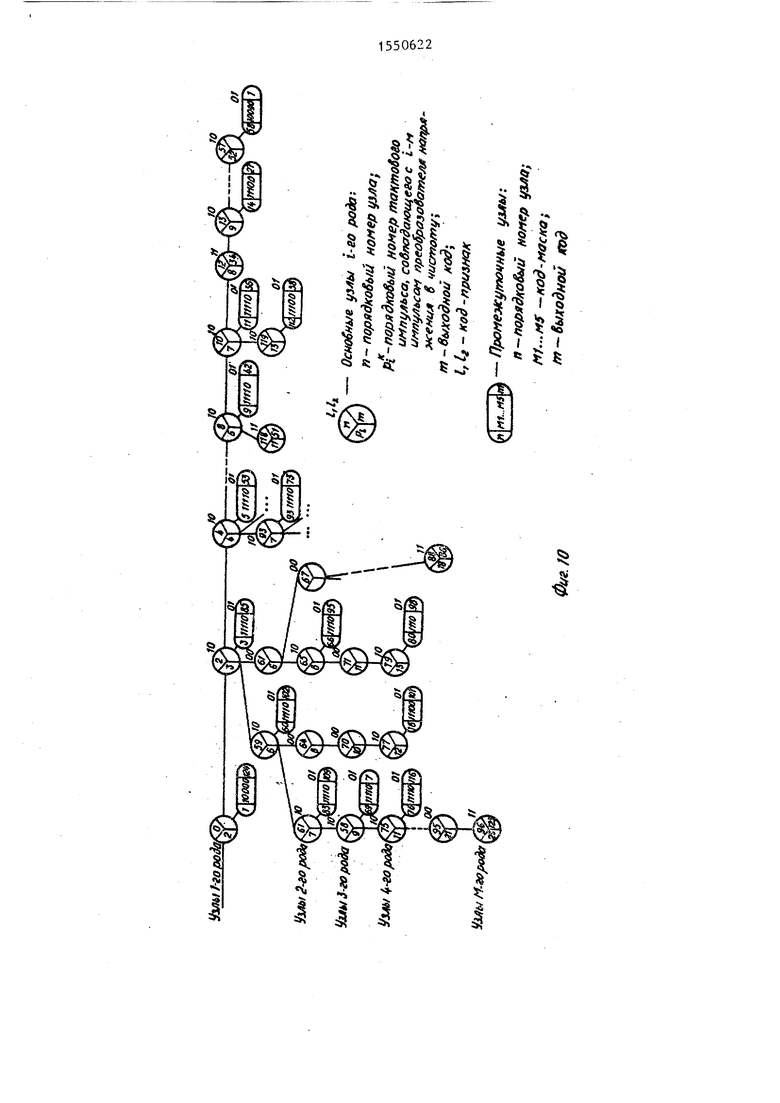

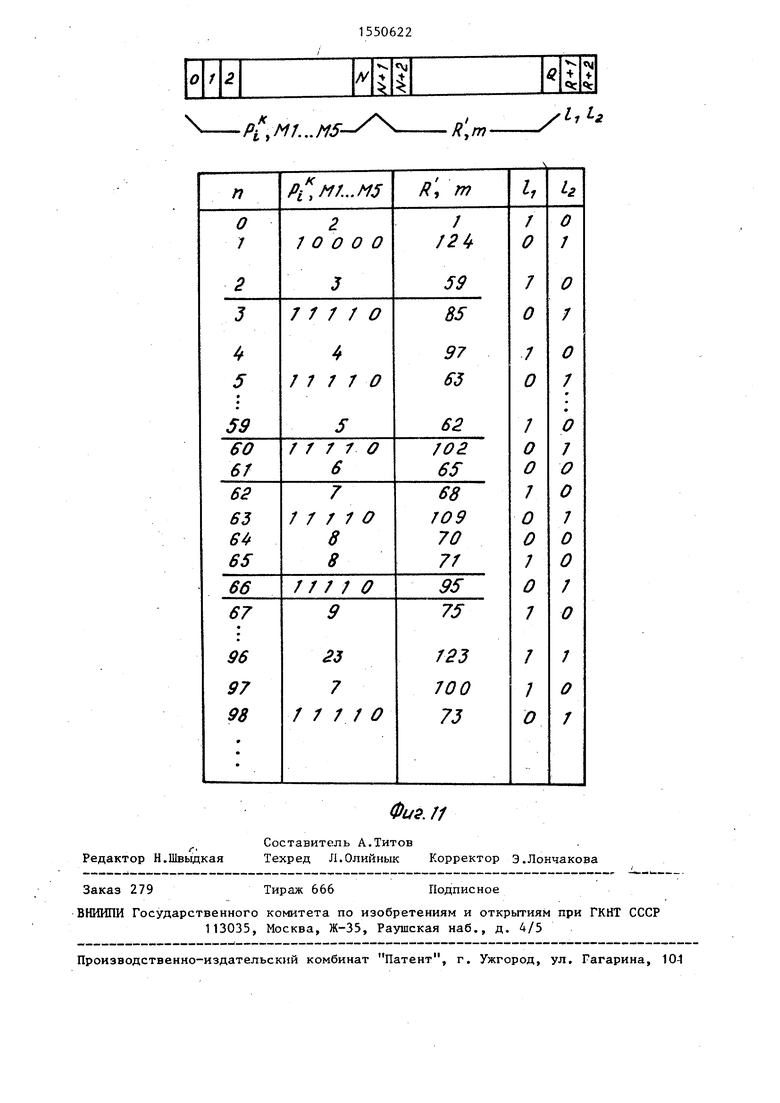

На фиг.1 приведена функциональная схема устройства; на фиг.2 - функциональная схема первого преобразователя напряжения в частоту; на фиг.3 - функциональная схема блока вычисления кодов; на фиг.4 - функциональная схема блока управления; на фиг.5 - функциональная схема второго, третьего, четвертого и шестого преобразователей напряжения в частоту;на фиг.6-- функциональная схема блока управления преобразователя напряжения в частоту ; на фиг.7 - схема дифференцирующего элемента; на фиг.8 - временные диаграммы работы устройства; на фиг.9 - алгоритм работы блоков управления; на фиг.10 - дерево кодов; на фиг.11 - таблица программирования.

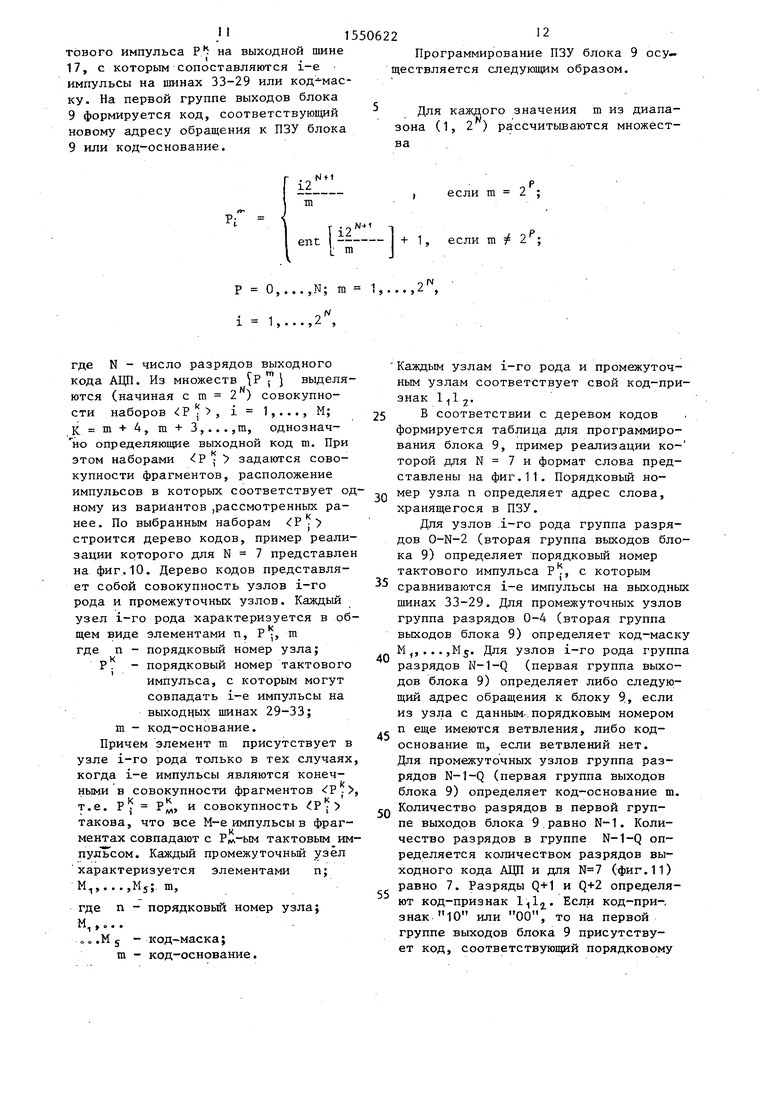

Аналого-цифровой преобразователь (фиг.1) содержит преобра зователи 1 - 5 напряжения в частоту, блок 6 управления преобразователями напряжения в частоту, счетчик 7 тактовых импуль- сов, блок 8 сравнения кодов, блок 9 постоянной памяти, адресный счетчик 10, регистр 11, блок 12 управления, генератор 13 тактовых импульсов,блок 14 вычисления кодов, шину 15 запуска, входную шину 16, выходные шины 17 и 18 генератора 13, шины 19-24 управ ления, шину 25 сбоя, выходную шину 26 блока 8, шину 27 сброса, выходную шину 28 блока 6, выходные шины 29 - 33 преобразователей напряжения в частоту.

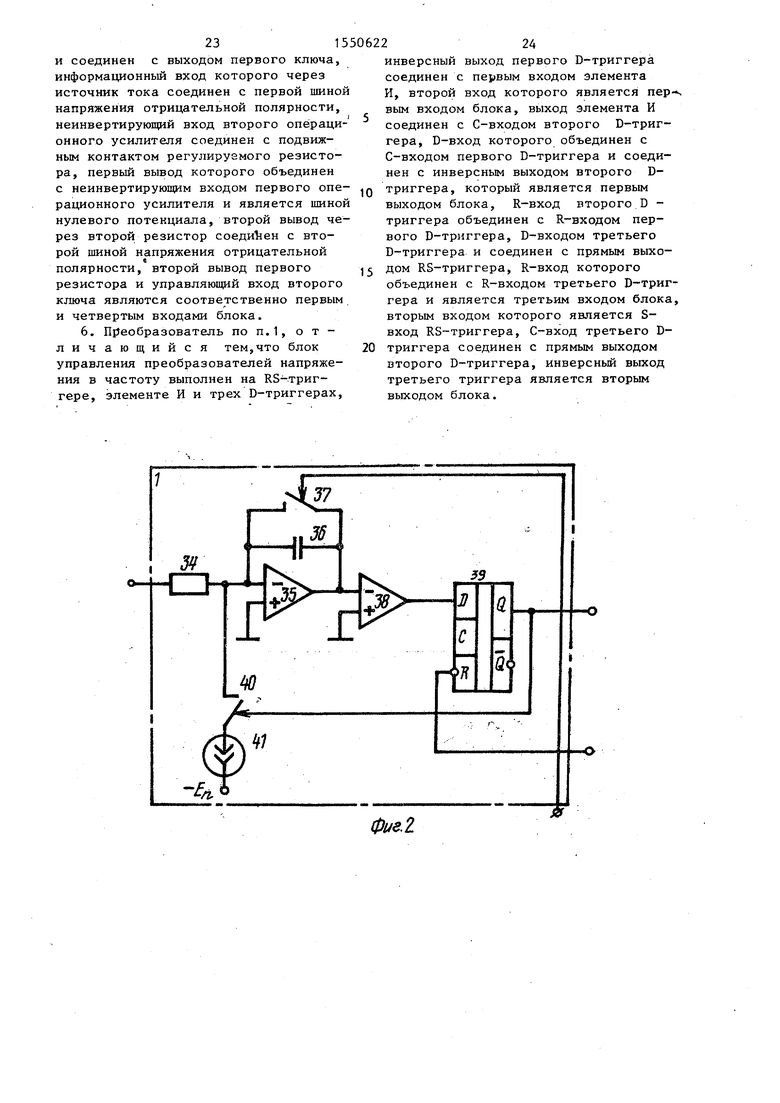

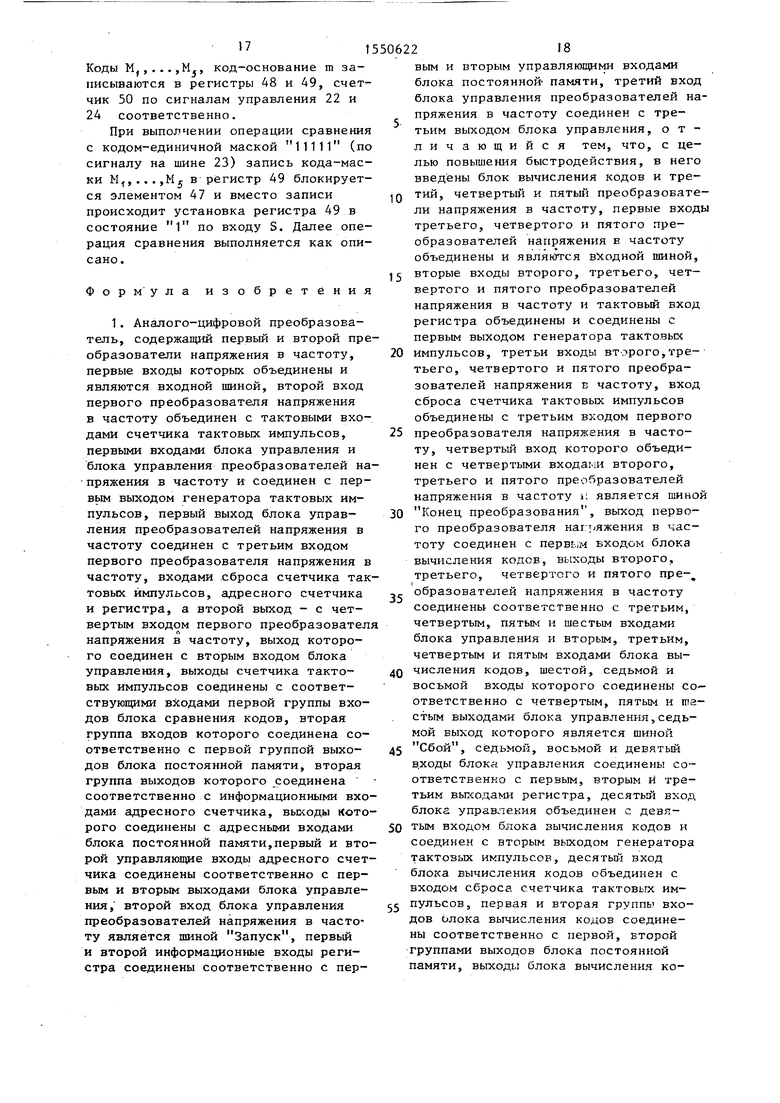

Первый преобразователь напряжения в частоту (фиг.2.) содержит резистор

5

5 0

5 о

0

50

5

34, операционный усилитель 35, конденсатор 36, ключ 37, операционный усилитель 38, D-триггер 39, ключ 40, источник 41 тока.

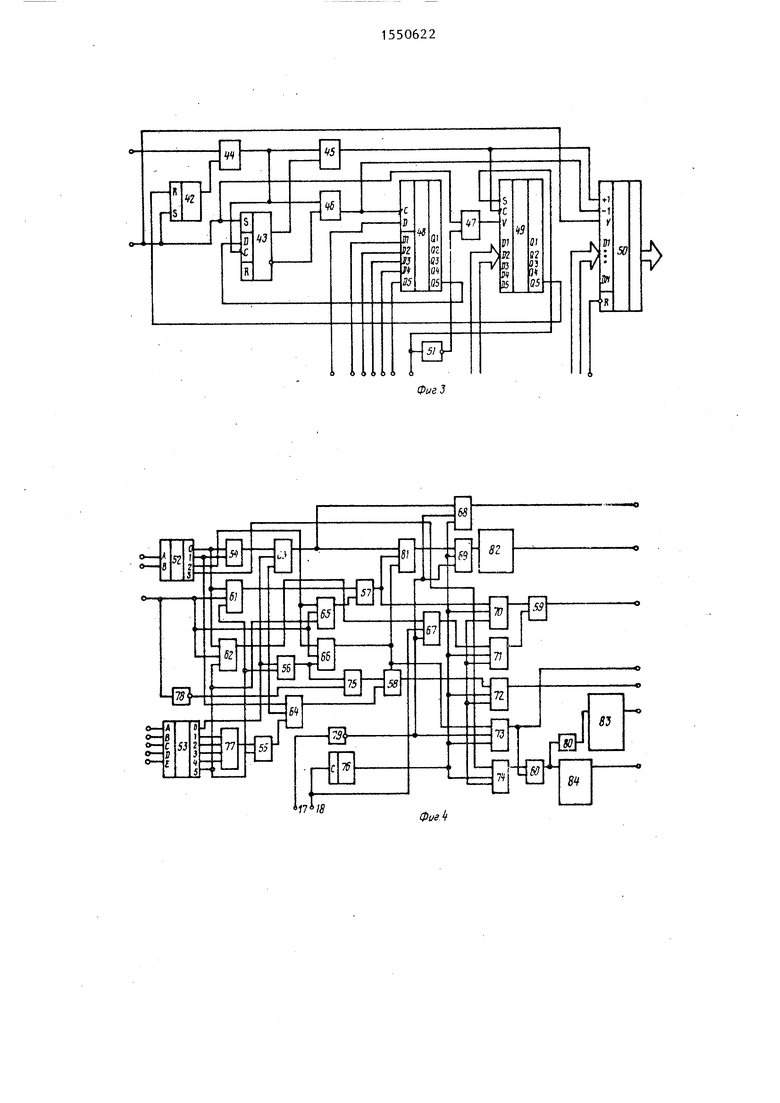

Блок вычисления кодов (фиг.З) содержит RS-триггер 42, D-триггер 43, элементы И 44-47, регистры 48 и 49 сдвига, реверсивный счетчик 50, элемент НЕ 51.

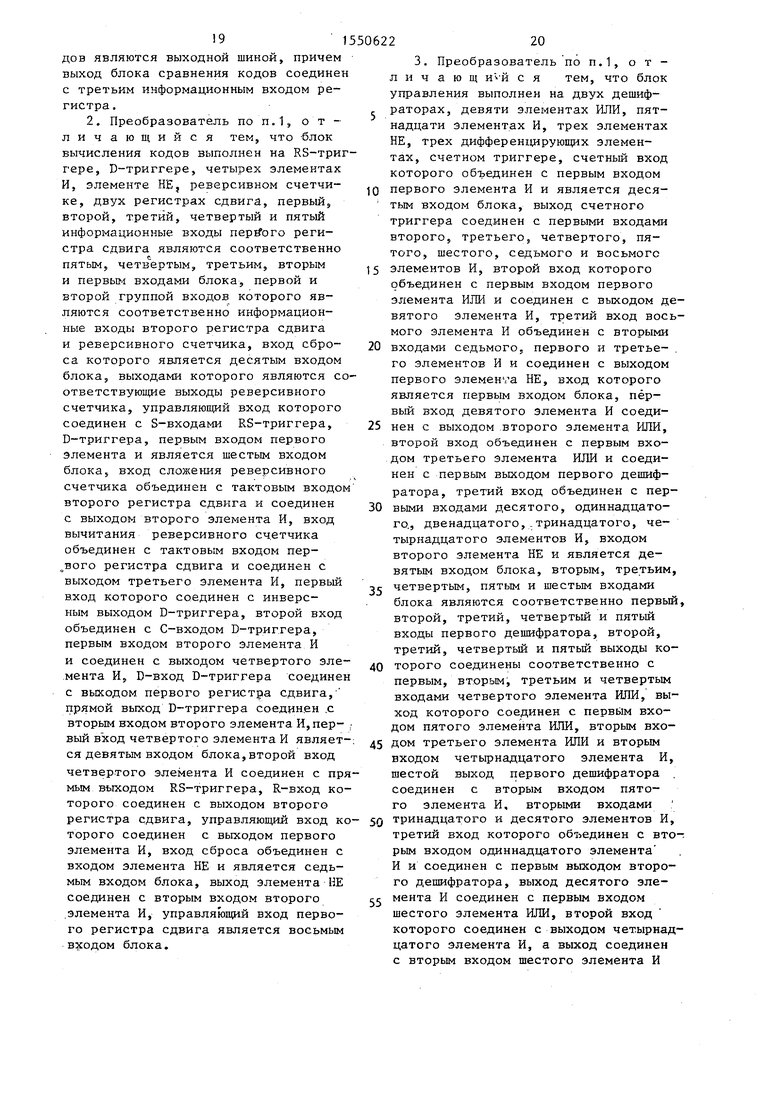

Блок управления (фиг.4) содержит дешифраторы 52 и 53, элементы ИЛИ 54-60, элементы И 61-74, элемент И 75, счетный триггер 76, элемент ИЛИ 77, элементы НЕ 78-80, элемент ИЛИ 81, дифференцирующие элементы 82,83 и 84.

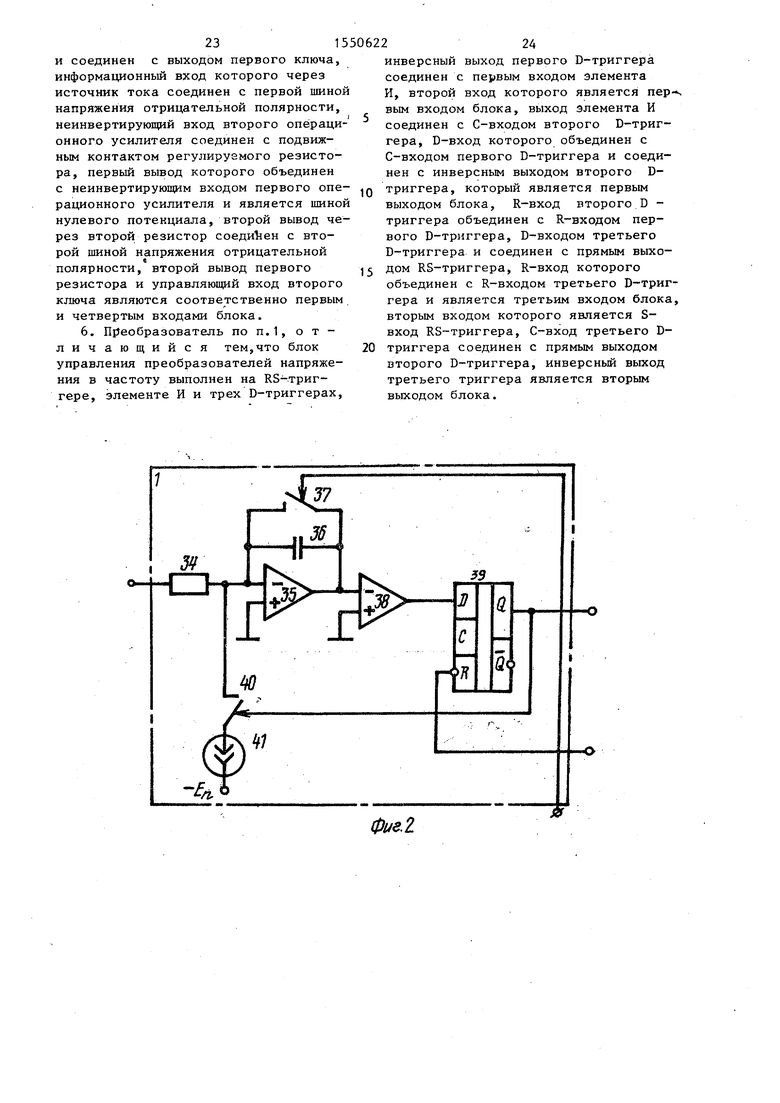

Второй, третий, четвертый и пятый преобразователи напряжения в частоту (фиг.5) содержат резисторы 85, 86 и 87, операционный усилитель 88, конденсатор 89, ключ 90, операционный усилитель 91, D-триггер 92, ключ 93, источник 94 тока.

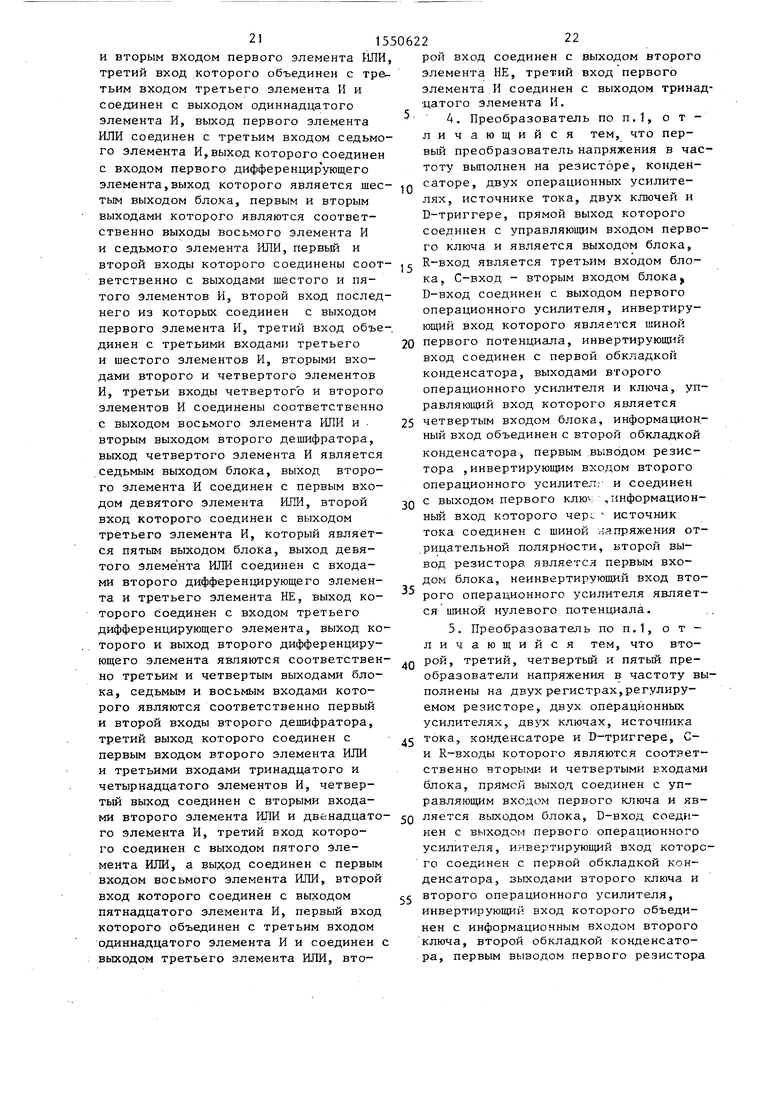

Блок управления преобразователем напряжения в частоту (фиг.6) содержит RS-триггер 95, элемент И 96, D-триггеры 97, 98 и 99.

Дифференцирующий элемент (фиг.7) содержит конденсатор 100 и резистор 101.

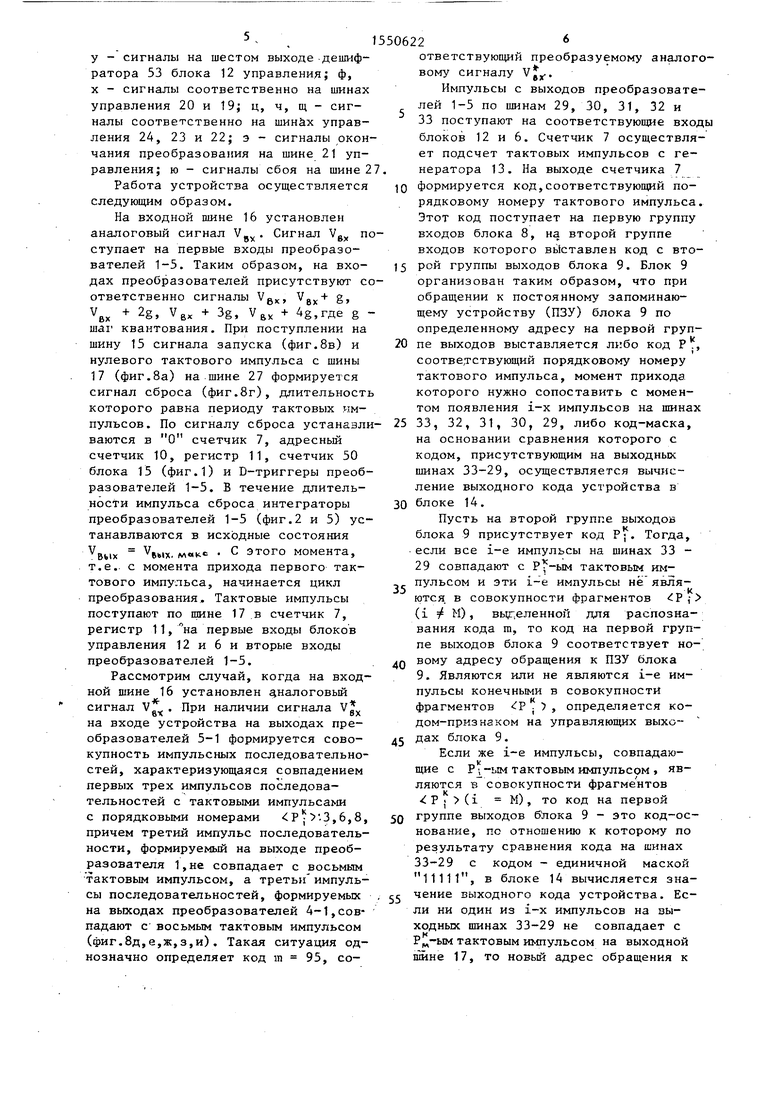

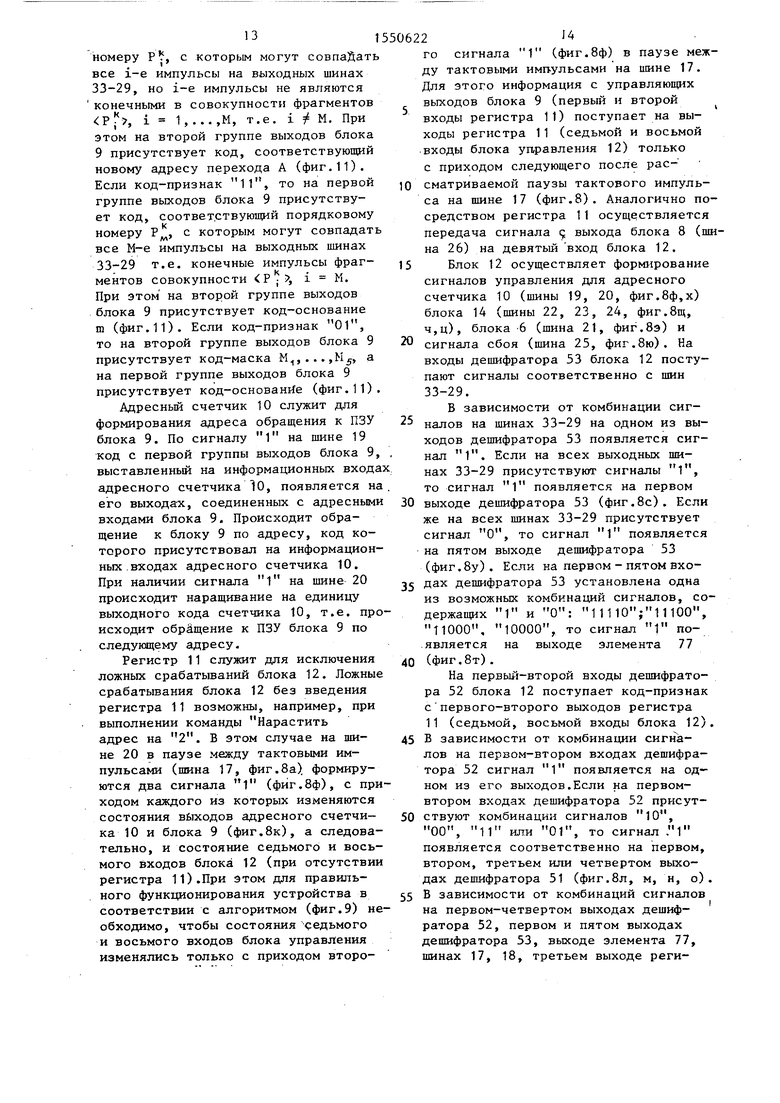

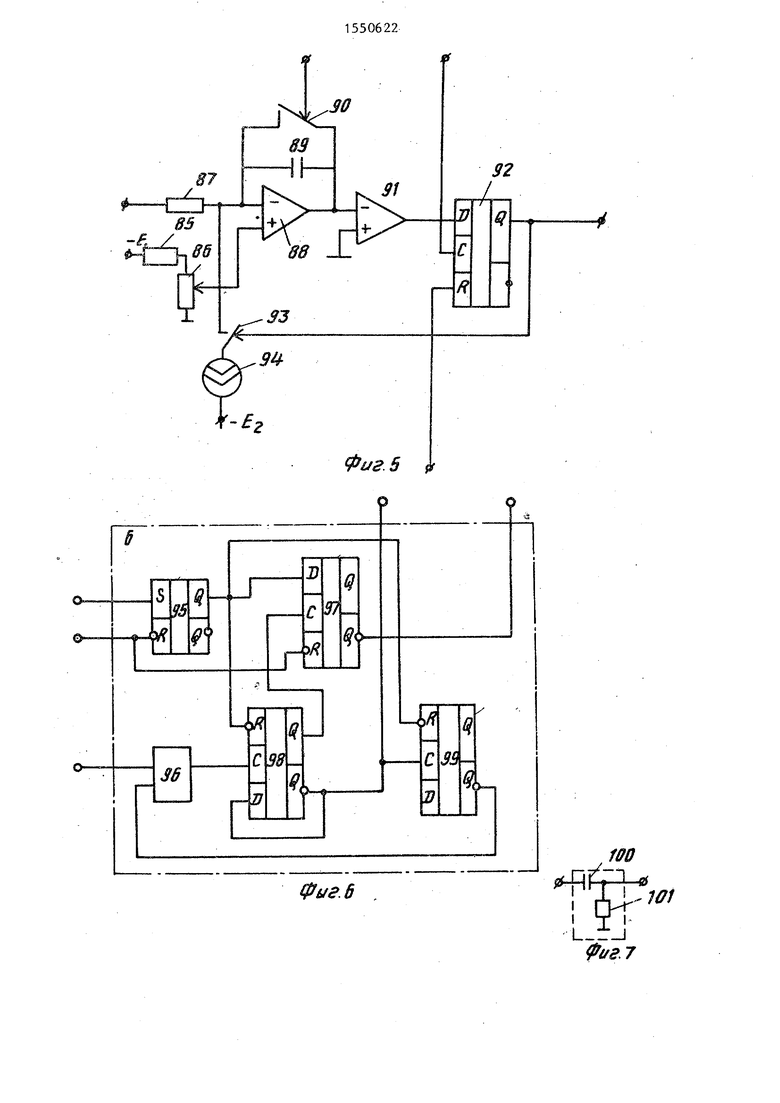

Временная диаграмма (фиг.8) содержит следующие обозначения: а, б - тактовые импульсы соответственно на выходных шинах 17 и 18; в - сигналы запуска на шине 15; г - сигналы сброса на шине 27; д, е, ж, з, и - импульсы соответственно на выходных шинах 33, 32, 31, 30 и 29; к - сигналы на выходах адресного счетчика 10; л, м, н, о - сигналы соответственно на третьем, четвертом, первом и втором выходах дешифратора 52 блока управления 12; р - сигналы на выходах регистра 11; с - сигналы на первом выходе дешифратора 53 блока 12 управления; т - сигналы на выходе элемента 77 блока 12 управления;

у - сигналы на шестом выходе дешифратора 53 блока 12 управления; ф, х - сигналы соответственно на шинах управления 20 и 19; ц, ч, щ - сигналы соответственно на шинах управления 24, 23 и 22; э - сигналы окончания преобразования на шине 21 управления; ю - сигналы сбоя на шине 2

Работа устройства осуществляется следующим образом.

На входной шине 16 установлен аналоговый сигнал VBX. Сигнал Vex поступает на первые входы преобразователей 1-5. Таким образом, на входах преобразователей присутствуют соответственно сигналы Vi V. + 2g, V6X + 3g, V

V8X +

6x y ex 6

Bx-o ex T J& v &X + 4g,Tfle g шаг квантования. При поступлении на шину 15 сигнала запуска (фиг.8в) и нулевого тактового импульса с шины 17 (фиг.8а) на шине 27 формируется сигнал сброса (фиг.вг), длительность которого равна периоду тактовых им-

пульсов. По сигналу сброса устаназли- 25 33, 32, 31, 30, 29, либо код-маска,

на основании сравнения которого с кодом, присутствующим на выходных шинах 33-29, осуществляется вычисление выходного кода устройства в 30 блоке 14.

п счетчик 7, адресный регистр 11, счетчик 50

ваются в О счетчик 10,

блока 15 (фиг.1) и D-триггеры преобразователей 1-5. В течение длительности импульса сброса интеграторы преобразователей 1-5 (фиг.2 и 5) ус- танавлваются в исходные состояния

VBt.ix . м«к с этого момента, т.е. с момента прихода первого тактового импульса, начинается цикл преобразования. Тактовые импульсы поступают по шине 17 в счетчик 7, регистр 11, на первые входы блоков управления 12 и 6 и вторые входы преобразователей 1-5.

Рассмотрим случай, когда на входной шине 16 установлен диалоговый

40

сигнал VT- . При наличии сигнала V

6Х . при наличии сигнала v gx на входе устройства на выходах преобразователей 5-1 формируется совокупность импульсных последовательностей, характеризующаяся совпадением первых трех импульсов последовательностей с тактовыми импульсами с порядковыми номерами .3,6,8, причем третий импульс последовательности, формируемый на выходе преобразователя 1,не совпадает с восьмым тактовым импульсом, а третьи импульсы последовательностей, формируемых на выходах преобразователей 4- совпадают с восьмым тактовым импульсом (фиг.8д,е,ж,з,и). Такая ситуация однозначно определяет код m 95, соПусть на второй группе выходов блока 9 присутствует код Р. Тогда, если все 1-е импульсы на шинах 33 - 29 совпадают с тактовым импульсом и эти i-e импульсы не являются в совокупности фрагментов Р,- (i М), выделенной для распознавания кода т, то код на первой группе выходов блока 9 соответствует новому адресу обращения к ПЗУ блока 9. Являются или не являются 1-е импульсы конечными в совокупности фрагментов Р ) , определяется кодом-признаком на управляющих выходу дах блока 9.

Если же 1-е импульсы, совпадающие с тактовым импульсом , являются в совокупности фрагментов Р; (i М), то код на первой 50 группе выходов блока 9 - это код-основание, по отношению к которому по результату сравнения кода на шинах 33-29 с кодом - единичной маской 11111, в блоке 14 вычисляется значение выходного кода устройства. Если ни один из 1-х импульсов на выходных шинах 33-29 не совпадает с Рм-ым тактовым импульсом на выходной шине 17, то новый адрес обращения к

55

ответствующий преобразуемому аналоговому сигналу Vj,,..

Импульсы с выходов преобразователей 1-5 по шинам 29, 30, 31, 32 и 33 поступают на соответствующие входы блоков 12 и 6. Счетчик 7 осуществляет подсчет тактовых импульсов с генератора 13. На выходе счетчика 7

0 формируется код,соответствующий порядковому номеру тактового импульса. Этот код поступает на первую группу входов блока 8, на второй группе входов которого выставлен код с вто5 РОЙ группы выходов блока 9. Блок 9 организован таким образом, что при обращении к постоянному запоминающему устройству (ПЗУ) блока 9 по определенному адресу на первой груп0 пе выходов выставляется либо код Рк, соответствующий порядковому номеру тактового импульса, момент прихода которого нужно сопоставить с моментом появления 1-х импульсов на шинах

0

Пусть на второй группе выходов блока 9 присутствует код Р. Тогда, если все 1-е импульсы на шинах 33 - 29 совпадают с тактовым импульсом и эти i-e импульсы не являются в совокупности фрагментов Р,- (i М), выделенной для распознавания кода т, то код на первой группе выходов блока 9 соответствует новому адресу обращения к ПЗУ блока 9. Являются или не являются 1-е импульсы конечными в совокупности фрагментов Р ) , определяется кодом-признаком на управляющих выхоу дах блока 9.

Если же 1-е импульсы, совпадающие с тактовым импульсом , являются в совокупности фрагментов Р; (i М), то код на первой 0 группе выходов блока 9 - это код-основание, по отношению к которому по результату сравнения кода на шинах 33-29 с кодом - единичной маской 11111, в блоке 14 вычисляется значение выходного кода устройства. Если ни один из 1-х импульсов на выходных шинах 33-29 не совпадает с Рм-ым тактовым импульсом на выходной шине 17, то новый адрес обращения к

5

блоку 9 должен быть сформирован прибавлением 2 к предыдущему. Если хотя бы один из 1-х импульсов на шинах 33-29 совпадает с тактовым импульсом (за исключением случая, когда все 1-е импульсы синхронизированы с Р- тактовым импульсом, описанным ранее), то новый адрес обращения к блоку 9 должен быть сформирован прибавлением 1 к предыдущему. Если значение кода т распознается по совокупности фрагментов Р 1, ...,МгК т + 4, m + 3 , m + 2, m + + 1, га и коду-маске 11110, то при изменении входного сигнала от значения, соответствующего коду m до значения, соответствующего коду т+1, возможно смещение импульса фрагмента Р 7, такое, что все М-е импульсы на шинах 33-29 совпадут с Рк-ым тактовым импульсом.При этом на шинах 29-33 присутствует код 11111 В этом случае осуществляется переход по новому адресу, в качестве которого используется код, установленный на второй группе выходов блока 9 Но этот новый адрес всегда равен текущий адрес + 1. При обращении к блоку 9 по адресу текущий + 1 на второй группе выходов блока 9 присутствует уже не код, соответствующий

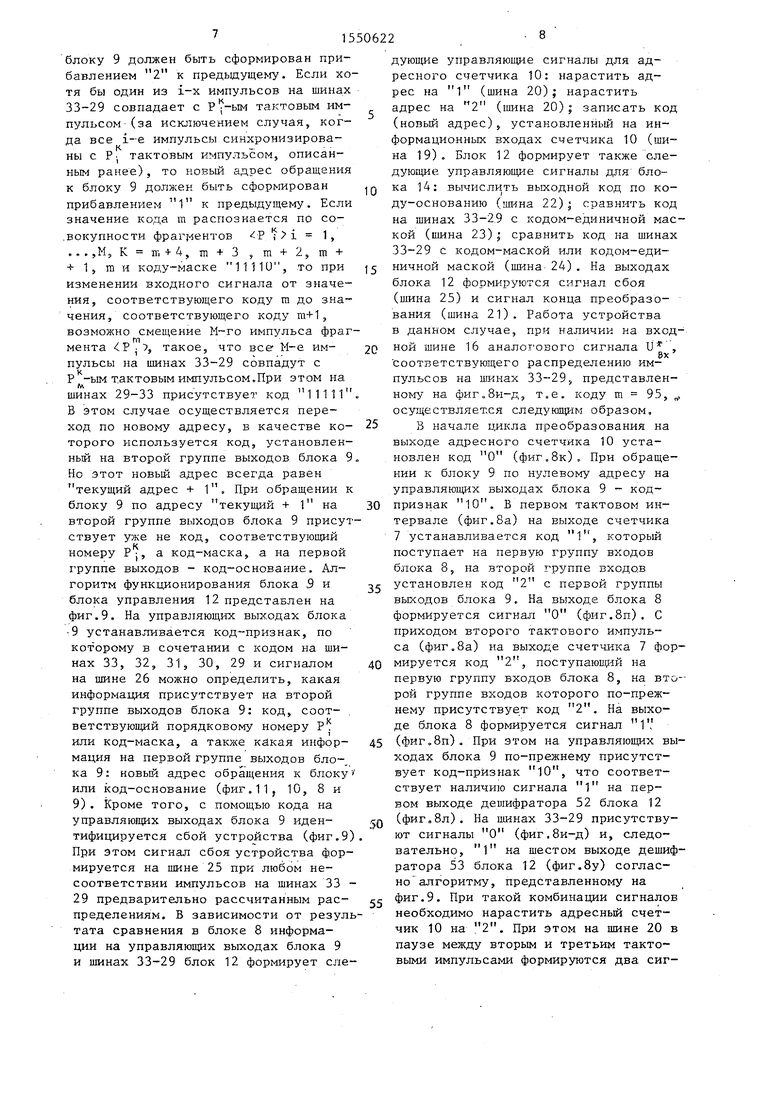

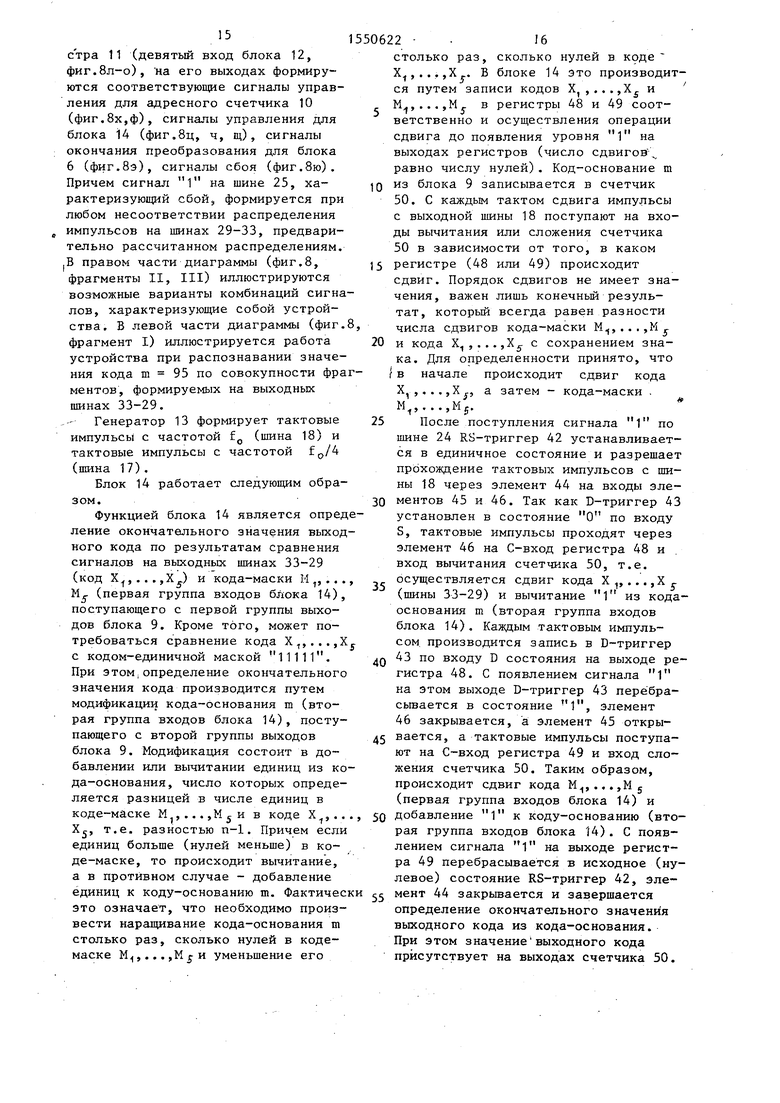

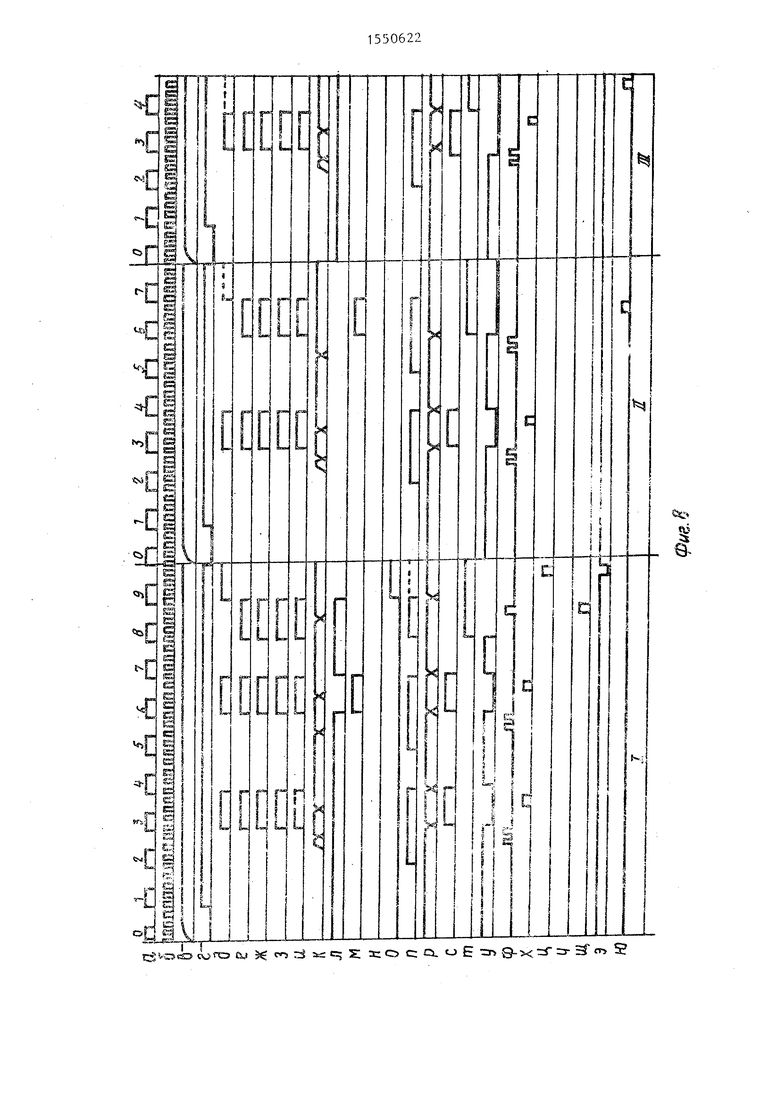

номеру Р, а код-маска, а на первой группе выходов - код-основание. Алгоритм функционирования блока Э и блока управления 12 представлен на фиг.9. На управляющих выходах блока -9 устанавливается код-признак, по которому в сочетании с кодом на шинах 33, 32, 31, 30, 29 и сигналом на шине 26 можно определить, какая информация присутствует на второй группе выходов блока 9: код, соответствующий порядковому номеру Р1 или код-маска, а также какая информация на первой группе выходов блока 9: новый адрес обращения к блоку или код-основание (фиг.11, 10, 8 и 9). Кроме того, с помощью кода на управляющих выходах блока 9 идентифицируется сбой устройства (фиг.9) При этом сигнал сбоя устройства формируется на шине 25 при любом несоответствии импульсов на шинах 33 - 29 предварительно рассчитанным распределениям. В зависимости от результата сравнения в блоке 8 информации на управляющих выходах блока 9 и шинах 33-29 блок 12 формирует сле

5

0

5

0

5

0

5

0

5

дующие управляющие сигналы для адресного счетчика 10: нарастить адрес на 1 (шина 20); нарастить адрес на Н2 (шина 20); записать код (новый адрес), установленный на информационных входах счетчика 10 (шина 19). Блок 12 формирует также следующие управляющие сигналы для блока 14: вычислить выходной код по коду-основанию (шина 22)| сравнить код на шинах 33-29 с кодом-единичной маской (шина 23)j сравнить код на шинах 33-29 с кодом-маской или кодом-единичной маской (шина 24). На выходах блока 12 формируются сигнал сбоя (шина 25) и сигнал конца преобразования (шина 21). Работа устройства в данном случае, при наличии на входной шине 16 аналогового сигнала U ,

Вх

соответствующего распределению импульсов на шинах 33-29, представленному на фиг.8и-д, т.е. коду m 95, „ осуществляется следующим образом,

Н начале цикла преобразования на выходе адресного счетчика 10 установлен код О (фиг.8к). При обращении к блоку 9 по нулевому адресу на управляющих выходах блока 9 - код- признак 10. В первом тактовом интервале (фиг.ба) на выходе счетчика 7 устанавливается код 1, который поступает на первую группу входов блока 8, на второй группе входов установлен код 2 с первой группы выходов блока 9 На выходе блока 8 формируется сигнал О (фиг.вп). С приходом второго тактового импульса (фиг„8а) на выходе счетчика 7 формируется код 2, поступающий на первую группу входов блока 8, на второй группе входов которого по-прежнему присутствует код 2. На выходе блока 8 формируется сигнал 1V (фиг.8п). При этом на управляющих выходах блока 9 по-прежнему присутствует код-признак 10, что соответствует наличию сигнала 1 на первом выходе дешифратора 52 блока 12 (фиг.8л). На шинах 33-29 присутствуют сигналы О (фиг.8и-д) и, следовательно, 1 на шестом выходе дешифратора 53 блока 12 (фиг.8у) согласно алгоритму, представленному на фиг.9. При такой комбинации сигналов необходимо нарастить адресный счетчик 10 на 2. При этом на шине 20 в паузе между вторым и третьим тактовыми импульсами формируются два сигнала 1, длительность которых равна длительности тактовых импульсов н 18 (фиг.8б,ф). По сигналам Г1 на шине 20 меняются состояния выходов адресного счетчика 10 (фиг.8к) и происходит обращение к ПЗУ блока 9 по адресу текущий + 2. При этом на второй группе выходов блока 9 присутствует код 59, на первой группе выходов - код 3, на управляющих выходах - код-признак 10 (фиг.8л). С приходом третьего тактового импульса (фиг.8а) сигнал 1, установившийся на выходе блока 8, и сигналы на управляющих выходах блока 9 поступают на выходы регистра 11 (фиг.8р) и соответствующие входы блока 12. При этом в третьем тактовом интервале на всех шинах 33-29 присутствуют сигналы 1 (фиг.8и-д), а следовательно, сигнал 1 присутствует на первом выходе дешифратора 53 блока 12 (фиг.8с) согласно алгоритму, представленному на фиг.9. При такой комбинации сигналов необходимо осуществить переход по адресу, код которого присутствует на первой группе выходов блока 9, т.е. по адресу 59.При этом на шине 19 в паузе между третьим и четвертым тактовыми импульсами на шине 17 (фиг.8а) формируется сигнал 1 (фиг.8х) длительностью в интервал между тактовыми импульсами на выходной шине 18 (фиг.86). С появлением сигнала 1 на шине 19 изменяются состояния выо

ходов адресного счетчика 10 (фиг.8к) код 59, установленный на информационных выходах адресного счетчика 9, поступает на его выходы, и осуществляется обращение к блоку 9 по адресу 59. В четвертом, пятом и т.д. тактовых интервалах (фиг.8а) устройство работает в соответствии временными диаграммами, представленными на фиг.8. На фиг.11 и 10 выделен рассматриваемый случай распознавания выходного кода 95. Согласно фиг.11 и 10 восьмой тактовый интервал является конечным при определении выходного кода 95. В восьмом тактовом интервале формируются сигналы 1 на шинах 20 и 22 (фиг.8ф,ш). По сигналу 1 на шине 22 Вычислить выходной код по коду-основанию осуществляется запись кода 11110 с шин 33-29 в регистр 48 блока 14. По сигналу 1 на шине 20 осуществляется обращение к блоку 9 до адресу текущий + 1. По этому адресу (для данного случая это адрес 66, см.

фиг.9, 10) на второй группе выходов установлен код-маска 11110, а на первой группе выходов - выходной код-основание 95, на управляющих выходах - код-признак 01. В следующем

тактовом интервале на шине 24 формируется сигнал 1 (фиг.8ц),по которому формируется блок 14 и осуществляется запись код а-маски в регистр

49блока 14. В блоке 14 осуществля- 5 ется вычисление выходного кода устройства по отношению к коду-основанию на основании сравнения кода-маски с кодом на шинах 33-29. В данном случае код-маска и код на шинах 33-

0 29 совпадает, из чего следует, что определяемый код равен коду-основанию 95. При этом сигнал окончания преобразования на шине 21 (фиг.8э) представляет собой инверсию сигна5 ла на шине 24. Сигнал О по шине 21 поступает в блок 6. На шине 28 появляется сигнал обнуления преобразователей 1-5. Поступление импульсов по шинам 33-29 прекращается,

0 а на выходах реверсивного счетчика

50блока 14 присутствует выходной код 95. С приходом нового импульса запуска процесс повторяется.

В рассмотренном случае выходной код был определен за 8 тактовых интервалов вместо 256, т.е. время преобразования сократилось в 32 раза. Счетчик 7 осуществляет счет тактовых импульсов с генератора 13. На выходе счетчика 7 формируется код, соответствующий порядковым номерам тактовых импульсов, поступающих по выходной шине 17.

Блок 8 осуществляет сравнение кодов порядковых номеров тактовых импульсов на Вогходе счетчика 7 и первой группе выходов блока 9. При равенстве кодов на обеих группах вхо-

дов блока 8 на его выходе формируется сигнал 1. Если же коды на обеих группах входов блока 8 не равны, то на выходе появляется сигнал О.

Блок 9 постоянной памяти осуществляет дешифрирование состояний адресного счетчика 10 и формирует на второй группе выходов код, соответствующий порядковому номеру так

тового импульса Р1 на выходной шине 17, с которым сопоставляются 1-е импульсы на шинах 33-29 или код-маску. На первой группе выходов блока 9 формируется код, соответствующий новому адресу обращения к ПЗУ блока 9 или код-основание.

izl l

m

р;

Г N4 1

ent + 1, если m j 2P;

I m J

P 0,...,N; m 1, . .. ,2 , i 1,...,2 ,

где N - число разрядов выходного кода АЦП. Из множеств Р выделяются (начиная с m 2 ) совокупности наборов Р j , i 1, . .. , M; К m + 4, m + 3,...,ra, однознач- но определяющие выходной код т. При этом наборами Р задаются совокупности фрагментов, расположение импульсов в которых соответствует одному из вариантов .рассмотренных ра Is

нее. По выбранным наборам Р j строится дерево кодов, пример реализации которого для N 7 представлен на фиг.10. Дерево кодов представляет собой совокупность узлов 1-го рода и промежуточных узлов. Каждый узел 1-го рода характеризуется в общем виде элементами n, Р , m где n - порядковый номер узла;

Рк - порядковый номер тактового импульса, с которым могут совпадать 1-е импульсы на выходных шинах 29-33; m - код-основание. Причем элемент m присутствует в узле 1-го рода только в тех случаях, когда 1-е импульсы являются конеч1/

ными в совокупности фрагментов Р . ,

Т a G

Р7

Рм, и совокупность Р ;

такова, что все М-е импульсы в фрагментах совпадают с тактовым им- пулТсом. Каждый промежуточньй узел характеризуется элементами п; М.,,. ..,М5; т,

где n - порядковый номер узла;

М,.. .

о о.Ms - код-маска;

m - код-основание.

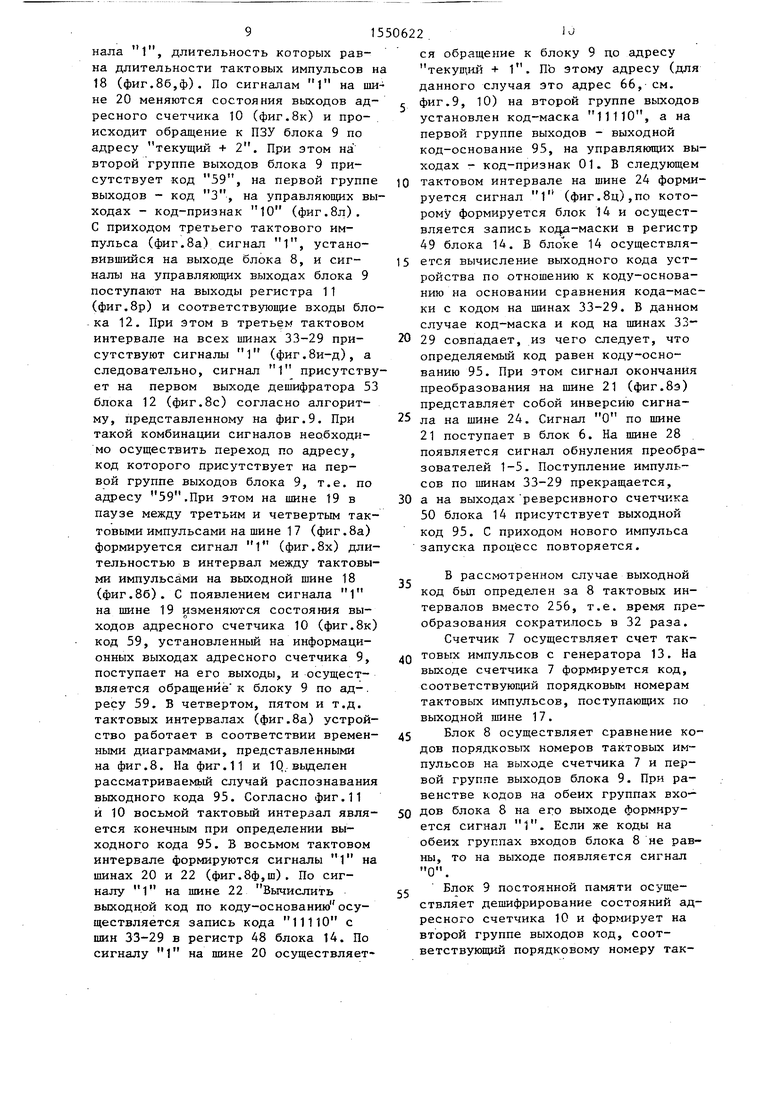

Программирование ПЗУ блока 9 осу., ществляется следующим образом.

Для каждого значения m из диапазона (1, 2 ) рассчитываются множества

если m 2 ;

5

0

5

0

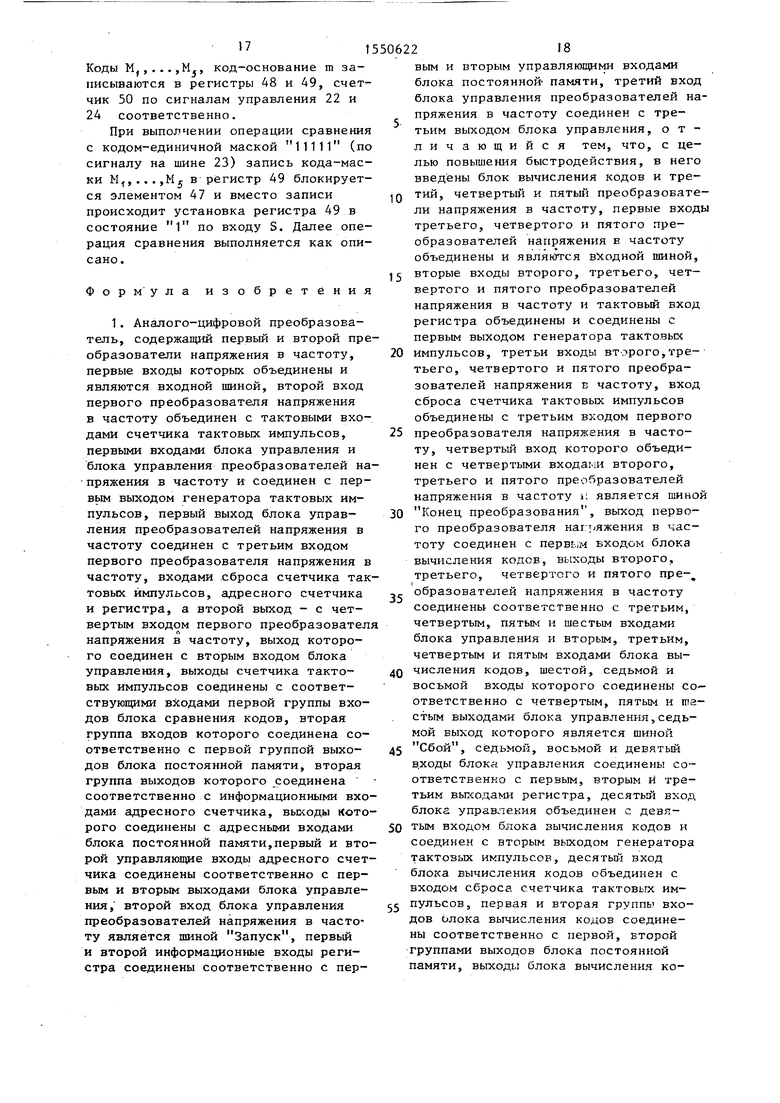

Каждым узлам 1-го рода и промежуточным узлам соответствует свой код-признак 1112В соответствии с деревом кодов формируется таблица для программирования блока 9, пример реализации ко- торой для N 7 и формат слова представлены на фиг.11. Порядковый номер узла n определяет адрес слова, хранящегося в ПЗУ.

Для узлов 1-го рода группа разрядов 0-N-2 (вторая группа выходов блока 9) определяет порядковый номер тактового импульса Р, с которым сравниваются 1-е импульсы на выходных шинах 33-29. Для промежуточных узлов группа разрядов 0-4 (вторая группа выходов блока 9) определяет код-маску М,,...,М5. Для узлов 1-го рода группа

разрядов N-1-Q (первая группа выходов блока 9) определяет либо следующий адрес обращения к блоку 9, если из узла с данным- порядковым номером n еще имеются ветвления, либо код- основание т, если ветвлений нет. Для промежуточных узлов группа разрядов N-1-Q (первая группа выходов блока 9) определяет код-основание т. Количество разрядов в первой группе выходов блока 9 равно N-1. Количество разрядов в группе N-1-Q определяется количеством разрядов выходного кода АЦП и для (фиг.11) равно 7. Разряды Q+1 и Q+2 определяют код-признак . Если код-признак 10 или 00, то на первой группе выходов блока 9 присутствует код, соответствующий порядковому

0

5

омеру Р, с которым могут совпадать се 1-е импульсы на выходных шинах 3-29, но 1-е импульсы не являются конечными в совокупности фрагментов P|S, i 1,...,М, т.е. i f M. При этом на второй группе выходов блока 9 присутствует код, соответствующий новому адресу перехода А (фиг.11). Если код-признак 11, то на первой группе выходов блока 9 присутствует код, соответствующий порядковому

ц

номеру Р , с которым могут совпадать все М-е импульсы на выходных шинах 33-29 т.е. конечные импульсы фрагментов совокупности Р ; , i М. При этом на второй группе выходов блока 9 присутствует код-основание m (фиг.11). Если код-признак 01, то на второй группе выходов блока 9 присутствует код-маска М.,,...,М5 а на первой группе выходов блока 9 присутствует код-основанИе (фиг.11).

Адресный счетчик 10 служит для формирования адреса обращения к ПЗУ блока 9. По сигналу 1 на шине 19 код с первой группы выходов блока 9, , выставленный на информационных входах адресного счетчика 10, появляется на.

его выходах, соединенных с адресными 30 выходе дешифратора 53 (фиг.8с). Если

входами блока 9. Происходит обращение к блоку 9 по адресу, код которого присутствовал на информационных входах адресного счетчика 10. При наличии сигнала 1 на шине 20 происходит наращивание на единицу выходного кода счетчика 10, т.е. происходит обращение к ПЗУ блока 9 по следующему адресу.

Регистр 11 служит для исключения ложных срабатываний блока 12. Ложные срабатывания блока 12 без введения регистра 11 возможны, например, при выполнении команды Нарастить адрес на 2. В этом случае на шине 20 в паузе между тактовыми импульсами (шина 17, фиг.8а). формируются два сигнала 1 (фиг.8ф), с приходом каждого из которых изменяются состояния выходов адресного счетчика 10 и блока 9 (фиг.8к), а следовательно, и состояние седьмого и восьмого входов блока 12 (при отсутствии регистра 11).При этом для правильного функционирования устройства в соответствии с алгоритмом (фиг.9) необходимо, чтобы состояния седьмого и восьмого входов блока управления изменялись только с приходом второже на всех шинах 33-29 присутствует сигнал О, то сигнал 1 появляется на пятом выходе дешифратора 53 (фиг.8у). Если на первом - пятом вхо35 дах дешифратора 53 установлена одна из возможных комбинаций сигналов, содержащих 1 и 11110 ; 11100, 11000, 10000, то сигнал 1 появляется на выходе элемента 77

40 (фиг.8т).

На первый-второй входы дешифратора 52 блока 12 поступает код-признак с первого-второго выходов регистра 11 (седьмой, восьмой входы блока 12).

45 В зависимости от комбинации сигналов на первом-втором входах дешифратора 52 сигнал 1 появляется на одном из его выходов.Если на первом- втором входах дешифратора 52 присут50 ствуют комбинации сигналов 10, 00, 11 или 01, то сигнал .1 появляется соответственно на первом, втором, третьем или четвертом выходах дешифратора 51 (фиг.8л, м, н, о).

55 В зависимости от комбинаций сигналов на первом-четвертом выходах дешиф- ратора 52, первом и пятом выходах дешифратора 53, выходе элемента 77, шинах 17, 18, третьем выходе реги

го сигнала 1 (фиг.8ф) в паузе между тактовыми имп-ульсами на шине 17. Для этого информация с управляющих выходов блока 9 (первый и второй входы регистра 11) поступает на выходы регистра 11 (седьмой и восьмой входы блока управления 12) только с приходом следующего после рассматриваемой паузы тактового импульса на шине 17 (фиг.8). Аналогично посредством регистра 11 осуществляется передача сигнала с; выхода блока 8 (шина 26) на девятый вход блока 12.

Блок 12 осуществляет формирование сигналов управления для адресного счетчика 10 (шины 19, 20, фиг.8ф,х) блока 14 (шины 22, 23, 24, фиг.Зщ, ч,ц), блока 6 (шина 21, фиг.вэ) и сигнала сбоя (шина 25, фиг.8ю). На входы дешифратора 53 блока 12 поступают сигналы соответственно с шин 33-29.

В зависимости от комбинации сиг- 5 налов на шинах 33-29 на одном из выходов дешифратора 53 появляется сигнал 1. Если на всех выходных шинах 33-29 присутствуют сигналы 1, то сигнал 1 появляется на первом

5

0

же на всех шинах 33-29 присутствует сигнал О, то сигнал 1 появляется на пятом выходе дешифратора 53 (фиг.8у). Если на первом - пятом входах дешифратора 53 установлена одна из возможных комбинаций сигналов, содержащих 1 и 11110 ; 11100, 11000, 10000, то сигнал 1 появляется на выходе элемента 77

(фиг.8т).

На первый-второй входы дешифратора 52 блока 12 поступает код-признак с первого-второго выходов регистра 11 (седьмой, восьмой входы блока 12).

В зависимости от комбинации сигналов на первом-втором входах дешифратора 52 сигнал 1 появляется на одном из его выходов.Если на первом- втором входах дешифратора 52 присутствуют комбинации сигналов 10, 00, 11 или 01, то сигнал .1 появляется соответственно на первом, втором, третьем или четвертом выходах дешифратора 51 (фиг.8л, м, н, о).

В зависимости от комбинаций сигналов на первом-четвертом выходах дешиф- ратора 52, первом и пятом выходах дешифратора 53, выходе элемента 77, шинах 17, 18, третьем выходе реги15

с тра 11 (девятый вход блока 12, фиг.8л-о), на его выходах формируются соответствующие сигналы управления для адресного счетчика 10 (фиг.8х,ф), сигналы управления для блока 14 (фиг.8ц, ч, щ), сигналы окончания преобразования для блока 6 (фиг.8э), сигналы сбоя (фиг.8ю). Причем сигнал 1 на шине 25, ха- рактеризующий сбой, формируется при любом несоответствии распределения импульсов на шинах 29-33, предварительно рассчитанном распределениям. В правом части диаграммы (фиг.8, фрагменты II, III) иллюстрируются возможные варианты комбинаций сигналов, характеризующие собой устройства. В левой части диаграммы (фиг. фрагмент I) иллюстрируется работа устройства при распознавании значения кода m 95 по совокупности фраментов, формируемых на выходных шинах 33-29.

Генератор 13 формирует тактовые импульсы с частотой f0 (шина 18; и тактовые импульсы с частотой f0/4 (шина 17).

Блок 14 работает следующим образом.

Функцией блока 14 является опредление окончательного значения выходного кода по результатам сравнения сигналов на выходных шинах 33-29 (код Х,...,хр и кода-маски И f, .. . Mj (первая группа входов блока 14), поступающего с первой группы выходов блока 9. Кроме того, может потребоваться сравнение кода X ,,...,Х с кодом-единичной маской 11111. При этом,определение окончательного значения кода производится путем модификации кода-основания m (вторая группа входов блока 14), поступающего с второй группы выходов блока 9. Модификация состоит в добавлении или вычитании единиц из кода-основания, число которых определяется разницей в числе единиц в коде-маске Mt,...,M5H в коде X.

ч

Х5, т.е. разностью п-1. Причем если

единиц больше (нулей меньше) в коде-маске, то происходит вычитание, а в противном случае - добавление

единиц к коду-основанию т. Фактически мент 44 закрывается и завершается

это означает, что необходимо произвести наращивание кода-основания m столько раз, сколько нулей в коде- маске М1,..., уменьшение его

определение окончательного значени выходного кода из кода-основания. При этом значение выходного кода присутствует на выходах счетчика 5

20

JQ 55 , 550622 столько раз, Х., ... ,Х.

J6

сколько нулей в коде В блоке 14 это производится путем записи кодов Х1,...,ХЈ и Мл,...,М, в регистры 48 и 49 соответственно и осуществления операции сдвига до появления уровня 1 на выходах регистров (число сдвигов v равно числу нулей). Код-основание m из блока 9 записывается в счетчик 50. С каждым тактом сдвига импульсы с выходной шины 18 поступают на входы вычитания или сложения счетчика 50 в зависимости от того, в каком регистре (48 или 49) происходит сдвиг. Порядок сдвигов не имеет значения, важен лишь конечный результат, который всегда равен разности числа сдвигов кода-маски М

1

35

М

и кода Х.,,... с сохранением знака. Для определенности принято, что в начале происходит сдвиг кода X4,...,Xj, а затем - кода-маски . М,...,М5.

25 После поступления сигнала 1 по шине 24 RS-триггер 42 устанавливается в единичное состояние и разрешает прохождение тактовых импульсов с шины 18 через элемент 44 на входы эле30 ментов 45 и 46. Так как D-триггер 43 установлен в состояние О по входу S, тактовые импульсы проходят через элемент 46 на С-вход регистра 48 и вход вычитания счетчика 50, т.е. осуществляется сдвиг кода X.,, ...,Х,. (шины 33-29) и вычитание 1 из кода- основания m (вторая группа входов блока 14). Каждым тактовым импульсом производится запись в D-триггер 43 по входу D состояния на выходе регистра 48. С появлением сигнала 1 на этом выходе D-триггер 43 перебрасывается в состояние 1, элемент 46 закрывается, а элемент 45 открывается, а тактовые импульсы поступают на регистра 49 и вход сложения счетчика 50. Таким образом, происходит сдвиг кода М1, ...,М5 (первая группа входов блока 14) и

50 добавление 1 к коду-основанию (вторая группа входов блока 14). С появлением сигнала 1 на выходе регистра 49 перебрасывается в исходное (нулевое) состояние RS-триггер 42, эле40

45

определение окончательного значения выходного кода из кода-основания. При этом значение выходного кода присутствует на выходах счетчика 50.

Коды Mf,...,M5, код-основание m записываются в регистры 48 и 49, счетчик 50 по сигналам управления 22 и 24 соответственно.

При выполнении операции сравнения с кодом-единичной маской 11111 (по сигналу на шине 23) запись кода-маски МТ,...,М5 в регистр 49 блокируется элементом 47 и вместо записи происходит установка регистра 49 в состояние 1 по входу S. Далее операция сравнения выполняется как описано.

Формула изобретения 1. Аналого-цифровой преобразователь, содержащий первый и второй преобразователи напряжения в частоту, первые входы которых объединены и являются входной шиной, второй вход первого преобразователя напряжения в частоту объединен с тактовыми входами счетчика тактовых импульсов, первыми входами блока управления и блока управления преобразователей напряжения в частоту и соединен с первым выходом генератора тактовых импульсов, первый выход блока управления преобразователей напряжения в частоту соединен с третьим входом первого преобразователя напряжения в частоту, входами сброса счетчика тактовых импульсов, адресного счетчика и регистра, а второй выход - с четвертым входом первого преобразователя напряжения в частоту, выход которого соединен с вторым входом блока управления, выходы счетчика тактовых импульсов соединены с соответствующими входами первой группы входов блока сравнения кодов, вторая группа входов которого соединена соответственно с первой группой выходов блока постоянной памяти, вторая группа выходов которого соединена соответственно с информационными входами адресного счетчика, выходы которого соединены с адресными входами блока постоянной памяти,первый и второй управляющие входы адресного счетчика соединены соответственно с первым и вторым выходами блока управления, второй вход блока управления преобразователей напряжения в частоту является шиной Запуск, первый и второй информационные входы регистра соединены соответственно с пер0

5

0

5

вым и вторым управляющими входами блока постоянной памяти, третий вход блока управления преобразователей напряжения в частоту соединен с третьим выходом блока управления, отличающийся тем, что, с целью повышения быстродействия, в него введены блок вычисления кодов и третий, четвертый и пятый преобразователи напряжения в частоту, первые входы третьего, четвертого и пятого преобразователей напряжения в частоту объединены и являются входной шиной,

5 вторые входы второго, третьего, четвертого и пятого преобразователей напряжения в частоту и тактовый вход регистра объединены и соединены с первым выходом генератора тактовых

0 импульсов, третьи входы второго,третьего, четвертого и пятого преобразователей напряжения в частоту, вход сброса счетчика тактовых импульсов объединены с третьим входом первого

5 преобразователя напряжения в частоту, четвертый вход которого объединен с четвертыми входаки второго, третьего и пятого преобразователей напряжения в частоту i. является шиной

0 Конец преобразования, выход первого преобразователя наг ьяжения в частоту соединен с первьм входом блока вычисления кодов, впходы второго, третьего, четвертого и пятого пре- образователен напряжения в частоту соединены- соответственно с третьим, четвертым, пятым и шестым входами блока управления и вторым, третьим, четвертым и пятым входами блока вычисления кодов, шестой, седьмой и восьмой входы которого соединены соответственно с четвертым, пятым и шестым выходами блока управления,седьмой выход которого является шиной Сбой, седьмой, восьмой и девятый входы блока управления соединены соответственно с первым, вторым и третьим выхода.ш регистра, десятый вход блока управления объединен с девя0 тым входом блока вычисления кодов и соединен с вторым выходом генератора тактовых импульсов, десятый вход блока вычисления кодов объединен с входом сброса счетчика тактов пс импульсов, первая и вторая группы входов олока вычисления кодов соединены соответственно с первой, второй группами выходов блока постоянной памяти, выходы блока вычисления кодов являются выходной шиной, причем выход блока сравнения кодов соединен с третьим информационным входом регистра .

первого элемента И и является десятым входом блока, выход счетного триггера соединен с первыми входами второго, третьего, четвертого, пятого, шестого, седьмого и восьмого

5 элементов И, второй вход которого объединен с первым входом первого элемента ИЛИ и соединен с выходом девятого элемента И, третий вход восьмого элемента И объединен с вторыми

0 входами седьмого, первого и третьего элементов И и соединен с выходом первого элемента НЕ, вход которого является первым входом блока, первый вход девятого элемента И соеди5 нен с выходом второго элемента ИЛИ, второй вход объединен с первым входом третьего элемента ИЛИ и соединен с первым выходом первого дешифратора, третий вход объединен с пер0 выми входами десятого, одиннадцатого, двенадцатого, тринадцатого, четырнадцатого элементов И, входом второго элемента НЕ и является девятым входом блока, вторым, третьим,

с четвертым, пятым и шестым входами

блока являются соответственно первый, второй, третий, четвертый и пятый входы первого дешифратора, второй, третий, четвертый и пятый выходы ко0 торого соединены соответственно с первым, вторым, третьим и четвертым входами четвертого элемента ИЛИ, выход которого соединен с первым входом пятого элемента ИЛИ, вторым вхо5 Дом третьего элемента ИЛИ и вторым входом четырнадцатого элемента И, шестой выход первого дешифратора соединен с вторым входом пятого элемента И, вторыми входами

0 тринадцатого и десятого элементов И, третий вход которого объединен с вторым входом одиннадцатого элемента И и соединен с первым выходом второго дешифратора, выход десятого элег мента И соединен с первым входом шестого элемента ИЛИ, второй вход которого соединен с выходом четырнадцатого элемента И, а выход соединен с вторым входом шестого элемента И

и вторым входом первого элемента ИЛИ третий вход которого объединен с третьим входом третьего элемента И и соединен с выходом одиннадцатого элемента И, выход первого элемента ИЛИ соединен с третьим входом седьмого элемента И, выход которого соединен с входом первого дифференцир ующего элемента,выход которого является шестым выходом блока, первым и вторым выходами которого являются соответственно выходы восьмого элемента И и седьмого элемента ИЛИ, первый и второй входы которого соединены соот ветственно с выходами шестого и пятого элементов И, второй вход последнего из которых соединен с выходом первого элемента И, третий вход объединен с третьими входами третьего и шестого элементов И, вторыми входами второго и четвертого элементов И, третьи входы четвертого и второго Элементов И соединены соответственно с выходом восьмого элемента ИЛИ и вторым выходом второго дешифратора, выход четвертого элемента И является седьмым выходом блока, выход второго элемента И соединен с первым входом девятого элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, который является пятым выходом блока, выход девятого элемента ИЛИ соединен с входами второго дифференцирующего элемента и третьего элемента НЕ, выход которого соединен с входом третьего дифференцирующего элемента, выход которого и выход второго дифференцирующего элемента являются соответственно третьим и четвертым выходами блока, седьмым и восьмым входами которого являются соответственно первый и второй входы второго дешифратора, третий выход которого соединен с первым входом второго элемента ИЛИ и третьими входами тринадцатого и четырнадцатого элементов И, четвертый выход соединен с вторыми входами второго элемента ИЛИ и двенадцатого элемента И, третий вход которого соединен с выходом пятого элемента ИЛИ, а БЫХ.ОД соединен с первым входом восьмого элемента ИЛИ, второй вход которого соединен с выходом пятнадцатого элемента И, первый вход которого объединен с третьим входом одиннадцатого элемента И и соединен с выходом третьего элемента ИЛИ, вто

0

0

с

рой вход соединен с выходом второго элемента НЕ, третий вход первого элемента И соединен с выходом тринадцатого элемента И.

5 четвертым входом блока, информационный вход объединен с второй обкладкой конденсатора, первым выводом резистора ,инвертирующим входом второго операционного усилите.гг и соединен с выходом первого клкп ,информационный вход которого чер.. источник тока соединен с шиной лапряжения отрицательной полярности, второй вывод резистора является первым входом блока, неинвертирующий вход второго операционного усилителя является шиной нулевого потенциала.

5 тока, конденсаторе и D-триггере, С- и R-входы которого являются соотрет- ственно вторыми и четвертыми входами блока, прямой выход соединен с управляющим входом первого ключа и является выходом блока, D-вход соединен с выходом первого операционного усилителя, инвертирующий вход которого соединен с первой обкладкой конденсатора, выходами второго ключа и второго операционного усилителя, инвертирующий вход которого объединен с информационным входом второго ключа, второй обкладкой конденсатора, первым выводом первого резистора

0

5

0

0

5

и соединен с выходом первого ключа, информационный вход которого через источник тока соединен с первой шиной

напряжения отрицательной полярности,

j

неинвертирующий вход второго операционного усилителя соединен с подвижным контактом регулируемого резистора, первый вывод которого объединен с неинвертирующим входом первого операционного усилителя и является шиной нулевого потенциала, второй вывод через второй резистор соединен с второй шиной напряжения отрицательной полярности, второй вывод первого резистора и управляющий вход второго ключа являются соответственно первым и четвертым входами блока.

инверсный выход первого D-триггера соединен с первым входом элемента И, второй вход которого является nep-s вым входом блока, выход элемента И соединен с С-входом второго D-триггера, D-вход которого объединен с С-входом первого D-триггера и соединен с инверсным выходом второго Dтриггера, который является первым выходом блока, R-вход второго D - триггера объединен с R-входом первого D-триггера, D-входом третьего D-триггера и соединен с прямым выхо-

5 Дом RS-триггера, R-вход которого

объединен с R-входом третьего D-триггера и является третьим входом блока, вторым входом которого является S- вход RS-триггера, С-вход третьего D0 триггера соединен с прямым выходом второго D-триггера, инверсный выход третьего триггера является вторым выходом блока.

Фие.2

$

ФигЬ

Фиг. 6

Фиг. 5

100

г-ЯЙ

Ґ

Pt/8.7

W1

Код-п/зизнак1,1г (управляющие, быходы б/то на 9)

1-й выход де- шифрато- pa5S .Выход шиныЗЗ-29

11171

10

Т,.. О

ооооо

7111

00

ООООО

77771

71

ООООО

01

5-й бь/ход де шифра/по-,

paS2 &bfXod ишны 33-29

Вьмод элемента

Г ВЫХОВ UJUH6133-29

Выход

ШиНб/ 26

Сигналы управления

71111

О

11111

Переход по адресу „А

/.., О

ТТ.. О

Нарастить адрес на ,JH

ООООй

ооооо

Нарастить адрес на „2

71111

7/7 //

Переход по адресу „ А

/... О

/... О

Сбой устройства

ООООО

о

ооооо

71111

71171

/

Сравнить код на вых. шинах 29-35 с кодом-единичной маской „fitIf, конец преобразования

ооооо

о

ооооо

Нарастить адрес на „7

Сравнить код на вь/х. шинах 29-33 с кодом-маской, конец преобразования

О

Сбой устройства

Фие,&

Узм1/-гороЗаЈ&

V biM-iofo tf

ТУ - gv

0/

moo

©

Фиг. /О

w «/.../«/ri

Основные узлы i-so рода: n порядковый номер ума;

р -порядковый нонер тактового импульса, совпадающего с 1-м Ufi/ty/ibcati прсойразобатем на/фл- жыил в wcmofrty;

т - выходной

lr If - код -признак

i - Промежуточные узлы: а-порядковый номер узла; M...Mf -код-маска} т - Выходной ход

Ln Ul О О 10 КЗ

Редактор Н.Швыдкая

Составитель А.Титов

Техред Л.Олийнык Корректор Э.Лончакова

Заказ 279

Тираж 666

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Фиг. Ц

Подписное

| Аналого-цифровой преобразователь | 1983 |

|

SU1132357A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1462482A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-03-15—Публикация

1987-08-24—Подача