Изобретение относится к области вычислительной техники и может быть использовано в сетевых системах обеспечения управления объектами экономики, топливно-энергетического комплекса, транспорта, связи, энергетики, сельского хозяйства, промышленности, космонавтики и в других областях. Так, его применение в составе аппаратуры на объектах наземного комплекса управления космическими аппаратами (КА), в том числе и в центрах управления полетами КА, позволит сократить потери времени на ожидание выделения требуемых системных ресурсов, а также на фиксации и выдаче информации о нештатных ситуациях (тупиковых), что способствует повышению оперативности и устойчивости работы комплекса в целом.

Из предшествующего уровня техники известны устройства для контроля и обслуживания распределения ресурсов: Устройство для обслуживания запросов, авторское свидетельство СССР, №972512, 1982 г., - (Д1); Устройство для контроля распределения ресурсов, авторское свидетельство СССР, №1215112, 1986 г., - (Д2); Устройство для контроля распределения ресурсов в вычислительных системах, авторское свидетельство СССР, №1269138, 1986 г., - (Д3); Устройство для обнаружения тупиковых ситуаций, авторское свидетельство СССР, №1320810, 1987 г., - (Д4); Устройство для контроля распределения ресурсов, авторское свидетельство СССР, №1297051, 1987 г., - (Д5); Устройство для контроля распределения ресурсов в вычислительной системе, авторское свидетельство СССР, №1312583, 1987 г., - (Д6); Устройство для контроля распределения ресурсов, авторское свидетельство СССР, №1341642, 1987 г., - (Д7).

К основным недостаткам вышеприведенных устройств следует отнести невозможность непосредственного их использования в составе компьютеров или в сетях ввиду отсутствия у них так называемой стандартной интерфейсной части, а также возможные временные простои между окончанием приема устройствами входной информации и готовностью устройств к выполнению контрольных процедур, в том числе невозможность фиксации и выдачи информации о тупиковых ситуациях непосредственно в управляющий компьютер или в сеть.

Из вышеприведенных известных устройств (Д1-Д7) наиболее близким по оперативности и функциональности является устройство, приведенное в (Д7), которому присуща совокупность признаков, наиболее близкая к совокупности существенных признаков заявляемого устройства, и поэтому оно выбрано в качестве прототипа. Однако, как показывает анализ аналогов и прототипа, в устройствах отсутствуют технические решения, обеспечивающие их высокую готовность и оперативность процессов контроля распределения системных ресурсов. Именно отсутствие стандартной интерфейсной части не позволяет обеспечить прямое подключение устройств к источнику информации (к управляющему компьютеру либо к адаптеру сети) и фиксацию моментов времени начала и окончания заполнения информацией входных регистров, после чего устройство, хотя и готово начать процедуру анализа и контроля распределения ресурсов, но простаивает ввиду отсутствия сигнала начала процедуры по причине отсутствия компонента, формирующего сигнал «Пуск». В дополнение к этому в данных устройствах отсутствует буферная память для записи и считывания информации об обнаруженных тупиковых ситуациях и выдачи ее в компьютер управления или в сеть.

Задачей, на решение которой направлено заявленное техническое решение, является расширение арсенала технических средств, в которых возможно использование устройства контроля распределения ресурсов, а именно в составе управляющих компьютеров или в компьютерных сетях.

Сущность заявленного изобретения заключается в том, что в состав устройства введены интерфейсная часть, реализуемая на основе стандартных интерфейсов (СОМ-портов), а также буферная память со схемами управления, счетчиком и схемой И, что совместно с другими элементами цифровой техники обеспечивает расширение арсенала технических средств использования контроллера распределения ресурсов. При этом контроллер распределения ресурсов содержит две группы регистров, триггер режима, два триггера управления, триггеры анализа и тупика, три группы элементов И, элемент И-НЕ, распределитель импульсов, мультиплексор, первую схему сравнения, две группы ключей, семь элементов И, первый элемент ИЛИ и элемент ИЛИ-НЕ, третью группу ключей, второй элемент ИЛИ, (n-1) схему сравнения, причем информационный вход р-го регистра первой группы (р=1,…n, где n - число ресурсов в системе) соединен с выходом р-го ключа первой группы, информационный вход р-го регистра второй группы соединен с выходом р-го ключа второй группы, первый вход сброса р-го регистра первой группы подключен к выходу р-го элемента И третьей группы, второй вход сброса р-го регистра первой группы подключен к выходу р-го элемента И второй группы, вход сброса р-го регистра второй группы подключен к выходу р-го элемента И первой группы, выходы р-го регистра первой группы соединены с соответствующими инверсными входами р-го элемента И первой группы и с р-ми информационными входами мультиплексора, выходы р-го регистра второй группы соединены с соответствующими инверсными входами р-го элемента И второй группы, входы установки и сброса триггера режима соединены с входом пуска устройства и с выходом триггера анализа соответственно, инверсный выход триггера режима соединен с управляющими входами ключей первой и второй групп и с соответствующими инверсными входами элементов И первой и второй групп, входы установки и синхронизации первого триггера управления подключены к выходам первого элемента ИЛИ и второго элемента И соответственно, входы установки и сброса второго триггера управления соединены с выходом седьмого и четвертого элементов И соответственно, прямой и инверсный выходы второго триггера управления подключены к первым входам четвертого и пятого элементов И соответственно, выход пятого элемента И соединен с входом установки триггера анализа, вход сброса которого соединен с входом сброса триггера тупика и с входом пуска устройства, выход триггера анализа соединен с первым входом шестого элемента И, выход которого подключен к входу установки триггера тупика, выход которого соединен с выходом признака тупиковой ситуации устройства, выходы элементов И первой группы соединены с входами элемента И-НЕ, выход которого соединен с вторым входом шестого элемента И, тактовый вход распределителя импульсов подключен к выходу второго элемента И, выходы распределителя импульсов подключены к входам элемента ИЛИ-НЕ, к управляющим входам мультиплексора и к первым входам соответствующих элементов И третьей группы, выход признака окончания цикла распределителя импульсов соединен с вторыми входами четвертого и пятого элементов И, выходы мультиплексора соединены с первыми информационными входами первой схемы сравнения и с инверсными входами третьего элемента И, информационные входы ключей первой и второй групп образуют входы номеров процессов, соответственно владеющих и запрашивающих ресурсы устройства, вторые входы элементов И третьей группы соединены с выходом седьмого элемента И, первый и второй инверсные входы первого элемента И подключены к выходам третьего элемента И и элемента ИЛИ-НЕ соответственно, второй вход второго элемента И подключен к входу тактовых импульсов устройства, выход элемента ИЛИ-НЕ соединен с соответствующим инверсным входом третьего элемента И, выход которого подключен к первому входу первого элемента ИЛИ, выход четвертого элемента И соединен с вторым входом первого элемента ИЛИ, третий вход которого подключен к входу пуска устройства, информационные входы р-го ключа третьей группы объединены с соответствующими выходами р-го регистра второй группы, входы управления ключей третьей группы подключены к выходу первого элемента И, первые информационные входы с второй по n-ю схем сравнения соединены с выходом мультиплексора, выходы р-го ключа третьей группы подключены к соответствующим вторым информационным входам р-й схемы сравнения, выходы признака совпадения всех схем сравнения подключены к соответствующим входам второго элемента ИЛИ, выход которого соединен с четвертым входом первого элемента ИЛИ, выходы признаков несовпадения всех схем сравнения подключены к входам седьмого элемента И, выход которого соединен с пятым входом первого элемента ИЛИ, интерфейсную часть, содержащую два стандартных разъема СОМ-порта, две группы элементов И, два распределителя импульсов, три схемы И, два инвертора НЕ и два универсальных асинхронных приемопередатчика, причем первые входы первой и второй группы элементов И соединены с выходом первого и второго универсального асинхронного приемопередатчика, которые по входу соединены с разъемом первого и второго СОМ-порта соответственно, вторые входы первой и второй группы элементов И соединены с выходами первого и второго распределителя импульсов, выходы признака окончания цикла первого и второго распределителя импульсов заведены на входы первого и второго инвертора и третьей схемы И, выход которой соединен с единичным входом триггера режима, а выход первого и второго инвертора соединены со входом первого и второго СОМ-порта с шиной CTS «Вход - Устройство готово к работе», первые входы первой и второй схемы И соединены с выходом первого и второго СОМ-порта с шиной RTS «Выход - Готовность компьютера к передаче данных», вторые входы первой и второй схемы И соединены с инверсным выходом триггера режима, а также буферную память со схемами управления, схему И и счетчик, при этом буферная память со схемами управления содержит микросхемы памяти и схемы управления записью информации и считыванием, причем по первому входу схемы управления (запись) соединены с выходом счетчика, по второму входу схемы управления (считывание) - с инверсным выходом триггера режима, буферная память по входу соединена с выходом группы схем сравнения, а по выходу - со входом первого универсального асинхронного приемопередатчика, по входу счетчик соединен с выходом схемы И, первый вход которой соединен с выходом триггера тупика, второй вход - с тактовым генератором.

Технический результат изобретения заключается в расширении арсенала технических средств, в которых возможно использование контроллера распределения ресурсов, и заключается в фиксации оборудованием интерфейсной части моментов времени начала и окончания заполнения информацией входных регистров, после чего устройство автоматически сформированным сигналом «Пуск» переводится в состояние готовности выполнения процедуры контроля, а также путем своевременного обнаружения и фиксации тупиковых ситуаций и оперативной передачи этой информации в управляющий компьютер или в сеть посредством задействования интерфейсной части устройства.

Указанный технический результат достигается тем, что в известное устройство, выбранное в качестве прототипа, и содержащее две группы регистров, триггер режима, два триггера управления, триггеры анализа и тупика, три группы элементов И, элемент И-НЕ, распределитель импульсов, мультиплексор, первую схему сравнения, две группы ключей, семь элементов И, первый элемент ИЛИ и элемент ИЛИ-НЕ, третью группу ключей, второй элемент ИЛИ, (n-1) схему сравнения, причем информационный вход р-го регистра первой группы (р=1,…n, где n - число ресурсов в системе) соединен с выходом р-го ключа первой группы, информационный вход р-го регистра второй группы соединен с выходом р-го ключа второй группы, первый вход сброса р-го регистра первой группы подключен к выходу р-го элемента И третьей группы, второй вход сброса р-го регистра первой группы подключен к выходу р-го элемента И второй группы, вход сброса р-го- регистра второй группы подключен к выходу р-го элемента И первой группы, выходы р-го регистра первой группы соединены с соответствующими инверсными входами р-го элемента И первой группы и с р-ми информационными входами мультиплексора, выходы р-го регистра второй группы соединены с соответствующими инверсными входами р-го элемента И второй группы, входы установки и сброса триггера режима соединены с входом пуска устройства и с выходом триггера анализа соответственно, инверсный выход триггера режима соединен с управляющими входами ключей первой и второй групп и с соответствующими инверсными входами элементов И первой и второй групп, входы установки и синхронизации первого триггера управления подключены к выходам первого элемента ИЛИ и второго элемента И соответственно, входы установки и сброса второго триггера управления соединены с выходом седьмого и четвертого элементов И соответственно, прямой и инверсный выходы второго триггера управления подключены к первым входам четвертого и пятого элементов И соответственно, выход пятого элемента И соединен с входом установки триггера анализа, вход сброса которого соединен с входом сброса триггера тупика и с входом пуска устройства, выход триггера анализа соединен с первым входом шестого элемента И, выход которого подключен к входу установки триггера тупика, выход которого соединен с выходом признака тупиковой ситуации устройства, выходы элементов И первой группы соединены с входами элемента И-НЕ, выход которого соединен с вторым входом шестого элемента И, тактовый вход распределителя импульсов подключен к выходу второго элемента И, выходы распределителя импульсов подключены к входам элемента ИЛИ-НЕ, к управляющим входам мультиплексора и к первым входам соответствующих элементов И третьей группы, выход признака окончания цикла распределителя импульсов соединен с вторыми входами четвертого и пятого элементов И, выходы мультиплексора соединены с первыми информационными входами первой схемы сравнения и с инверсными входами третьего элемента И, информационные входы ключей первой и второй групп образуют входы номеров процессов, соответственно владеющих и запрашивающих ресурсы устройства, вторые входы элементов И третьей группы соединены с выходом седьмого элемента И, первый и второй инверсные входы первого элемента И подключены к выходам третьего элемента И и элемента ИЛИ-НЕ соответственно, второй вход второго элемента И подключен к входу тактовых импульсов устройства, выход элемента ИЛИ-НЕ соединен с соответствующим инверсным входом третьего элемента И, выход которого подключен к первому входу первого элемента ИЛИ, выход четвертого элемента И соединен с вторым входом первого элемента ИЛИ, третий вход которого подключен к входу пуска устройства, информационные входы р-го ключа третьей группы объединены с соответствующими выходами р-го регистра второй группы, входы управления ключей третьей группы подключены к выходу первого элемента И, первые информационные входы с второй по n-ю схем сравнения соединены с выходом мультиплексора, выходы р-го ключа третьей группы подключены к соответствующим вторым информационным входам р-й схемы сравнения, выходы признака совпадения всех схем сравнения подключены к соответствующим входам второго элемента ИЛИ, выход которого соединен с четвертым входом первого элемента ИЛИ, выходы признаков несовпадения всех схем сравнения подключены к входам седьмого элемента И, выход которого соединен с пятым входом первого элемента ИЛИ, дополнительно введены интерфейсная часть и буферная память со схемами управления, схемой И и счетчиком, при этом интерфейсная часть содержит два разъема СОМ-порта, две группы элементов И, два распределителя импульсов, три схемы И, два инвертора НЕ и два универсальных асинхронных приемопередатчика, причем первые входы первой и второй группы элементов И соединены с выходом первого и второго универсального асинхронного приемопередатчика, которые по входу соединены с разъемом первого и второго СОМ-порта соответственно, вторые входы первой и второй группы элементов И соединены с выходами первого и второго распределителя импульсов, выходы признака окончания цикла первого и второго распределителя импульсов заведены на входы первого и второго инвертора и третьей схемы И, выход которой соединен с единичным входом триггера режима, а выход первого и второго инвертора соединены со входом первого и второго СОМ-порта с шиной CTS «Вход - Устройство готово к работе», первые входы первой и второй схемы И соединены с выходом первого и второго СОМ-порта с шиной RTS «Выход - Готовность компьютера к передаче данных», вторые входы первой и второй схемы И соединены с инверсным выходом триггера режима, а буферная память со схемами управления содержит микросхемы памяти и схемы управления записью информации и считыванием, причем по первому входу схемы управления (запись) соединены с выходом счетчика, по второму входу схемы управления (считывание) соединены с инверсным выходом триггера режима, буферная память по входу соединена с выходом группы схем сравнения, а по выходу - со входом первого универсального асинхронного приемопередатчика, по входу счетчик соединен с выходом схемы И, первый вход которой соединен с выходом триггера тупика, второй вход - с тактовым генератором. При этом информационными входами контроллера распределения ресурсов являются входы универсальных асинхронных приемопередатчиков, а выходом - выход буферной памяти, соединенной с выходом первого универсального асинхронного приемопередатчика.

Описание изобретения поясняется следующими фигурами:

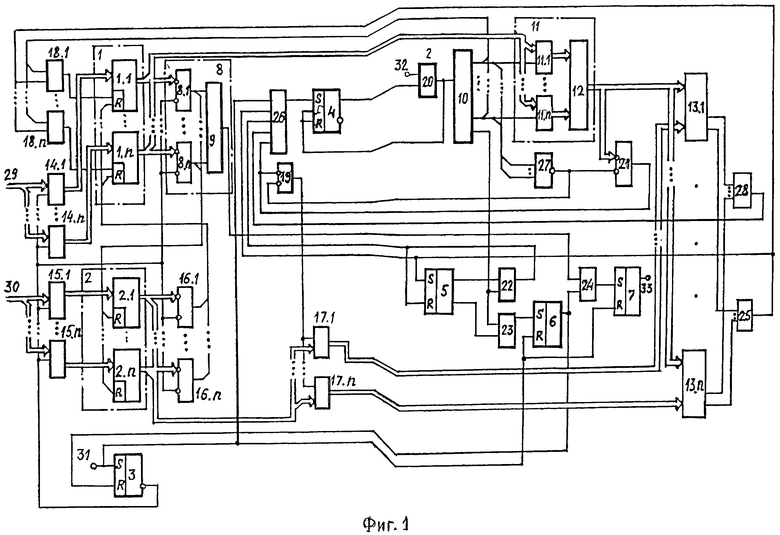

- на фиг.1 представлена структурная схема прототипа - устройства для контроля распределения ресурсов;

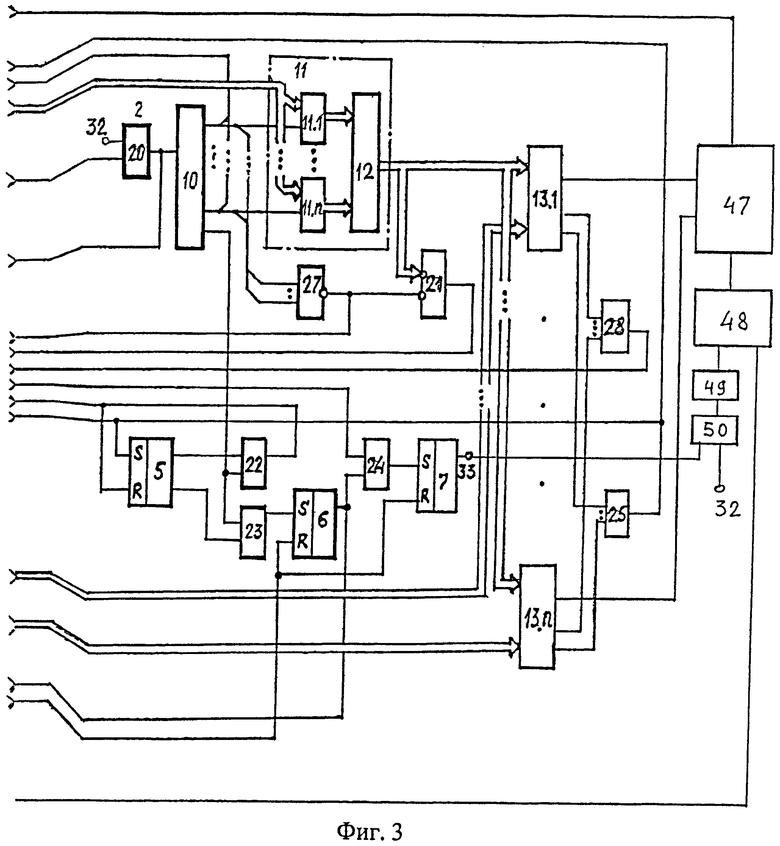

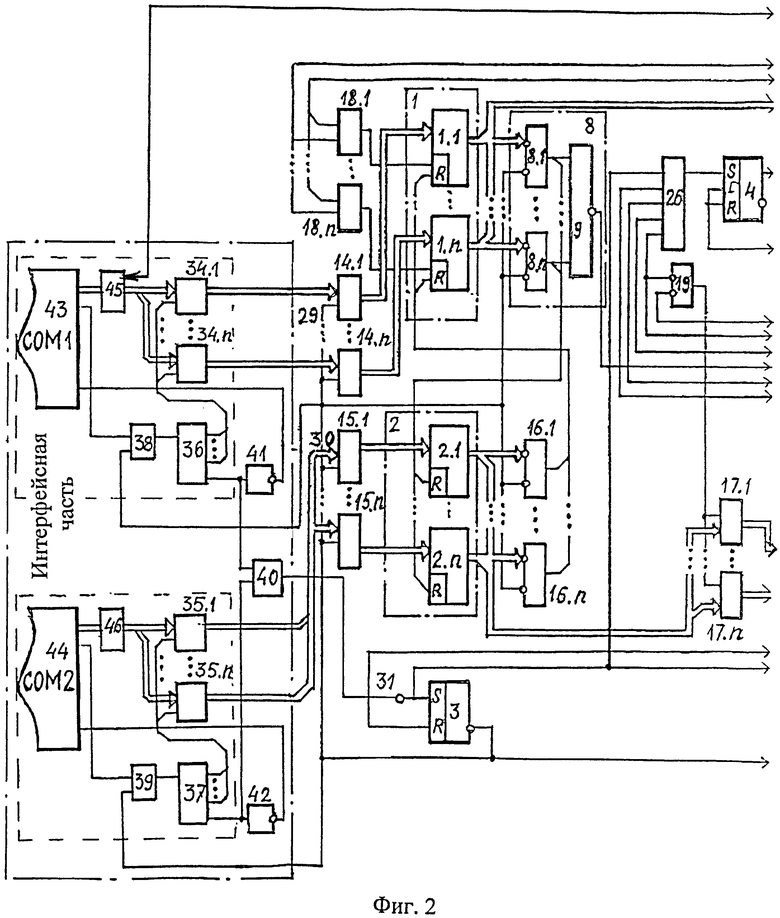

- на фиг.2 и 3 приведена структурная схема изобретения - контроллера распределения ресурсов.

Контроллер распределения ресурсов содержит первую группу 1 регистров 1.1-1.n, вторую группу 2 регистров 2.1-2.n, триггер 3 режима, первый 4 и второй 5 триггеры управления, триггеры анализа 6 и тупика 7, первую группу элементов И 8.1-8.n и элемент И-НЕ 9, распределитель 10 импульсов, мультиплексор 11 с выходным регистром 12, группу 13 схем 13.1-13.n сравнения, первую 14, вторую 15 группы ключей, вторую 16, четвертую 17 и третью 18 группы элементов И, первый - седьмой элементы И 19-25, а также первый элемент ИЛИ 26, элемент ИЛИ-НЕ 27 и второй элемент ИЛИ 28, первую 29 и вторую 30 группы информационных входов, вход 31 пуска и тактовый вход 32, выход 33 признака тупиковой ситуации, а также интерфейсную часть, содержащую первый 43 и второй 44 стандартные разъемы СОМ-порта, первую группу элементов И 34.1-34.n и вторую группу элементов И 35.1-35.n, два распределителя импульсов 36 и 37, три схемы И 38,39, 40, два инвертора НЕ 41 и 42, первый 45 и второй 46 универсальный асинхронный приемопередатчик, буферную память 47, схемы управления 48, счетчик 49 и схему И 50. Следует отметить, что назначение и нумерация общих элементов прототипа и заявленного изобретения совпадают, кроме элементов интерфейсной части и буферной памяти и ее управления. Устройство работает следующим образом.

В исходном состоянии все триггеры находятся в нулевом состоянии (входы начальной установки условно не показаны). Единичный сигнал с инверсного выхода триггера 3 разрешает прием информации через первую 14.1 - 14.n и вторую 15.1 - 15.n группы ключей в регистры 1 и 2 групп, а также закрывает группы элементов И 8 и 16, тем самым запрещается взаимная установка в нулевое состояние регистров первой 1 и второй 2 групп.

Информацией, поступающей на входы 29 и 30 устройства, являются коды номеров процессов, которые владеют ресурсами или выдают запросы, причем на вход 29 информация в последовательном коде поступает с СОМ1-порта 43 через универсальный асинхронный приемопередатчик 45, на вход 30 - с СОМ2-порта 44 через универсальный асинхронный приемопередатчик 46. СОМ1 и COM2 - это стандартные порты компьютера или коммуникатора сети, с помощью которых возможно информационное взаимодействие данного устройства с внешними компонентами (управляющими компьютерами или локальной сетью) [Михаил Гук, Аппаратные средства IBM PC, Санкт-Петербург, изд. Питер, 1999, стр.669 - (Д8)]. Важным моментом является то, что согласно протоколу СОМ-порта (Д8), информационный обмен осуществляется последовательной передачей битов. Последовательный режим обеспечивает двусторонний обмен данными, последовательность обмена данными определяется специальным протоколом. Данные разделяются служебными посылками, такими как стартовый и стоп биты (start bit, stop bit), для контроля ошибок служит бит контроля четности (parity bit), соответствующий четности или нечетности суммы битов машинного «слова» (байта).

Следует отметить, что входом устройства является интерфейсная часть в виде СОМ-портов типа RS-232 43 и 44, выполненных на универсальных асинхронных приемопередатчиках 45 и 46, которые, в свою очередь, построены на микросхемах UART (Universal Asynchronous Receiver/Transmitter). Как отмечается в (Д8), обычно используется микросхема UART 16550А. Она имеет 16-символьный буфер на прием и на передачу и, кроме того, может использовать несколько каналов прямого доступа в память DMA. При передаче микросхема UART преобразует параллельный код в последовательный и передает его побитно в линию, обрамляя исходную последовательность битами старта, останова и контроля. При приеме данных UART преобразует последовательный код в параллельный (разумеется, опуская служебные символы). Таким образом, с приемом универсальными асинхронными приемопередатчиками 45 и 46 первой информационной посылки на первые входы первой 38 и второй 39 схем И сигнал проходит на вход первого 36 и второго 37 распределителя импульсов, пока открыты вторые входы первой 38 и второй 39 схем И от инверсного выхода триггера режима 3. Первый 36 и второй 37 распределитель импульсов на выходе формируют и выбирают первые элементы И 34.1 и 35.1, остальные остаются невыбранными. Таким образом, информация проходит на входы блока ключей 14.1 и 15.1 соответственно.

С приемом универсальными асинхронными приемопередатчиками 45 и 46 второй информационной посылки распределителями 36 и 37 выбираются вторые элементы И 34.1 и 35.1, остальные остаются невыбранными, и принимаемая устройством информация поступает на входы вторых блоков ключей 14.2 и 15.2 соответственно. Такие циклы приема устройством информации повторяются до тех пор, пока на последних выходах распределителей импульсов 36 и 37 не появятся сигналы признака окончания циклов приема информации. С приходом этих сигналов на выходах инверторов 41 и 42 формируются сигналы, подаваемые на входы третьей схемы И 40 и на входы СОМ-портов 43 и 44 как сигналы неготовности устройства к приему информации от компьютера или от сетевого адаптера. С выхода третьей схемы И 40 сигнал подается на вход 31, запускающий цикл контроля распределения ресурсов (начала анализа). К этому моменту вся введенная информации находится в регистрах 1 и 2 групп, так как единичный сигнал с инверсного выхода триггера 3 разрешает прием информации через первую 14 и вторую 15 группы ключей.

По сигналу пуска (начала анализа) на входе 31 устройства триггер 3 режима устанавливается в единичное состояние, тем самым блокируется прием информации в регистры. С помощью групп 8.n элементов И устанавливаются в нулевое состояние те регистры 2.1-2.n, которые хранят коды номеров процессов, запрашивающих свободные ресурсы. Для таких ресурсов соответствующие регистры 1 группы регистров хранят нулевой код. Таким же образом устанавливаются в нуль регистры 1 группы регистров, хранящих коды номеров процессов, владеющих ресурсами, для которых в регистрах 2 группы хранится нулевой код.

Исключение из дальнейшего анализа некоторых процессов приводит к сокращению времени анализа. Удаленные процессы являются процессами, которые заведомо могут завершиться и не приведут к тупику.

Далее производится выявление процессов, являющихся только владельцами некоторых ресурсов, но не запрашивающих ресурсы. Если такой процесс существует, то код его номера не должен быть записан в одном из регистров 2 блока. Этим же сигналом начала анализа (через элемент ИЛИ 26) триггер 4 устанавливается в единичное состояние и сигнал с его выхода открывает элемент 20 И при наличии на втором входе элемента тактового импульса с входа 32 устройства. Сигнал с выхода элемента И 20 поступает на вход распределителя 10 импульсов. Потенциалом с первого выхода распре- делителя 10 импульсов через мультиплексор 11 выходы регистра 1.1 подключаются к первым группам входов схем 13.1-13.n сравнения. По заднему фронту сигнала с выхода элемента 20 И триггер 4 устанавливается в нулевое состояние и блокирует последующие выдачи тактовых сигналов на вход распределителя 10 импульсов.

Если код процесса оказывается нулевым, то элемент И 21 вырабатывает сигнал, разрешающий переход к проверке содержимого следующего «регистра 1 (р+1)». В противном случае элементы И-НЕ 27 и И 21 вырабатывают сигналы, открывающие элемент И 19, который выдает с выхода сигнал на входы элементов И блоков 17.1-17.n. Тем самым коды процессов, хранящиеся в регистрах 2.1-2.n, поступают на вторые группы входов схем 13.1-13.n сравнения.

Если при параллельном сравнении происходит хотя бы одно совпадение, т.е. проверяемый процесс не только владеет, но и запрашивает ресурсы, то срабатывает элемент ИЛИ 28, с выхода которого выдается сигнал на вход элемента ИЛИ 26. Тем самым осуществляется переход на анализ следующего процесса, владеющего ресурсами. При таком исходе сравнения триггеры 5, 6 и 7 остаются в нулевом состоянии. Если при сравнении результат иной, т.е. совпадения кодов не зафиксировано, то срабатывает элемент И 25. Сигнал на его выходе свидетельствует о том, что проверяемый процесс не запрашивает ресурсы и может быть завершен, а следовательно, при анализе его можно вычеркнуть из списка.

Для этого данный сигнал поступает на первые входы элементов И 18.1-18.n, с выходов которых единичный сигнал поступает на вход сброса в нуль регистра, в котором записан код процесса, выбранного для анализа. Изменение информации в данном регистре вызывает формирование на выходе одного из элементов И 8 потенциала, который поступает на вход сброса соответствующего регистра 2. Таким образом, осуществляется корректировка состояния распределения ресурсов после проведенного удаления. Одновременно с этим сигнал, сформированный на выходе элемента И 25, поступает на вход установки триггера 5 и на вход элемента ИЛИ 26. При этом начинается новая выборка кода процесса для анализа. Признаком окончания анализа в устройстве является формирование сигнала на последнем выходе распределителя 10 импульсов. Этот сигнал поступает на входы элементов И 22 и 23, выходные сигналы которых зависят от состояния триггера 5. Если триггер 5 находится в единичном состоянии, то срабатывает элемент И 22, с выхода которого сигнал поступает на вход установки в нуль триггера 5 и на вход элемента ИЛИ 26 для начала нового цикла анализа оставшихся процессов. Такие циклы выполняются до выработки сигнала на выходе устройства или пока все регистры обоих блоков не будут установлены в нуль.

Если же триггер 5 находится в нулевом состоянии, т.е. в процессе сравнения кодов всех владельцев с кодами процессов, которые выдали запросы на ресурсы, не произошло ни одного вычеркивания процессов из списков, то сигнал с выхода элемента И 23 устанавливает в единичное состояние триггер 6. Кроме того, в зависимости от сигнала, подаваемого с выхода элемента И-НЕ 9 на вход элемента И 24, триггер 7 устанавливается в соответствующее состояние (установка триггера 7 в единичное состояние означает, что система находится в тупике). Тем же сигналом с выхода триггера 6 устанавливается в нулевое состояние триггер 3. При этом схема И 50 по единичному сигналу триггера тупика 7 разрешает прохождение тактовых сигналов на вход счетчика 49, по которым в соответствии с его значениями, являющимися адресами данных в буферной памяти, схемами управления 48 осуществляется запись информации о тупиковой ситуации.

На этом завершается процесс анализа и разрешается запись новой информации в регистры контроллера, во время которой с выхода буферной памяти 47 через вход приемопередатчика 45 проводится считывание информации о тупиковой ситуации, что является выходом устройства. На этом процедура контроля распределения ресурсов прекращается.

Покажем возможность осуществления изобретения, то есть возможность его промышленного применения. Все используемые в устройстве элементы (счетчики, регистры, логические схемы И, НЕ, ИЛИ, И-НЕ, ИЛИ-НЕ, триггеры, распределители импульсов, мультиплексоры, микросхемы буферной памяти со схемами управления записью-считыванием, ключи, схемы сравнения) являются стандартными изделиями цифровой техники, и их назначение и характеристики описаны во многих справочниках, например в (Д8), а также в справочнике «Аналоговые и цифровые интегральные микросхемы». Справочник. Якубовский С.В., Кулешова В.И., Ниссельсон Л.И. и др., под ред. Якубовского С.В., М., Радио и связь, 495 стр. - (Д9). Используемые в интерфейсной части универсальные асинхронные приемопередатчиками построены на основе интегральных микросхем 16550 UART, разработанных корпорацией National Semiconductor (англ. universal asynchronous receiver/transmitter), для организации связи посредством реализации последовательного интерфейса. Информация об интегральных микросхемах помещена, например, на сайте http://ru.wikipedia.org/wiki/16550_UART - (Д10).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля распределения ресурсов | 1986 |

|

SU1341642A1 |

| Устройство контроля | 1981 |

|

SU1015385A1 |

| Устройство для контроля распределения ресурсов | 1985 |

|

SU1297051A1 |

| Устройство для синхронизации распределенной вычислительной системы | 1988 |

|

SU1508201A1 |

| Микропроцессорное устройство обработки данных | 1982 |

|

SU1291999A1 |

| Устройство для контроля распределения ресурсов | 1987 |

|

SU1509898A1 |

| Устройство для контроля распределения ресурсов в вычислительной системе | 1985 |

|

SU1312583A1 |

| Устройство для контроля распределения ресурсов | 1984 |

|

SU1215112A1 |

| Устройство для контроля распределения ресурсов | 1989 |

|

SU1702372A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1983 |

|

SU1140125A1 |

Изобретение относится к области вычислительной техники и может быть использовано в сетевых системах обеспечения управления объектами экономики, топливно-энергетического комплекса, транспорта, связи, энергетики, сельского хозяйства, промышленности, космонавтики и в других областях. Техническим результатом является сокращение временных потерь на ожидание выделения требуемых системных ресурсов, а также повышение оперативности и готовности устройства к работе. В контроллер распределения ресурсов введены буферная память, содержащая схемы управления, схему И, счетчик, и интерфейсная часть устройства, содержащая два стандартных разъема СОМ-портов, две группы элементов И, два распределителя импульсов, три схемы И, два инвертора НЕ и два универсальных асинхронных приемопередатчика, электрически соединенных таким образом, что обеспечивается прием входной информации и фиксация моментов времени начала и окончания приема устройством информации, после чего в автоматическом режиме осуществляется перевод работы устройства в режим контроля и запуск процедуры выполнения контроля распределения ресурсов с последующей записью информации о тупиках в буферной памяти устройства и ее считыванием через первый приемопередатчик в управляющий компьютер или в локальную сеть. 3 ил.

Контроллер распределения ресурсов, содержащий две группы регистров, триггер режима, два триггера управления, триггеры анализа и тупика, три группы элементов И, элемент И-НЕ, распределитель импульсов, мультиплексор, первую схему сравнения, две группы ключей, семь элементов И, первый элемент ИЛИ и элемент ИЛИ-НЕ, третью группу ключей, второй элемент ИЛИ, (n-1) схему сравнения, причем информационный вход р-го регистра первой группы (р=1,…n, где n - число ресурсов в системе) соединен с выходом р-го ключа первой группы, информационный вход р-го регистра второй группы соединен с выходом р-го ключа второй группы, первый вход сброса р-го регистра первой группы подключен к выходу р-го элемента И третьей группы, второй вход сброса р-го регистра первой группы подключен к выходу р-го элемента И второй группы, вход сброса р-го- регистра второй группы подключен к выходу р-го элемента И первой группы, выходы р-го регистра первой группы соединены с соответствующими инверсными входами р-го элемента И первой группы и с р-ми информационными входами мультиплексора, выходы р-го регистра второй группы соединены с соответствующими инверсными входами р-го элемента И второй группы, входы установки и сброса триггера режима соединены с входом пуска устройства и с выходом триггера анализа соответственно, инверсный выход триггера режима соединен с управляющими входами ключей первой и второй групп и с соответствующими инверсными входами элементов И первой и второй групп, входы установки и синхронизации первого триггера управления подключены к выходам первого элемента ИЛИ и второго элемента И соответственно, входы установки и сброса второго триггера управления соединены с выходом седьмого и четвертого элементов И соответственно, прямой и инверсный выходы второго триггера управления подключены к первым входам четвертого и пятого элементов И соответственно, выход пятого элемента И соединен с входом установки триггера анализа, вход сброса которого соединен с входом сброса триггера тупика и с входом пуска устройства, выход триггера анализа соединен с первым входом шестого элемента И, выход которого подключен к входу установки триггера тупика, выход которого соединен с выходом признака тупиковой ситуации устройства, выходы элементов И первой группы соединены с входами элемента И-НЕ, выход которого соединен с вторым входом шестого элемента И, тактовый вход распределителя импульсов подключен к выходу второго элемента И, выходы распределителя импульсов подключены к входам элемента ИЛИ-НЕ, к управляющим входам мультиплексора и к первым входам соответствующих элементов И третьей группы, выход признака окончания цикла распределителя импульсов соединен с вторыми входами четвертого и пятого элементов И, выходы мультиплексора соединены с первыми информационными входами первой схемы сравнения и с инверсными входами третьего элемента И, информационные входы ключей первой и второй групп образуют входы номеров процессов, соответственно владеющих и запрашивающих ресурсы устройства, вторые входы элементов И третьей группы соединены с выходом седьмого элемента И, первый и второй инверсные входы первого элемента И подключены к выходам третьего элемента И и элемента ИЛИ-НЕ соответственно, второй вход второго элемента И подключен к входу тактовых импульсов устройства, выход элемента ИЛИ-НЕ соединен с соответствующим инверсным входом третьего элемента И, выход которого подключен к первому входу первого элемента ИЛИ, выход четвертого элемента И соединен с вторым входом первого элемента ИЛИ, третий вход которого подключен к входу пуска устройства, информационные входы р-го ключа третьей группы объединены с соответствующими выходами р-го регистра второй группы, входы управления ключей третьей группы подключены к выходу первого элемента И, первые информационные входы с второй по n-ю схем сравнения соединены с выходом мультиплексора, выходы р-го ключа третьей группы подключены к соответствующим вторым информационным входам р-й схемы сравнения, выходы признака совпадения всех схем сравнения подключены к соответствующим входам второго элемента ИЛИ, выход которого соединен с четвертым входом первого элемента ИЛИ, выходы признаков несовпадения всех схем сравнения подключены к входам седьмого элемента И, выход которого соединен с пятым входом первого элемента ИЛИ, отличающийся тем, что введены интерфейсная часть и буферная память со схемами управления, схемой И и счетчиком, при этом интерфейсная часть содержит два разъема СОМ-порта, две группы элементов И, два распределителя импульсов, три схемы И, два инвертора НЕ и два универсальных асинхронных приемопередатчика, причем первые входы первой и второй группы элементов И соединены с выходом первого и второго универсального асинхронного приемопередатчика, которые по входу соединены с разъемом первого и второго СОМ-порта соответственно, вторые входы первой и второй группы элементов И соединены с выходами первого и второго распределителя импульсов, выходы признака окончания цикла первого и второго распределителя импульсов заведены на входы первого и второго инвертора и третьей схемы И, выход которой соединен с единичным входом триггера режима, а выход первого и второго инвертора соединены со входом первого и второго СОМ-порта с шиной CTS «Вход - Устройство готово к работе», первые входы первой и второй схемы И соединены с выходом первого и второго СОМ-порта с шиной RTS «Выход - Готовность компьютера к передаче данных», вторые входы первой и второй схемы И соединены с инверсным выходом триггера режима, а буферная память со схемами управления содержит микросхемы памяти и схемы управления записью информации и считыванием, причем по первому входу схемы управления соединены с выходом счетчика, по второму входу схемы управления связаны с инверсным выходом триггера режима, буферная память по входу соединена с выходом группы схем сравнения, а по выходу - со выходом первого универсального асинхронного приемопередатчика, по входу счетчик соединен с выходом схемы И, первый вход которой соединен с выходом триггера тупика, второй вход - с тактовым генератором, при этом информационными входами контроллера распределения ресурсов являются входы универсальных асинхронных приемопередатчиков, а выходом - выход буферной памяти, соединенной с выходом первого универсального асинхронного приемопередатчика.

| Устройство для контроля распределения ресурсов | 1986 |

|

SU1341642A1 |

| Устройство для контроля распределения ресурсов | 1985 |

|

SU1297051A1 |

| Устройство для контроля распределения ресурсов | 1984 |

|

SU1215112A1 |

| Топчак-трактор для канатной вспашки | 1923 |

|

SU2002A1 |

| US 7337446 B2, 26.02.2008 | |||

Авторы

Даты

2014-08-27—Публикация

2013-03-26—Подача