Изобретение относится к вычисли- тельной технике и может быть использовано в системах управления технологическими процессами в различные отраслях народного хозяйства: энергетике, машиностроении, в химической, газовой промьппленности, в экономике, научных экспериментах, информационных системах и т.До

Цель изобретения - расширение функциональных возможностей микропроцессорного устройства обработки данных.

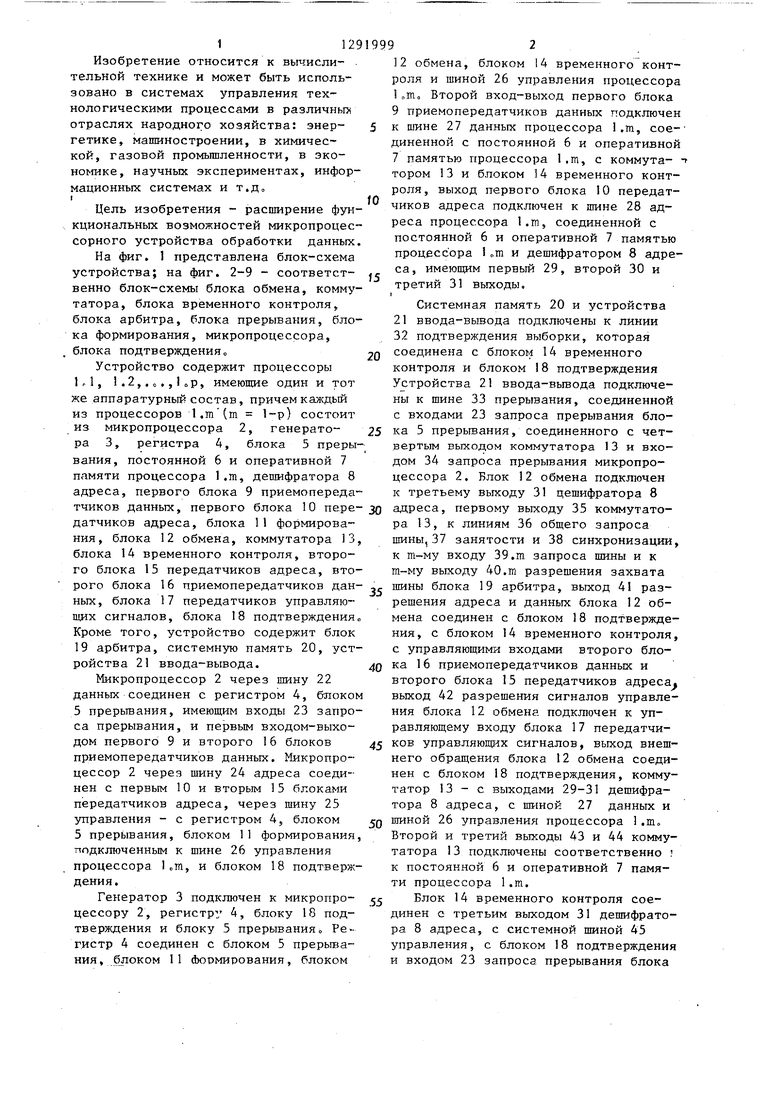

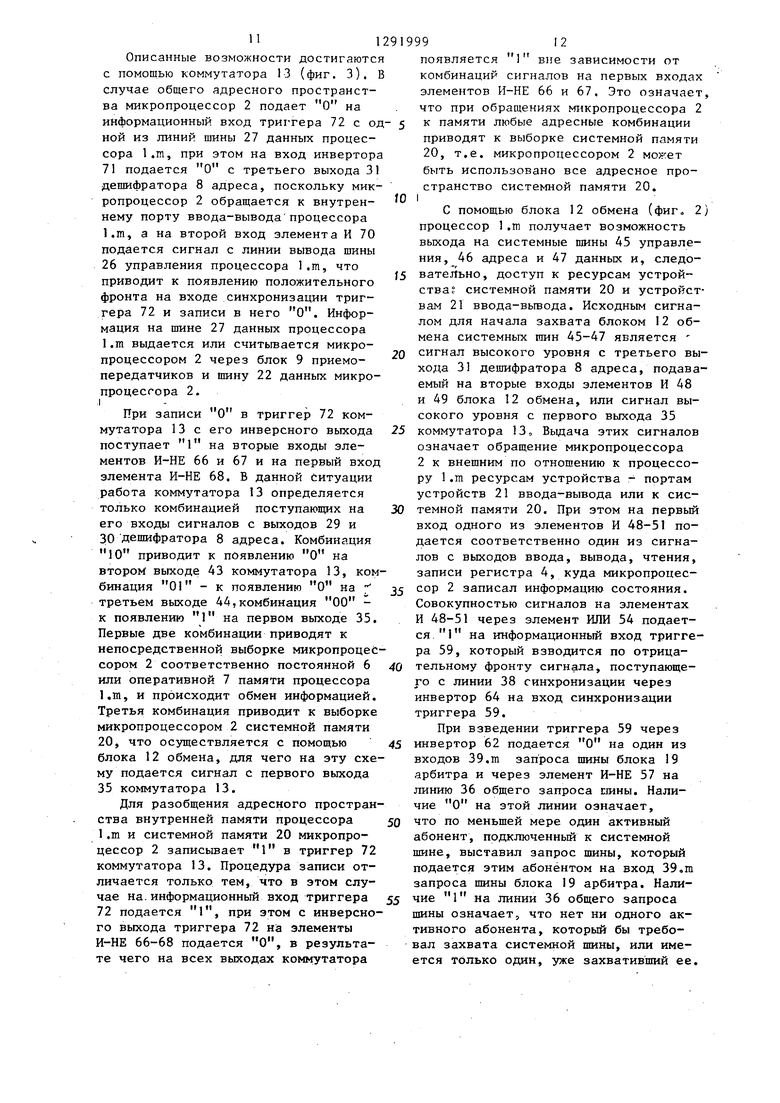

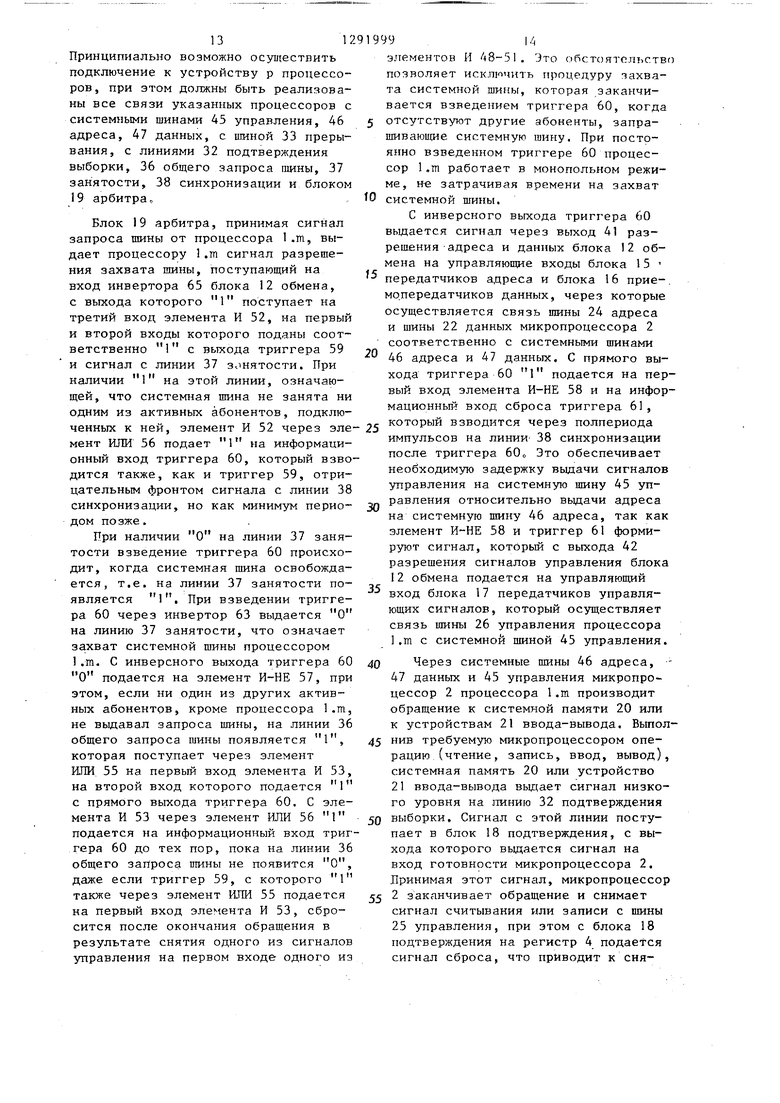

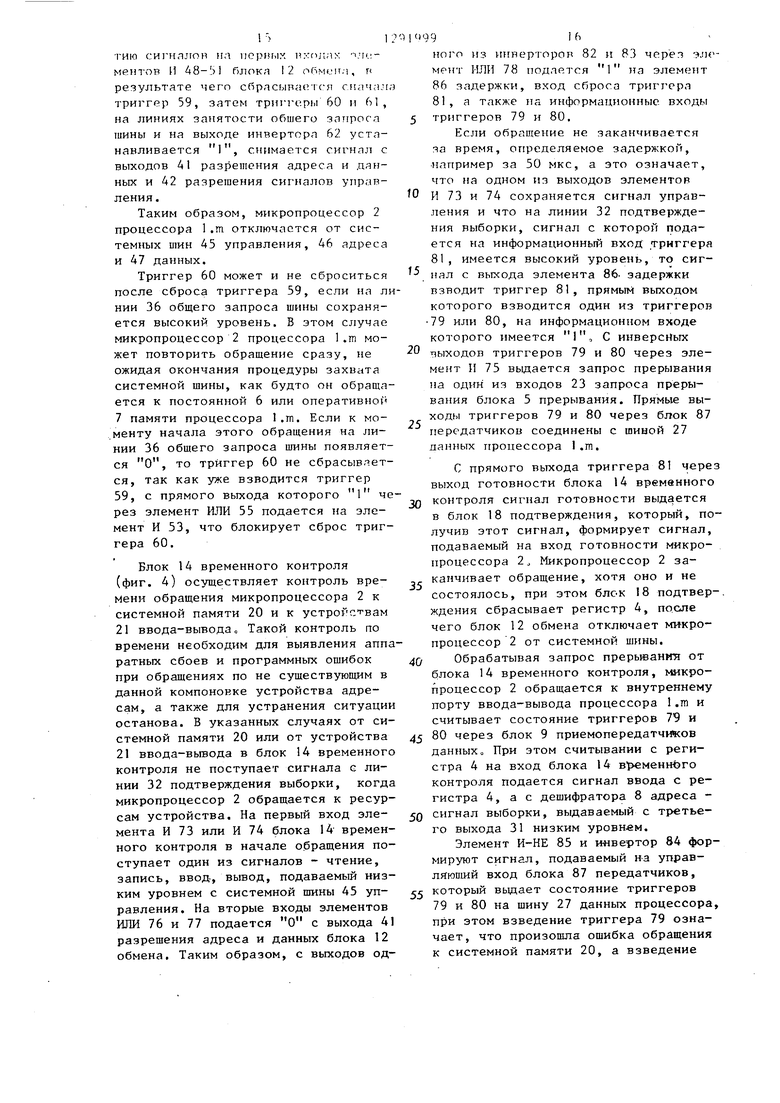

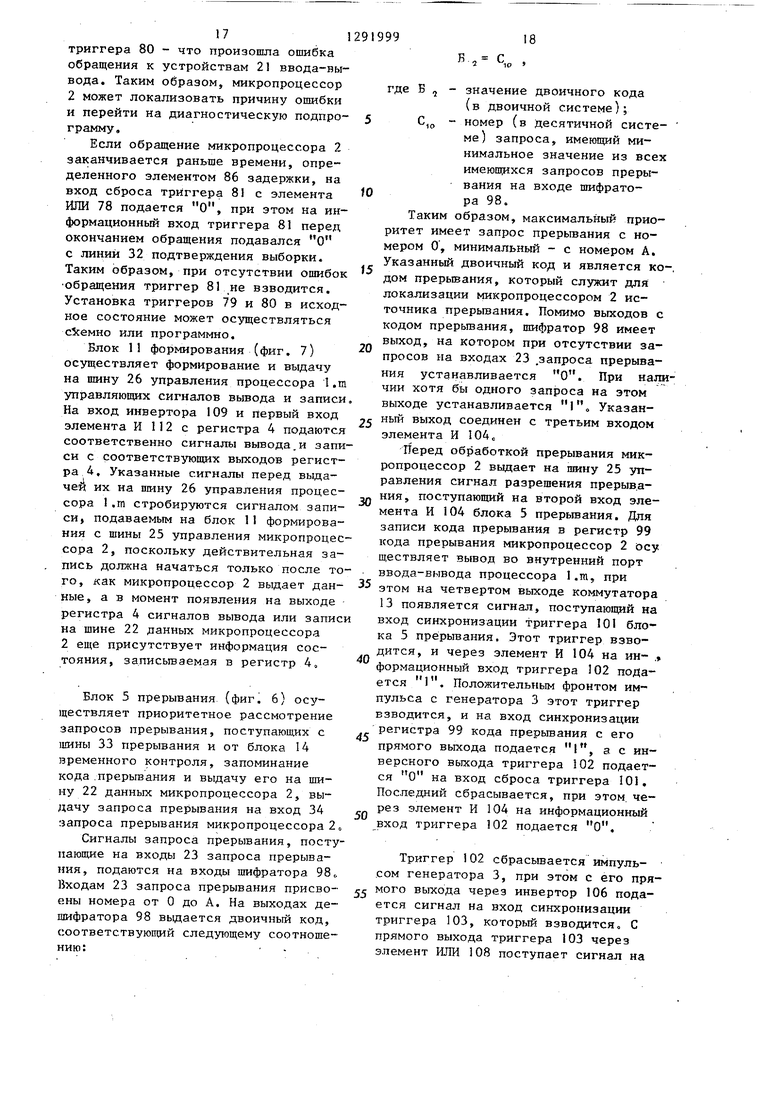

На фиг, 1 представлена блок-схема устройства; на фиг. 2-9 - соответст- венно блок-схемы блока обмена, коммутатора, блока временного контроля, блока арбитра, блока прерывания, блока формирования, микропроцессора, блока подтвержденияо

Устройство содержит процессоры К 1, }.2,.о,,I о р, имеющие один и тот же аппаратурный состав, причем каждый из процессоров l.m (m 1-р) состоит из микропроцессора 2, генератора 3, регистра 4, блока 5 прерывания, постоянной 6 и оперативной 7 памяти процессора 1.т, дешифратора 8

Системная память 20 и устройства 21 ввода-вывода подключены к линии 32 подтверждения выборки, которая соединена с блоком 14 временного контроля и блоком 18 подтверждения Устройства 2 ввода-вьгеода подключены к шине 33 прерывания, соединенной с входами 23 запроса прерывания бло- 25 ка 5 прерьгоания, соединенного с четвертым выходом коммутатора 13 и входом 34 запроса прерывания микропроцессора 2. Блок 12 обмена подключен к третьему выходу 31 дешифратора 8

шины,37 занятости и 38 синхронизации к т-му входу 39.m запроса шины и к т-му выходу 40.ш разрешения захвата

адреса, первого блока 9 приемопередатчиков данных, первого блока 10 пере- зо адреса, первому выходу 35 коммутато- датчиков адреса, блока 11 формирова- ра 13, к линиям 36 общего запроса ния, блока 12 обмена, коммутатора 13, блока 14 временного контроля, второго блока 15 передатчиков адреса, второго блока 16 приемопередатчиков дан- , шины блока 19 арбитра, выход 41 разных, блока 17 передатчиков управляю- решения адреса и данных блока 12 об- сигналов, блока 18 подтверждения. Кроме того, устройство содержит блок 19 арбитра, системную память 20, устройства 21 ввода-вывода.

Микропроцессор 2 через шину 22

мена соединен с блоком 18 подтверждения, с блоком 14 временного контроля с управляющими входами второго бло- 40 ка 16 приемопередатчиков данных и второго блока 15 передатчиков адреса

данных соединен с регистром 4, блоко 5 прерьгаания, имеющим входы 23 запроса прерывания, и первым входом-выходом первого 9 и второго 16 блоков приемопередатчиков данных. Микропроцессор 2 через шину 24 адреса соединен с первым 10 и вторым 15 блоками передатчиков адреса, через шину 25 управления - с регистром 4, блоком 5 прерывания, блоком 11 формирования подключенным к шине 26 управления процессора 1 сТп, и блоком 18 подтверждения.

Генератор 3 подключен к микропро- цессору 2, регистру 4, блоку 18 подтверждения и блоку 5 прерывания Регистр 4 соединен с блоком 5 прерьша- ния, ejiOKOM 11 сЬормирования, блоком

12 обмена, блоком 14 временного контроля и шиной 26 управления процессора „Шо Второй вход-выход первого блока 9 приемопередатчиков данных подключен к шине 27 данных процессора 1.т, сое- диненной с постоянной 6 и оперативной 7 памятью процессора 1,т, с коммута- f тором 13 и блоком 14 временного контроля, выход первого блока 10 передатчиков адреса подключен к шине 28 адреса процессора l.m, соединенной с постоянной 6 и оперативной 7 памятью процессора 1«т и дешифратором 8 адреса, имеюш 1;м первый 29, второй 30 и

третий 31 выходы.

I

Системная память 20 и устройства 21 ввода-вывода подключены к линии 32 подтверждения выборки, которая соединена с блоком 14 временного контроля и блоком 18 подтверждения Устройства 2 ввода-вьгеода подключены к шине 33 прерывания, соединенной с входами 23 запроса прерывания бло- ка 5 прерьгоания, соединенного с четвертым выходом коммутатора 13 и входом 34 запроса прерывания микропроцессора 2. Блок 12 обмена подключен к третьему выходу 31 дешифратора 8

адреса, первому выходу 35 коммутато- ра 13, к линиям 36 общего запроса шины блока 19 арбитра, выход 41 разрешения адреса и данных блока 12 об-

шины,37 занятости и 38 синхронизации, к т-му входу 39.m запроса шины и к т-му выходу 40.ш разрешения захвата

адреса, первому выходу 35 коммутато- ра 13, к линиям 36 общего запроса шины блока 19 арбитра, выход 41 разрешения адреса и данных блока 12 об-

адреса, первому выходу 35 коммутато- ра 13, к линиям 36 общего запроса шины блока 19 арбитра, выход 41 разрешения адреса и данных блока 12 об-

мена соединен с блоком 18 подтверждения, с блоком 14 временного контроля, с управляющими входами второго бло- ка 16 приемопередатчиков данных и второго блока 15 передатчиков адреса

выход 42 разрешения сигналов управления блока 12 обмена подключен к управляющему входу блока 17 передатчиков управляюшз х сигналов, выход внешнего обращения блока 12 обмена соединен с блоком 18 подтверждения, коммутатор 13 - с выходами 29-31 дешифратора 8 адреса, с шиной 27 данных и

шиной 26 управления процессора 1.т. Второй и третий выходы 43 и 44 коммутатора 13 подключены соответственно к постоянной 6 и оперативной 7 памяти процессора l.m.

Блок 14 временного контроля соединен с третьим выходом 31 дешифратора 8 адреса, с системной шиной 45 управления, с блоком 18 подтверждения и входом 23 запроса прерывания блока

.129

5 прерывания. Выход второго блокп 15 передатчиков адреса подключен к системной шине Д6 адреса, второй вход- выход второго блока 16 приемопередатчиков данных - к системной шнне 47 данных, вход блока 17 передатчиков управляющих сигналов - к пгине 26 управления процессора 1.т, а выходы ввода, вывода, чтения и записи блока 17 передатчиков управляющих сигналов - соот- 10 триггера 60. Прямой выход триггера

ветственно к линиям системной шины 45 управления. Блок 18 подтверждения подключен к регистру 4 и микропроцессору 2, блок 9 арбитра - к линиям 37 занятости и 38 синхронизации, систем- t5 ная память 20 и устройства 21 ввода- вьгоода - к системным шинам 46 адреса, 47 данных и 45 управления.

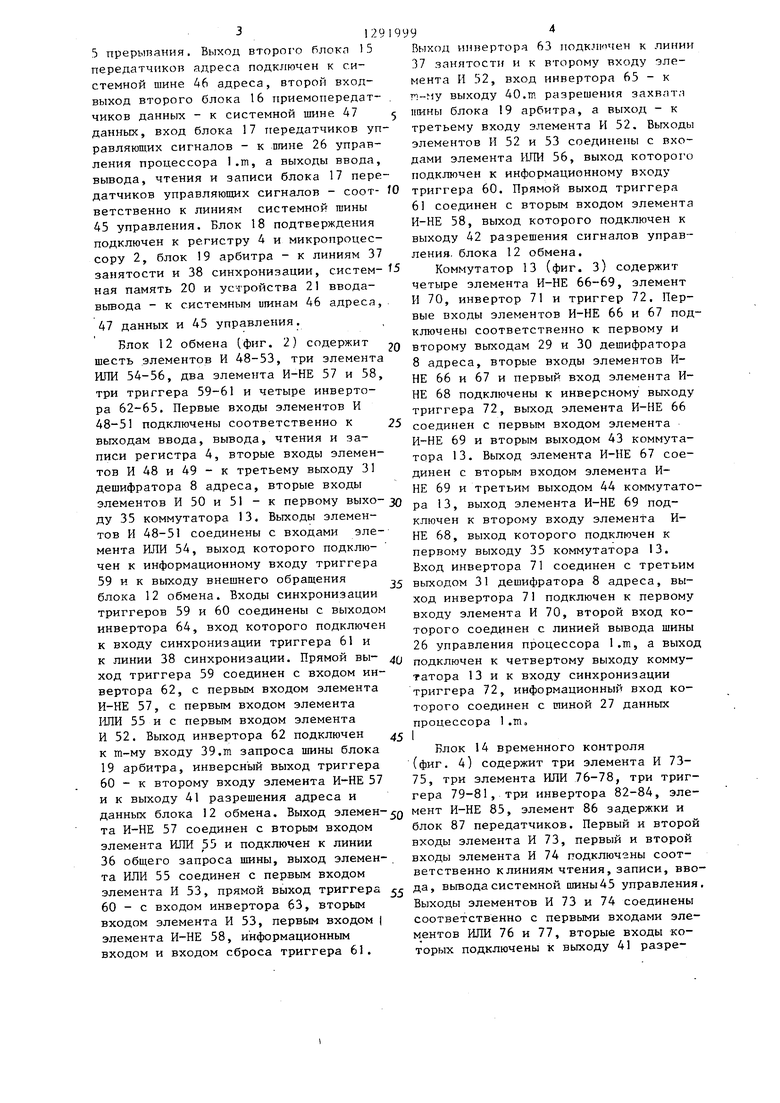

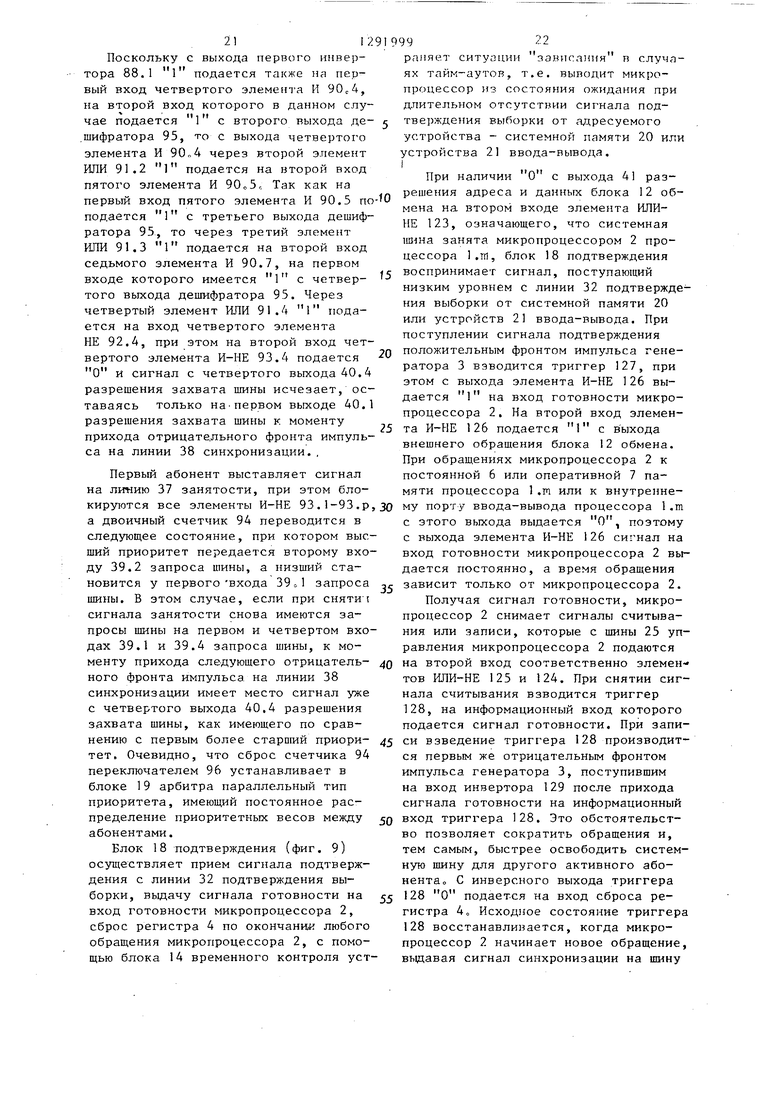

Блок 12 обмена (фиг. 2) содержит л шесть элементов И 48-53, три элемента ИЛИ 54-56, два элемента И-НЕ 57 и 58, три триггера 59-61 и четыре инвертора 62-65. Первые входы элементов И 48-51 подключены соответственно к 25 выходам ввода, вывода, чтения и записи регистра 4, вторые входы элементов И 48 и 49 - к третьему выходу 31 дешифратора 8 адреса, вторые входы

элементов И 50 и 51 - к первому выхо-зо ра 13, выход элемента И-НЕ 69 под- ду 35 коммутатора 13. Выходы элемен61 соединен с вторым входом элемен И-НЕ 58, выход которого подключен выходу 42 разрешения сигналов упра ления, блока 12 обмена.

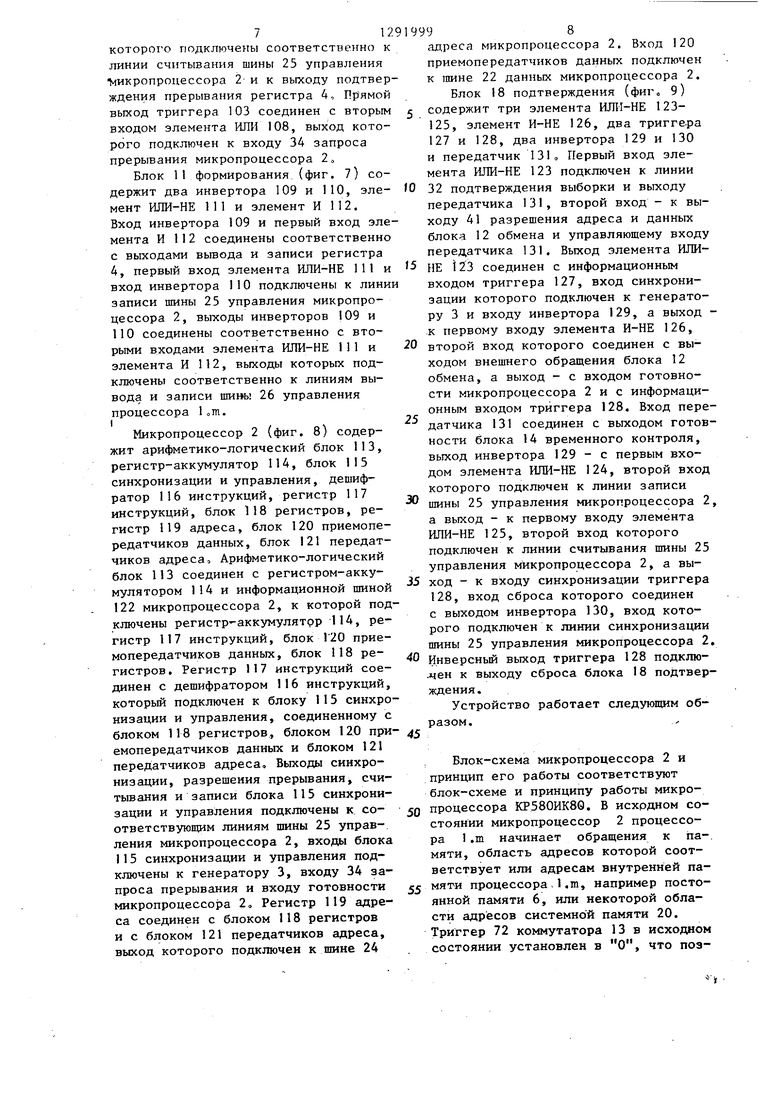

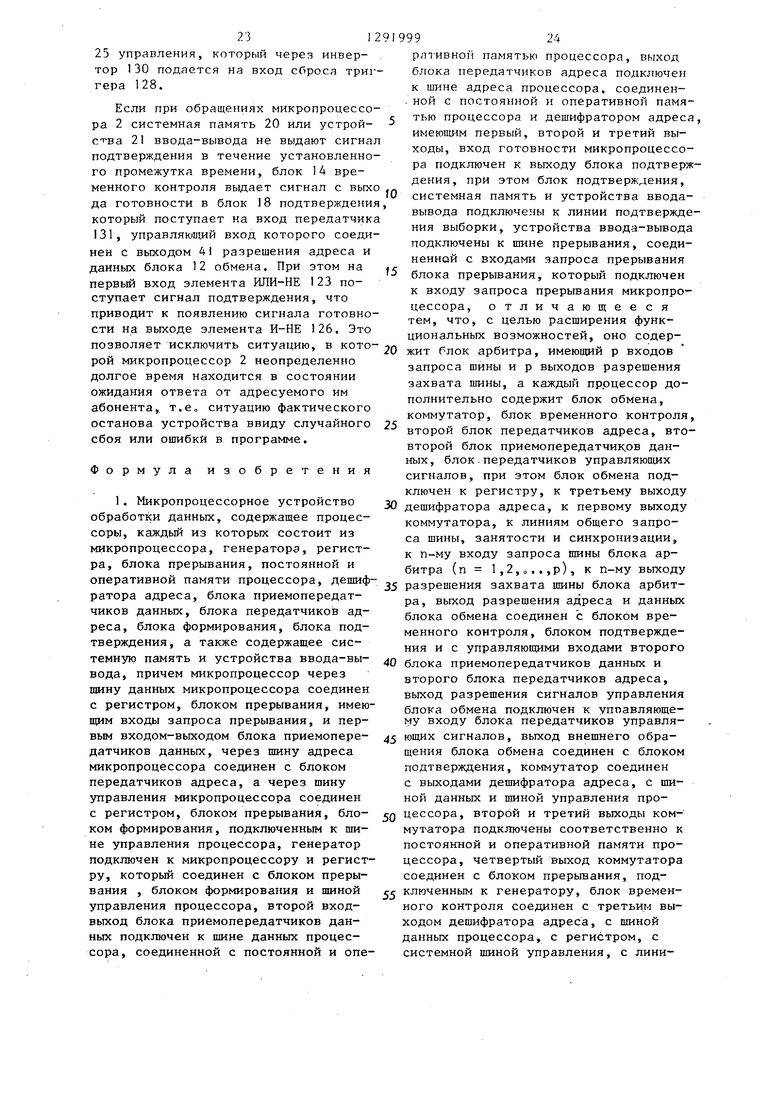

Коммутатор 13 (фиг. З) содержит четыре элемента И-НЕ 66-69, элемен И 70, инвертор 71 и триггер 72. Пе вые входы элементов И-НЕ 66 и 67 п ключены соответственно к первому и второму выходам 29 и 30 дешифратор 8 адреса, вторые входы элементов И НЕ 66 и 67 и первый вход элемента НЕ 68 подключены к инверсному выхо триггера 72, выход элемента И-НЕ 6 соединен с первым входом элемента И-НЕ 69 и вторым выходом 43 коммут тора 13. Выход элемента И-НЕ 67 со динен с вторым входом элемента И- НЕ 69 и третьим выходом 44 коммута

ключей к второму входу элемента И- НЕ 68, выход которого подключен к первому выходу 35 коммутатора 13. Вход инвертора 71 соединен с третьи 35 выходом 31 дешифратора 8 адреса, вы ход инвертора 71 подключен к первом входу элемента И 70, второй вход ко торого соединен с линией вывода шин 26 управления процессора I.m, а вых подключен к четвертому выходу комму татора 13 и к входу синхронизации триггера 72, информационный вход ко торого соединен с шиной 27 данных процессора 1.т.

тов И 48-51 соединены с входами элемента ИЛИ 54, выход которого подключен к информационному входу триггера

59и к выходу внешнего обращения блока 12 обмена. Входы синхронизации триггеров 59 и 60 соединены с выходом инвертора 64, вход которого подключен к входу синхронизации триггера 61 и

к линии 38 синхронизации. Прямой вы- ход триггера 59 соединен с входом инвертора 62, с первым входом элемента И-НЕ 57, с первым входом элемента ИЛИ 55 и с первым входом элемента И 52. Выход инвертора 62 подключен к т-му входу 39.m запроса шины блока 19 арбитра, инверсный выход триггера

60- к второму входу элемента И-НЕ 57 и к выходу 41 разрешения адреса и данных блока 12 обмена. Выход элемента И-НЕ 57 соединен с вторым входом элемента ИЛИ 55 и подключен к линии

36 общего запроса шины, выход элемента ИЛИ 55 соединен с первым входом элемента И 53, прямой выход триггера 60 - с входом инвертора 63, вторым входом элемента И 53, первым входом | элемента И-НЕ 58, информационным входом и входом сброса триггера 61.

94

Выход инвертора 63 подкли чен к линии 37 занятости и к второму входу элемента И 52, вход инвертора 65 - к п-му выходу 40.m разрешения захватя

пины блока 19 арбитра, а выход - к третьему входу элемента И 52. Выходы элементов И 52 и 53 соединены с входами элемента ИПИ 56, выход которого подключен к информационному входу

ра 13, выход элемента И-НЕ 69 под-

61 соединен с вторым входом элемента И-НЕ 58, выход которого подключен к выходу 42 разрешения сигналов управления, блока 12 обмена.

Коммутатор 13 (фиг. З) содержит четыре элемента И-НЕ 66-69, элемент И 70, инвертор 71 и триггер 72. Первые входы элементов И-НЕ 66 и 67 подключены соответственно к первому и второму выходам 29 и 30 дешифратора 8 адреса, вторые входы элементов И- НЕ 66 и 67 и первый вход элемента И- НЕ 68 подключены к инверсному выходу триггера 72, выход элемента И-НЕ 66 соединен с первым входом элемента И-НЕ 69 и вторым выходом 43 коммутатора 13. Выход элемента И-НЕ 67 соединен с вторым входом элемента И- НЕ 69 и третьим выходом 44 коммутатора 13, выход элемента И-НЕ 69 под-

ключей к второму входу элемента И- НЕ 68, выход которого подключен к первому выходу 35 коммутатора 13. Вход инвертора 71 соединен с третьим выходом 31 дешифратора 8 адреса, выход инвертора 71 подключен к первому входу элемента И 70, второй вход которого соединен с линией вывода шины 26 управления процессора I.m, а выход подключен к четвертому выходу коммутатора 13 и к входу синхронизации триггера 72, информационный вход которого соединен с шиной 27 данных процессора 1.т.

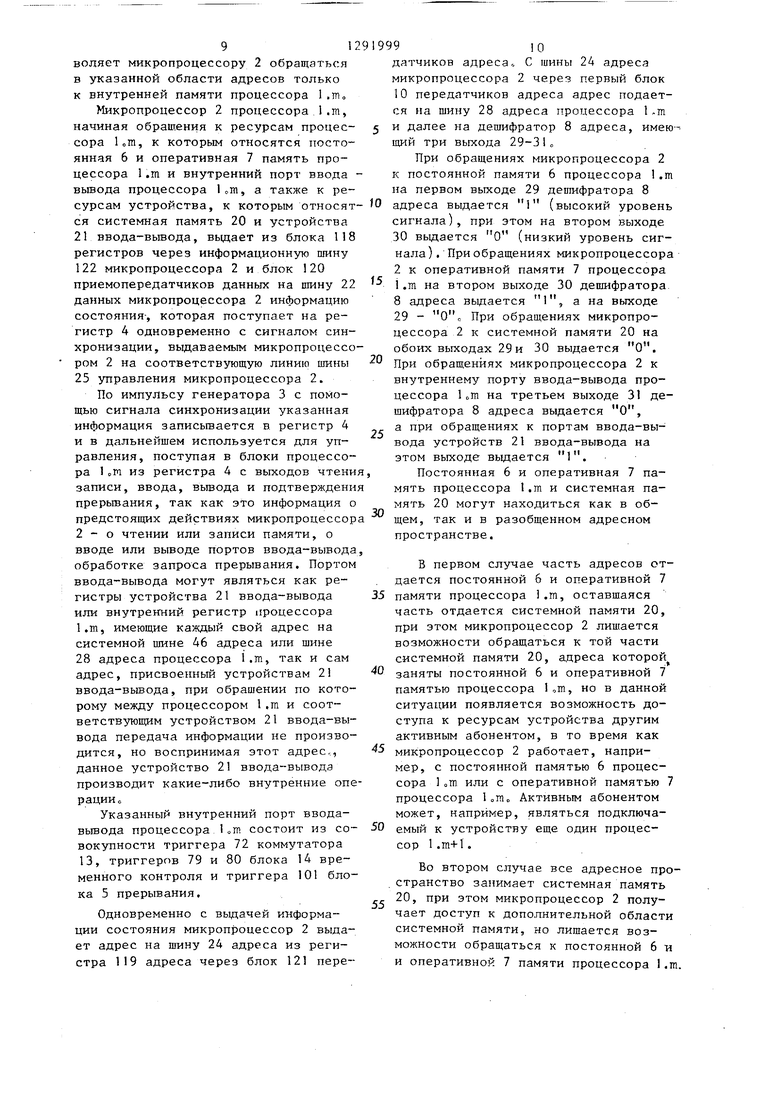

Блок 14 временного контроля (фиг. 4) содержит три элемента И 73- 75, три элемента ИЛИ 76-78, три триггера 79-81, три инвертора 82-84, элемент И-НЕ 85, элемент 86 задержки и блок 87 передатчиков. Первый и второй входы элемента И 73, первый и второй входы элемента И 74 подключены соответственно клиниям чтения, записи, ввода, вывода системной шины 4 5 управления. Выходы элементов И 73 и 74 соединены соответственно с первыми входами эле- м ентов ИЛИ 76 и 77, вторые входы которых подключены к выходу 41 разре512

шения адреса и данных блока 12 обмена. Выходы элементов ИЛИ 76 и 77 соединены соответственно с входами инверторов 82 и 83, выход инвертора 82 соединен с информационны входом - триггера 79 и первым входом элемента ИЛИ 78, а выход инвертора 83 - с информационным входом триггера 80 и BTOipbiM входом элемента ИЛИ 78, выход которого подключен к входу элемента 86 задержки и входу сброса триггера 81. Выход элемента 86 задержки соединен с входом синхронизации триггера 81, информационный вход которого подключен к линии 32 подтверждения выборки Прямой выход триггера 81 соединен с выходом готовности блока 14 временного контроля и с входами синхронизации триггеров 79 и 80- прямые выходы которых подключены к входам блока 87 передатчиков, а инверсные выходы соединены с входами элемента И 75, выход которого подключен к входу 23 запроса прерывания блока 5 прерьшания. Первый и второй входы элемента И-НЕ 85 подключены соответственно к выходу ввода регистра 4 и выходу инвертора 84, вход которого подключен к третьему выходу 31 дешифратора 8 адреса. Выход элемента И- НЕ 85 соединен с управляющим входом блока 87 передатчиков, выход которого подключен к шине 27. данных процессора 1 .т.

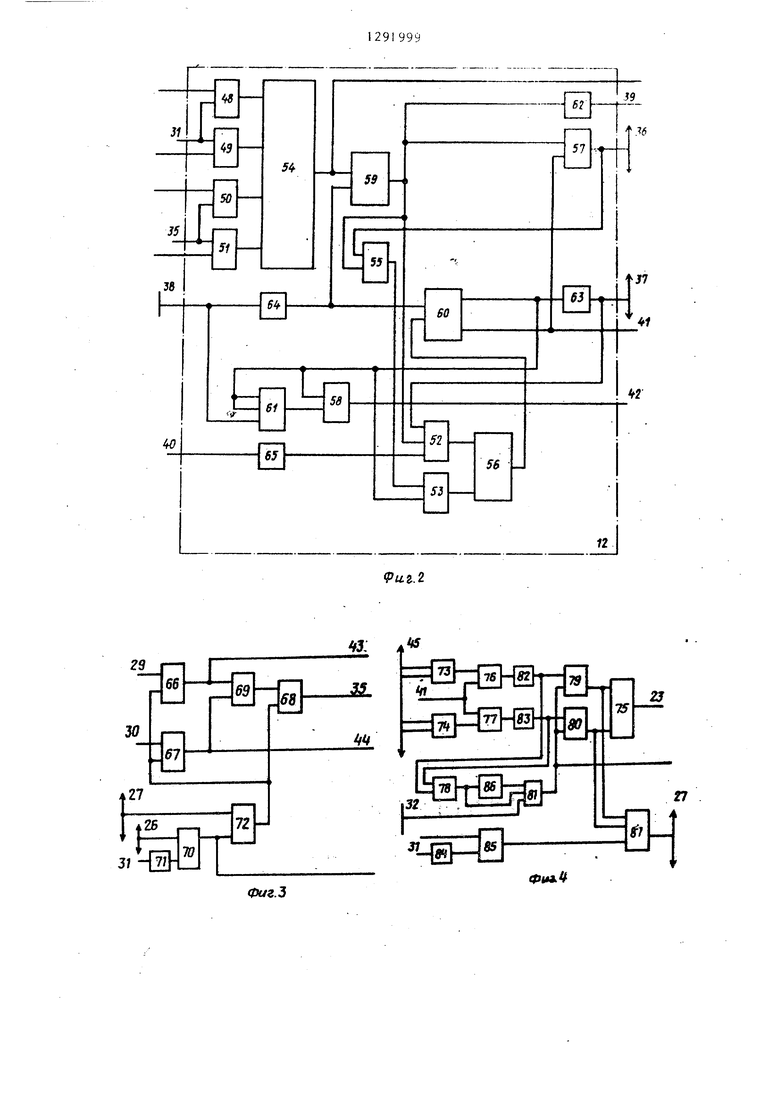

Блок 19 арбитра (фиг, 5) содержит- р (р 4) инверторов 88.1-88.р, инвертор 89, 2р элементов И 90.1-90.2р, р элементов ИЛИ 91.1-91.р, НЕ 92.1- 92.р, И-НЕ 93.1-93.Р, двоичный счетчик 94, дешифратор 95, переключатель 96 и генератор 97, Входы каждого из р инверторов 88.1-88.Р соединены с входами 39.1-39.р запроса пшны блока 19 арбитра, выход каждого п-го инвертора 88.п (п 1,2,..о, р-1) соединен с первым входом п-го элемента И-НЕ 93.п и первым входом (2п + )-го элемента И 90.2п+1. Выход р-го инвертора 88.р соединен с первым входом р-го элемента И-НЕ 93.р и с первым входом первого элемента И 90„1. Выход каждого п-го элемента ИЛИ 91.П соединен с вторым входом (2п+2)-го элемента И 90.2п+2 и с входом п-го элемента 92,п. Выход р-го элемента ИЛИ 91.р соединен с вторым входом второго элемента И И 90.2 и входом р-го элемента НЕ 92.

96

второй вход (21-1)-го и первый вход 2i-ro (i 1,2,,,,,р) элементов И 90.2i-l и 90.21 подключены к 1-му выходу дешифратора 95, выходы (211)-гй и 21-го элементов И 90.21-1 и 90.21 подключены к входам 1-го элемента ИЛИ 91 „1. Выход каждого 1-го элемента НЕ 92„1 соединен с вторым входом 1-го элемента И-НЕ 93.1,

третий вход элементов И-НЕ 93.1-93.р подключен к линии 37 занятости и входу инвертора 89. Выходы элементов И-НЕ 93(,1-93.,р подключены к выходам 40.1-40.р разрешения захвата шины

блока 19 арбитра. Счетный вход и вход сброса двоичного счетчика 94 подключены соответственно к выходам инвертора 89 и переключателя 96, а выходы двоичного счетчика 94 - к

дешифратору 95. Выход генератора 97

соединен с линией 38 синхронизации.

I

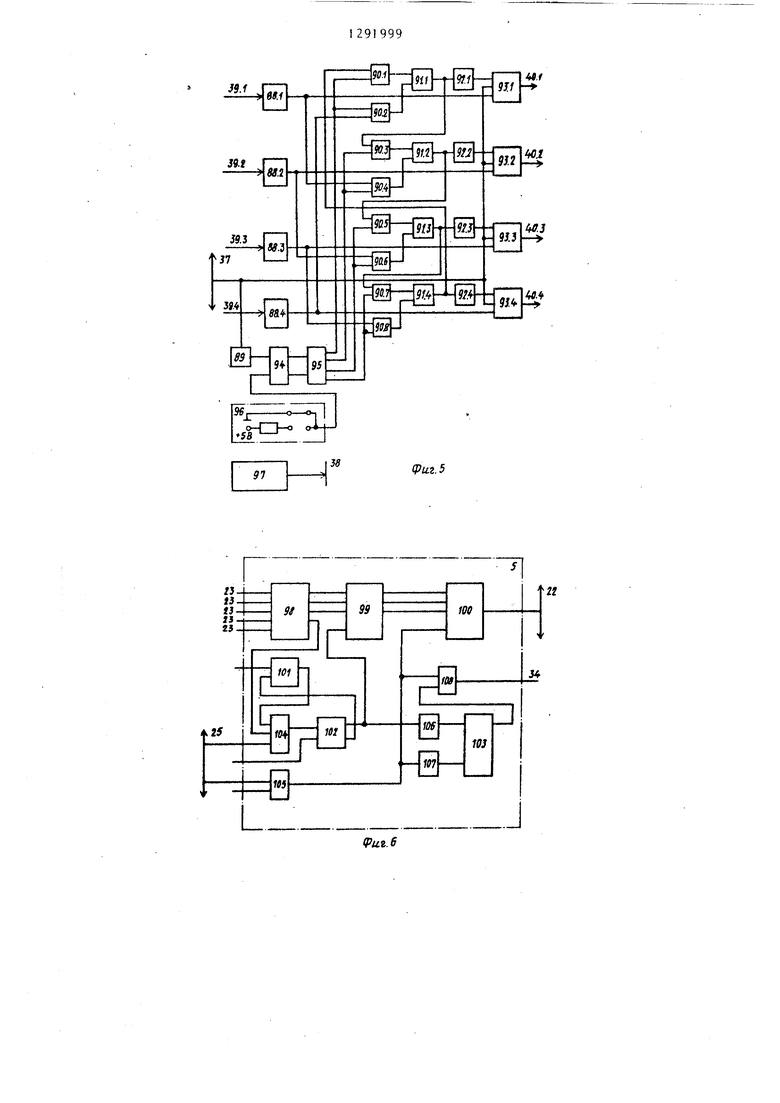

БЛОК 5 прерывания (фиг. 6) содержит шифратор 98, регистр 99 кода пре- рывания, блок 100 передатчиков, три триггера 101-103, два элемента И 104 и 105, два инвертора 106 и 107 и элемент ИЛИ 108, Входы шифратора 98 подключены к входам 23 запроса пре- рьгоания блока 5 прерьшания, выходы шифратора 98 соединены с третьим входом первого элемента И и с информационными входами регистра 99 кода прерывания, выходы которого.соединены с блоком 100 передатчиков, подключенным к ш;ине 22 данных микропроцессора 2. Вход синхронизации триггера 101 соединен с четвертым выходом коммутатора 13, а прямой выход триггера 101 - с первым входом эле- « мента И 104, второй вход которого подключен к линии разрешения прерьшания шины 25 управления микропроцессора 2, а выход - к информационному входу триггера 102. Вход синхронизации второго триггера подключен к генератору Зо Прямой выход триггера 102 соединен с входом синхронизации регистра 99 кода прерывания и входом инвертора 106,, выход которого соединен с входом синхронизации триггера 103. Инверсный выход триггера 102 подключен к входу сброса триггера 101, вход сброса триггера 103 соеди- нен с выходом инвертора Ю7, вход которого соединен с первым входом элемента ИЛИ 108, с управляющим входом блока 100 передатчиков и выходом элемента И 105, первый и второй входы

которого подключены соответстненно к линии считывания шины 25 управления Т икропроцессора 2 и к выходу подтверждения прерывания регистра 4, Прямой выход триггера 103 соединен с вторым входом элемента ИЛИ 108, выход которого подключен к входу 34 запроса прерывания микропроцессора 2

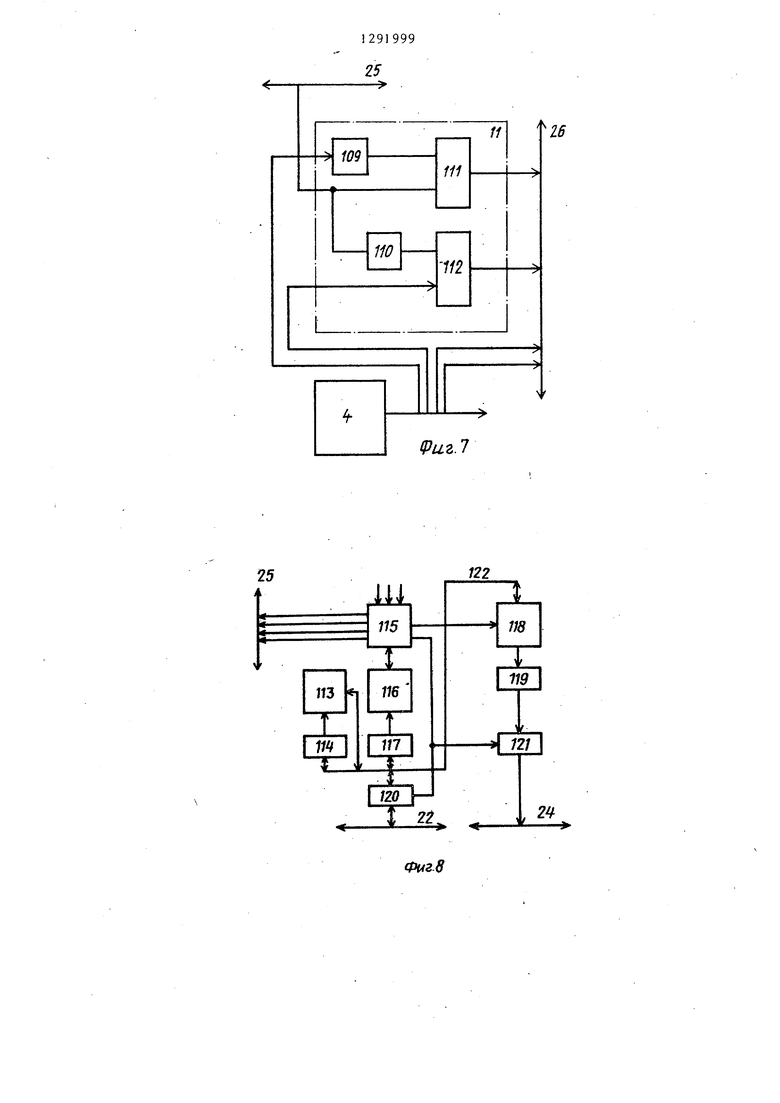

Блок 11 формирования (фиг. 7) содержит два инвертора 109 и 110, эле- О мент ИЛИ-НЕ 111 и элемент И 112. Вход инвертора 109 и первый вход элемента И 112 соединены соответственно с выходами вьгеода и записи регистра

адреса микропроцессора 2. Вход 120 приемопередатчиков данных подключен к ншне 22 данных микропроцессора 2.

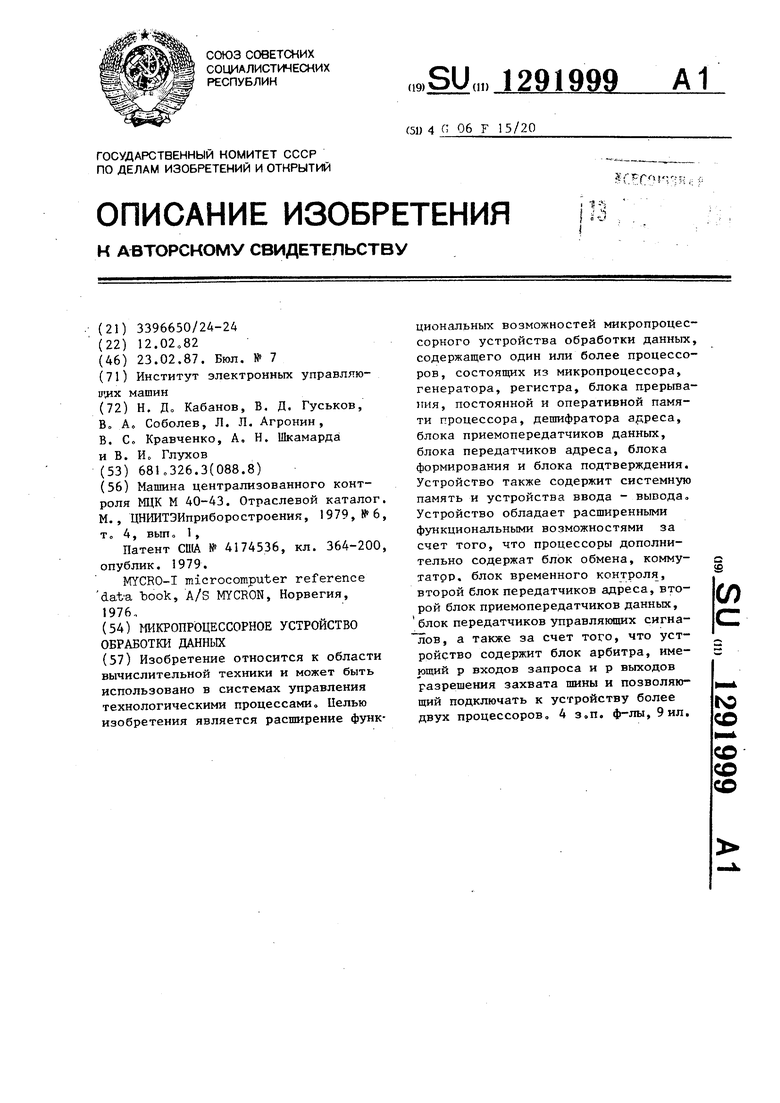

Блок 18 подтверждения (фиг, 9) содержит три элемента ИЛ11-НЕ 123- 125, элемент И-НЕ 126, два триггера 127 и 128, два инвертора 129 и 130 и передатчик 131, Первый вход элемента ИЛИ-НЕ 123 подключен к линии 32 подтверждения выборки и выходу передатчика 131, второй вход - к вы ходу 41 разрешения адреса и данных блока 12 обмена и управляющему вход передатчика 131. Выход элемента ИЛИ

4, первый вход элемента ИЛИ-НЕ 111 и 5 ЦЕ 123 соединен с информационным вход инвертора I10 подключены к линии входом триггера 127, вход синхрони- записи шины 25 управления микропрозации которого подключен к генератору 3 и входу инвертора 129, а выход к первому входу элемента И-НЕ 126, второй вход которого соединен с выходом внешнего обращения блока 12 обмена, а выход - с входом готовности микропроцессора 2 и с информационным входом триггера 128. Вход пере датчика 131 соединен с выходом готов ности блока 14 временного контроля, выход инвертора 129 - с первым входом элемента ИЛИ-НЕ 124, второй вход которого подключен к линии записи шины 25 управления микропроцессора 2 а выход - к первому входу элемента ИЛИ-НЕ 125, второй вход которого подключен к линии считывания шины 25 управления микропроцессора 2, а выцессора 2, выходы инверторов 109 и 110 соединены соответственно с вторыми входами элемента ИЛИ-НЕ 111 и элемента И 112, выходы которых подключены соответственно к линиям вывода и записи шины 26 управления процессора 1„т.

25

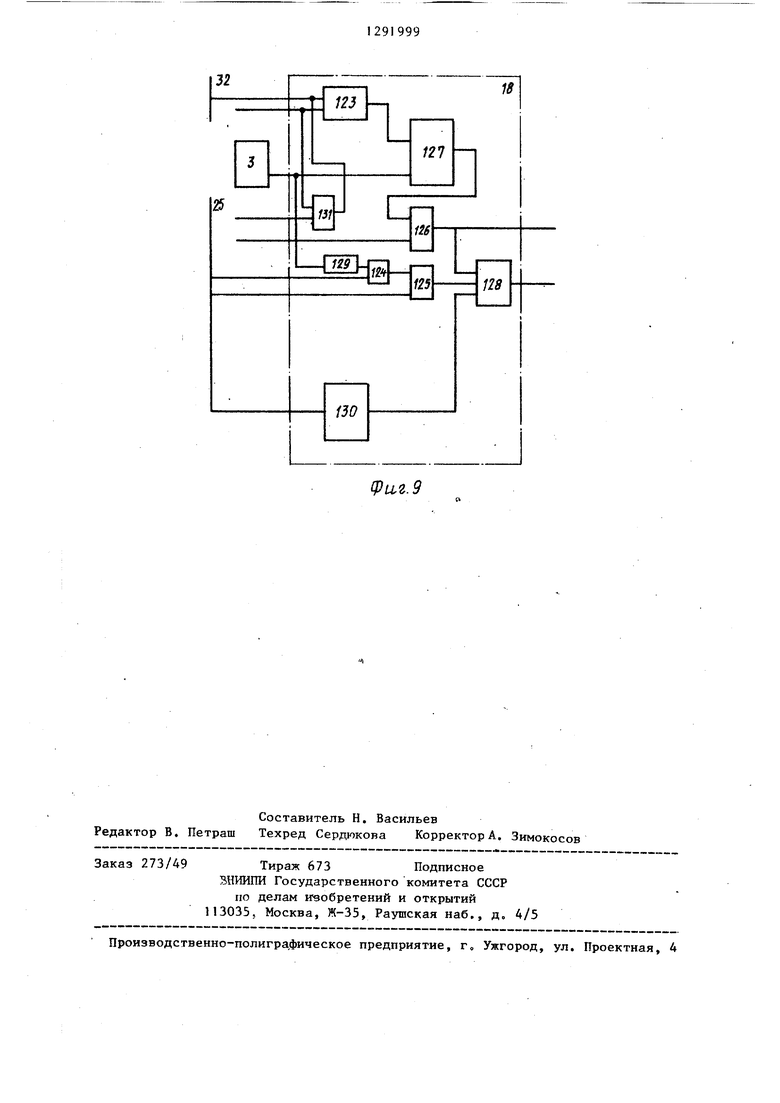

зации которого подключен к генератору 3 и входу инвертора 129, а выход - к первому входу элемента И-НЕ 126, второй вход которого соединен с выходом внешнего обращения блока 12 обмена, а выход - с входом готовности микропроцессора 2 и с информационным входом триггера 128. Вход передатчика 131 соединен с выходом готовности блока 14 временного контроля, выход инвертора 129 - с первым входом элемента ИЛИ-НЕ 124, второй вход которого подключен к линии записи шины 25 управления микропроцессора 2, а выход - к первому входу элемента ИЛИ-НЕ 125, второй вход которого подключен к линии считывания шины 25 управления микропроцессора 2, а выМикропроцессор 2 (фиг. 8) содержит арифметико-логический блок 113, регистр-аккумулятор 114, блок 115 синхронизации и управления, дешифратор 116 инструкций, регистр 117 инструкций, блок 118 регистров, регистр 119 адреса, блок 120 приемопередатчиков данных, блок 121 передатчиков адреса Арифметико-логический блок 113 соединен с регистром-аккумулятором 114 и информационной шиной °ДУ синхронизации триггера 122 микропроцессора 2, к которой под- , вход сброса которого соединен ключены регистр-аккумулятрр 114, ре- ходом инвертора 130, вход кото л . - ,.„„ рого подключен к линии синхронизации гистр 117 инструкции, блок 120 прие-

110 шины 25 управления микропроцессора 2, мопередатчиков данных, блок 118 ре-f - ч i

0 Инверсный выход триггера 128 подклю- -чен к выходу сброса блока 18 подтверждения.

гистров. Регистр 117 инструкций соединен с дешифратором 116 инструкций, который подключен к блоку 115 синхронизации и управления, соединенному с блоком 118 регистров, блоком 120 при емопередатчиков данных и блоком 121 передатчиков адреса. Выходы синхронизации, разрешения прерывания считывания и записи блока 115 синхронизации и управления подключены к соответствующим линиям шины 25 управления микропроцессора 2, входы блока 115 синхронизации и управления подключены к генератору 3, входу 34 запроса прерывания и входу готовности микропроцессора 2„ Регистр 119 адреса соединен с блоком 118 регистров

и с блоком 121 передатчиков адреса, выход которого подключен к шине 24

адреса микропроцессора 2. Вход 120 приемопередатчиков данных подключен к ншне 22 данных микропроцессора 2.

Блок 18 подтверждения (фиг, 9) содержит три элемента ИЛ11-НЕ 123- 125, элемент И-НЕ 126, два триггера 127 и 128, два инвертора 129 и 130 и передатчик 131, Первый вход элемента ИЛИ-НЕ 123 подключен к линии 32 подтверждения выборки и выходу передатчика 131, второй вход - к выходу 41 разрешения адреса и данных блока 12 обмена и управляющему входу передатчика 131. Выход элемента ИЛИ 5 ЦЕ 123 соединен с информационным входом триггера 127, вход синхрони-

0

5

зации которого подключен к генератору 3 и входу инвертора 129, а выход - к первому входу элемента И-НЕ 126, второй вход которого соединен с выходом внешнего обращения блока 12 обмена, а выход - с входом готовности микропроцессора 2 и с информационным входом триггера 128. Вход передатчика 131 соединен с выходом готовности блока 14 временного контроля, выход инвертора 129 - с первым входом элемента ИЛИ-НЕ 124, второй вход которого подключен к линии записи шины 25 управления микропроцессора 2, а выход - к первому входу элемента ИЛИ-НЕ 125, второй вход которого подключен к линии считывания шины 25 управления микропроцессора 2, а вы °ДУ синхронизации триггера , вход сброса которого соединен ходом инвертора 130, вход кото шины 25 управления микропроцессора 2, f - ч i

45

0 Инверсный выход триггера 128 подклю- -чен к выходу сброса блока 18 подтверждения.

Устройство работает следующим образом.

Блок-схема микропроцессора 2 и принцип его работы соответствуют блок-схеме и принципу работы микро- процессора КР580ИК80. Б исходном состоянии микропроцессор 2 процессора 1.т начинает обращения к па-, мяти, область адресов которой соот45

ветствует или адресам внутренней па- 55 мяти процессора,1,т, например постоянной памяти 6, или некоторой области адресов системной памяти 20. Триггер 72 коммутатора 13 в исходаом состоянии установлен в О, что позволяет микропроцессору 2 обращаться в указанной области адресов только к внутренней памяти процессора 1.т

Микропроцессор 2 процессора 1.т, начиная обращения к ресурсам процессора Km, к которым относятся постоянная 6 и оперативная 7 память процессора 1.т и внутренний порт ввода вьшода процессора Km, а также к ресурсам устройства, к которым относятся системная память 20 и устройства 21 ввода-вьгоода, выдает из блока 118 регистров через информационную шину 122 микропроцессора 2 и блок 120 приемопередатчиков данных на шину 22 данных микропроцессора 2 информацию состояния-, которая поступает на регистр 4 одновременно с сигналом синхронизации, вьщаваемым микропроцессором 2 на соответствующую линию шины 25 управления микропроцессора 2.

По импульсу генератора 3 с помощью сигнала синхронизации указанная информация записьгоается в регистр 4 и в дальнейшем используется для управления, поступая в блоки процессора Km из регистра 4 с выходов чтени записи, ввода, вьщода и подтверждени прерьгоания, так как это информация о предстоящих действиях микропроцессор 2 - о чтении или записи памяти, о вводе или выводе портов ввода-вывода обработке запроса прерывания. Портом ввода-вывода могут являться как регистры устройства 21 ввода-вывода или внутренний регистр процессора Km, имеющие каждый свой адрес на системной шине 46 адреса или шине 28 адреса процессора Km, так и сам адрес, присвоенный устройствам 2 ввода-вывода, при обрашении по которому между процессором 1.т и соответствующим устройством 21 ввода-вывода передача информации не производится, но воспринимая этот адрес,, данное устройство 21 ввода-вывода производит какие-либо внутренние операции о

Указанный внутренний порт ввода- вьшода процессора Km состоит из совокупности триггера 72 коммутатора 13, триггеров 79 и 80 блока 14 временного контроля и триггера 101 блока 5 прерывания.

Одновременно с выдачей информации состояния микропроцессор 2 выдает адрес на шину 24 адреса из регистра 119 адреса через блок 121 пере

датчиков адреса,, С шины 24 адреса микропроцессора 2 через первый блок 10 передатчиков адреса адрес подается на шину 28 адреса процессора 1-т

и далее на дешифратор 8 адреса, имею-- щий три выхода 29-3 К

При обращениях микропроцессора 2 к постоянной памяти 6 процессора 1.ш на первом выходе 29 дешифратора 8 адреса выдается 1 (высокий уровень сигнала), при этом на втором выходе 30 выдается О (низкий уровень сигнала ). При обращениях микропроцессора 2 к оперативной памяти 7 процессора

.т на втором выходе 30 дешифратора 8 адреса выдается 1, а на выходе 29 - При обращениях микропроцессора 2 к системной памяти 20 на обоих выходах 29и 30 выдается О. При обращениях микропроцессора 2 к внутреннему порту ввода-вывода процессора 1 от на третьем выходе 31 дешифратора 8 адреса выдается О, а при обращениях к портам ввода-вывода устройств 21 ввода-вывода на этом выходе вьщается 1.

Постоянная 6 и оперативная 7 память процессора Km и системная память 20 могут находиться как в общем, так и в разобщенном адресном пространстве.

В первом случае часть адресов отдается постоянной 6 и оперативной 7

памяти процессора 1.т, оставшаяся часть отдается системной памяти 20, при этом микропроцессор 2 лишается возможности обращаться к той части системной памяти 20, адреса которой

заняты постоянной 6 и оперативной 7 памятью процессора Km, но в данной ситуации появляется возможность доступа к ресурсам устройства другим активным абонентом, в то время как

микропроцессор 2 работает, например, с постоянной памятью 6 процессора 1 от или с оперативной памятью 7 процессора Кто Активным абонентом может, например, являться подключаемый к устройству еще один процессор 1.m+I.

Во втором случае все адресное про- . странство занимает системная память 20, при этом микропроцессор 2 получает доступ к дополнительной области системной памяти, но лишается возможности обращаться к постоянной 6 и и оперативной 7 памяти процессора Km.

Описанные возможности достигаются с помощью коммутатора 13 (фиг. 3). В случае общего адресного пространства микропроцессор 2 подает О на информационный вход триггера 72 с од ной из линий шины 27 данных процессора l.m, при этом на вход инвертора

71подается О с третьего выхода 31 дешифратора 8 адреса, поскольку микропроцессор 2 обращается к внутрен- нему порту ввода-вывода процессора l.m, а на второй вход элемента И 70 подается сигнал с линии вывода шины

26 управления процессора 1.т, что приводит к появлению положительного фронта на входе синхронизации триггера 72 и записи в него О. Информация на шине 27 данных процессора 1.т выдается или считьтается микропроцессором 2 через блок 9 приемопередатчиков и шину 22 данных микропроцессора 2. .1 При записи О в триггер 72 коммутатора 13 с его инверсного выхода поступает 1 на вторые входы элементов И-НЕ 66 и 67 и на первый вход элемента И-НЕ 68. В данной Ситуации работа коммутатора 13 определяется только комбинацией поступающих на его входы сигналов с выходов 29 и 30 дешифратора 8 адреса. Комбинация 10 приводит к появлению О на втором выходе 43 коммутатора 13, комбинация 01 - к появлению О на третьем выходе 44,комбинация 00 - к появлению 1 на первом выходе 35. Первые две комбинации приводят к непосредственной выборке микропроцессором 2 соответственно постоянной 6 или оперативной 7 памяти процессора ,ю, и происходит обмен информацией. Третья комбинация приводит к выборке микропроцессором 2 системной памяти 20, что осуществляется с помощью блока 12 обмена, для чего на эту схему подается сигнал с первого выхода 35 коммутатора 13.

Для разобщения адресного пространства внутренней памяти процессора 1.т и системной памяти 20 микропроцессор 2 записывает 1 в триггер 72 коммутатора 13. Процедура записи отличается только тем, что в этом случае на.информационный вход триггера

72подается 1, при этом с инверсного выхода триггера 72 на элементы И-НЕ 66-68 подается О, в результате чего на всех выходах коммутатора

5

0

5

5 0 5

появляется 1 вне зависимости от комбинаций сигналов на первых входах элементов И-НЕ 66 и 67. Это означает, что при обращениях микропроцессора 2 к памяти любые адресные комбинации приводят к выборке системной памяти 20, т.е. микропроцессором 2 может быть использовано все адресное пространство системной памяти 20. I

С помощью блока 12 обмена (фиг 2)

процессор 1.т получает возможность выхода на системные шины 45 управления, 46 адреса и 47 данных и, следовательно, доступ к ресурсам устройства s системной памяти 20 и устройствам 21 ввода-вьшода. Исходным сигналом для начала захвата блоком 12 обмена системных шин 45-47 является сигнал высокого уровня с третьего выхода 31 дешифратора 8 адреса, подаваемый на вторые входы элементов И 48 и 49 блока 12 обмена, или сигнал высокого уровня с первого выхода 35 коммутатора 13, Выдача этих сигналов означает обращение микропроцессора 2 к внешним по отношению к процессору 1.га ресурсам устройства - портам устройств 21 ввода-вывода или к системной памяти 20. При этом на первый вход одного из элементов И 48-51 подается соответственно один из сигналов с выходов ввода, вывода, чтения, записи регистра 4, куда микропроцессор 2 записал информацию состояния. Совокупностью сигналов на элементах И 48-51 через элемент ИЛИ 54 подается. на информационный вход триггера 59, который взводится по отрицательному фронту сигнала, поступающего с линии 38 синхронизации через инвертор 64 на вход синхронизации триггера 59.

При взведении триггера 59 через инвертор 62 подается О на один из входов З9.т запроса щины блока 19 арбитра и через элемент И-НЕ 57 на линию 36 общего запроса сшны. Наличие О на этой линии означает, что по меньшей мере один активный абонент, подключенный к системной шине, выставил запрос шины, который подается этим абонентом на вход 39,m запроса шины блока 19 арбитра. Наличие 1 на линии 36 общего запроса шины означает, что нет ни одного активного абонента, который бы требовал захвата системной шины, или имеется только один, уже захвативший ее.

1312

Принципиально возможно осущестнить подключение к устройству р процессоров, при этом должны быть реализованы все связи указанных процессоров с системными шинами 45 управления, 46 адреса, 47 данных, с шиной 33 прерывания, с линиями 32 подтверждения выборки, 36 общего запроса шины, 37 занятости, 38 синхронизации и блоком 19 арбитра.

Блок 19 арбитра, принимая сигнал запроса шины от процессора 1.т, выдает процессору 1.т сигнал разрешения захвата шины, поступающий на вход инвертора 65 блока 12 обмена, с выхода которого 1 поступает на третий вход элемента И 52, на первый и второй входы которого поданы соответственно с вькода триггера 59 и сигнал с линии 37 з.шятости. При наличии 1 на этой линии, означающей, что системная шина не занята ни одним из активных абонентов, подключенных к ней, элемент И 52 через элемент ИЛИ 56 подает 1 на информационный вход триггера 60, который взводится также, как и триггер 59, отрицательным фронтом сигнала с линии 38 синхронизации, но как минимум периодом позже.

При наличии О на линии 37 занятости взведение триггера 60 происходит, когда системная шина освобождается, т.е. на линии 37 занятости появляется 1. При взведении триггера 60 через инвертор 63 выдается О на линию 37 занятости, что означает захват системной шины процессором 1.т. С инверсного выхода триггера 60 О подается на элемент И-НЕ 57, при этом, если ни один из других активных абонентов, кроме процессора 1.т, не выдавал запроса шины, на линии 36 общего запроса шины появляется 1, которая поступает через элемент И.ПИ 55 на первый вход элемента И 53, на второй вход которого подается 1 с прямого выхода триггера 60, С элемента И 53 через элемент ИЛИ 56 1 подается на информационный вход триггера 60 до тех пор, пока на линии 36 общего запроса шины не появится О, даже если триггер 59, с которого 1 также через элемент И.ПИ 55 подается на первый вход элемента И 53, сбросится после окончания обращения в результате снятия одного из сигналов управления на первом входе одного из

91/

элементов И 48-51. Это обстоятельство позволяет исключить процедуру захвата системной шины, которая заканчивается взведением триггера 60, когда

отсутствуют другие абоненты, запрашивающие системную шину. При постоянно взведенном триггере 60 процессор 1.т работает в монопольном режиме, н« затрачивая времени на захват

системной шины.

С инверсного выхода триггера 60 вьщается сигнап через выход 41 разрешения адреса и данных блока 12 обмена на управляюшие входы блока 15

передатчиков адреса и блока 16 прие-. мопередатчиков данных, через которые осуществляется связь шины 24 адреса и шины 22 данных микропроцессора 2 соответственно с системными шинами

46адреса и 47 данных. С прямого выхода триггера 60 1 подается на первый вход элемента И-НЕ 58 и на информационный вход сброса триггера 61, который взводится через полпериода импульсов на линии 38 синхронизации после триггера 60о Это обеспечивает необходимую задержку выдачи сигналов управления на системную шину 45 управления относительно выдачи адреса на системную шину 46 адреса, так как элемент И-НЕ 58 и триггер 61 формируют сигнал, который с выхода 42 разрешения сигналов управления блока

12 обмена под 1ется на управляющий вход блока 17 передатчиков управляющих сигналов, который осуществляет связь шины 26 управления процессора 1.т с системной шиной 45 управления.

Через системные шины 46 адреса, 47данных и 45 управления микропроцессор 2 процессора 1.т производит обращение к системной памяти 20 или

к устройствам 21 ввода-вывода. Вьшол- нив требуемую микропроцессором операцию (чтение, запись, ввод, вывод), системная память 20 или устройство 21 ввода-вывода вьщает сигнал низкого уровня на линию 32 подтверждения выборки. Сигнал с этой линии поступает в блок 18 подтверждения, с выхода которого выдается сигнал на вход готовности микропроцессора 2. Принимая этот сигнал, микропроцессор 2 заканчивает обращение и снимает сигнал считывания или записи с шины 25 управления, при этом с блока 18 подтверждения на регистр 4 подается сигнал сброса, что приводит к сня

тию сигнялов на nepHi.ix ллодпх .:- меитпв И А8- .1 блока 12 оИмси.ч, п результате чего сбрасыпается сиач;)л триггер 59, затем триггеры 60 и (S1, на линиях занятости обшего запроса шины и на выходе инвертора 62 устанавливается I, снимается сигнал с выходов А1 разрешения адреса и данных и 42 разрешения сигналов управления.

Таким образом, микропроцессор 2 процессора 1.т отключается от системных шин 45 управления, 46 адреса и 47 данных.

Триггер 60 может и не сброситься после сброса триггера 59, если на лнии 36 общего запроса шины сохраняется высокий уровень. В этом случае микропроцессор 2 процессора 1.т может повторить обрашение сразу, не ожидая окончания процедуры захвата системной шины, как будто он обращается к постоянной 6 или оперативной 7 памяти процессора 1.т. Если к моменту начала этого обращения на линии 36 обшего запроса шины появляется О, то триггер 60 не сбрасывается, так как уже взводится триггер 59, с прямого выхода которого 1 через элемент ИЛИ 55 подается на элемент И 53, что блокирует сброс триггера 60.

Блок 14 временного контроля (фиг. 4) осуществляет контроль времени обращения микропроцессора 2 к системной памяти 20 и к устройствам 21 ввода-вывода. Такой контроль по времени необходим для выявления аппаратных сбоев и программных ошибок при обращениях по не существующим в данной компоновке устройства адресам, а также для устранения ситуации останова. В указанных случаях от системной памяти 20 или от устройства 21 ввода-вьгоода в блок 14 временного контроля не поступает сигнала с линии 32 подтверждения выборки, когда микропроцессор 2 обращается к ресурсам устройства. На первый вход элемента И 73 или И 74 блока 14 временного контроля в начале обращения поступает один из сигналов - чтение, запись, ввод, вывод, подаваемый низким уровнем с системной шины 45 управления. На вторые входы элементов ИЛИ 76 и 77 подается О с выхода 41 разрешения адреса и данных блока 12 обмена. Таким образом, с выходов од149916

ного из итшерторов 82 и 83 через элг- мет(т ИЛИ 78 подается 1 )ia элемент 86 задержки, вход сброса трип сра 81, а также на информационные входы 5 триггеров 79 и 80.

Если обращение не заканчивается за время, определяемое задержкой, например за 50 мкс, а это означает, что на одном из выходов элементов О И 73 и 74 сохраняется сигнал управления и что на линии 32 подтверждения выборки, сигнал с которой подается на информационный вход триггера 81, имеется высокий уровень, то сигf5

нал с выхода элемента 86- задержки

взводит триггер 81, прямым выходом которого взводится один из триггеров 79 или 80, на информационном входе которого имеется I, С инверсных выходов триггеров 79 и 80 через элемент И 75 выдается запрос прерывания на один из входов 23 запроса прерывания блока 5 прерывания. Прямые выходы триггеров 79 и 80 через блок 87 передатчиков соединены с шиной 27 данных процессора l.m.

С прямого выхода триггера 81 через выход готовности блока 14 временного

контроля сигнал готовности выдается в блок 18 подтвержден11я, который, получив этот сигнал, формирует сигнал, подаваемый на вход готовности микропроцессора 2j Микропроцессор 2 заканчивает обращение, хотя оно и не состоялось, при этом блок 18 подтвер-. ждения сбрасывает регистр 4, после чего блок 12 обмена отключает микропроцессор 2 от системной шины.

Обрабатывая запрос прерывания от блока 14 временного контроля, микропроцессор 2 обращается к внутреннему порту ввода-вывода процессора 1.т и считывает состояние триггеров 79 и

80 через блок 9 приемопередатч йсов данных При этом считывании с регистра 4 на вход блока 14 временного контроля подается сигнал ввода с регистра 4, а с дешифратора 8 адреса сигнал выборки, выдаваемый с третьего выхода 31 низким уровнем.

Элемент И-НЕ 85 и инвертор 84 формируют сигнал, подаваемый на управляющий вход блока 87 передатчиков,

который выдает состояние триггеров 79 и 80 на шину 27 данных процессора, при этом взведение триггера 79 означает, что произошла ошибка обращения к системной памяти 20, а взведение

17

триггера 80 - что произошла ошибка обращения к устройствам 21 ввода-вывода. Таким образом, микропроцессор 2 может локализовать причину ошибки и перейти на диагностическую подпрограмму.

Если обращение микропроцессора 2 заканчивается раньше времени, определенного элементом 86 задержки, на вход сброса триггера 81 с элемента ИЛИ 78 подается О, при этом на информационный вход триггера 81 перед окончанием обращения подавался О с линий 32 подтверждения выборки. Таким образом, при отсутствии ошибок обращения триггер 81 не взводится. Установка триггеров 79 и 80 в исходное состояние может осуществляться с5семно или программно.

Блок 11 формирования (фиг, 7) осуществляет формирование и выдачу на щину 26 управления процессора 1 .га управляющих сигналов вьгоода и запис На вход инвертора 109 и первый вход элемента И 112 с регистра 4 подаютс соответственно сигналы вывода.и запси с соответствующих выходов регистра 4. Указанные сигналы перед вьща- чеи их на шину 26 управления процессора 1.т стробируются сигналом записи, подаваемым на блок 1I формирования с щины 25 управления микропроцесора 2, поскольку действительная запись должна начаться только после т го, как микропроцессор 2 вьщает данные, а в момент появления на выходе регистра 4 сигналов вывода или запи на щине 22 данных микропроцессора 2 еще присутствует информация состояния, записьшаемая в регистр 4

Блок 5 прерывания (фиг. 6) осуществляет приоритетное рассмотрение запросов прерывания, поступающих с шны 33 прерывания и от блока 14 временного контроля, запоминание кода .прерывания и выдачу его на шину 22 данных микропроцессора 2, выдачу запроса прерывания на вход 34 запроса прерывания микропроцессора 2 „

Сигналы запроса прерывания, поступающие на входы 23 запроса прерьшания, подаются на входы шифратора 98 о Входам 23 запроса прерывания присвоены номера от О до А. На выходах дешифратора 98 выдается двоичный код, cooтвeтcтвyюп J й следующему соотношению:

18

Б.,

5

0

0

5

0

где Б , - значение двоичного кода

(в двоичной системе); С,р - номер (в Десятичной смете- ме) запроса, имеющий минимальное значение из всех имеющихся запросов прерывания на входе шифратора 98.

Таким образом, максимальный приоритет имеет запрос прерьшания с номером О, минимальный - с номером А, Указанный двоичный код и является ко-, дом прерьгоания, который служит дли локализации микропроцессором 2 источника прерьшания. Помимо выходов с кодом прерывания, щифратор 98 имеет выход, на котором при отсутствии запросов на входах 23 .запроса прерывания устанавливается О. При наш1- чии хотя бы одного запроса на этом выходе устанавливается Указан- 5 ный выход соединен с третьим входом

5

0

элемента И ЮА

Перед обработкой прерывания микропроцессор 2 выдает на шину 25 управления сигнал разрешения прерывания, поступающий на второй вход элемента И 104 блО ка 5 прерьгаания. Для записи кода прерывания в регистр 99 кода прерывания микропроцессор 2 осу ществляет вывод во внутренний порт ввода-вывода процессора l.m, при этом на четвертом выходе коммутатора 13 появляется сигнал, поступающий на вход синхронизации триггера 101 блока 5 прёрьгаания. Этот триггер взводится, и через элемент И 104 на ий- . формационный вход триггера 102 подается 1. Положительным фронтом им- пульса с генератора 3 этот триггер взводится, и на вход синхронизации регистра 99 кода прерьгоания с его прямого выхода подается I, а с инверсного вь1хода триггера 102 подается О на вход сброса триггера 101, Последний сбрасывается, при этом, через элемент И 104 на информационный 102 подается О,

вход триггера

55

Триггер 02 сбрасьшается импуль- сом генератора 3, при этом с его прямого выхода через инвертор 106 подается сигнал на вход синхронизации триггера 103, который взводится, С прямого выхода триггера 103 через элемент ПЛИ 108 поступает сигнал на

191

вход 34 запроса прерывания микропро- цессора 2„ Таким образом, в регистре 99 кода прерывания находится код прерывания, а на вход микропроцессора 2 подан запрос прерывания, Восприни- мая этот запрос, микропроцессор 2 начинает обработку прерывания, записывая в регистр 4 информацию о подтверждении прерывания о

С выхода регистра 4 сигнал подтвер ждения прерьшания поступает на второй вход элемента И 105 блока 5 прерывания, на первый вход элемента И 105 поступает сигнал считывания с шины 25 управления микропроцессора 2 при этом выдается сигнал на управляющий вход блока 100 передатчиков и код прерьгоания из регистра 99 кода прерьшания вьщается на шину 22 данных микропроцессора 2„ Кроме того, через инвертор 107 сбрасьгоается триггер 103, что подготавливает условие снятия сигнала запроса прерывания с выхода элемента ИЛИ 108, который снимается после того, как на выходе элемента И 105 снимается 1, т.е. после снятия сигнала считьшания, что одновременно вызывает снятие сигнала с управляющего входа блока 100 передат- чикрв,

Блок 19 арбитра (фиг/ 5) осуществляет приоритетное рассмотрение запросов, подаваемьпс на входы 39.1- 39,р запроса шины активными абонентами, например такими как процессор 1оШ, которые могут подключаться к системной шине устройства, и выдачу разрешений этим абонентам с выходов 40о1-40„р разрешения захвата шины. Генератор 97 блока 19 арбитра осу- ществляет синхронизацию всех актив- ньк абонентов во время процедуры захвата системной шины, выдавая импульсы на линию 38 синхронизации

Особенностью блока 19 арбитра является возможность организации двух типов приоритета - параллельного и динамического При подаче 1 с переключателя 96 на вход сброса двоич- ного счетчика 94 блоком 19 арбитра устанавливается пара-плельный приоритет, при этом наивысший приоритет будет иметь запрос, подаваемый на первый вход 39.1 запроса шины, низ- ший приоритет - запрос на Р-м входе 39.р запроса шины. Подачей 1 на вход сброса двоичного счетчика 94 последний устанавливается в исходное

25

91

5

О 5 20

35

о 5

5

99920

состояние, при котором с его выхода на вход дешифратора 95 вьщается нулевой двоичный код„

При подаче О с переключателя 96 на вход сброса двоичного счетчика 94 блоком 19 арбитра устанавливается динамический приоритет, при котором приоритет запроса на каждом входе .р запроса шины возрастает от низшего до высшего, после чего опять становится низшям и опять возрастает до высшего и т.д. Такое изменение приоритета обуславливается изменением состояния двоичного счетчика 94 после каждой вьщачи одним из активных абонентов, занимающих в данный момент системную шину, сигнала на линию 37 занятости, при этом дешифратор 95, имеющий р выходов, попеременно устанавливает на одном из них О.

В блоке 19 арбитра (фиг. 5) для упрощения дан вариант с четырьмя входами 39.1-39.4 запросов шины. Пусть в данный момент с первого выхода дешифратора 95 вьщается О на второй вход первого 90.1 и на первый вход второго 90.2 элементов И. В этом случае с выхода первого элемента НЕ 92 Л на второй вход первого элемента И-НЕ 93.1 подается 1. Можно установить, что на втором входе всех остальных элементов И-НЕ 93,2- 93.4 также будет 1 при отсутствии запросов от абонентов, т.е„ когда с выходов всех инверторов 88.1-88„4 вьщается О. При отсутствии запросов на линии 37 занятости установлена ГЧ U .

При одновременном появлении запроса на первом н четвертом входах 39о 1 и 39.4 запроса шины с выходов инверторов 88.1 и 88.4 на первый вход элементов И-НЕ 93.1 и 93.4 подается 1 и в первый момент появляется О на первом и четвертом выходах 40.1 и 40.4 разрешения захвата шины. В блоке 12 обмена вьщача как сигнала запроса шины, так и сигнала занятости производится по отрицательному фронту импульса на линии 38 синхронизации, при этом вьщача сигнала занятости осуществляется через период импульса на линии 38 синхронизации после получения блоком 12 обмена разрешения захвата шины от блока 19 арбитра.

Поскольку с выхода первого инвертора 88.1 1 подается также на первый вход четвертого элемента И , на второй вход которого в данном случае подается 1 с второго выхода де- шифратора 95, то с выхода четвертого элемента И 90„4 через второй элемент ИЛИ 91.2 1 подается на второй вход пятого элемента И 90о5с Так как на первый вход пятого элемента И 90.5 по подается 1 с третьего выхода дешифратора 95, то через третий элемент ИЛИ 91.3 1 подается на второй вход седьмого элемента И 90.7, на первом входе которого имеется 1 с четвер- того выхода дешифратора 95. Через четвертый элемент ИЛИ 91.4 1 подается на вход четвертого элемента НЕ 92.4, при этом на второй вход четвертого элемента И-НЕ 93.4 подается О и сигнал с четвертого выхода 40.4 разрешения захвата шины исчезает, оставаясь только на первом выходе 40. разрешения захвата шины к моменту

прихода отрицательного фронта импульса на линии 38 синхронизации..

Первый абонент выставляет сигнал на линию 37 занятости, при этом блокируются все элементы И-НЕ 93.1-93,р а двоичный счетчик 94 переводится в следующее состояние, при котором высший приоритет передается второму входу 39.2 запроса шины, а низший становится у первого входа 39 о 1 запроса шины. В этом случае, если при снятич сигнала занятости снова имеются запросы шины на первом и четвертом входах 39.1 и 39.4 запроса шины, к моменту прихода следующего отрицатель- ного фронта импульса на линии 38 синхронизации имеет место сигнал уже с четвертого выхода 40,4 разрешения захвата шины, как имеющего по сравнению с первым более старший приори- тет. Очевидно, что сброс счетчика 94 переключателем 96 устанавливает в блоке 19 арбитра параллельный тип приоритета, имеющий постоянное распределение приоритетных весов между абонентами.

Блок 18 подтверждения (фиг. 9) осуществляет прием сигнала подтверждения с линии 32 подтверждения выборки, выдачу сигнала готовности на вход готовности микропроцессора 2, сброс регистра 4 по окончанш любого обращения микропроцессора 2, с помощью блока 14 временного контроля уст

5

о Q 5 0

5

раняет ситуации зависания п случаях тайм-аутов, т.е. выводит микропроцессор из состояния ожидания при длительном отсутствии сигнала подтверждения выборки от адресуемого устройства - системной памяти 20 или

устройства 21 ввода-вывода. I

При наличии О с выхода 41 разрешения адреса и данных блока 12 обмена на втором входе элемента ИЛИ- НЕ 123, означающего, что системная тина занята микропроцессором 2 процессора 1.171, блок 18 подтверждения воспринимает сигнал, поступающий низким уровнем с линии 32 подтверждения выборки от системной памяти 20 или устройств 21 ввода-вывода. При поступлении сигнала подтверждения положительным фронтом импульса генератора 3 взводится триггер 127, при этом с выхода элемента И-НЕ 126 выдается 1 на вход готовности микропроцессора 2. На второй вход элемента И-НЕ 126 подается I с в ыхода внешнего обращения блока 12 обмена. При обращениях микропроцессора 2 к постоянной 6 или оперативной 7 памяти процессора 1.т или к внутреннему порту ввода-вывода процессора 1.т с этого выхода выдается О, поэтому с выхода элемента И-НЕ 126 сигнал на вход готовности микропроцессора 2 выдается постоянно, а время обращения зависит только от микропроцессора 2.

Получая сигнал готовности, микропроцессор 2 снимает сигналы считывания или записи, которые с шины 25 управления микропроцессора 2 подаются на второй вход соответственно элементов ИЛИ-НЕ 125 и 124. При снятии сигнала считывания взводится триггер 128, на информационный вход которого подается сигнал готовности. При записи взведение триггера 128 производится первьм же отрицательным фронтом импульса генератора 3, поступившим на вход инвертора 129 после прихода сигнала готовности на информационный вход триггера 128. Это обстоятельство позволяет сократить обращения и, тем самым, быстрее освободить системную щину для другого активного абонента С инверсного выхода триггера 128 О подается на вход сброса регистра 4„ Исходное состояние триггера 128 восстанавливается, когда микропроцессор 2 начинает новое обращение, вьщавая сигнал синхронизации на шину

25 управления, который через инвертор 130 подается на вход сброса триггера 128.

Если при обращениях микропроцессора 2 системная память 20 или устрой- 21 ввода-вывода не выдают сигнал подтверждения в течение установленного промежутка времени, блок 1А временного контроля выдает сигнал с выхо да готовности в блок 18 подтверждения, который поступает на вход передатчика 131, управляющий вход которого соединен с выходом 41 разрешения адреса и данных блока 12 обмена. При этом на первый вход элемента ИЛИ-НЕ 123 поступает сигнал подтверждения, что приводит к появлению сигнала готовности на выходе элемента И-НЕ 126. Это

fO

ративной памятью процессора, выход блока передатчиков адреса подключен к шине адреса процессора, соединен- . ной с постоянной и оперативной памятью процессора и дешифратором адреса, имеюш;им первый, второй и третий выходы, вход готовности микропроцессора подключен к выходу блока подтверждения, при этом блок подтверждения, системная память и устройства ввода- вывода подключены к линии подтверждения выборки, устройства ввода-вывода подключены к шине прерывания, соединенной с входами запроса прерывания блока прерывания, который подключен к входу запроса прерывания микропроцессора, отличающееся тем, что, с целью расширения функциональных возможностей, оно содер- позволяет исключить ситуацию, в кото- Q жит блок арбитра, имеющий р входов

запроса шины и р выходов разрешения захвата шины, а каждый процессор дополнительно содержит блок обмена, коммутатор, блок временного контроля, второй блок передатчиков адреса, вто- второй блок приемопередатчикрв данных, блок.передатчиков управляющих

рой микропроцессор 2 неопределенно долгое время находится в состоянии ожидания ответа от адресуемого им абонента, т.е„ ситуацию фактического останова устройства ввиду случайного сбоя или ошибки в программе.

25

Формула изобретения

1. Микропроцессорное устройство обработки данных, содержащее процессоры, каждый из которых состоит из микропроцессора, генератора, регистра, блока прерывания, постоянной и

сигналов, при этом блок обмена подключен к регистру, к третьему выходу 30 дешифратора адреса, к первому выходу коммутатора, к линиям общего запроса шины, занятости и синхронизации, к п-му входу запроса шины блока арбитра (п 1,2,о..,р), к п-му выходу

сигналов, при этом блок обмена подключен к регистру, к третьему выходу 30 дешифратора адреса, к первому выходу коммутатора, к линиям общего запроса шины, занятости и синхронизации, к п-му входу запроса шины блока арбитра (п 1,2,о..,р), к п-му выходу

оперативной памяти процессора, дещиф- разрешения захвата шины блока арбитратора адреса, блока приемопередатчиков данных, блока передатчиков адреса, блока формирования, блока подра, выход разрешения адреса и данных блока обмена соединен с блоком временного контроля, блоком подтверждения и с управляющими входами второго 40 блока приемопередатчиков данных и второго блока передатчиков адреса, выход разрешения сигналов управления

тверждения, а также содержащее системную память и устройства ввода-вывода, причем микропроцессор через пшну данных микропроцессора соединен с регистром, блоком прерывания, имеющим входы запроса прерывания, и первым входом-выходом блока приемопередатчиков данных, через шину адреса микропроцессора соединен с блоком передатчиков адреса, а через шину управления микропроцессора соединен

с регистром, блоком прерывания, бло- Q цессора, второй и третий выходы комком формирования, подключенным к ши- мутатора подключены соответственно к не управления процессора, генератор постоянной и оперативной памяти про- подключен к микропроцессору и регист- цессора, четвертый выход коммутатора

соединен с блоком прерывания, под- ключенньм к генератору, блок временного контроля соединен с третьим выходом дешифратора адреса, с шиной данных процессора, с регистром, с системной шиной управления, с линиру, который соединен с блоком прерывания , блоком формирования и шиной управления процессора, второй вход- выход блока приемопередатчиков данных подключен к шине данных процессора, соединенной с постоянной и one

ративной памятью процессора, выход блока передатчиков адреса подключен к шине адреса процессора, соединен- . ной с постоянной и оперативной памятью процессора и дешифратором адреса, имеюш;им первый, второй и третий выходы, вход готовности микропроцессора подключен к выходу блока подтверждения, при этом блок подтверждения, системная память и устройства ввода- вывода подключены к линии подтверждения выборки, устройства ввода-вывода подключены к шине прерывания, соединенной с входами запроса прерывания блока прерывания, который подключен к входу запроса прерывания микропроцессора, отличающееся тем, что, с целью расширения функсигналов, при этом блок обмена подключен к регистру, к третьему выходу 30 дешифратора адреса, к первому выходу коммутатора, к линиям общего запроса шины, занятости и синхронизации, к п-му входу запроса шины блока арбитра (п 1,2,о..,р), к п-му выходу

разрешения захвата шины блока арбит разрешения захвата шины блока арбитра, выход разрешения адреса и данных блока обмена соединен с блоком временного контроля, блоком подтверждения и с управляющими входами второго 40 блока приемопередатчиков данных и второго блока передатчиков адреса, выход разрешения сигналов управления

блока обмена подключен к уппавляюще- МУ входу блока передатчиков управля45 ющих сигналов, выход внешнего обращения блока обмена соединен с блоком подтверждения, коммутатор соединен с выходами дешифратора адреса, с шиной данных и шиной управления про.25

ей подтверждения выборки, с входом запроса прерывания блока прерывания, с блоком подтверждения, подключенным к генератору, регистру и шине управления микропроцессора, вход второго блока передатчиков адреса подключен к шине адреса микропроцессора, а выход - к системной шине адреса, первый вход-выход второго блока приемопередатчиков данных подключен к шине данных микропроцессора второй вход-выход второго блока приемопередатчиков данных подключен к системной шине данных, вход блока передатчиков управляющих сигналов подключен к шине управления процессора, а выходы ввода, вывода, чтения и записи блока передатчиков управляющих сигналов подключены к соответствующим линиям системной гаины управления, блок арбитра подключен к линиям занятости и синхронизации, а системная память и устройства ввода- вьшода подключены к системным шинам

адреса, данных и управления о

I

2о Устройство по п. 1, о т л итем, что блок обме

чающееся

на содержит шесть элементов И, три элемента ИЛИ, два элемента И-ЧЕ, три триггера и четыре инвертора, причем первые входы первого, второго, третьего и четвертого элементов И подключены соответственно к выходам ввода, вьгоода, чтения и записи реги- стра, вторые входы первого и второГ Т элементов И подключены к третьему выходу дешифратора адреса, вторые входы третьего и четвертого элементов И подключены к первому выходу коммутатора, выходы первого, второго, третьего и четвертого элемента И соединены с входами первого элемента ИЛИ, выход которого подключен

2

к информационному входу первого триг- 45 И-НЕ и вторым выходом коммутатора.

гера и к выходу внешнего обращения блока обмена, входы синхронизации первого и второго триггеров соединены с выходом третьего инвертора, вход которого подключен к входу синхронизации третьего триггера и к линии синхронизации, прямой выход первого триггера соединен с уходом первого инвертора, с первым входом первого элемента И-НЕ, с первым входом второго элемента ИЛИ, с первым входом пятого элемента И, выход первого инвертора подключен к п-му входу запроса шины блока арбитра, -инверсный

, 10

30 40

9199926

выход второго триггера подключен к второму входу первого элемента И-НЕ и к выходу разрешения адреса и данных блока обмена, выход первого элемента И-НЕ соединен.с вторым входом второго элемента ИЛИ и подключен к линии общего запроса шины, выход второго элемента ИЛИ соединен с первым входом шестого элемента И, прямой выход второго триггера соединен с входом второго инвертора, вторь1М . входом шестого элемента И, первым входом второго элемента И-НЕ, информационным входом и входом сброса , третьего триггера, выход второго инвертора подключен к линии занятости и к второму входу пятого элемента И, вход четвертого инвертора подключен к п-му выходу разрешения захвата шины блока арбитра, а выход - к третьему входу пятого элемента И, выходы пятого и шестого элементов И соединены с входами третьего элемента ИЛИ, выход которого подключен к информационному входу второго триггера, прямой выход третьего триггера соединен с вторым входом второго элемента И-НЕ, выход которого подключен к выходу разрешения сигналов управления блока обмена.

15

20

25

3„ Устройство по п. 1, отличающееся тем, что коммутатор содержит четыре элемента И-НЕ, элемент И, инвертор и триггер, причем первые входы первого и второго элементов И-НЕ подключены соответственно к первому и второму выходам дешифратора адреса, вторые входы первого и второго элементов И-НЕ и первый, вход третьего элемента И-НЕ подключены к инверсному выходу триггера, выход первого элемента И-НЕ соединен с первым входом четвертого элемента

выход второго элемента И-НЕ соединен с вторым входом четвертого элемента И-НЕ и третьим выходом коммутатора, выход четвертого элемента И-НЕ подключен к второму входу третьего элемента И-НЕ, выход которого подключен к первому выходу коммутатора, вход инвертора соединен с третьим выходом дешифратора адреса, выход инвертора

подключен к первому входу элемента И, второй вход которого соединен с линией вьгоода шины управления процессора, а выход подключен к четвертому выходу коммутатора и к входу синхро 129

ниэации триггера, информационный вход которого соединен с шиной дан- ньгх нроцессора.

4. Устройство но п. 1, отличающееся тем, что блок вре- , менного контроля содержит три элемента И, три элемента HJW, три триггера три инвертора, элемент И-НЕ, элемент задержки и блок передатчиков, причем первый и второй входы первого элемен- )0 та И, первый и второй входы второго элемента И подключены соответственно к линиям чтения, записи, ввода, вывода системной шины управления, выходы первого и второго элементов И соеди- 15 иены соответственно с первыми входами первого и второго элементов ИЛИ, вторые входы которых подключены к выходу разрешения адреса и данных блока обме на, выходы первого и второго элемен- 20 тов ИЛИ соединены соответственно с входами первого и второго инверторов, выход первого инвертора соединен с информационным входом первого триггера и первым входом третьего элемента ИЛИ, выход второго инвертора соединен с информационным входом второго триггера и вторым входом третьего элемента ИЛИ, выход которого подключен к входу элемента задержки и входу сбро-- са третьего триггера, выход элемента задержки соединен с входом синхронизации третьего триггера, информационный вход третьего триггера подключен к линии подтверждения выборки, пря- 35 мой выход третьего триггера соединен с выходом готовности блока временного контроля и с входами синхронизации первого и второго триггеров, прямые выходы которых подключены к входам 40 блока передатчиков, а ийверсные вы- ходы соединены с входами третьего элемента И, выход которого подключен к входу запроса прерывания блока прерывания, первый и второй входы эле- мента И-НЕ подключены соответственно

99928

к выходу ввода регистра и выходу третьего инвертора, вход которого подключен к третьему выходу дешифратора адреса, выход элемента И-НЕ соединен с управляющим входом блока передатчиков, выходы которого подключены к шине данных процессора.

5. Устройство по п. 1, отличающееся тем, что блок арбитра содержит р+1 инверторов, 2р элементов И, р элементов ИЛИ, НЕ и И-НЕ, двоичный счетчик, дешифратор, переключатель и генератор, причем входы, каждого из р инверторов соединены с входами запроса шины блока: арбитра, выход каждого п-го инвертора (п 1,2,..,,р-1) соединен с первым входом п-го элемента И-НЕ и первым входом (2п+1)-го элемента И, выход р-го инвертора соединен с первым входом р-го элемента И-НЕ и с первым входом первого элемента И,, выход каждого п-го элемента ИЛИ соединен с вторым входом (2п+2)-го элемента И и с входом п-го элемента НЕ, выход р-го элемента ИЛИ соединен с вторым входом второго элемента И и входом р-го элемента НЕ, второй вход (2i+l)-ro и первый вход 2i-ro элементов И (1 1,2,...,р) подключен к i-му выходу дешифратора, выходы (21- 1)-го и 2i-ro элементов И подключены к входам i-ro элемента ИЛИ, выход каждого 1-го элемента НЕ соединен с вторым входом i-ro элемента И-НЕ, третий вход элементов И-НЕ подключен к линии занятости и входу (р+1)-го инвертора, выходы элементов И-НЕ подключены к выходам разрешения захвата шины блока арбитра, счетный вход и вход сброса двоичного счетчика подключены соответственно к выходам (р+1)-го инвертора и переключателя, выходы двоичного счетчика подключены к дешифратору, вькод генератора соединен с линией синхронизации.

S2

39

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕЗЕРВИРОВАННАЯ СИСТЕМА | 1991 |

|

RU2010315C1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для обмена данными между процессором и периферийными устройствами | 1987 |

|

SU1501078A1 |

| Резервированная система | 1990 |

|

SU1785087A1 |

| Устройство для сопряжения системной и локальной магистралей. | 1988 |

|

SU1672460A1 |

| Устройство для сопряжения ЭВМ с магистралью | 1988 |

|

SU1508227A1 |

| Мультимикропроцессорная система | 1980 |

|

SU907551A1 |

| Многопроцессорная система | 1989 |

|

SU1647597A1 |

| УСТРОЙСТВО КОНТРОЛЯ ПРОЧНОСТИ КРЫЛА ВОЗДУШНОГО СУДНА | 2011 |

|

RU2469289C1 |

| Устройство для сопряжения ЭВМ в вычислительной системе с децентрализованным арбитром магистрали | 1984 |

|

SU1291997A1 |

Изобретение относится к области вычислительной техники и может быть использовано в системах управления технологическими процессами. Целью изобретения является расширение функциональных возможностей микропроцессорного устройства обработки данных, содержащего один или более процессоров, состоящих из микропроцессора, генератора, регистра, блока прерыва- }1ия, постоянной и оперативной памяти процессора, дешифратора адреса, блока приемопередатчиков данных, блока передатчиков адреса, блока формирования и блока подтверждения. Устройство также содержит системную память и устройства ввода - вывода Устройство обладает расширенными функциональными возможностями за счет того, что процессоры дополнительно содержат блок обмена, комму- татрр. блок временного контроля, второй блок передатчиков адреса, второй блок приемопередатчиков данньш, блок передатчиков управляющих сигна- лов, а также за счет того, что устройство содержит блок арбитра, имеющий р входов запроса и р выходов разрешения захвата шины и позволяющий подключать к устройству более двух процессоров 4 з.п. ф-лы, 9 ил. (О (Л tc со ;о со со

38

О

J7 4f

-W

52

Риг..2

з: 4

2в

65h-1..

30

67

.27

i26

72

3J -TT/I

70

Фиг.З

2J

Фм(

J9.f

4«Y

4tf.«

38

(Риг. 5

11

16

111

112

fPLLZ.l

25

122

Составитель Н. Васильев Редактор В. Петраш Техред Сердюкова Корректор А. Зимокосов

273/49

Тираж 673 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д, А/5

Производственно-полигра.фическое предприятие, г, Ужгород, ул. Проектная, 4

fpuz.9

| Приспособление с иглой для прочистки кухонь типа "Примус" | 1923 |

|

SU40A1 |

| Отраслевой каталог | |||

| М., ЦНИИТЭИприборостроения, 1979, №6, т, 4, вьт, 1, Патент США № 4174536, кл | |||

| Способ получения мыла | 1920 |

|

SU364A1 |

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

| MYCRO-I microcomputer reference dat a book, A/S ЖСКОИ, Норвегия, 1976, | |||

Авторы

Даты

1987-02-23—Публикация

1982-02-12—Подача