элемента ИЛИ, а синхронизирую1дий выход вывода последовательного кода с выходом разрешения вывода памяти масок прерыпания и вторым входом первого элемента ИЛИ, информационный вход распределителя управляющих сигналов соединен с информационным входом параллельного кода устройства, а первый и второй входы выбора режима соответственно - с входами сигналов режима записи и чтения устройства. 2, Устройство по п. отличающееся тем, что многоканаль ный блок.обратимого преобразования параллельного кода в последовательный содержит в каждом канале входной и выходной буферные регистры, дна сдвиговых регистра, делитель ча тоты, три счетчика импульсов, генератор импульсов, восемь триггеров, два элемента И-НЕ, два элемента И, два элемента ИЛИ и два магистральных усилителя, причем информационные входы входных буферных регистров каналов соединены с входом параллел ного кода блока, выходы выходных бу ферных регистров каналов соединены выходом параллельного кода блока, в каждом канале информационный вход и выход первого сдвигового регистра подключены соответственно к выходу входного буферного регистра и инфор мационному входу первого триггера, вход синхронизации - к выходу делителя частоты и входам синхронизации первого триггера и первого счетчика импульсов, а вход продвижения - к выходу первого элемента И и входу сброса первого триггера, вход устав ки которого соединен с входом сброса блока первым входом установки второго триггера, входами сброса третьего и четвертого триггеров и ; первыми входами первого и второго элементов ИЛИ, выходы которых подключены соответственно ко входу сброса пятого триггера и входу установки шестого триггера, инверсный выход которого соединен с входом сброса седьмого триггера и синхрони зирующим входом восьмого триггера, информационный вход и выход которог подключены соответственно к выходу седьмого триггера и информационному входу пятого триггера, синхронизиРЯощий вход которого подключен к синхронизирующему входу выходного буферного регистра, входу сброса второго счетчика импульсов, первому . входу второго элемента И и прямому выходу шестого триггера, вход сброса которого соединен с синхронизирующими входами вторых счетчика импульсов и сдвигового регистра и выходом третьего счетчика иг.1пульсов, вход сброса которого подключен к второму входу второго элемента ИЛИ и выходу второго элемента И, а синхронизирующий вход - к выходу генератора импульсов, синхронизирующим входам делителя частоты и четвертого триггера и первому входу первого элемента И-НЕ, вторым входом соединенного с выходом BTQjporo элемента И-НЕ, а выходом - с синхронизирующим входом третьего триггера, информационный вход которого соединен с вьгкодом первого счетчика импульсов, прямой выход - с вторым входом установки второго триггера, а инверсный выход - с первыми входами первого .элемента И и второго элемента И-НЕ и входами сброса делителя частоты и первого счетчика импульсов, вход сброса второго триггера подключен к синхронизирующему входу входного буферного регистра, инверсный выход к информа ционному входу четвертого триггера, а прямой выход - к информационному входу первого магистрального усилителя, выход которого соединен с синхронизирующим ВЫХОДОМ вывода последовательного кода блока, а управляющий вход - с входом управления третьим состоянием выходного буферного регистра и управляющим входом второго магистрального усилителя, выход которого подключен к синхронизирующему выходу ввода последовательного кода блока, а информационный вход - к выходу пятого триггера, выход второго сдвигового регистра соединен с информационным входом выходного буферного регистра, а информационный вход - с входом установки седьмого триггера и вторым входом второго элемента И, выход второго счетчика импульсов соединен с треть-, им входом второго элемента ИЛИ, причем выходы первых триггеров каналов образуют группу выходов последова тельного кода блока, информационные входы вторых сдвиговых регистров каналов образуют группу входов последовательного.кода блока, входа сброса вторых триггеров каналов, входы управления третьим состоянием выходных буферных регистров и вторые ды первых элементов ИЛИ каналов вхо- разуют группу входов выборки канала об- блока. 1140125;

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Устройство для сопряжения ЭВМ с факсимильным аппаратом | 1988 |

|

SU1524060A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1987 |

|

SU1472913A1 |

| Станция локальной сети | 1987 |

|

SU1478221A1 |

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

| Устройство для сопряжения цифровой вычислительной машины с каналами связи | 1983 |

|

SU1160421A1 |

| Устройство для сопряжения абонентов с электронной вычислительной машиной | 1983 |

|

SU1132283A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1990 |

|

SU1727126A1 |

| Многоканальная система сбора и регистрации измерительной информации | 1989 |

|

SU1783547A1 |

| Устройство для сопряжения ЭВМ с объектами управления | 1986 |

|

SU1401469A1 |

1. УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛА Ш СВЯЗИ, содержащее два элемента ИЛИ, триггер, распределитель управляющих сигналов и многоканальный блок обратимого преобразования параллельного кода в последовательный,группы входов и выходов последовательного кода которого являются соответственно группами информационных входов и выходов последовательного кода устройства, вход и выход параллельного кода - соответственно информационным ВХОДОМ и выходом параллельного кода устройства,а группа входов выборки канала соединена с группой выходов распределителя управляющих сигналов, информационный вход и выход триггера подключены соответственно к выходу первого элемента ИЛИ и выходу яапроса прерывания устройства, отличающееся тем, что, с целью расширения области применения устройства, в него введены память масок прерывания, группа элементов ЗАПРЕТ, генератор импульсов., элемент И и элемент задержки, причем первый вход элемента И соединен с выxoдo элемента задержки, а выход - с первым входом второго элемента ИЛИ, выход генератора импульсов подключен к синхронизирующему входу триггера и тактовому входу распределителя управляющих сигналов, вход останова которого соединен с выходом первого элемента ИЛИ, а вход записи уставкис входом записи маски прерывания (Л устройства и вторым входом элемента И, выход второго элемента ИЛИ подключен к входу разрешения записи памяти масок прерывания, адресный вход которой соединен с выходом адреса состояния распределителя управляющих сигналов и выходом номера канала устройства, а группа информационных входов - с выходами элементов „ЗАПРЕТ группы, информационные входы которых подключены к информационному входу параллельного кода устрой э ел ства, а управляющие входы - к входу сброса устройства, второму входу второго элемента ИЛИ и входу сброса многоканального блока обратимого преобразования параллельного кода в последовательный, синхронизирующий выход ввода последовательного кода которого соединен с выходом разрещения ввода памяти масок прерывания, выходом адреса вектора прерывания устройства и первым входом первого

Изобретение относится к вычислительной технике и предназначено для организации обмена ЭВМ с большим числом последоватепьных каналов связи, в частности для подключения группы символьных дисплеев.

Известны устройства.для сопряжения цифровой, вычислительной машины с дискретными каналами связи, содержащие линейныйблок, буферный регистр, регистр информации, регистр маркеров, регистр коммутации, коммутатор, блок памяти, блок синхронизации, блок управления коммутацией и блок очередности выдачи знаков. Основой .устройства является блок памяти, представляющий собой ассоциативное запоминающее устройство, с помощью которого осуществляется обмен байтами с ЭВМ, двойная буферизация приема и передачи и вьщача очередных бит в линейньп блок 1 .

Недостатками данного устройства являются сложность и большой объем оборудования.

Наиболее близким к предлагаемому является устройство для српряжения вычислительной машины с каналами связи, содержащее многоканальный, блок обратимого преобразования параллельного кода в последовательный группы входов и выходов последовательного кода которого являются соответственно группами информациойны последовательных входов и выходов устройства, вход и выход параллельного кода являются соответственно информа.ционными параллельными входо и выходом устройства, адресный вход непосредственно, а управляющий вход через распределитель импульсов подключены соответственно к первому и второму выходам блока управления, группа входов которого соединена с выходами элементов И группы, первым входами соединенных с группой входо готовности абонентов устройства и группой входов регистра конца обмена, а вторыми входами - с группой вьгходов регистра адреса, входом подключенного к адресному входу устройства, группа выходов регистра конца обмена через первьй элемент ИЛИ соединена со входом сброса счетчика и первьм

входом второго элемвнта ИЛИ, выход и второй вход которого соединены соответственно с установочным вхоом триггера и выходом счетчика, разрешающий вход которого соединен с входом сброса триггера, выход которого является выходом запроса обращения устройства, и входом сброса устройства, а счетный вход - с вхо- дом тактовых импульсов устройства, причем многоканальный блок обратимого преобразования параллельного кода в последовательный содержит коммутатор, блок контроля, обратимый преобразователь параллельного кода в последовательный и буферную память з

Недостаток устройства состоит в ограниченной области применения устройства, поскольку оно, во-первых, требует дополнительных управляющих сигналов от абонентов, работающих по каналам связи, а во-вторых, не способно обеспечить маскированке каналов раздельно по вводу и выводу.

Цель изобретения - расширение области применения устройства.

Поставленная цель достигается тем, что в устройство, содержащее два элемента ИЛИ, триггер, распределитель управляющих сигналов и многоканальный блок обратимого преобразования параллельного кода в последовательный, группы входов и выходов последовательного кода которого являются соответственно группами информационных входов и выходов последовательного кода устройства вход и выход параллельного кода - соответственно информационными входом и вь ходом параллельного кода устройства, а группа входов выборки канала сое3динена с группой выходов распределителя управляющих сигналов, информационный вход и выход триггера подключены соответственно к выходу первого элемента ШШ и выходу зацроса прерывания устройства, введены память масок прерывания группа элементов ЗАПРЕТ, генератор импульсов, элемент И и элемент задержки, причем первый вход элемента И соединен с вы ходом элемента задержки, а выход - с первым входом второго элемента ИЛИ, выход генератора импульсов подключен к синхронизирующему входу триггера и тактовому входу распределителя управляющих сигналов, вход останова которого соединен с выходом, первого элемента ИЛИ, а вход записи уставки с входом записи маски прерывания устройства и вторым входом элемента И, выход второго элемента ИЛИ подключен к входу разрешения записи памяти масок прерывания, адресный вход которой соединен с выходом адреса состояния распределителя управляю;щих сигналов и выходом номера канала устройства, а группа информационных входов с выходами элементов ЗАПРЕТ группы, и формационные вхбды которых подключены к информационному входу параллельного кода устройства, а управляющие входы-- к входу сброса устройства, второму входу вто рого элемента ИЛИ и-входу сброса многоканального блока обратимого . преобразования параллельного кода в последовательный, синхронизирующий выход ввода последовательного кода которого соединен с выходом разрешения ввода памяти масок прерывания, выходом адреса вектора прерывания устройства и первым входом первого элемента ИЛИ, а синхронизирующий выход вывода последовательного кода с выходом разрешения вывода памяти масок прерывания и вторым входом первого элемента ИЛИ, информационны вход распределителя управляющих сиг налов соединен с информационным входом параллельного кода устройств а первый и второй входы выбора режи ма соответственно - с входами сигна .лов режима записи и чтения устройства. Многоканальный блок обратимого преобразования параллельного кода в последовательный содержит в каждом канале входной и выходной буферные 254 регистры, два сдвиговых регистра, делитель частоты.три счетчика импульсов, генератор импульсов, восемь триггеров, два элемента И-НЕ, два элемента И, два элемента ИЛИ и два магистральных усилителя, причем информационные входы входных буферных регистров каналов соединены с входом параллельного кода блока, выходы выходных буферных регистров каналов соединены с выходом параллельного кода блока, в каждом канале информационный вход и выход первого сдвигового регистра подключены соответственно к выходу входного регистра и информационному входу первого триггера, вход синхронизации ,к выходу делителя частоты и входам синхронизации первого триггера и первого счетчика импульсов, а вход продвижения - к выходу первого элемента И и входу сброса первого триггера, вход установки которого соединен с входом сброса блока, первым входом установки второго триггера, входами сброса третьего и четвертого триггеров.и первыми входами первого и второго элементов ИЛИ, выходы которых подключены соответственно к входу сброса пятого триггера и входу установки шестого триггера, инверсный выход которого соединен с входом сброса седьмого триггера и синхронизирующим входом восьмого триггера, информационный вход и выход которого подключены соответственно к выходу седьмого триггера и информационному входу пятого триггера, синхронизирующий вход которого подключен к синхронизирующему входу выходного буферного регистра,входу сброса второго счетчика импульсов, первому входу второго элемента И и прямому выходу шестого триггера, вход сброса которого соединен с синхронизирующими входами вторых счетчика импульсов и сдвигового регистра и выходом третьего счетчика импульсов, вход сброса которого подключен к второму входу второго элемента ИЛИ и выходу второго элемента И, а синхронизирующий вход - к выходу генератора импульсов, синхронизирующим входам делителя частоты и четвертого триггера и первому входу первого элемента И-НЕ, вторым входом соединенного с выходом второго элемента И-НЕ, а выходом - с синхронизирующим

5

входом третьего триггера, информаци онный вход которого соединен с выходом первого счетчика импульсов,прямой выход - с вторым входом установки второго триггера, а инверсный выход - с первыми входами первого элемента И и второго элемента И-НЕ и входами сброса делителя частоты и первого счетчика импульсов, вход сброса второго триггера подключен к синхронизирующему входу входного буфеч ного регистра, инверсный выход - к информационному входу четвертого тригге, ра, а прямой выход - к информационному входу первого магистрального усилителя, выход которого соединен с синхронизирующим выходом вывода последовательного кода блока, а управляющий вход - с входом управления третьим состоянием выходного буферного регистра и управляющим входом второго магистрального усилителя, выход которого подключен к синхронизирующему выходу ввода последовательного- кода блока, а информационный вход - к выходу пятого триггера, выход второго сдвигового регистра соединен с информационным входом выходного буферного регистра, а информационный вход - с входом установки седьмого триггера и вторым входом второго элемента И, выход второго счетчика импульсов соединен с третьим входом второго элемента ИЛИ, причем выходы первых триггеров каналов образуют группу выходов последоэательного кода блока, информационные входы вторых сдвиговых регистров каналов образуют группу входов последовательного кода блока, входы сброса вторых триггеров каналов, входы управления третьим состоянием выходных буферных регистров и вторы входы первых элементов ИЛИ каналов образуют группу входов выборки канала блока.

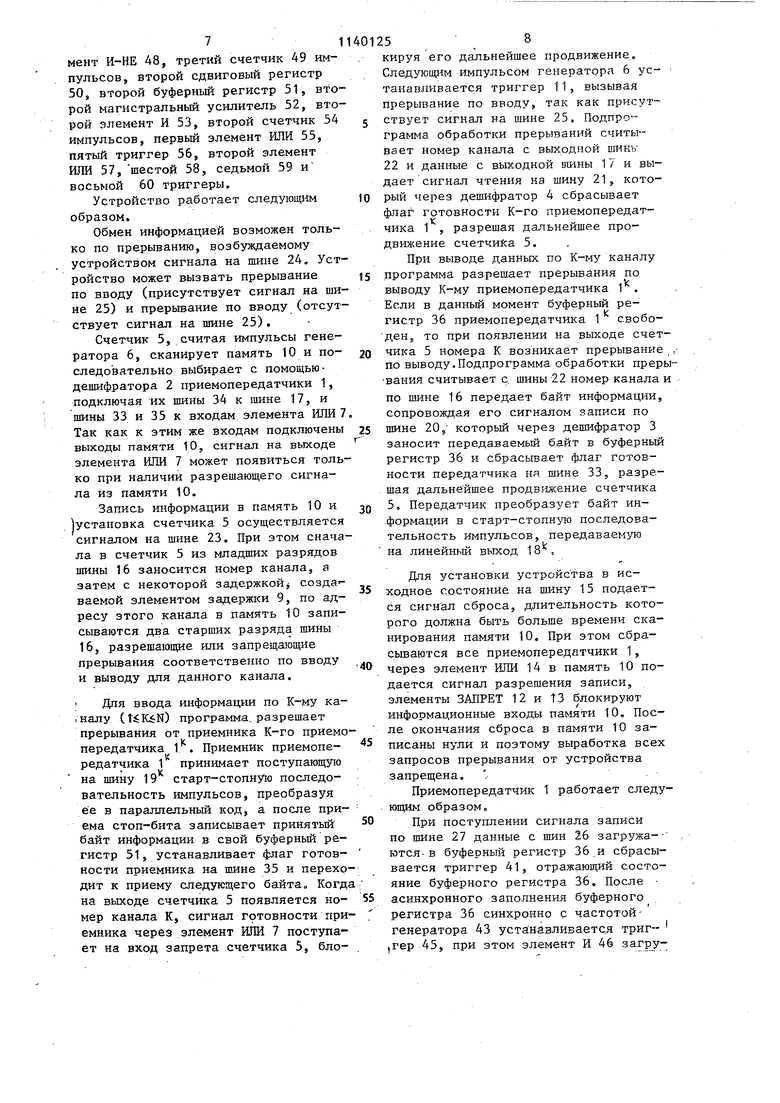

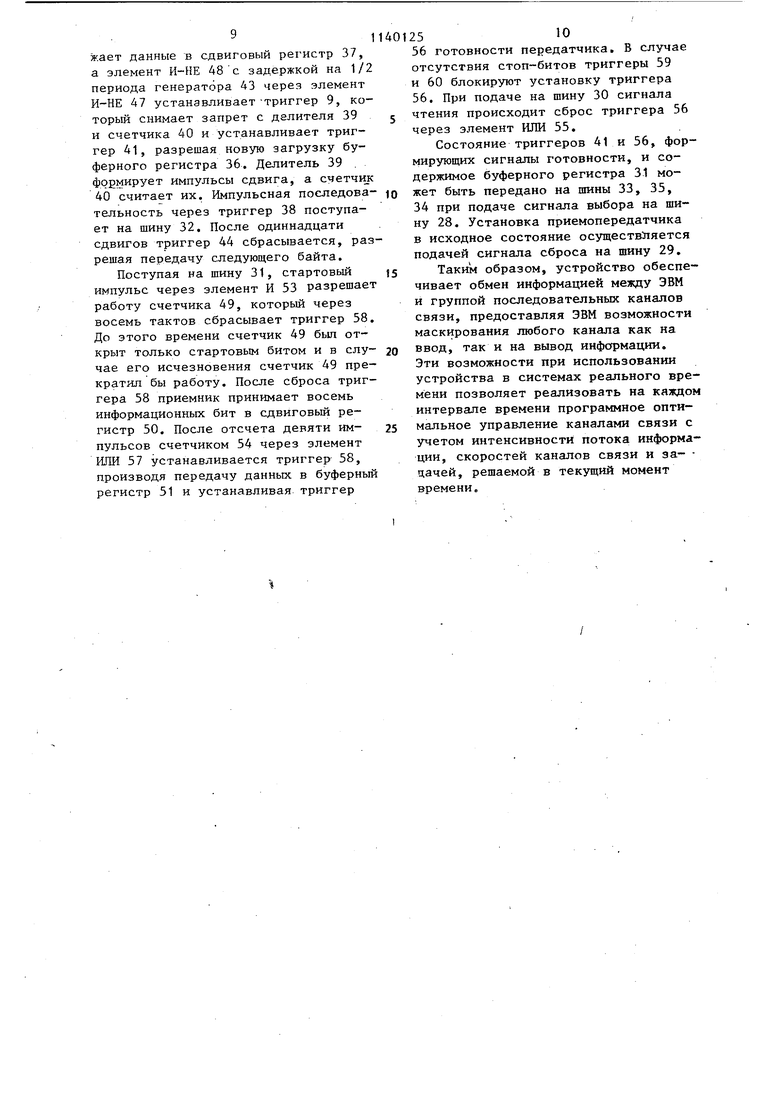

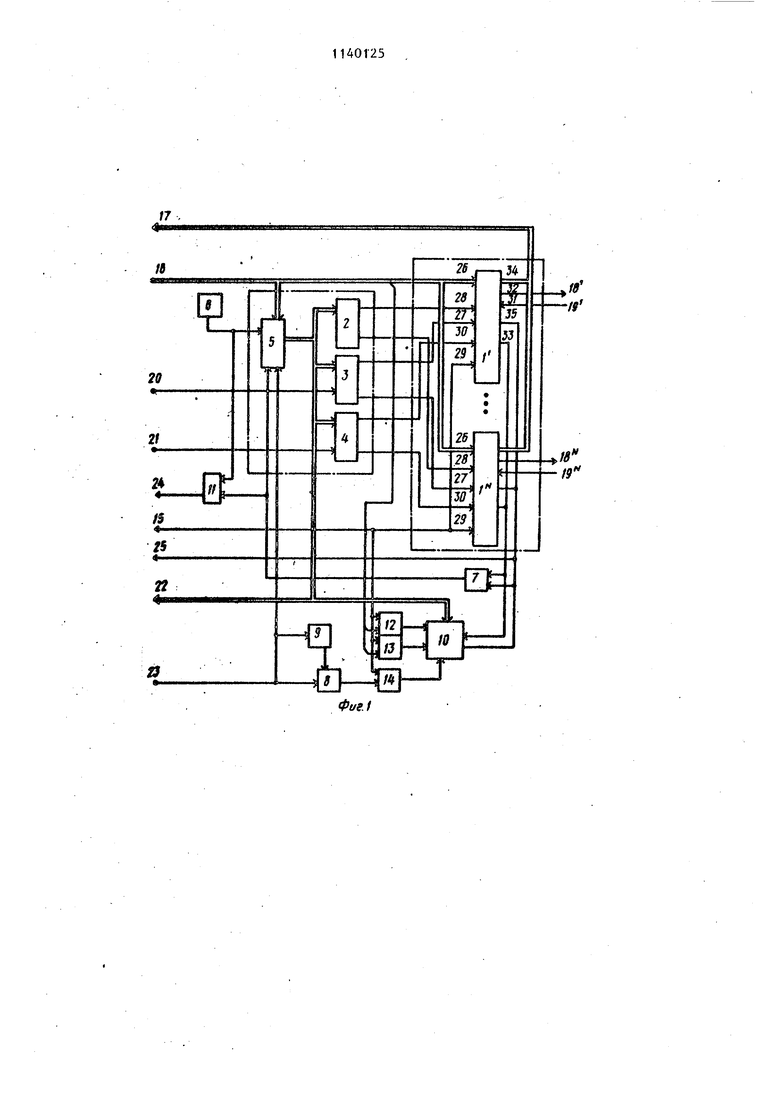

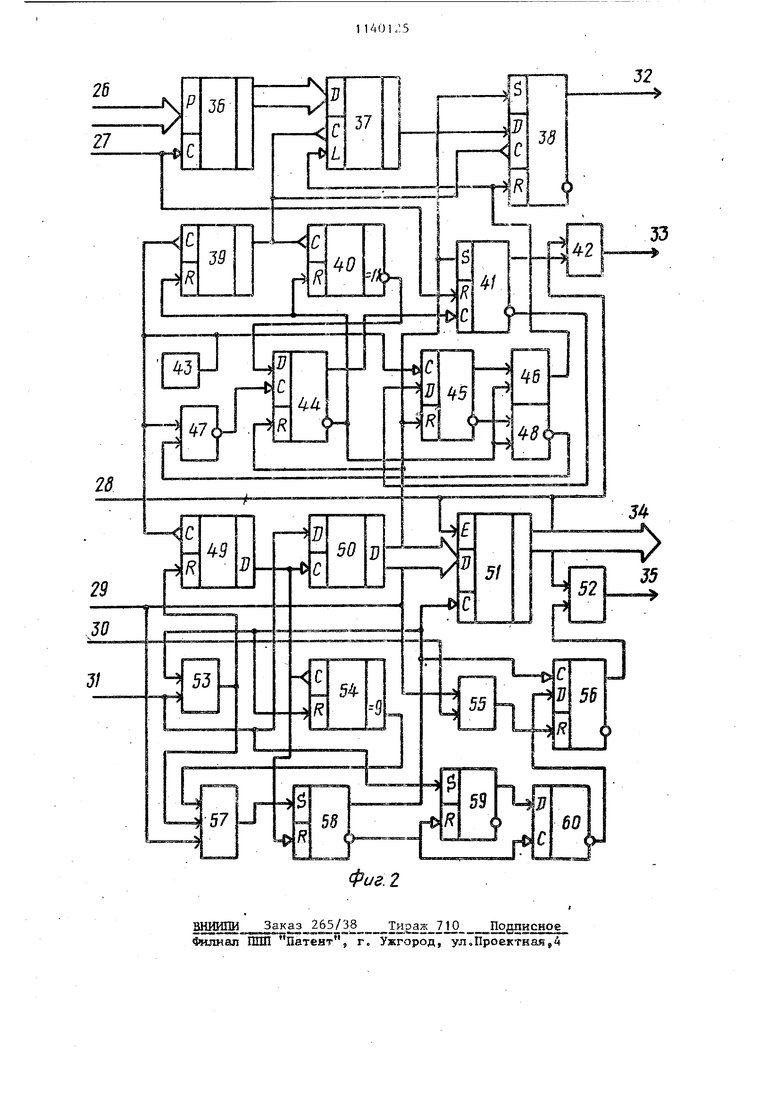

На фиг, 1 представлена блок-схема устройства; на фиг, 2 - функциональная схема одного канала (приемопередатчика) многоканального бло ка обратимого преобразования параллельного кода в последовательный.

Устройство содержит (фиг, 1) приемопередатчики 1, образующие многоканальный блок, обратимого преобразования параллельного кода в последовательный, распределитель управляющих сигналов, состоящий из дешифра256

тора 2 выборки, дешифратора 3 сигнала записи, дешифратора 4 сигнала чтения и счетчика 5, генератор 6 импульсов, элемент ИЛИ 7, элемент И 8, элемент задержки 9, память 10 масок прерывания, триггер 11, элементы ЗАПРЕТ 12 и 13 группы, элемент ИЛИ 14, шину 15 сброса, шины 16 и 17 информационных входа и выхода параллельного кода устройства, шины 18 и 19 групп информационных выходов и выходов последовательного кода устройства, шины 20 и 21 входа сигналов режима записи и чтения, шины 22 выхода номера канала устройства, шину 23 входа записи маски прерывания устройства, шину 24 запроса прерывания и шину 25 адреса вектора прерывания устройства. Шинами 16, 17, 2025 устройство подключается к ЭВМ, а кажд.ая пара шин 18 и 19 с одним и тем же индексом - к соответствующему каналу связи.

На фиг,1 обозначены также шины приемопередатчиков 1: шина 26 входов параллельного кода, шина 27 записи параллельного кода, шина 28 входов выборки приемопередатчика 1, шина 29 сброса приемопередатчика 1, шина 30 чтения параллельного кода, шины 3-1 входа и выхода последова-, тельного кода, шина 33 синхронизи-. рующего выхода вывода последовательного кода (готовность передатчика) приемопередатчика 1, шина 34 выхода параллельного кода и шина 35 синхронизирующего выхода ввода последовательного кода (готовность приемника) приемопередатчика 1,

Приемопередатчики 1 осуществляют преобразование машинного слова параллельного кода в последоватепьной код, например, имеющий структуру; стартовый бит + 8 информационных бит 2 стоповых бита,

В качестве приемопередатчиков 1 могут быть использованы приемник и передатчик, описанные в 2.

Приемопередатчик 1 может, например, содержать (фиг. 2) первый буферный регистр 36, первый сдвиговый регистр 37, первый триггер 38, делитель 39 частоты, первый счетчик 40 импульсов, второй триггер 41, первый магистральный усилитель 42, генератор 43 импульсов, третий 44 и четвертый 45 триггеры, первые элементы И 46 и элемент. И-НЕ 47, второй элемент И-НЕ 48, третий счетчик 49 импульсов, второй сдвиговый регистр 50, второй буферный регистр 51, вто рой магистральный усилитель 52, вто рой элемент И 53, второй счетчик 54 импульсов, первый элемент ИЛИ 55, пятый триггер 56, второй элемент ИЛИ 57,шестой 58, седьмой 59 и восьмой 60 триггеры. Устройство работает следующим образом. Обмен информацией возможен только по прерыванию, возбуждаемому устройством сигнала на шипе 24, Уст ройство может вызвать прерывание по вводу (присутствует сигнал на ши не 25) и прерывание по вводу (отсут ствует сигнал на шине 25). Счетчик 5, считая импульсы генератора 6, сканирует память 10 и последовательно выбирает с помощьюдешифратора 2 приемопередатчики 1, подключая их шины 34 к шине 17, и шины 33 и 35 к входам элемента ИЛИ 7 Так как к этим же входам подключены выходы памяти 10, сигнал на выходе элемента ИЛИ 7 может появиться толь ко при наличии разрешающего сигнала из памяти 10. Запись информации в память 10 и установка счетчика 5 осуществляется сигналом на шине 23, Лри этом снача ла в счетчик 5 из младших разрядов шины 16 заносится номер канала, а затем с некоторой задержкой созда ваемой элементом задержки 9, по адресу этого канала в память 10 записываются два старших разряда шины 16, разрешающие или запрещающие прерывания соответственно по вводу и выводу для данного канала. Дпя ввода информации по К-му ка,налу () программа, разрешает прерывания от приемника К-го приемо передатчика 1 . Приемник приемопередатчика 1 принимает поступающую на шину 19 старт-стопную последовательность импульсов, преобразуя ее в параллельный код а после при- ема стоп-бита записывает принятый байт информации в свой буферньй регистр 51, устанавливает флаг готовности приемника на шине 35 и перехо дит к приему следующего байта. Когд на выходе счетчика 5 появляется номер канала К, сигнал готовности при емника через элемент ИЛИ 7 поступает на вход запрета счетчика 5, блокируя его дальнейшее продвижение. Следующим импульсом генератора 6 ус- танашшвается триггер 11 , вызывая прерывание по вводу, так как присутствует сигнал на шине 25, Подпро грамма обработки прерываний считывает номер канала с выходной шинь 22 и данные с выходной ишны 17 и выдает сигнал чтения на шину 21, который через дешифратор 4 сбрасывает флаг готовности К-го приемопередатчика 1 , разрешая да.пьнейшее продвижение счетчика 5. Лри выводе данных по К-му каналу программа разрешает прерывания по выводу К-му приемопередатчика 1. Если в данный момент буферный регистр 36 приемопередатчика 1 свободен, то при появлении на выходе счетчика 5 номера К возникает прерывание . по выводу.Подпрограмма обработки прерывания считывает с. шины 22 номер канала и по шине 16 передает байт информации, сопровождая его сигналом записи по шине 205 который через дешифратор 3 заносит передаваемый байт в буферный регистр 36 и сбрасывает флаг готовности передатчика на шине 33, разрешая дальнейшее продвижение счетчика 5, Передатчик преобразз ет байт ин-формации в старт-стопн то последовательность импульсов, передаваемую на линейный выход 18, Для установки устройства в исходное состояние на шину 15 подается сигнал сброса, длительность которого должна быть больше времени сканирования памяти 10. При этом сбрасьюаются все приемопередатчики 1, через элемент ИЛИ 14 в память 10 подается сигнал разрешения записи, элементы ЗАПРЕТ 12 и 13 блокируют информационные входы памяти 10, После окончания сброса в памяти 10 записаны нули и поэтому выработка всех запросов прерывания от устройства запрещена. Приемопередатчик 1 работает следуюпщм образом. .При поступлении сигнала записи по шине 27 данные с шин 26 загружа-ются-в буферный регистр 36.и сбрасывается триггер 41, отражающий состояние буферного регистра 36, После асинхронного заполнения буферного регистра 36 синхронно с частотойгенератора 43 уста;назливаетс.я триг-гер 45, при этом элемент И 46 загруу

жает данные в сдвиговый регистр 37, а элемент И-НЕ 48 с задержкой на 1/2 периода генератора 43 через элемент И-НЕ 47 устанавливает-триггер 9, который снимает запрет с делителя 39 и счетчика 40 и устанавливает триггер 41, разрешая новую загрузку буферного регистра 36, Делитель 39 формирует импульсы сдвига, а счетчи к 40 считает их. Импульсная последовательность через триггер 38 поступает на шину 32, После одиннадцати сдвигов триггер 44 сбрасывается, разрешая передачу следующего байта.

Поступая на шину 31, стартовый импульс через элемент И 53 разрешает работу счетчика 49, который через восемь тактов сбрасывает триггер 58, До этого времени счетчик 49 был открыт только стартовым битом и в случае его исчезновения счетчик 49 прекратил бы работу. После сброса триггера 58 приемник принимает восемь информационных бит в сдвиговый регистр 50, После отсчета девяти импульсов счетчиком 54 через элемент ИЛИ 57 устанавливается триггер- 58, производя передачу данных в буферный регистр 51 и устанавливая триггер

4012510

56 готовности передатчика. В случае отсутствия стоп-битов триггеры 59 и 60 блокируют установку триггера 56, При подаче на шину 30 сигнала 5 чтения происходит сброс триггера 56 через элемент ИЛИ 55.

Состояние триггеров 41 и 56, формирующих сигналы готовности, и содержимое буферного регистра 31 может быть передано на шины 33, 35, 34 при подаче сигнала выбора на шину 28, Установка приемопередатчика в исходное состояние осуществляется подачей сигнала сброса на шину 29.

5 Таким образом, устройство обеспечивает обмен информацией между ЭВМ и группой последовательных каналов связи, предоставляя ЭВМ возможности маскирования любого канала как на

0 ввод, так и на вывод инфсгрмадии. Эти возможности при использовании устройства в системах реального времени позволяет реализовать на каждом интервале времени программное опти5 мальное управление каналами связи с учетом интенсивности потока информации, скоростей каналов связи и за цачей, решаемой в текущий момент времени.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с дискретными каналами связи | 1980 |

|

SU907538A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-02-15—Публикация

1983-04-13—Подача