Предлагаемое изобретение относится к области электротехники, радиотехники, связи и может использоваться в структуре различных интерфейсов, измерительных приборах.

В устройствах информационно-измерительной техники, связи, автоматики и радиотехники широкое применение находят резистивные делители напряжения - аттенюаторы (AT), обеспечивающие заданное деление (ослабление) входного напряжения (uвх) [1-16]. С повышением частоты uвх в таких аттенюаторах возникают существенные погрешности передачи сигнала, обусловленные влиянием паразитного конденсатора C0 цепи нагрузки. Снижение этих погрешностей - одна из проблем современной информационно-измерительной техники, которая решается сегодня как за счет схемотехники AT, так и за счет конструктивных особенностей входных цепей (например, специальных «щупов» СВЧ-вольтметров, осциллографов, антенных систем радиоприемников и т.п.).

В связи с достаточно широким применением резистивных аттенюаторов в различных областях техники они присутствуют в различных классах МПК (H03H 7/24, A61B, G01R 31/02, H01P 1/22, H03K 5/08, H03L 5/00, G01R 27/00, G05F 3/00, H01H 47/00, H03G 3/20).

Предлагаемое схемотехническое решение относится к подклассу AT устройств, в которых входное сопротивление аттенюатора (Rвх) с увеличением частоты не уменьшается до нуля, а принимает значение, определяемое входным резистором AT. Данное ограничение весьма существенно для многих применений AT в электро-радиотехнических устройствах и системах связи, где уменьшение Rвх до нуля недопустимо.

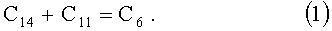

Ближайшим прототипом заявляемого устройства является резистивный делитель напряжения фиг.1, представленный в патентной заявке US 2012/0086528 fig.8B. Он имеет вход 1 и выход 2, между которыми включен первый 3 резистор, второй 4 резистор, включенный между выходом устройства 2 и общей шиной 5 для входных и выходных сигналов, конденсатор цепи нагрузки 6.

Существенный недостаток аттенюатора-прототипа фиг.1 состоит в том, что с повышением частоты входного сигнала его коэффициент передачи существенно уменьшается из-за шунтирующего влияния паразитной емкости нагрузки. Это ограничивает частотный диапазон аттенюатора.

Кроме этого, при импульсном изменении входного напряжения, например, на 2B, время установления переходного процесса в AT-прототипе фиг.1 недопустимо велико для многих применений, что ограничивает быстродействие аналого-цифровых интерфейсов на его основе.

Основная задача предлагаемого изобретения состоит в существенном расширении диапазона рабочих частот устройства и повышении его быстродействия при работе с импульсными сигналами большой амплитуды. Причем достижение данных качественных показателей обеспечивается при относительно больших входных сопротивлениях AT в широком диапазоне частот.

Поставленная задача достигается тем, что в аттенюаторе фиг.1, имеющем вход 1 и выход 2, между которыми включен первый 3 резистор, второй 4 резистор, включенный между выходом устройства 2 и общей шиной 5 для входных и выходных сигналов, конденсатор цепи нагрузки 6, предусмотрены новые элементы и связи - в схему введен первый 7 дополнительный транзистор, база которого подключена ко входу 1 устройства, коллектор связан с первой 8 шиной источника питания, а эмиттер подключен ко второй 9 шине источника питания через первый 10 токостабилизирующий двухполюсник и связан с выходом устройства 2 через первый 11 корректирующий конденсатор.

Кроме этого, в соответствии с п.2 формулы изобретения в схему введен второй 12 дополнительный транзистор, база которого подключена ко входу 1 устройства, коллектор связан со второй 9 шиной источника питания, а эмиттер подключен к первой 8 шине источника питания через второй 13 токостабилизирующий двухполюсник и связан с выходом устройства 2 через второй 14 корректирующий конденсатор.

На фиг.1 приведена схема аттенюатора-прототипа.

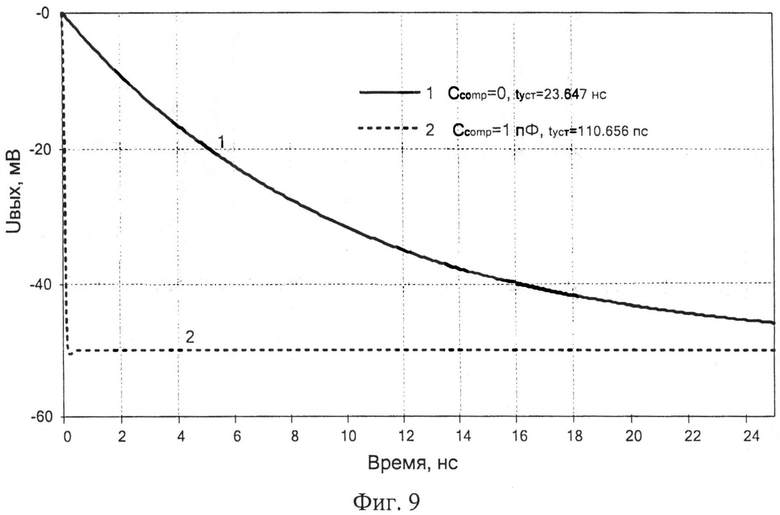

На фиг.2 представлена схема заявляемого устройства в соответствии с п.1 и п.2 формулы изобретения.

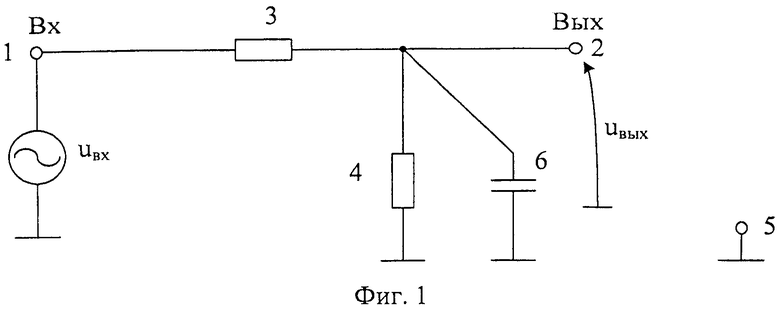

На фиг.3 представлена схема аттенюатора фиг.2 в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НЛП «Пульсар» при конденсаторе цепи нагрузки C6=C0=2 пф и R3=10 кОм, R4=10 кОм.

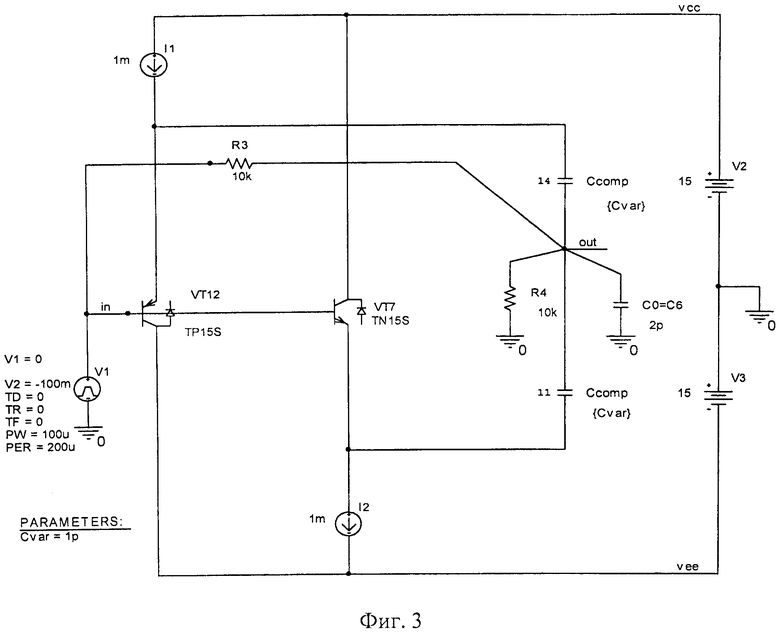

На фиг.4 показана зависимость коэффициента передачи по напряжению AT фиг.3 от частоты при разных значениях емкости корректирующих конденсаторов C14=C11=Ccom=Cvar и при логарифмическом масштабе по оси «Y».

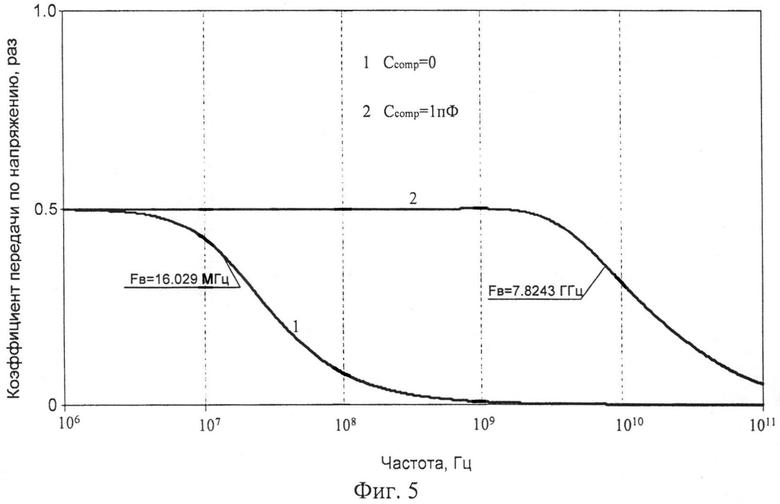

На фиг.5 показана та же (фиг.4) зависимость коэффициента передачи по напряжению AT от частоты, но при линейном масштабе по оси «Y». Из данного графика следует, что верхняя граничная частота AT фиг.3 (фиг.2) улучшается в 481 раз.

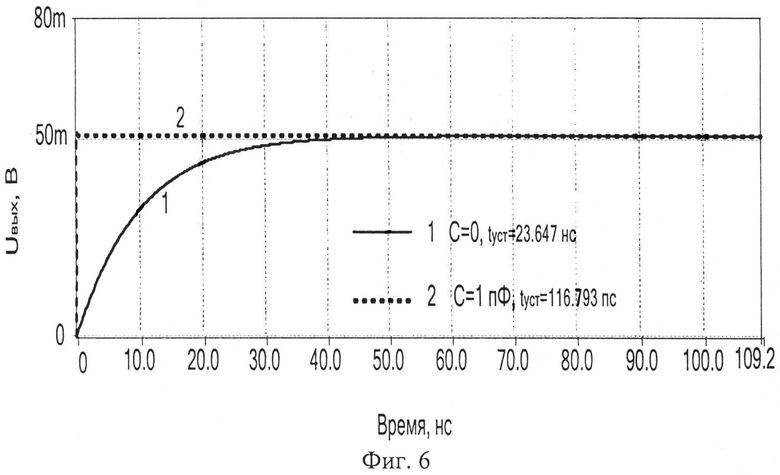

На фиг.6 приведена зависимость выходного напряжения AT фиг.3 от времени при разных значениях емкости корректирующих конденсаторов C14=C11=Ccom=Cvar для положительного импульса входного напряжения с амплитудой Uвх=100 мВ. Из данных графиков следует, что время установления переходного процесса в схеме фиг.3 (фиг.2) улучшается в 203 раза.

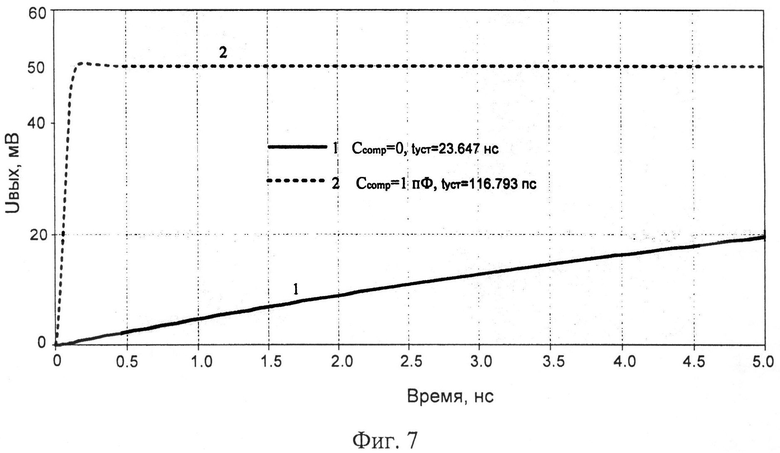

На фиг.7 приведена зависимость выходного напряжения от времени AT фиг.3 при разных значениях емкости корректирующих конденсаторов C14=C11=Ccom=Cvar для положительного импульса (Uвх=100 мВ) в увеличенном масштабе.

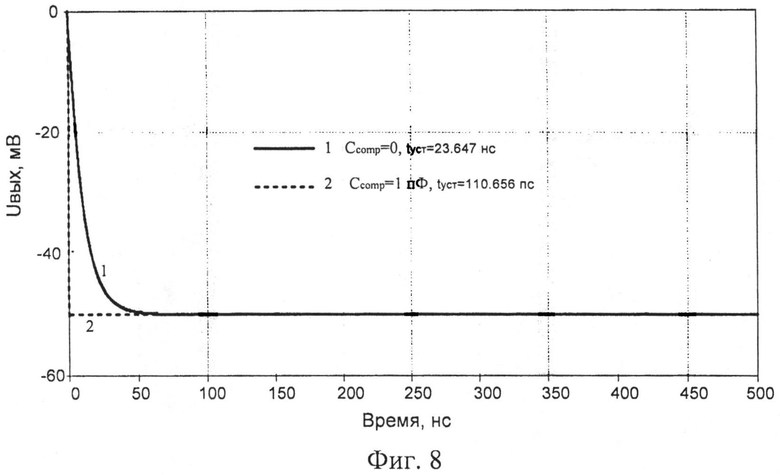

На фиг.8 приведена зависимость выходного напряжения AT фиг.3 от времени при разных значениях емкости корректирующего конденсатора C14=C11=Ccom=Cvar для отрицательного входного импульса Uвх=-100 мВ.

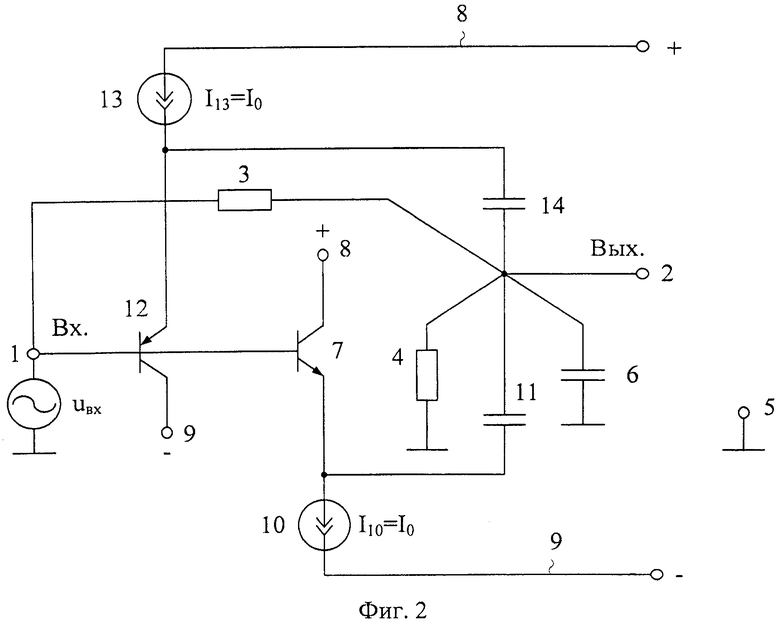

На фиг.9 приведена зависимость выходного напряжения AT фиг.3 от времени при разных значениях емкости корректирующего конденсатора C14=C11=Ccom=Cvar для отрицательного входного импульса Uвх=-100 мВ в увеличенном масштабе.

Быстродействующий аттенюатор для входных цепей аналого-цифровых интерфейсов фиг.2 имеет вход 1 и выход 2, между которыми включен первый 3 резистор, второй 4 резистор, включенный между выходом устройства 2 и общей шиной 5 для входных и выходных сигналов, конденсатор цепи нагрузки 6. В схему введен первый 7 дополнительный транзистор, база которого подключена ко входу 1 устройства, коллектор связан с первой 8 шиной источника питания, а эмиттер подключен ко второй 9 шине источника питания через первый 10 токостабилизирующий двухполюсник и связан с выходом устройства 2 через первый 11 корректирующий конденсатор.

На фиг.2 в соответствии с п.2 формулы изобретения в схему введен второй 12 дополнительный транзистор, база которого подключена ко входу 1 устройства, коллектор связан со второй 9 шиной источника питания, а эмиттер подключен к первой 8 шине источника питания через второй 13 токостабилизирующий двухполюсник и связан с выходом устройства 2 через второй 14 корректирующий конденсатор.

Рассмотрим работу устройства фиг.2.

Коэффициент передачи по напряжению аттенюатора фиг.2 не уменьшается с повышением частоты. Это обусловлено эффектом компенсации влияния емкости конденсатора 6 цепи нагрузки C6 на амплитудно-частотную характеристику AT корректирующими конденсаторами 14 и 11 при выполнении условия

При работе с импульсными сигналами также должно выполняться условие (1). За счет применения разнотипных транзисторов 7 и 12 (n-p-n и p-n-p) обеспечивается повышение быстродействия при импульсных входных напряжениях разных полярностей.

Приведенные на фиг.4 - фиг.9 результаты компьютерного моделирования позволяют сделать следующие выводы:

1. Для выбранных транзисторов верхняя граничная частота коэффициента передачи fв предлагаемого AT увеличивается в 481 раз.

2. Максимальная скорость нарастания выходного напряжения схемы AT фиг.2 увеличивается в 203 раза.

3. Входное сопротивление заявляемого AT не уменьшается в широком диапазоне частот и для выбранных параметров схемы удовлетворяет условию Rвх>R3=10 кОм.

Таким образом, предлагаемый аттенюатор характеризуется существенными преимуществами по быстродействию и широкополосности, что позволяет рекомендовать его для входных цепей быстродействующих интерфейсов различного назначения.

Источники информации

1. Патент US 5.867.018

2. Патент US 5.363.070 fig.2а

3. Патент US 4.912.394

4. Патент US 8.076.995

5. Патент US 4.050.055 fig.5

6. Патент US 4.198.988 fig.1

7. Патентная заявка US 2007/0176664 fig.2

8. Патент US 4.839.611 fig.2

9. Патент US 4.670.723 fig.2

10. Патент US 4.272.739 fig.1

11. Патент JP 10-211-0068595

12. Патент JP 2010-252241

13. Патент ЕР 2337219% fig.2

14. Патент ЕР 0753937 fig.1

15. Патент ЕР 0612982

16. Патент US 7.477.085 fig.1

| название | год | авторы | номер документа |

|---|---|---|---|

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ДИФФЕРЕНЦИРУЮЩЕЙ ЦЕПЬЮ КОРРЕКЦИИ | 2018 |

|

RU2669075C1 |

| УПРАВЛЯЕМЫЙ ИЗБИРАТЕЛЬНЫЙ УСИЛИТЕЛЬ | 2012 |

|

RU2520418C2 |

| ИЗБИРАТЕЛЬНЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ НЕИНВЕРТИРУЮЩЕГО УСИЛИТЕЛЯ ТОКА | 2012 |

|

RU2488955C1 |

| СВЕРХБЫСТРОДЕЙСТВУЮЩИЙ ПАРАЛЛЕЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С ДИФФЕРЕНЦИАЛЬНЫМ ВХОДОМ | 2013 |

|

RU2536377C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ДИФФЕРЕНЦИРУЮЩИМИ ЦЕПЯМИ КОРРЕКЦИИ | 2018 |

|

RU2684500C1 |

| ИЗБИРАТЕЛЬНЫЙ УСИЛИТЕЛЬ | 2012 |

|

RU2507675C1 |

| ИЗБИРАТЕЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ ТОКОМ ПОТРЕБЛЕНИЯ ДЛЯ SiGe ТЕХПРОЦЕССОВ | 2012 |

|

RU2515544C2 |

| ИЗБИРАТЕЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2468498C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2017 |

|

RU2668968C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ИСТОКОВЫЙ ПОВТОРИТЕЛЬ НАПРЯЖЕНИЯ | 2013 |

|

RU2536671C1 |

Изобретение относится к области электротехники, радиотехники, связи и может использоваться в структуре различных интерфейсов, измерительных приборах. Технический результат заключается в расширении диапазона рабочих частот устройства и повышении его быстродействия при работе с импульсными сигналами большой амплитуды. Быстродействующий аттенюатор для входных цепей аналого-цифровых интерфейсов содержит вход (1) и выход (2), между которыми включен первый (3) резистор, второй (4) резистор, включенный между выходом устройства (2) и общей шиной (5) для входных и выходных сигналов, первый (6) конденсатор цепи нагрузки. В схему введен первый (7) дополнительный транзистор, база которого подключена ко входу (1) устройства, коллектор связан с первой (8) шиной источника питания, а эмиттер подключен ко второй (9) шине источника питания через первый (10) токостабилизирующий двухполюсник и связан с выходом устройства (2) через первый (11) корректирующий конденсатор. 1 з.п. ф-лы, 9 ил.

1. Быстродействующий аттенюатор для входных цепей аналого-цифровых интерфейсов, содержащий вход (1) и выход (2), между которыми включен первый (3) резистор, второй (4) резистор, включенный между выходом устройства (2) и общей шиной (5) для входных и выходных сигналов, первый (6) конденсатор цепи нагрузки, отличающийся тем, что в схему введен первый (7) дополнительный транзистор, база которого подключена ко входу (1) устройства, коллектор связан с первой (8) шиной источника питания, а эмиттер подключен ко второй (9) шине источника питания через первый (10) токостабилизирующий двухполюсник и связан с выходом устройства (2) через первый (11) корректирующий конденсатор.

2. Быстродействующий аттенюатор для входных цепей аналого-цифровых интерфейсов по п.1, отличающийся тем, что в схему введен второй (12) дополнительный транзистор, база которого подключена ко входу (1) устройства, коллектор связан со второй (9) шиной источника питания, а эмиттер подключен к первой (8) шине источника питания через второй (13) токостабилизирующий двухполюсник и связан с выходом устройства (2) через второй (14) корректирующий конденсатор.

| ДИСКРЕТНЫЙ ШИРОКОПОЛОСНЫЙ АТТЕНЮАТОР СВЧ | 2011 |

|

RU2469443C1 |

| Управляемый аттенюатор | 1986 |

|

SU1356206A1 |

| Аттенюатор | 1974 |

|

SU508902A1 |

| Изложница с суживающимся книзу сечением и с вертикально перемещающимся днищем | 1924 |

|

SU2012A1 |

| Изложница с суживающимся книзу сечением и с вертикально перемещающимся днищем | 1924 |

|

SU2012A1 |

Авторы

Даты

2014-10-10—Публикация

2013-03-05—Подача