Изобретение относится к области аналоговой микроэлектроники и может быть использовано в аналоговых интерфейсах и устройствах преобразования сигналов, в том числе работающих в диапазоне низких температур.

Быстродействие операционных усилителей (ОУ), которое характеризуется максимальной скоростью нарастания выходного напряжения (ϑвых.) и временем установления переходного процесса (tуст.), определяет динамические параметры многих аналоговых интерфейсов датчиков, буферных каскадов, АЦП, драйверов линий связи и т.п.

В современной радиоэлектронной аппаратуре находят применение операционные усилители (ОУ), реализуемые на основе двухканальной структуры входного каскада (dual-input-stage), содержащего два параллельно-включенных по входу дифференциальных усилителя на однотипных транзисторах [1-14]. Причем структура dual-input-stage реализуется как на биполярных [1-5], так и на полевых [6-14] транзисторах и часто используется совместно с так называемыми «перегнутыми» каскодами [15-28], реализуемыми на биполярных [15-17] или полевых [18-28] транзисторах. Благодаря многоканальности и применению высокочастотного «перегнутого» каскода такое схемотехническое решение наиболее популярно как в зарубежных, так и в российских широкополосных аналоговых микросхемах, имеющих повышенные значения частоты единичного усиления. На основе ОУ данного класса возможно построение как быстродействующих, так и прецизионных усилителей.

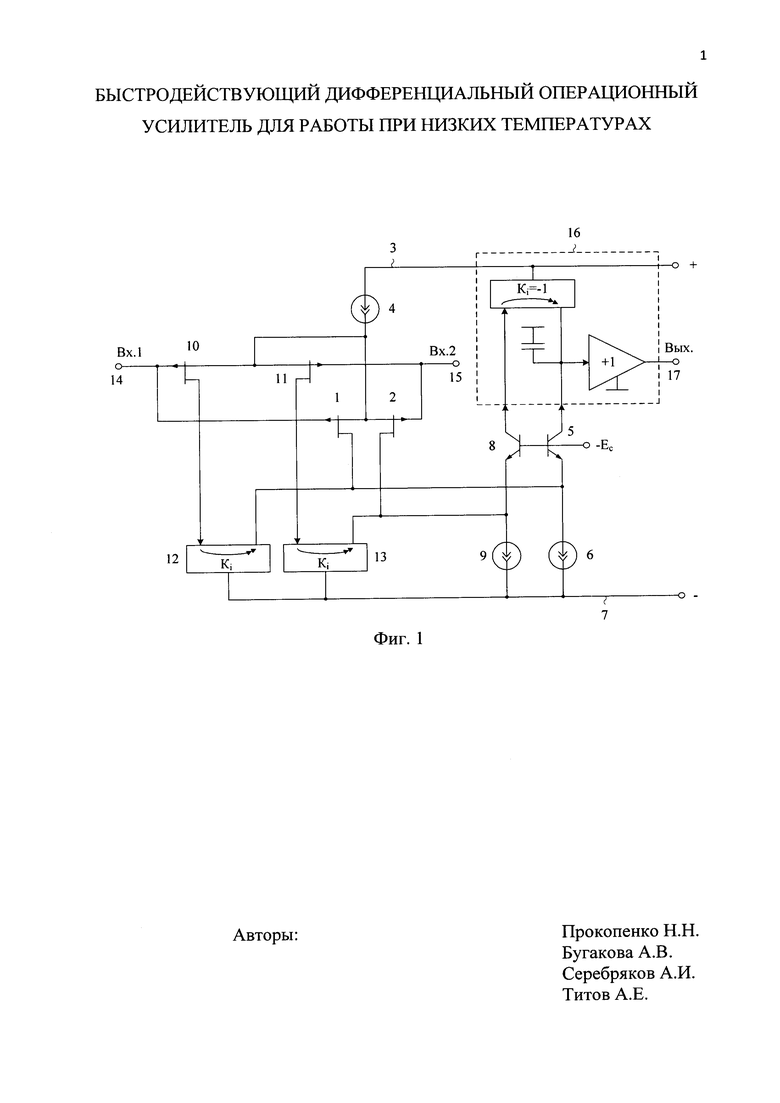

Ближайшим прототипом (фиг. 1) заявляемого устройства является дифференциальный операционный усилитель по патенту RU 2595923. Он содержит (фиг. 1) первый 1 и второй 2 входные полевые транзисторы, объединенные истоки которых связаны с первой 3 шиной источника питания через первый 4 токостабилизирующий двухполюсник, сток первого 1 входного полевого транзистора соединен с эмиттером первого 5 выходного транзистора и через второй 6 токостабилизирующий двухполюсник соединен со второй 7 шиной источника питания, сток второго 2 входного полевого транзистора соединен с эмиттером второго 8 выходного транзистора и через третий 9 токостабилизирующий двухполюсник связан со второй 7 шиной источника питания, третий 10 и четвертый 11 входные полевые транзисторы с объединенными истоками, причем сток третьего 10 входного полевого транзистора соединен со входом первого 12 усилителя тока, согласованного со второй 7 шиной источника питания, сток четвертого 11 входного полевого транзистора соединен со входом второго 13 усилителя тока, согласованного со второй 7 шиной источника питания, затворы первого 1 и третьего 10 входных полевых транзисторов подключены к первому 14 входу устройства, а затворы второго 2 и четвертого 11 входных полевых транзисторов подключены ко второму 15 входу устройства, причем коллекторы первого 5 и второго 8 выходных транзисторов связаны с дифференциальными входами выходного преобразователя ток-напряжение 16, выход которого 17 является выходом устройства, цепь установления статического режима на базах первого (5) и второго (8) выходных транзисторов.

Существенный недостаток известного ОУ фиг. 1 состоит в том, что при работе транзисторов его входного каскада в режиме микротоков (1÷10 мкА) максимальная скорость нарастания выходного напряжения ОУ получается небольшой (1÷3 В/мкс). Это связано с тем, что известная схема ОУ фиг. 1 предназначена для работы с сильноточными статическими режимами входных транзисторов (Iс=1÷10 мА).

Основная задача предполагаемого изобретения состоит в повышении (на 1-2 порядка) максимальной скорости нарастания выходного напряжения ОУ при работе его входных полевых транзисторов 1, 2, 10, 11 с микроамперными статическими токами (1÷10 мкА), т.е. в энергоэкономичном режиме.

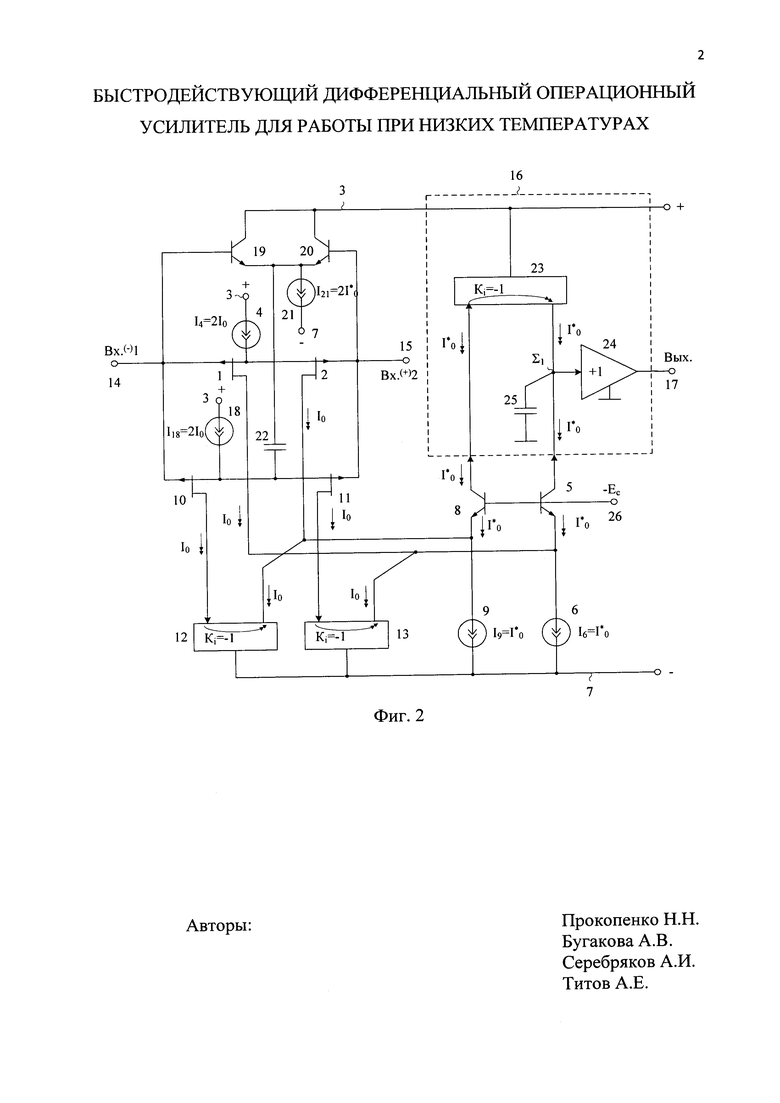

Поставленная задача достигается тем, что в операционном усилителе фиг. 1, содержащем первый 1 и второй 2 входные полевые транзисторы, объединенные истоки которых связаны с первой 3 шиной источника питания через первый 4 токостабилизирующий двухполюсник, сток первого 1 входного полевого транзистора соединен с эмиттером первого 5 выходного транзистора и через второй 6 токостабилизирующий двухполюсник соединен со второй 7 шиной источника питания, сток второго 2 входного полевого транзистора соединен с эмиттером второго 8 выходного транзистора и через третий 9 токостабилизирующий двухполюсник связан со второй 7 шиной источника питания, третий 10 и четвертый 11 входные полевые транзисторы с объединенными истоками, причем сток третьего 10 входного полевого транзистора соединен со входом первого 12 усилителя тока, согласованного со второй 7 шиной источника питания, сток четвертого 11 входного полевого транзистора соединен со входом второго 13 усилителя тока, согласованного со второй 7 шиной источника питания, затворы первого 1 и третьего 10 входных полевых транзисторов подключены к первому 14 входу устройства, а затворы второго 2 и четвертого 11 входных полевых транзисторов подключены ко второму 15 входу устройства, причем коллекторы первого 5 и второго 8 выходных транзисторов связаны с дифференциальными входами выходного преобразователя ток-напряжение 16, выход которого 17 является выходом устройства, цепь установления статического режима на базах первого (5) и второго (8) выходных транзисторов, предусмотрены новые элементы и связи - объединенные стоки третьего 10 и четвертого 11 входных полевых транзисторов связаны с первой 3 шиной источника питания через первый 18 дополнительный токостабилизирующий двухполюсник, в качестве первого 12 усилителя тока используется инвертирующий усилитель тока, выход которого подключен к эмиттеру второго 8 выходного транзистора, в качестве второго 13 усилителя тока используется инвертирующий усилитель тока, выход которого подключен к эмиттеру первого 5 выходного транзистора, первый 14 вход устройства соединен с базой первого 19 дополнительного транзистора, коллектор которого связан с первой 3 шиной источника питания, второй 15 вход устройства соединен с базой второго 20 дополнительного транзистора, коллектор которого подключен к первой 3 шине источника питания, причем объединенные эмиттеры первого 19 и второго 20 дополнительных транзисторов связаны со второй 7 шиной источника питания через второй 21 дополнительный токостабилизирующий двухполюсник, а между объединенными эмиттерами первого 19 и второго 20 дополнительных транзисторов и объединенными истоками третьего 10 и четвертого 11 входных полевых транзисторов включен дополнительный корректирующий конденсатор 22.

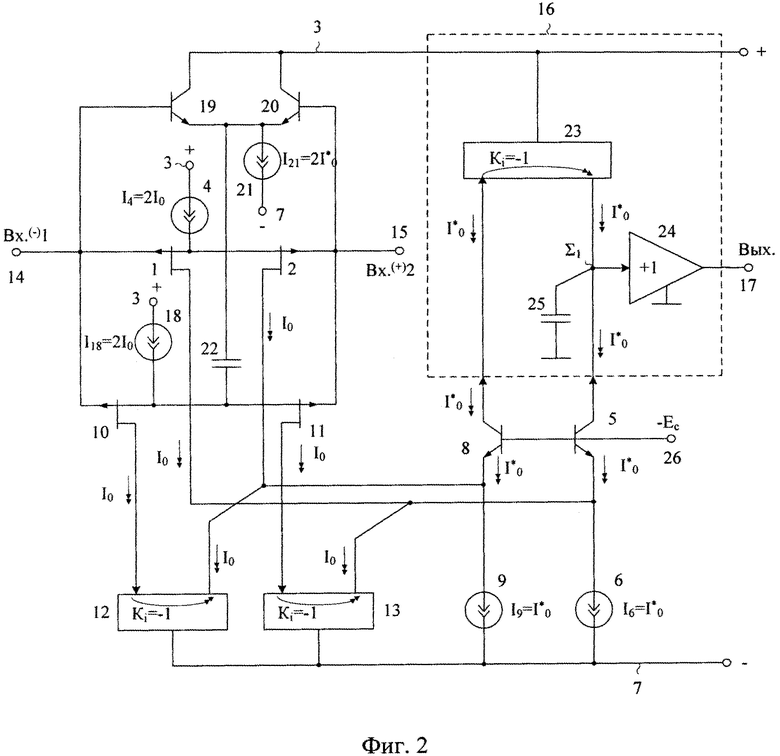

На чертеже фиг. 1 показана схема ОУ-прототипа, а на чертеже фиг. 2 - схема заявляемого устройства в соответствии с п. 1 и п. 2 формулы изобретения.

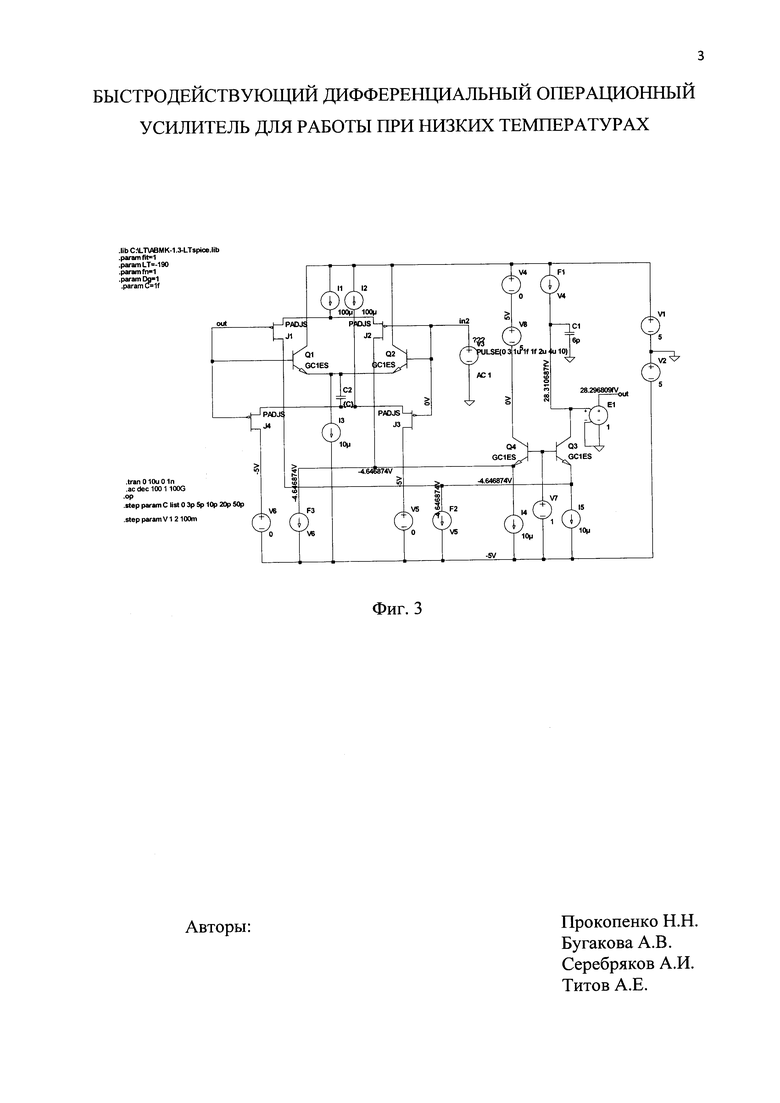

На чертеже фиг. 3 приведена схема заявляемого ОУ в среде LTSpice на низкотемпературных моделях транзисторов BiJFet базового матричного кристалла ABMK_1.7.

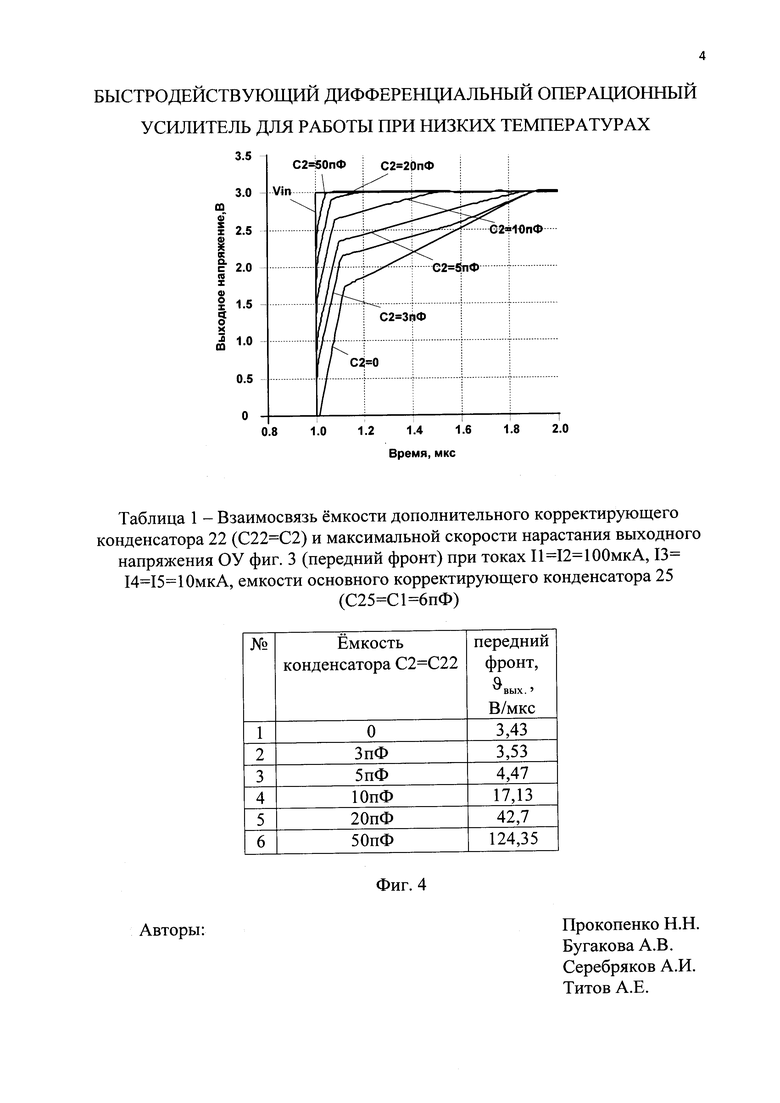

На чертеже фиг. 4 показана осциллограмма выходного напряжения ОУ фиг. 3 (передний фронт) при токах I1=I2=100 мкА, I3=I4=I5=10 мкА, емкости основного корректирующего конденсатора 25 (С25=С1=6пФ), емкости дополнительного корректирующего конденсатора 22 (C22=C2=Cvar) для низкой температуры t=-190°C (ширина импульса 2 мкс, амплитуда входного напряжения 3 В), а также таблица 1, построенная на основе данных графиков.

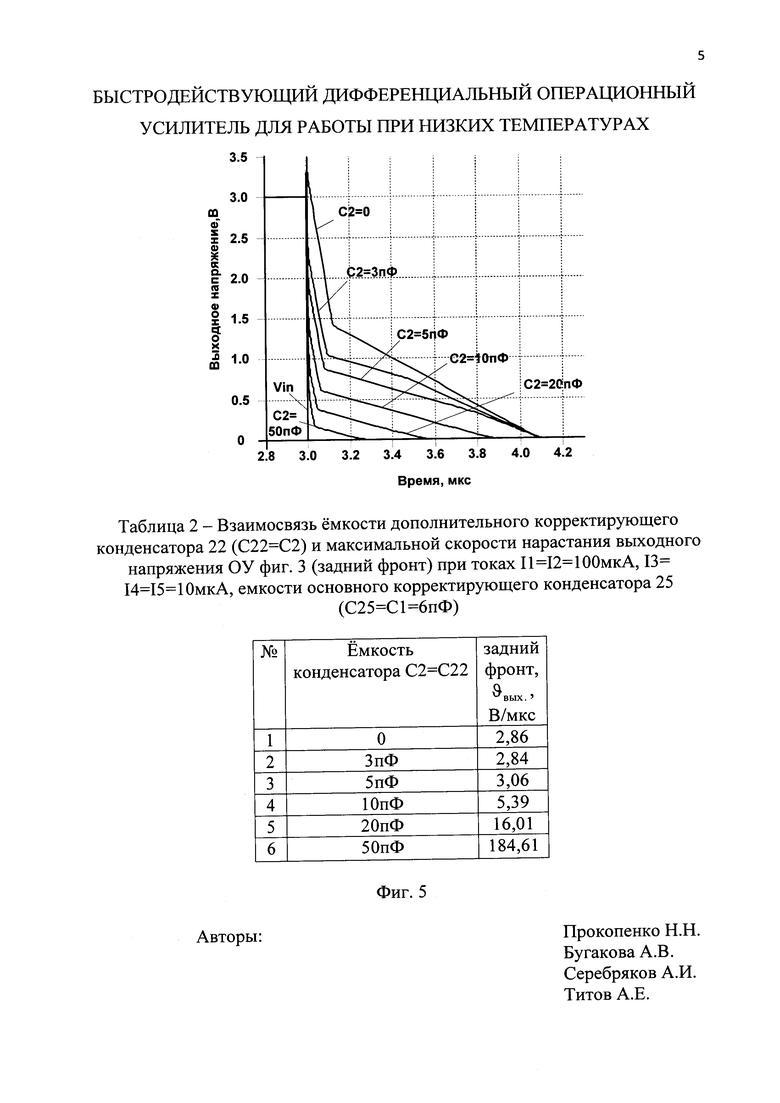

На чертеже фиг. 5 представлена осциллограмма выходного напряжения ОУ фиг. 3 (задний фронт) при токах I1=I2=100 мкА, I3=I4=I5=10 мкА, емкости основного корректирующего конденсатора 25 (С25=С1=6пФ), емкости дополнительного корректирующего конденсатора 22 (C22=C2=Cvar) для низкой температуры t=-190°C (ширина импульса 2 мкс, амплитуда входного напряжения 3 В), а также таблица 2, построенная на основе данных графиков.

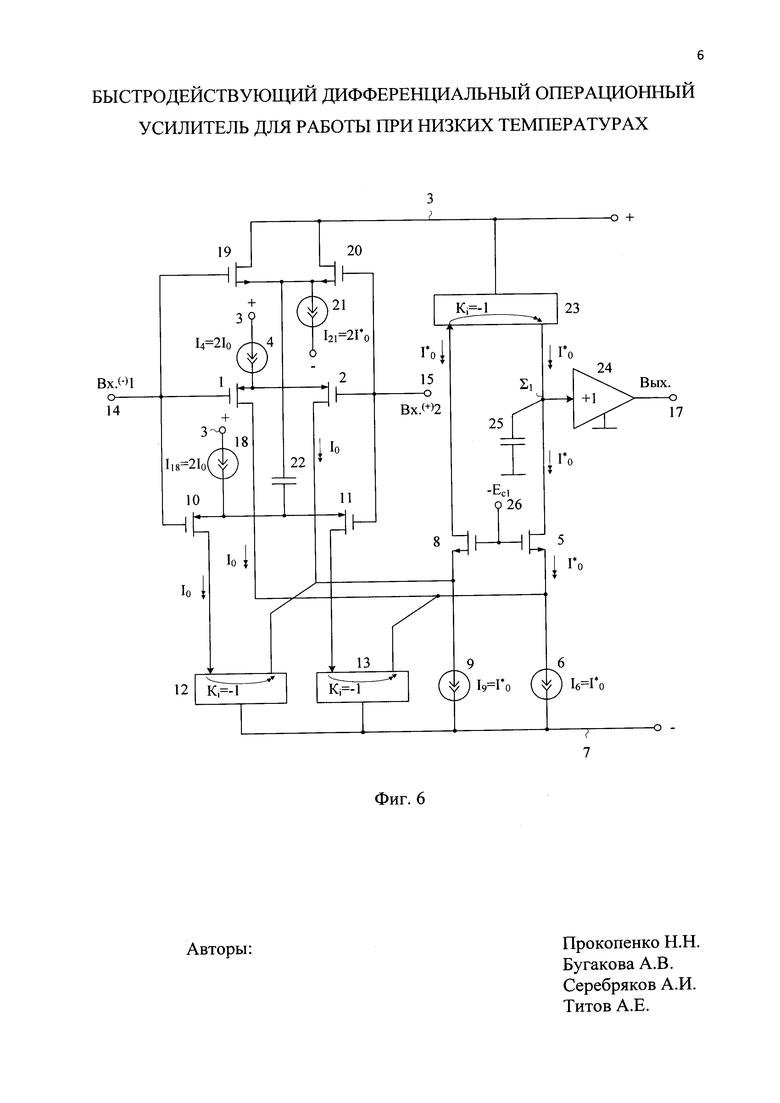

На чертеже фиг. 6 представлена схема ОУ с топологией фиг. 2 для случая, когда в ней используются КМОП транзисторы, у которых, как известно, затвор соответствует базе, сток - коллектору, а исток - эмиттеру биполярного транзистора.

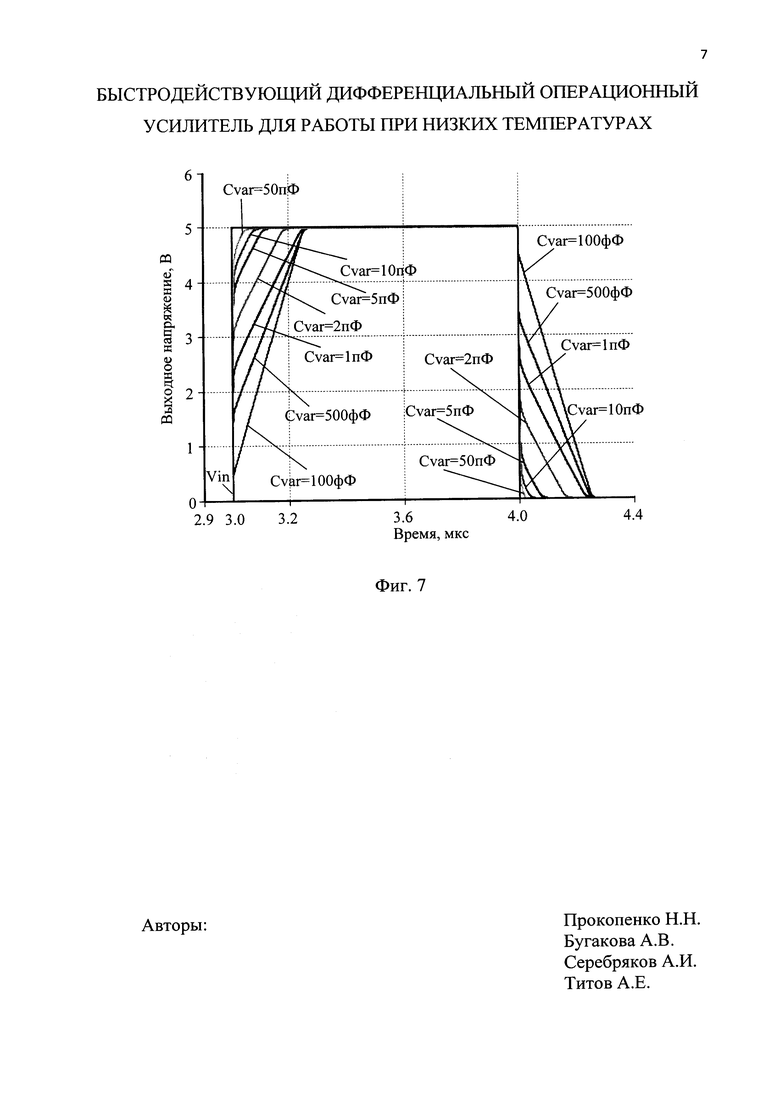

На чертеже фиг. 7 показана осциллограмма входного и выходного напряжений ОУ фиг. 6 (передний и задний фронты) на моделях транзисторов tsmc035_t65 в среде Oread при разных значениях емкости дополнительного корректирующего конденсатора 22 (С22=С2=Ovar), при токах I4=I18=I21=I9=I6=10 мкА, емкости основного корректирующего конденсатора 25 (С25=С1=1пФ), ширине импульса 1 мкс, амплитуде 5В.

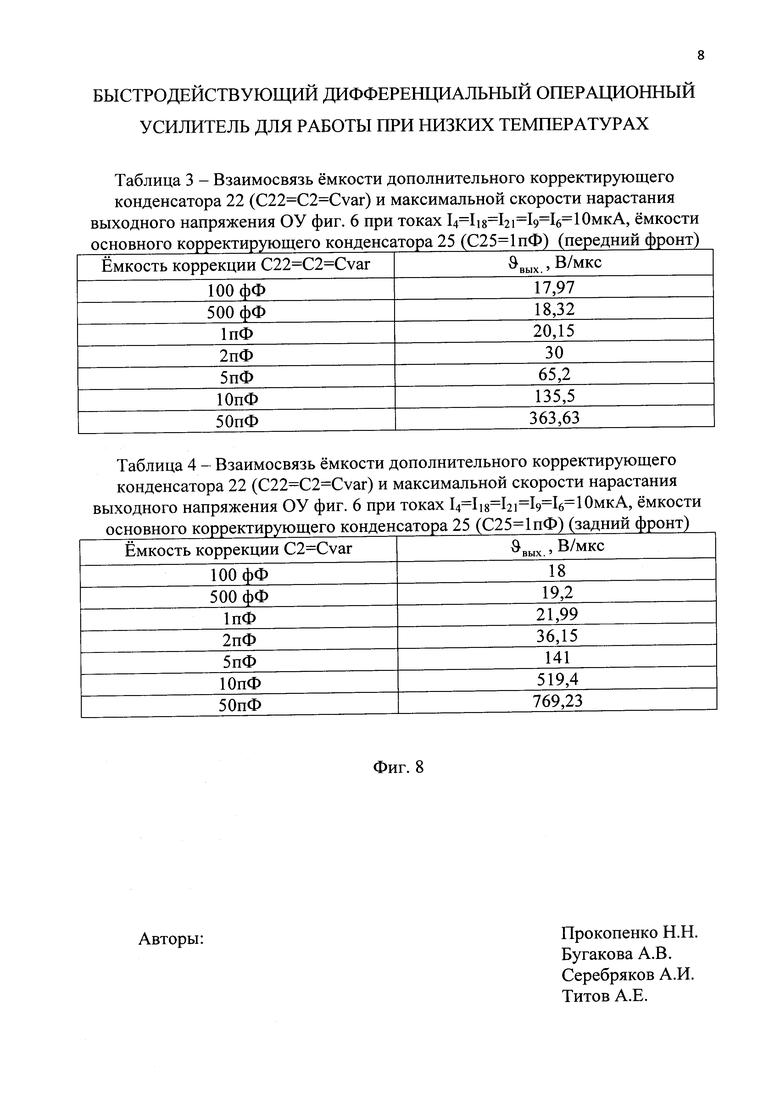

На чертеже фиг. 8 представлены таблицы 3 и 4, характеризующие взаимосвязь емкости дополнительного корректирующего конденсатора 22 (C22=C2=Cvar) и максимальной скорости нарастания выходного напряжения ОУ фиг. 6 при токах I4=I18=I21=I9=I6=10 мкА, емкости основного корректирующего конденсатора 25 (С25=С1=1пФ) (для переднего (табл. 3) и заднего (табл. 4) фронтов выходного напряжения ОУ при импульсном входном сигнале 5В в схеме со 100% отрицательной обратной связью).

Быстродействующий дифференциальный операционный усилитель для работы при низких температурах фиг. 2 содержит первый 1 и второй 2 входные полевые транзисторы, объединенные истоки которых связаны с первой 3 шиной источника питания через первый 4 токостабилизирующий двухполюсник, сток первого 1 входного полевого транзистора соединен с эмиттером первого 5 выходного транзистора и через второй 6 токостабилизирующий двухполюсник соединен со второй 7 шиной источника питания, сток второго 2 входного полевого транзистора соединен с эмиттером второго 8 выходного транзистора и через третий 9 токостабилизирующий двухполюсник соединен со второй 7 шиной источника питания, третий 10 и четвертый 11 входные полевые транзисторы с объединенными истоками, причем сток третьего 10 входного полевого транзистора соединен со входом первого 12 усилителя тока, согласованного со второй 7 шиной источника питания, сток четвертого 11 входного полевого транзистора соединен со входом второго 13 усилителя тока, согласованного со второй 7 шиной источника питания, затворы первого 1 и третьего 10 входных полевых транзисторов подключены к первому 14 входу устройства, а затворы второго 2 и четвертого 11 входных полевых транзисторов подключены ко второму 15 входу устройства, причем коллекторы первого 5 и второго 8 выходных транзисторов связаны с дифференциальными входами выходного преобразователя ток-напряжение 16, выход которого 17 является выходом устройства. Объединенные стоки третьего 10 и четвертого 11 входных полевых транзисторов связаны с первой 3 шиной источника питания через первый 18 дополнительный токостабилизирующий двухполюсник, в качестве первого 12 усилителя тока используется инвертирующий усилитель тока, выход которого подключен к эмиттеру второго 8 выходного транзистора, в качестве второго 13 усилителя тока используется инвертирующий усилитель тока, выход которого подключен к эмиттеру первого 5 выходного транзистора, первый 14 вход устройства соединен с базой первого 19 дополнительного транзистора, коллектор которого связан с первой 3 шиной источника питания, второй 15 вход устройства соединен с базой второго 20 дополнительного транзистора, коллектор которого подключен к первой 3 шине источника питания, причем объединенные эмиттеры первого 19 и второго 20 дополнительных транзисторов связаны со второй 7 шиной источника питания через второй 21 дополнительный токостабилизирующий двухполюсник, а между объединенными эмиттерами первого 19 и второго 20 дополнительных транзисторов и объединенными истоками третьего 10 и четвертого 11 входных полевых транзисторов включен дополнительный корректирующий конденсатор 22.

На чертеже фиг. 2, в соответствии с п. 2 формулы изобретения, выходной преобразователь ток-напряжение 16 содержит токовое зеркало 23, вход которого соединен с первым входом преобразователя ток-напряжение 16 и подключен к коллектору второго 8 выходного транзистора, а выход связан со вторым входом преобразователя ток-напряжение 16 и подключен к коллектору первого 5 выходного транзистора, а также соединен со входом дополнительного буферного усилителя 24 и корректирующим конденсатором 25, причем выход дополнительного буферного усилителя 24 является выходом устройства 17, а объединенные базы первого 5 и второго 8 выходных транзисторов связаны с цепью установления статического режима 26.

Рассмотрим работу предлагаемого ОУ фиг. 2.

В режиме малого сигнала дополнительный корректирующий конденсатор 22 (С22) не влияет на максимальную скорость нарастания выходного напряжения ϑвых и амплитудно-частотную характеристику ОУ, так как он включен между эквипотенциальными (для переменного тока) узлами. При этом за счет каскодных структур передача входного дифференциального сигнала ОУ через первый 1 и второй 2 входные, а также первый 5 и второй 8 выходные транзисторы обеспечивается наибольшие значения частоты единичного усиления ОУ, которая формируется корректирующим конденсатором 25. Это характерная особенность каскодных усилителей.

При большом входном сигнале работа схемы фиг. 2 при 100% отрицательной обратной связи качественно изменяется. В этом режиме при «скачке» положительного входного напряжения на втором 15 входе устройства относительно первого 14 входа в работу включается дополнительный корректирующий конденсатор 22 (С22), второй 20 дополнительный и третий 10 входной полевой транзисторы, первый 12 усилитель тока, второй 8 выходной транзистор и токовое зеркало 24. В конечном итоге это форсирует процесс заряда корректирующего конденсатора 25, что существенно повышает быстродействие ОУ (фиг. 4, таблица 1).

При импульсном отрицательном напряжении на втором 15 входе устройства в работу включается дополнительный корректирующий конденсатор 22 (С22), первый 19 дополнительный транзистор, четвертый 11 входной полевой транзистор, токовое зеркало 12 и первый 5 выходной транзистор. Это значительно ускоряет процесс перезаряда основного корректирующего конденсатора 25, обеспечивающего устойчивость ОУ. Об этом свидетельствуют графики и таблица фиг. 5.

Предлагаемая схема ОУ фиг. 2 может быть также реализована на КМОП транзисторах (фиг. 6). Результаты компьютерного моделирования данной схемы представлены на чертеже фиг. 7, а также в таблицах 3/4 (чертеж фиг. 8). Они показывают, что максимальная скорость нарастания выходного напряжения ОУ на полевых транзисторах фиг. 6 улучшается в 20 раз (передний фронт) и 42 раза (задний фронт). Это позволяет рекомендовать предлагаемое схемотехническое решение ОУ для реализации на основе, например, SiGe технологий, допускающих работу аналоговых схем при низких температурах.

Таким образом, заявляемое устройство обладает существенными преимуществами по сравнению с прототипом.

Источники информации

1. Патент US 4417292, fig. 1

2. Патент SU 1385255

3. Патент US 2005/0285677

4. Патент US 5610547, fig. 28

5. Патент SU 459780

6. Патент US 5070306, fig. 3

7. Патент US 2010/001797

8. Патент US 5610547, fig. 34

9. Патент US 6972623, fig. 4, fig. 6

10. Патент US 2008/0238546, fig. 2

11. Патент US 2008/0252374

12. Патент US 7567124

13. Патент US 7586373

14. Патент US 2006/0215787

15. Патент US 5570972

16. Патент US 5153529

17. Патент US 5523718, fig. 1

18. Патент US 7215200, fig. 6

19. Патент US 5420540

20. Патент US 5963085

21. Патент US 6788143

22. Патент US 7411451, fig. 2

23. Патент US 4406990, fig. 4

24. Патент US 4390850

25. Патент US 4607232

26. Патент US 7453319

27. Патент WO 01/80422 A2

28. Патент US 5586089, fig. 3

| название | год | авторы | номер документа |

|---|---|---|---|

| Быстродействующий операционный усилитель с повышенной скоростью нарастания выходного напряжения | 2018 |

|

RU2683160C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ "ПЕРЕГНУТОГО" КАСКОДА | 2015 |

|

RU2595923C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ ДВУХТАКТНОГО «ПЕРЕГНУТОГО» КАСКОДА | 2022 |

|

RU2786422C1 |

| Операционный усилитель с улучшенными статическими и динамическими параметрами на комплементарных полевых транзисторах | 2024 |

|

RU2836428C1 |

| Операционный усилитель на основе широкозонных полупроводников | 2023 |

|

RU2822157C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ ДВУХТАКТНОГО "ПЕРЕГНУТОГО" КАСКОДА И КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРОВ С УПРАВЛЯЮЩИМ PN-ПЕРЕХОДОМ | 2022 |

|

RU2780220C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2016 |

|

RU2621286C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2015 |

|

RU2613842C1 |

| Многоканальный дифференциальный усилитель на арсенид-галлиевых полевых и биполярных транзисторах | 2022 |

|

RU2792710C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ НА АРСЕНИД-ГАЛЛИЕВЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2021 |

|

RU2770912C1 |

Изобретение относится к области аналоговой микроэлектроники и может быть использовано в аналоговых интерфейсах и устройствах преобразования сигналов, в том числе работающих в диапазоне низких температур. Техническим результатом является повышение максимальной скорости нарастания выходного напряжения при работе входных транзисторов операционного усилителя с микроамперными статическими токами (1÷10 мкА). Быстродействующий дифференциальный операционный усилитель для работы при низких температурах содержит первый (1) и второй (2) входные полевые транзисторы, первый (4), второй (6) и третий (9) токостабилизирующие двухполюсники, первый (5) и второй (8) выходные транзисторы, третий (10) и четвертый (11) входные полевые транзисторы, первый (12) и второй (13) усилители тока, выходной преобразователь ток-напряжение (16), а также содержит первый (18) и второй (21) дополнительные токостабилизирующие двухполюсники, первый (19) и второй (20) дополнительные транзисторы, дополнительный корректирующий конденсатор (22). 1 з.п. ф-лы, 8 ил.

1. Быстродействующий дифференциальный операционный усилитель для работы при низких температурах, содержащий первый (1) и второй (2) входные полевые транзисторы, объединенные истоки которых связаны с первой (3) шиной источника питания через первый (4) токостабилизирующий двухполюсник, сток первого (1) входного полевого транзистора соединен с эмиттером первого (5) выходного транзистора и через второй (6) токостабилизирующий двухполюсник соединен со второй (7) шиной источника питания, сток второго (2) входного полевого транзистора соединен с эмиттером второго (8) выходного транзистора и через третий (9) токостабилизирующий двухполюсник связан со второй (7) шиной источника питания, третий (10) и четвертый (11) входные полевые транзисторы с объединенными истоками, причем сток третьего (10) входного полевого транзистора соединен со входом первого (12) усилителя тока, согласованного со второй (7) шиной источника питания, сток четвертого (11) входного полевого транзистора соединен со входом второго (13) усилителя тока, согласованного со второй (7) шиной источника питания, затворы первого (1) и третьего (10) входных полевых транзисторов подключены к первому (14) входу устройства, а затворы второго (2) и четвертого (11) входных полевых транзисторов подключены ко второму (15) входу устройства, причем коллекторы первого (5) и второго (8) выходных транзисторов связаны с дифференциальными входами выходного преобразователя ток-напряжение (16), выход которого (17) является выходом устройства, цепь установления статического режима на базах первого (5) и второго (8) выходных транзисторов, отличающийся тем, что объединенные стоки третьего (10) и четвертого (11) входных полевых транзисторов связаны с первой (3) шиной источника питания через первый (18) дополнительный токостабилизирующий двухполюсник, в качестве первого (12) усилителя тока используется инвертирующий усилитель тока, выход которого подключен к эмиттеру второго (8) выходного транзистора, в качестве второго (13) усилителя тока используется инвертирующий усилитель тока, выход которого подключен к эмиттеру первого (5) выходного транзистора, первый (14) вход устройства соединен с базой первого (19) дополнительного транзистора, коллектор которого связан с первой (3) шиной источника питания, второй (15) вход устройства соединен с базой второго (20) дополнительного транзистора, коллектор которого подключен к первой (3) шине источника питания, причем объединенные эмиттеры первого (19) и второго (20) дополнительных транзисторов связаны со второй (7) шиной источника питания через второй (21) дополнительный токостабилизирующий двухполюсник, а между объединенными эмиттерами первого (19) и второго (20) дополнительных транзисторов и объединенными истоками третьего (10) и четвертого (11) входных полевых транзисторов включен дополнительный корректирующий конденсатор (22).

2. Быстродействующий дифференциальный операционный усилитель для работы при низких температурах по п. 1, отличающийся тем, что выходной преобразователь ток-напряжение (16) содержит токовое зеркало (23), вход которого соединен с первым входом преобразователя ток-напряжение (16) и подключен к коллектору второго 8 выходного транзистора, а выход связан со вторым входом преобразователя ток-напряжение (16) и подключен к коллектору первого (5) выходного транзистора, а также соединен со входом дополнительного буферного усилителя (24) и корректирующим конденсатором (25), причем выход дополнительного буферного усилителя (24) является выходом устройства (17), а объединенные базы первого (5) и второго (8) выходных транзисторов связаны с цепью установления статического режима 26.

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ "ПЕРЕГНУТОГО" КАСКОДА | 2015 |

|

RU2595923C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2354041C1 |

| Дифференциальный усилитель | 1985 |

|

SU1385255A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| US 7215200 B1, 08.05.2007. | |||

Авторы

Даты

2018-10-05—Публикация

2017-11-09—Подача