Изобретение относится к области радиотехники и аналоговой микроэлектроники и может быть использовано в различных аналоговых и аналого-цифровых интерфейсах для обработки сигналов датчиков.

В современной радиоэлектронной аппаратуре, приборостроении и измерительной технике находят применение быстродействующие операционные усилители (ОУ), которые определяют динамические параметры многих аналоговых интерфейсов, АЦП, драйверов линий связи и т.п.

Методам повышения максимальной скорости нарастания выходного напряжения ОУ (SR) с различной архитектурой посвящено значительное количество патентов, монографий и статей, в т.ч. [1-4].

В современной микроэлектронике широкое распространение получили операционные усилители с двухкаскадной архитектурой, которая включает входной ДК, токовое зеркало и буферный усилитель [1-4]. Известны сотни патентов, использующих данное техническое решение, в т.ч. [5-20]. Предполагаемое изобретение относится к данному классу устройств.

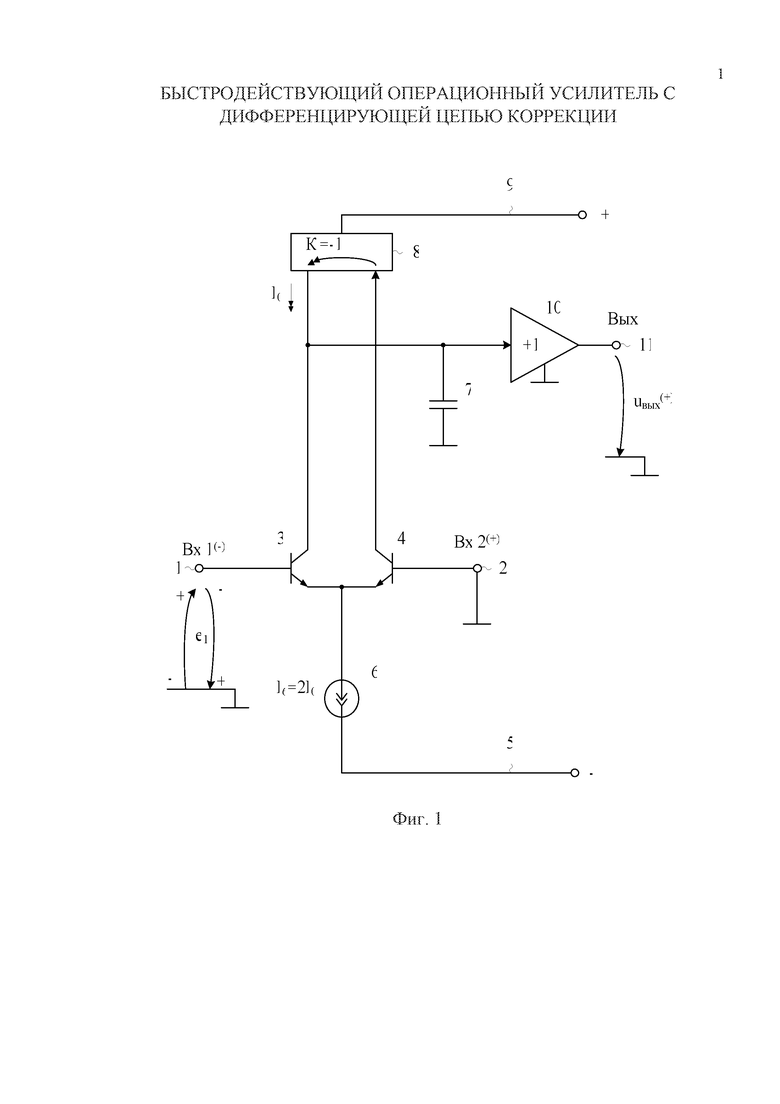

Ближайшим прототипом (фиг. 1) заявляемого устройства является ОУ по патенту США № 5.512.859, fig.3. Он содержит (фиг. 1) первый 1 инвертирующий и второй 2 неинвертирующий входы устройства, первый 3 и второй 4 входные транзисторы, эмиттеры которых объединены и подключены к первой 5 шине источника питания через первый 6 токостабилизирующий двухполюсник, база первого 3 входного транзистора соединена с первом 1 инвертирующим входом устройства, база второго 4 входного транзистора соединена со вторым 2 неинвертирующим входом устройства, первый 7 корректирующий конденсатор, связанный с коллектором первого 3 входного транзистора, токовое зеркало 8, согласованное со второй 9 шиной источника питания, вход которого связан с коллектором второго 4 входного транзистора, а выход подключен к коллектору первого 3 входного транзистора, а также соединен со входом буферного усилителя 10, выход которого является выходом устройства 11.

Существенный недостаток известного ОУ состоит в том, что при его инвертирующем включении с резисторами общей отрицательной обратной связи он имеет невысокую скорость нарастания выходного напряжения в режиме большого сигнала SR. Это обусловлено малыми значениями токов перезаряда первого 7 корректирующего конденсатора ОУ, которые жестко связаны с током первого 6 токостабилизирующего двухполюсника. По многим причинам этот ток не может выбираться большим.

Основная задача предполагаемого изобретения состоит в повышении SR без ухудшения энергетических параметров ОУ в статическом режиме.

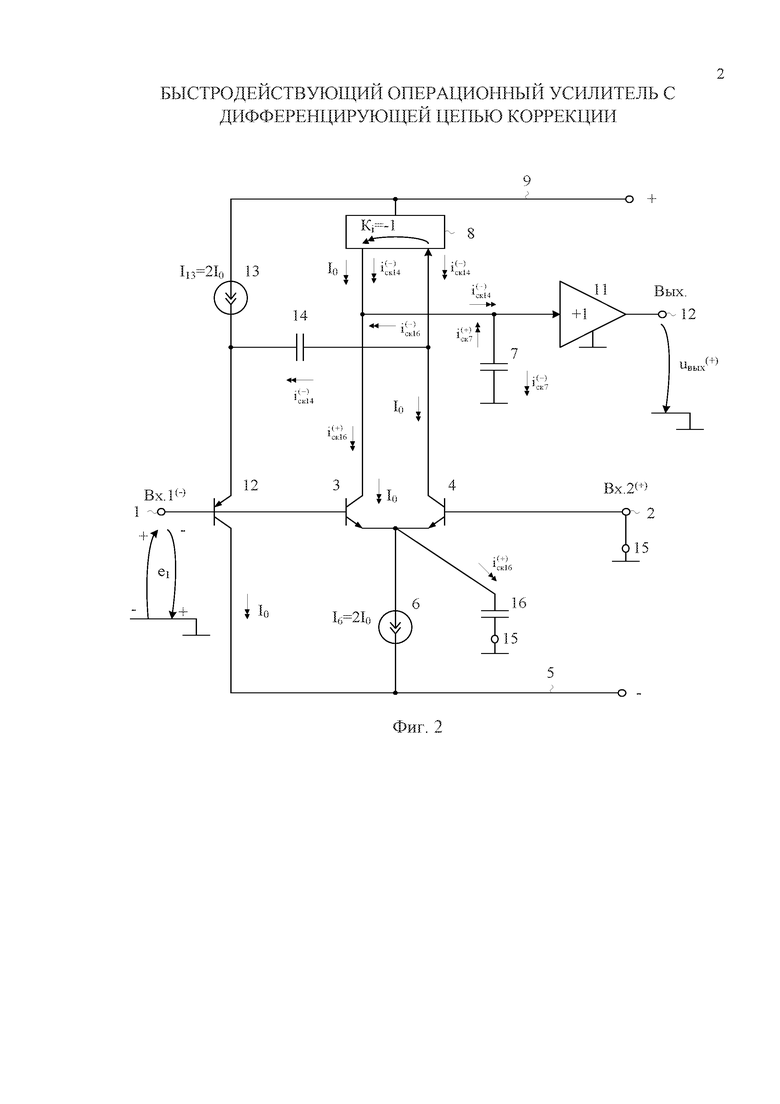

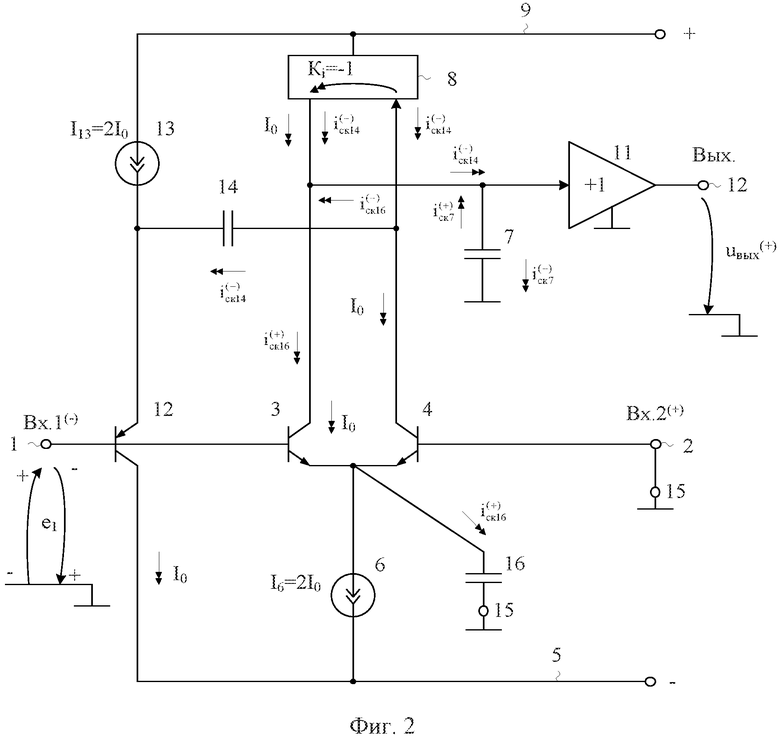

Поставленная задача достигается тем, что в операционном усилителе фиг.1, содержащем первый 1 инвертирующий и второй 2 неинвертирующий входы устройства, первый 3 и второй 4 входные транзисторы, эмиттеры которых объединены и подключены к первой 5 шине источника питания через первый 6 токостабилизирующий двухполюсник, база первого 3 входного транзистора соединена с первом 1 инвертирующим входом устройства, база второго 4 входного транзистора соединена со вторым 2 неинвертирующим входом устройства, первый 7 корректирующий конденсатор, связанный с коллектором первого 3 входного транзистора, токовое зеркало 8, согласованное со второй 9 шиной источника питания, вход которого связан с коллектором второго 4 входного транзистора, а выход подключен к коллектору первого 3 входного транзистора, а также соединен со входом буферного усилителя 10, выход которого является выходом устройства 11, предусмотрены новые элементы и связи – в схему введен первый 12 дополнительный транзистор, база которого соединена с первым 1 инвертирующим входом устройства, эмиттер первого 12 дополнительного транзистора связан со второй 9 шиной источника питания через второй 13 токостабилизирующий двухполюсник и соединен со входом токового зеркала 8 через второй 14 корректирующий конденсатор, причем коллектор первого 12 дополнительного транзистора связан с первой 5 шиной источника питания, а между объединенными эмиттерами первого 3 и второго 4 входных транзисторов и общей шиной источников питания 15 включен (по переменному току) третий 16 корректирующий конденсатор.

На чертеже фиг. 1 показана схема прототипа ОУ, а на чертеже фиг. 2 – схема заявляемого устройства в соответствии с п.1 формулы изобретения.

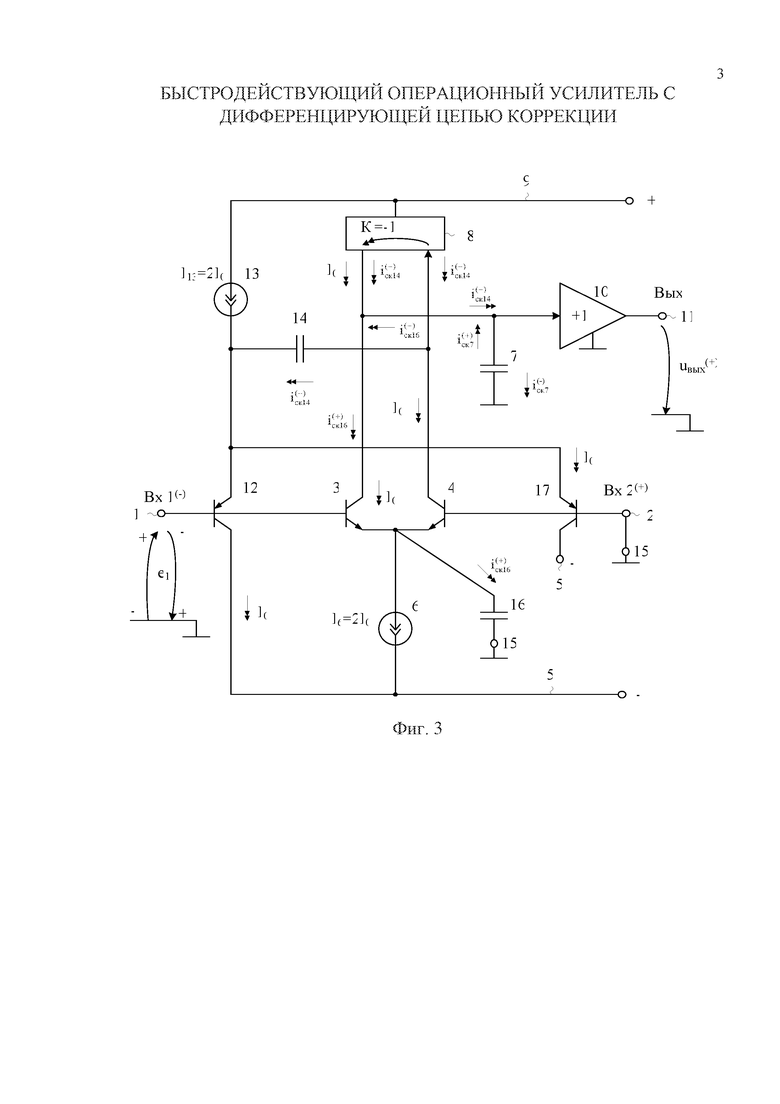

На чертеже фиг. 3 представлена схема заявляемого устройства в соответствии с п.2 формулы изобретения.

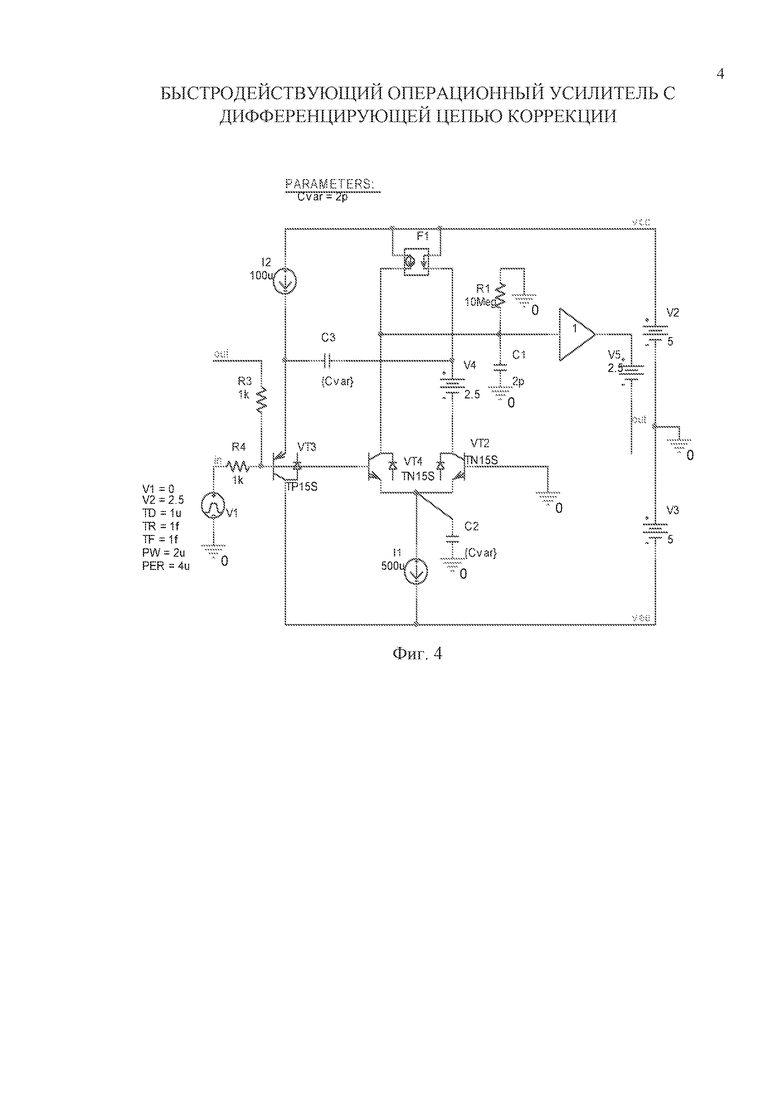

На чертеже фиг. 4 приведена схема заявляемого ОУ фиг. 2 в среде PSpice на компьютерных моделях комплементарных биполярных транзисторов АО «НПП» Пульсар». Источник напряжения V4 обеспечивает симметрирование статического режима транзисторов VT2 и VT4 по напряжению коллектор-база, что уменьшает напряжение смещения нуля.

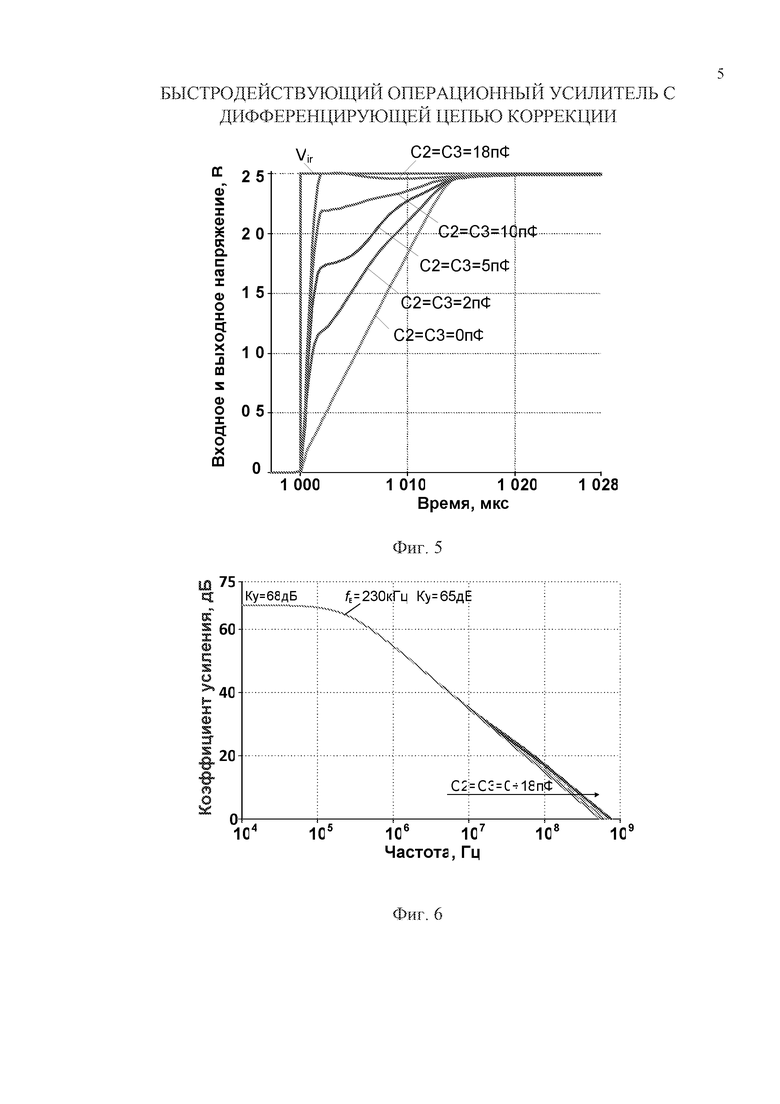

На чертеже фиг. 5 представлены графики переходного процесса в ОУ фиг. 4 при значениях емкости первого 7 корректирующего конденсатора С1(С7)=2пФ, амплитуде входного инвертирующего сигнала Uвх(+)=2,5В, статических токах I1(I6)=500 мкА, I2(I13)=100 мкА, сопротивлении резисторов обратной связи R3=R4=1кОм и различных значениях емкостей второго 14 и третьего 16 корректирующих конденсаторов С2(С14)=С3(С16)=Сvar=0;2;5;10;18пФ.

На чертеже фиг. 6 приведены амплитудно-частотные характеристики (АЧХ) разомкнутого ОУ фиг. 4 при емкости первого 7 корректирующего конденсатора С1(С7)=2пФ и различных значениях емкостей

второго 14 и третьего 16 корректирующих конденсаторов С2(С14)=С3(С16)=Сvar=0;2;5;10;18пФ.

Быстродействующий операционный усилитель фиг. 2 содержит первый 1 инвертирующий и второй 2 неинвертирующий входы устройства, первый 3 и второй 4 входные транзисторы, эмиттеры которых объединены и подключены к первой 5 шине источника питания через первый 6 токостабилизирующий двухполюсник, база первого 3 входного транзистора соединена с первом 1 инвертирующим входом устройства, база второго 4 входного транзистора соединена со вторым 2 неинвертирующим входом устройства, первый 7 корректирующий конденсатор, связанный с коллектором первого 3 входного транзистора, токовое зеркало 8, согласованное со второй 9 шиной источника питания, вход которого связан с коллектором второго 4 входного транзистора, а выход подключен к коллектору первого 3 входного транзистора, а также соединен со входом буферного усилителя 10, выход которого является выходом устройства 11. В схему введен первый 12 дополнительный транзистор, база которого соединена с первым 1 инвертирующим входом устройства, эмиттер первого 12 дополнительного транзистора связан со второй 9 шиной источника питания через второй 13 токостабилизирующий двухполюсник и соединен со входом токового зеркала 8 через второй 14 корректирующий конденсатор, причем коллектор первого 12 дополнительного транзистора связан с первой 5 шиной источника питания, а между объединенными эмиттерами первого 3 и второго 4 входных транзисторов и общей шиной источников питания 15 включен по переменному току третий 16 корректирующий конденсатор.

На чертеже фиг. 3, в соответствии с п. 2 формулы изобретения, в схему введен второй 17 дополнительный транзистор, эмиттер которого соединен с эмиттером первого 12 дополнительного транзистора, база соединена с базой второго 4 входного транзистора, а коллектор подключен к первой 5 шине источника питания. Данное схемотехническое решение позволяет обеспечить более высокую симметрию схемы ОУ по статическим токам первого 1 инвертирующего и второго 2 неинвертирующего входов устройства.

Рассмотрим работу предлагаемого быстродействующего ОУ фиг. 2 при его инвертирующем включении (фиг. 4).

Статический режим схемы фиг. 2 устанавливается источниками опорного тока I6 и I13. Первый 7 корректирующий конденсатор обеспечивает устойчивость ОУ при введении общей отрицательной обратной связи на его первый 1 инвертирующий вход.

Второй 14 и третий 16 корректирующие конденсаторы, из-за крайне малых постоянных времени, практически не влияют на работу ОУ в существенной полосе частот (до частоты единичного усиления f1). Об этом свидетельствует малосигнальная амплитудно-частотная характеристика разомкнутого ОУ, представленная на чертеже фиг. 6.

Если на первый 1 инвертирующий вход ОУ фиг. 2 поступает большой импульсный сигнал e1, то это создает дополнительные токи перезаряда первого 7 корректирующего конденсатора, пропорциональные производной от входного напряжения ОУ (

Если динамическая ошибка e1 мала, то и производная от

Таблица 1 – Взаимосвязь SR ОУ фиг. 4 и ёмкостей второго 14 и третьего 16 корректирующих конденсаторов С2(С14)=С3(С16)=Cvar, при I1(I6)=500 мкА, I2(I13)=100 мкА, С1(С7)=2пФ, Uвх(+)=2,5В, t=27°С

SR., В/мкс

Применение к качестве активных элементов схемы фиг. 2 базовых матричных кристаллов АБМК_1.3/1.7 [21] позволяет обеспечить работоспособность ОУ при низких температурах и условиях воздействия радиации.

Таким образом, в сравнении с ОУ-прототипом предлагаемое устройство обладает существенными преимуществами по динамическим параметрам в режиме большого сигнала. При этом, данный положительный эффект обеспечивается за счет введения двух, второго 14 и третьего 16 корректирующих конденсаторов, сравнительно небольшой емкости и не требует увлечения тока потребления ОУ в статическом режиме.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. I.M. Filanovsky, V.V. Ivanov, “Operational Amplifier Speed and Accuracy Improvement: Analog Circuit Design with Structural Methodology,” Kluwer Academic Publishers, New York, Boston, Dordrecht, London, 2004, 194 p.

2. Операционные усилители с непосредственной связью каскадов : монография / Анисимов В.И., Капитонов М.В., Прокопенко Н.Н., Соколов Ю.М. - Л.: «Энергия», 1979. - 148 с.

3. Прокопенко, Н.Н. Архитектура и схемотехника быстродействующих операционных усилителей: монография / Н.Н. Прокопенко, А.С. Будяков. – Шахты: Изд-во ЮРГУЭС, 2006. – 231 с.

4. Прокопенко Н.Н. Нелинейная активная коррекция в прецизионных аналоговых микросхемах (монография) // Ростов-на-Дону: Изд-во Северо-Кавказского научного центра высшей школы, 2000. 222 с.

5. Патент US 5.343.164

6. Патент US 6.822.505

7. Патент US 4.335.355

8. Патент US 4.912.425

9. Патент US 6.794.840, фиг.3

10. Патент US 7.167.052

11. Патент US 5.289.058

12. Патент US 6.822.505, фиг.4

13. Патент US 4.524.329, фиг.1-фиг.4

14. Заявка на патент US 2010/0085344

15. Заявка на патент EP 2007/054914

16. Заявка на патент W0 2007/135139

17. Патент US 4,464, 588

18. Патент US 7,646,247

19. Патент US 5,990,742, фиг.2

20. Патент US 6,774,722,фиг.2

21. O. V. Dvornikov, V. L. Dziatlau, N. N. Prokopenko, K. O. Petrosiants, N. V. Kozhukhov and V. A. Tchekhovski, "The accounting of the simultaneous exposure of the low temperatures and the penetrating radiation at the circuit simulation of the BiJFET analog interfaces of the sensors," 2017 International Siberian Conference on Control and Communications (SIBCON), Astana, 2017, pp. 1-6. DOI: 10.1109/SIBCON.2017.7998507.

| название | год | авторы | номер документа |

|---|---|---|---|

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2018 |

|

RU2676014C1 |

| Быстродействующий операционный усилитель | 2024 |

|

RU2822112C1 |

| Быстродействующий операционный усилитель | 2023 |

|

RU2810548C1 |

| Многоканальный быстродействующий операционный усилитель | 2018 |

|

RU2683851C1 |

| Быстродействующий дифференциальный операционный усилитель | 2018 |

|

RU2688227C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2577183C1 |

| ИЗБИРАТЕЛЬНЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ НЕИНВЕРТИРУЮЩЕГО УСИЛИТЕЛЯ ТОКА | 2012 |

|

RU2488955C1 |

| ИЗБИРАТЕЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2475945C1 |

| ИЗБИРАТЕЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2469464C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2017 |

|

RU2668968C1 |

Изобретение относится к области радиотехники и аналоговой микроэлектроники и может быть использовано в различных аналоговых и аналого-цифровых интерфейсах для обработки сигналов датчиков. Технический результат заключается в повышении максимальной скорости нарастания выходного напряжения и уменьшении времени установления переходного процесса в ОУ. Быстродействующий операционный усилитель содержит первый и второй входные транзисторы, источник питания, токостабилизирующий двухполюсник, первый корректирующий конденсатор, связанный с коллектором первого входного транзистора, токовое зеркало, согласованное со второй шиной источника питания, буферный усилитель. 1 з.п. ф-лы, 1 табл., 6 ил.

1. Быстродействующий операционный усилитель с дифференцирующей цепью коррекции, содержащий первый (1) инвертирующий и второй (2) неинвертирующий входы устройства, первый (3) и второй (4) входные транзисторы, эмиттеры которых объединены и подключены к первой (5) шине источника питания через первый (6) токостабилизирующий двухполюсник, база первого (3) входного транзистора соединена с первом (1) инвертирующим входом устройства, база второго (4) входного транзистора соединена со вторым (2) неинвертирующим входом устройства, первый (7) корректирующий конденсатор, связанный с коллектором первого (3) входного транзистора, токовое зеркало (8), согласованное со второй (9) шиной источника питания, вход которого связан с коллектором второго (4) входного транзистора, а выход подключен к коллектору первого (3) входного транзистора, а также соединен со входом буферного усилителя (10), выход которого является выходом устройства (11), отличающийся тем, что в схему введен первый (12) дополнительный транзистор, база которого соединена с первым (1) инвертирующим входом устройства, эмиттер первого (12) дополнительного транзистора связан со второй (9) шиной источника питания через второй (13) токостабилизирующий двухполюсник и соединен со входом токового зеркала (8) через второй (14) корректирующий конденсатор, причем коллектор первого (12) дополнительного транзистора связан с первой (5) шиной источника питания, а между объединенными эмиттерами первого (3) и второго (4) входных транзисторов и общей шиной источников питания (15) включен по переменному току третий (16) корректирующий конденсатор.

2. Быстродействующий операционный усилитель с дифференцирующей цепью коррекции по п.1, отличающийся тем, что в схему введен второй (17) дополнительный транзистор, эмиттер которого соединен с эмиттером первого (12) дополнительного транзистора, база соединена с базой второго (4) входного транзистора, а коллектор подключен к первой (5) шине источника питания.

| US 5512859 A, 30.04.1996 | |||

| ИЗБИРАТЕЛЬНЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ НЕИНВЕРТИРУЮЩЕГО УСИЛИТЕЛЯ ТОКА | 2012 |

|

RU2488955C1 |

| ИЗБИРАТЕЛЬНЫЙ УСИЛИТЕЛЬ | 2012 |

|

RU2480896C1 |

| Операционный усилитель | 1986 |

|

SU1356196A1 |

Авторы

Даты

2018-10-08—Публикация

2018-03-02—Подача