Изобретение относится к высокочастотной измерительной технике и может быть использовано для создания специализированных вычислительных структур и построения на их основе контроллеров для создания критичных систем управления железнодорожным транспортом.

Известны устройства, выполняющие логические функции при приеме радиочастотных сигналов (RU 2465645 С1 27.10.2012, SU 1251320 А1 15.08.1986, SU 1615878 А1 23.12.1990, US 20070150794 А1 28.06.2007). Недостатком данных устройств является низкая безопасность от ложного срабатывания.

Наиболее близкий к предлагаемому по функциональным особенностям элементу является представленный в (Кичак В.М. Радiочастотнi та широтно-iмпульснi елементи цифровоï технiки / В.М. Кичак, О.О. Семенова. - Монографiя Вiнниця: УНIВЕРСУМ-Вiнниця, 2008 - 163 с.) радиочастотный логический элемент «И», который содержит смеситель частот 1, имеющий два входа, на каждый из которых подается частота либо f0, либо частота f1, при этом f1>f0, соединенный с фильтром верхних частот 2 (выделяющий частоту f0 и выше), который, в свою очередь, соединен со смесителями 3 и 4, имеющими по два входа каждый, причем на смеситель 3 подается частота f0, а на смеситель 4 - частота f1. Смесители 3 и 4 соединены с сумматором 5, который, в свою очередь, соединяется с полосовым фильтром 6, выделяющим частоту f0, помимо прочего смеситель 4 соединяется так же с полосовым фильтром 7, выделяющим частоту f1. Далее выходы смесителей 6 и 7 соединяются с входом сумматора 17. Таким образом, при поступлении на вход элемента двух сигналов с частотой f1 представленная схема позволяет получить на выходе сигнал с частотой f1, а во всех остальных случаях - сигнал с частотой f0.

Недостатком данного устройства является то, что в результате появления на одном или обоих входах элемента смеси частот f0 и f1 (при коротком замыкании дорожек в аппаратном устройстве) элемент пропускает на выход суммарный сигнал этих частот, что недопустимо для критичных систем, таких как системы управления железнодорожным транспортом.

Технический результат заключается в повышении надежности работы путем обеспечения перехода элемента в безопасное состояние в случае попадания на вход смеси сигналов при коротком замыкании в аппаратном устройстве.

Для этого предлагается радиочастотный безопасный логический элемент И, содержащий первый смеситель, выход которого соединен через фильтр верхних частот с входами первого и второго сумматоров и первыми входами второго и третьего смесителей, выходы которых соединены соответственно со вторыми входами первого и второго сумматоров, выходы которых соединены соответственно через первый и второй полосовые фильтры с входами первого и второго вычислителей огибающей сигнала, выходы которых соединены соответственно с первыми и вторыми входами первого и второго вычитателей, выходы которых через первый и второй пороговые элементы соединены соответственно с управляющими входами первого и второго аналоговых ключей, выходы которых соединены с входами третьего сумматора, при этом выход второго смесителя соединен с третьим входом второго сумматора.

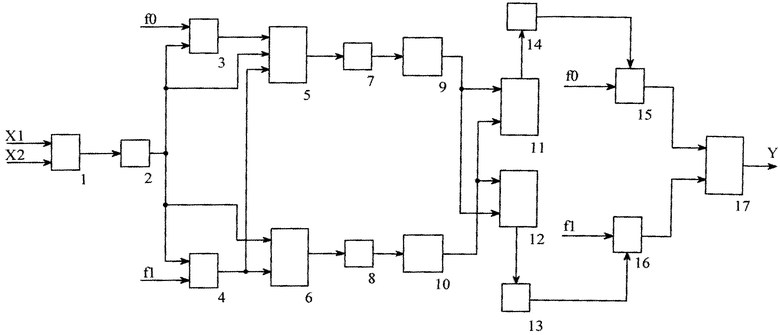

На фиг.1 представлена структурная электрическая схема радиочастотного безопасного логического элемента И.

Радиочастотный безопасный логический элемент И содержит первый смеситель 1, фильтр верхних частот 2, второй и третий смесители 3 и 4, первый и второй сумматоры 5 и 6, первый и второй полосовые фильтры 7 и 8, первый и второй вычислители огибающей сигнала 9 и 10, первый и второй вычитатели 11 и 12, первый и второй пороговые элементы 13 и 14, первый и второй аналоговые ключи 15 и 16, и третий сумматор 17.

Элемент функционирует следующим образом.

В условиях нормального режима работы входные информационные сигналы X1 и Х2 с частотами f1 и амплитудой А поступают на вход первого смесителя 1. Результирующий сигнал подается на фильтр верхних частот 2, пропускающий частоты, выше частоты f0. Так как на вход подавались сигналы с частотой f1, то фильтр верхних частот 2 пропускает поступивший на вход после первого смесителя 1 сигнал с частотой 2f1 на входы второго и третьего смесителей 3 и 4, а также с первого и второго сумматоров 5 и 6. На вход первого сумматора 5 поступают сигналы с выхода фильтра верхних частот 2, первого смесителя 3 и второго смесителя 4, а на вход второго сумматора 6 поступают сигналы с выходов фильтра верхних частот 2 и второго смесителя 4. С выходов первого и второго сумматоров 5 и 6 сигналы поступают на вход соответственно первого и второго полосовых фильтров 7 и 8 и далее на входы первого и второго вычислителей огибающей сигнала 9 и 10 соответственно. Первый полосовой фильтр 7 настроен на пропуск сигнала с частотой f0, поэтому на его выходе будет нулевой сигнал, а следовательно, на выходе первого вычислителя огибающей сигнала 9 будет присутствовать нулевой сигнал. Второй полосовой фильтр 8 настроен так, чтобы выделять сигнал с частотой f1, таким образом, на его выходе будет присутствовать сигнал с частотой f1, что соответственно приведет к возникновению огибающей сигнала с амплитудой А на выходе второго вычислителя огибающей сигнала 10. Выходы вычислителей огибающей сигнала 9 и 10 соединены с входами первого и второго вычитателей 11 и 12. Таким образом, на выходе первого вычитателя 11 будет присутствовать сигнал с амплитудой -А, а на выходе второго вычитателя 12 - сигнал с амплитудой +А. Выходы первого и второго вычитателей 11 и 12 соединены с входами второго и первого пороговых элементов 14 и 13 соответственно. Следовательно, на выходе второго порогового элемента 14 будет присутствовать логический ноль, на выходе первого порогового элемента 13 - логическая единица. Первый и второй пороговые элементы 13 и 14 соединены с входами второго и первого аналоговых ключей 16 и 15 соответственно (работают по принципу: если на входе есть логическая единица, полезный сигнал пропускается, если нет - блокируется). Поэтому на выходе первого аналогового ключа 15 будет присутствовать ноль, а на выходе второго аналогового ключа 16 - полезный сигнал с частотой f1. Выходы аналоговых ключей соединены с входом сумматора третьего 17, на выходе которого в данном случае будет присутствовать сигнал с частотой f1. В случае подачи на один или оба входа сигнала с частотой f0 на выходе первого вычитателя 11 будет присутствовать сигнал с амплитудой +А, а на выходе второго вычитателя 12 - сигнал с амплитудой -А, следствием чего будет являться появление логической единицы на выходе первого порогового элемента 13 и логического нуля на выходе второго порогового элемента 14, что соответственно приведет к срабатыванию первого аналогового ключа 15 и появлению на выходе сигнала с частотой f0.

В условиях неисправности: случай короткого замыкания, при котором на один или оба входа попадают сигналы с частотами f0 и f1, логический элемент сработает следующим образом: первый и второй полосовые фильтры 7 и 8 выделят частоты f0 и f1 соответственно и передадут их на вход первого и второго вычислителей огибающей сигнала 9 и 10 соответственно. С выходов первого и второго вычислителей огибающей сигнала 9 и 10 вычисленные огибающие сигналов будут переданы на входы первого и второго вычитателей 11 и 12 соответственно. В результате с выходов второго и первого пороговых элементов 14 и 13 на первый и второй аналоговые ключи 15 и 16 поступят логические нули, что приведет к их несрабатыванию. В результате на выходе схемы будет нулевой сигнал, что удовлетворяет требованиям, предъявляемым к элементам, используемым при построении функциональных узлов железнодорожных критичных систем.

В случае обрыва или подачи на вход нулевого сигнала на входе сигналы будут отсутствовать и соответственно на выходе тоже будет нулевой сигнал.

| название | год | авторы | номер документа |

|---|---|---|---|

| РАДИОЧАСТОТНЫЙ БЕЗОПАСНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ "ИЛИ" | 2013 |

|

RU2525753C1 |

| РАДИОЧАСТОТНЫЙ БЕЗОПАСНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ "НЕ" | 2013 |

|

RU2533447C1 |

| ЦЕНТРАЛИЗОВАННАЯ ДИСПЕТЧЕРСКАЯ СИСТЕМА С РАСПРЕДЕЛЕННЫМИ КОНТРОЛИРУЕМЫМИ ПУНКТАМИ | 2003 |

|

RU2240245C1 |

| Модуль безопасного сопряжения | 2019 |

|

RU2710978C1 |

| Унифицированный логический контроллер | 2019 |

|

RU2710502C1 |

| Гибридное устройство маршрутизации | 2019 |

|

RU2710503C1 |

| ОБНАРУЖИТЕЛЬ РАДИОИМПУЛЬСОВ | 1979 |

|

SU1840949A1 |

| СИСТЕМА УПРАВЛЕНИЯ И РЕГУЛИРОВАНИЯ ЭЛЕКТРОПРИВОДОМ ПОГРУЖНОГО НАСОСА | 2006 |

|

RU2334365C2 |

| АКТИВНАЯ ФАЗИРОВАННАЯ АНТЕННАЯ РЕШЕТКА | 2010 |

|

RU2451373C1 |

| СИСТЕМА СЕЛЕКЦИИ ДВИЖУЩИХСЯ ЦЕЛЕЙ С ИЗМЕРЕНИЕМ ДАЛЬНОСТИ, РАДИАЛЬНОЙ СКОРОСТИ И НАПРАВЛЕНИЯ ДВИЖЕНИЯ В КАЖДОМ ПЕРИОДЕ ЗОНДИРОВАНИЯ | 2022 |

|

RU2782575C1 |

Изобретение относится к высокочастотной измерительной технике и может быть использовано для создания специализированных вычислительных структур и построения на их основе контроллеров для создания критичных систем управления железнодорожным транспортом. Техническим результатом является повышение надежности работы за счет обеспечения перехода элемента в безопасное состояние в случае попадания на вход смеси сигналов при коротком замыкании в аппаратном устройстве. Устройство содержит смесители, фильтр верхних частот, сумматоры, полосовые фильтры, вычислители огибающей сигнала, вычитатели, пороговые элементы, аналоговые ключи. 1 ил.

Радиочастотный безопасный логический элемент И, содержащий первый смеситель, выход которого соединен через первый фильтр верхних частот с входами первого и второго сумматоров и первыми входами второго и третьего смесителей, выходы которых соединены соответственно со вторыми входами первого и второго сумматоров, выходы которых соединены соответственно через первый и второй полосовые фильтры с входами первого и второго вычислителей огибающей сигнала, выходы которых соединены соответственно с первыми и вторыми входами первого и второго вычитателей, выходы которых через первый и второй пороговые элементы соединены соответственно с управляющими входами первого и второго аналоговых ключей, выходы которых соединены с входами третьего сумматора, при этом выход второго смесителя соединен с третьим входом второго сумматора.

| Радиоимпульсный логический элемент И | 1988 |

|

SU1599986A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1991 |

|

RU2009612C1 |

| Логический элемент | 1986 |

|

SU1401596A1 |

| Безопасный логический элемент | 1987 |

|

SU1499479A1 |

| US 2006197557 A1, 07.09.2006 | |||

| US 2004041592 A1, 04.03.2004 | |||

Авторы

Даты

2014-11-20—Публикация

2013-10-10—Подача