Изобретение относится к области железнодорожной автоматики и телемеханики и может быть использовано в критичных системах управления железнодорожным транспортом.

К системам железнодорожной автоматики предъявляют высокие требования безопасности и надежности. Обычно безопасность функционирования обеспечивается за счет аппаратной и программной избыточности.

Известна мультипроцессорная компьютерная система, описанная в заявке WO2011147580 A1, опубликованной 01.12.2011. Известная система содержит множество рабочих процессоров, обеспечивающих функционирование программного обеспечения, и множество процессоров мониторинга, обеспечивающих контроль функционирования рабочих процессоров. Недостатком известной системы является большая аппаратная сложность ее реализации, обусловленная использованием большого количества рабочих процессоров и большого количества контролирующих процессоров. Кроме того, недостатком известной системы является отсутствие средств мониторинга выполнения программного обеспечения.

Наиболее близким к заявляемому изобретению является устройство для контроля системы с несколькими функциональными блоками, описанное в патенте RU2175451 C2, опубликованном 27.10.2001. Известное устройство содержит множество резервированных двухканальных устройств безопасности, связанных друг с другом и обеспечивающих индивидуальный контроль каждого функционального блока. Недостатком известного устройства является большая аппаратная сложность его реализации, обусловленная использованием большого количества устройств безопасности и аппаратных связей между ними. Кроме того, недостатком известного устройства является отсутствие средств мониторинга выполнения программного обеспечения функциональных блоков.

Задача изобретения: создание унифицированного логического контроллера (УЛК), обеспечивающего реализацию алгоритмов работы систем железнодорожной автоматики и телемеханики, построенного по архитектуре 2 из 2 с применением аппаратного арбитра, для применения такого УЛК в различного класса системах железнодорожной автоматики и телемеханики распределенной архитектуры.

Унифицированный логический контроллер (УЛК) содержит два (А, Б) микропроцессорных вычислителя, интерфейсы верхнего уровня CAN1А и CAN1Б, соединенные с соответствующими драйверами CAN-сетей, интерфейсы нижнего уровня CAN2А и CAN2Б, соединенные с соответствующими драйверами CAN-сетей, четыре универсальных асинхронных приемника-передатчика, соединенные с соответствующим из четырех драйверов последовательного интерфейса RS-422, два последовательных интерфейса SPI 1,2, два последовательных интерфейса SPI 3, безопасную асинхронную схему сравнения (БАСС).

В микропроцессорные вычислители (А, Б) загружается диверсифицированное программное обеспечение, обеспечивающее соответствующий алгоритм функционирования УЛК, причем программный код для микропроцессорного вычислителя А отличается от кода для микропроцессорного вычислителя Б.

Микропроцессорные вычислители (А, Б) соединены с соответствующими интерфейсами верхнего уровня CAN1А и CAN1, служащим для обмена сообщениями микропроцессорными вычислителями А и Б с внешними устройствами верхнего уровня.

Микропроцессорные вычислители (А, Б) соединены с соответствующими интерфейсами нижнего уровня CAN1А и CAN1Б, которые служат для обмена сообщениями микропроцессорными вычислителями А и Б с внешними устройствами нижнего уровня.

Микропроцессорный вычислитель А соединен с первым и третьим универсальными асинхронными приемниками-передатчиками.

Микропроцессорный вычислитель Б соединен со вторым и четвертым универсальными асинхронными приемниками-передатчиками.

Микропроцессорный вычислитель А соединен с первым последовательным интерфейсом SPI 1,2, применяющимся для передачи данных из микропроцессорного вычислителя А в микропроцессорный вычислитель Б, и соединен с первым последовательным интерфейсом SPI 3, обеспечивающим передачу данных их микропроцессорного вычислителя А в БАСС.

Микропроцессорный вычислитель Б соединен со вторым последовательным интерфейсом SPI 1,2, применяющимся для передачи данных из микропроцессорного вычислителя Б в микропроцессорный вычислитель А, и соединен со вторым последовательным интерфейсом SPI 3, обеспечивающим передачу данных их микропроцессорного вычислителя Б в БАСС.

Безопасная асинхронная схема сравнения (БАСС) выполняет функции арбитра и обеспечивает сравнение результатов работы микропроцессорных вычислителей А и Б по контрольным точкам и разрешает работу драйверам последовательного интерфейса RS-422 и драйверам CAN-сетей интерфейсов нижнего уровня в случае совпадения результатов вычислений.

Технический результат изобретения заключается в повышении безопасности и надежности систем железнодорожной автоматики и телемеханики распределенной архитектуры.

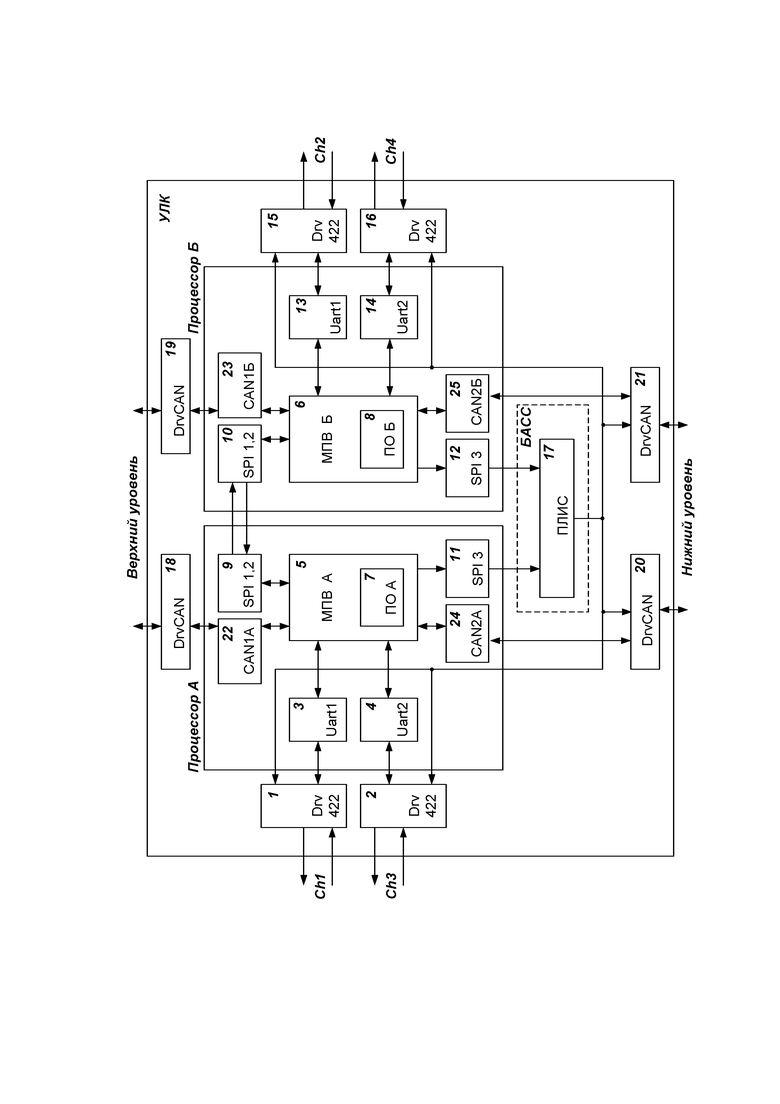

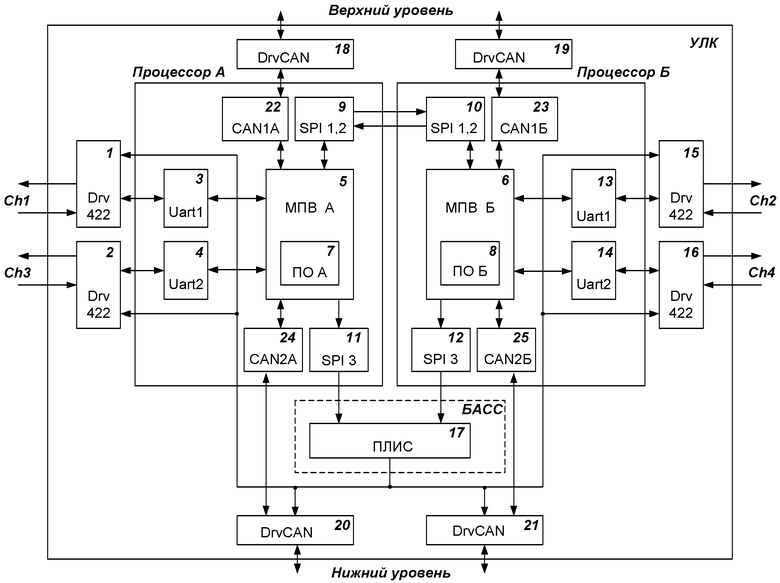

На чертеже представлена структурная схема унифицированного логического контроллера.

УЛК состоит из двух микропроцессорных вычислителей (МПВ_A 5, МПВ_Б 6), реализованных на однокристальных микроконтроллерах и работающих по диверсифицированным алгоритмам программного обеспечения (ПО_А 7, ПО_Б 8), четырех гальванически развязанных CAN-сетей (CAN1А 22, CAN2А 24, CAN1Б 23, CAN2Б 25), последовательных интерфейсов SPI 1, 2 (9 и 10), SPI 3 (11 и 12), интерфейсов Uart1 (3, 13), Uart2 (4, 14), безопасной асинхронной схемы сравнения (БАСС) 17, драйверов последовательного интерфейса RS-422 Drv422 (1, 2, 15, 16), драйверов CAN-сетей DrvCAN1_A 18, DrvCAN1_Б 19, DrvCAN2_A 20, DrvCAN2_Б 21.

Сети CAN1_A и CAN1_Б служат для обмена технологической и мониторинговой информацией между УЛК и согласующими устройствами систем верхнего уровня. Сети CAN2A и CAN2Б служат для обмена информацией с устройствами нижнего уровня.

Универсальные асинхронные приемники-передатчики Uart1 3, 13 и Uart2 4, 14 предназначены для обмена сообщениями между смежными УЛК. На базе интерфейсов RS-422 1, 2, 15, 16 образованы 4 канала (потока) передачи информации.

Порядок работы модуля УЛК следующий:

Микропроцессорные вычислители МПВ_А 5 и МПВ_Б 6 по сети верхнего уровня CAN1_А 22 и CAN1_Б 23 через драйверы последовательных интерфейсов DrvCAN1А 18 и DrvCAN1Б 19 и по сети нижнего уровня CAN2А 24 и CAN2Б 25, через драйверы последовательных интерфейсов DrvCAN2А 20 и DrvCAN2Б 21 получают сообщения от систем верхнего уровня, объектов контроля и управления соответственно. Одновременно с этим МПВ_А и МПВ_Б через интерфейсы Uart1 3, 13 и Uart2 4, 14, через драйверы последовательных интерфейсов Drv422 1, 2, 15, 16 получают сообщения от смежных УЛК (при их наличии). Информация обрабатывается одновременно процессором МПВ_А и процессором МПВ_Б в соответствии с алгоритмом функционирования программного обеспечения ПО_А 7 и ПО_Б 8, загружаемым в МПВ_А и МПВ_Б соответственно на стадии подготовки устройства к работе.

Безопасная асинхронная схема сравнения 17, являющаяся программируемой логической интегральной схемой (ПЛИС), осуществляет непрерывный контроль результатов функционирования алгоритма в процессорах МПВ_А и МПВ_Б в контрольных точках. В качестве контрольных точек выбираются состояния элементов внутренней логики процессоров. В случае несовпадения результатов работы хотя бы в одной контрольной точке схема сравнения отключает драйверы Drv422, DrvCAN2_А и DrvCAN2_Б и останавливает обмен информацией со смежными УЛК (при их наличии), а так же с системами нижнего уровня, чем обеспечивается перевод УЛК в безопасное состояние, которое сохраняется до перезапуска процессоров нажатием кнопки сброса.

Применение такого УЛК позволит повысить безопасность и надежность систем железнодорожной автоматики и телемеханики распределенной архитектуры, обеспечить гибкость и простоту проектирования данного класса систем.

| название | год | авторы | номер документа |

|---|---|---|---|

| Модуль безопасного сопряжения | 2019 |

|

RU2710978C1 |

| Блочная микропроцессорная централизация (БМПЦ) | 2023 |

|

RU2803696C1 |

| Релейно-процессорная электрическая централизация | 2023 |

|

RU2814418C1 |

| Система диспетчерской централизации | 2024 |

|

RU2833087C1 |

| Гибридное устройство маршрутизации | 2019 |

|

RU2710503C1 |

| ЦЕНТРАЛИЗОВАННАЯ ДИСПЕТЧЕРСКАЯ СИСТЕМА С РАСПРЕДЕЛЕННЫМИ КОНТРОЛИРУЕМЫМИ ПУНКТАМИ | 2003 |

|

RU2240245C1 |

| СИСТЕМА ГОРОЧНОЙ МИКРОПРОЦЕССОРНОЙ ЦЕНТРАЛИЗАЦИИ (ГМЦ) | 2017 |

|

RU2648488C1 |

| Система контроля местоположения поездов | 2019 |

|

RU2727438C1 |

| Система интервального регулирования движения поездов | 2021 |

|

RU2764315C1 |

| ХИРУРГИЧЕСКИЙ ИНСТРУМЕНТ, СОДЕРЖАЩИЙ ЗАКРЫВАЮЩИЙ ПРИВОД И ПУСКОВОЙ ПРИВОД, РАБОТАЮЩИЕ ОТ ОДНОГО ПОВОРАЧИВАЕМОГО ВЫХОДА | 2014 |

|

RU2650585C2 |

Изобретение относится к железнодорожной автоматикe для управления транспортом. Контроллер содержит два (А, Б) микропроцессорных вычислителя, интерфейсы верхнего уровня CAN1А и CAN1Б, соединенные с драйверами CAN-сетей, интерфейсы нижнего уровня CAN2А и CAN2Б, соединенные с драйверами CAN-сетей, четыре универсальных асинхронных приемника-передатчика, соединенные с соответствующим из четырех драйверов последовательного интерфейса RS-422, два последовательных интерфейса SPI 1,2, два последовательных интерфейса SPI 3, безопасную асинхронную схему сравнения (БАСС). В микропроцессорные вычислители (А, Б) загружается диверсифицированное программное обеспечение, причем программный код для микропроцессорного вычислителя А отличается от кода для микропроцессорного вычислителя Б. БАСС выполняет функции арбитра и обеспечивает сравнение результатов работы микропроцессорных вычислителей А и Б по контрольным точкам и разрешает работу драйверам последовательного интерфейса RS-422 и драйверам CAN-сетей интерфейсов нижнего уровня в случае совпадения результатов вычислений. Достигается повышение безопасности и надежности работы. 1 ил.

Унифицированный логический контроллер (УЛК), содержащий два (А, Б) микропроцессорных вычислителя, интерфейсы верхнего уровня CAN1А и CAN1Б, соединенные с соответствующими драйверами CAN-сетей, интерфейсы нижнего уровня CAN2А и CAN2Б, соединенные с соответствующими драйверами CAN-сетей, четыре универсальных асинхронных приемника-передатчика, соединенные с соответствующим из четырех драйверов последовательного интерфейса RS-422, два последовательных интерфейса SPI 1,2, два последовательных интерфейса SPI 3, безопасную асинхронную схему сравнения (БАСС), причем в микропроцессорные вычислители (А, Б) загружается диверсифицированное программное обеспечение, обеспечивающее соответствующий алгоритм функционирования УЛК, причем программный код для микропроцессорного вычислителя А отличается от кода для микропроцессорного вычислителя Б, причем микропроцессорные вычислители (А, Б) соединены с соответствующими интерфейсами верхнего уровня CAN1А и CAN1Б, служащими для обмена сообщениями микропроцессорными вычислителями А и Б с внешними устройствами верхнего уровня, соединены с соответствующими интерфейсами нижнего уровня CAN2А и CAN2Б, которые служат для обмена сообщениями микропроцессорными вычислителями А и Б с внешними устройствами нижнего уровня, причем микропроцессорный вычислитель А соединен с первым и третьим универсальными асинхронными приемниками-передатчиками, соединен с первым последовательным интерфейсом SPI 1,2, применяющимся для передачи данных из микропроцессорного вычислителя А в микропроцессорный вычислитель Б, и соединен с первым последовательным интерфейсом SPI 3, обеспечивающим передачу данных из микропроцессорного вычислителя А в БАСС, причем микропроцессорный вычислитель Б соединен со вторым и четвертым универсальными асинхронными приемниками-передатчиками, соединен со вторым последовательным интерфейсом SPI 1,2, применяющимся для передачи данных из микропроцессорного вычислителя Б в микропроцессорный вычислитель А, и соединен со вторым последовательным интерфейсом SPI 3, обеспечивающим передачу данных из микропроцессорного вычислителя Б в БАСС, и причем безопасная асинхронная схема сравнения выполняет функции арбитра и обеспечивает сравнение результатов работы микропроцессорных вычислителей А и Б по контрольным точкам и разрешает работу драйверам последовательного интерфейса RS-422 и драйверам CAN-сетей интерфейсов нижнего уровня в случае совпадения результатов вычислений.

| МИКРОПРОЦЕССОРНАЯ СИСТЕМА ЦЕНТРАЛИЗАЦИИ СТРЕЛОК И СИГНАЛОВ | 2011 |

|

RU2495778C2 |

| УСТРОЙСТВО ДИВЕРСИФИЦИРОВАННОГО БЕЗОПАСНОГО УПРАВЛЕНИЯ, В ЧАСТНОСТИ, ДЛЯ ЖЕЛЕЗНОДОРОЖНОЙ СИСТЕМЫ | 2007 |

|

RU2454345C2 |

| Устройство для дистанционного управления сбрасыванием бревен | 1960 |

|

SU133798A1 |

| СИСТЕМА ГОРОЧНОЙ МИКРОПРОЦЕССОРНОЙ ЦЕНТРАЛИЗАЦИИ (ГМЦ) | 2017 |

|

RU2648488C1 |

| Двухчелюстный грейфер | 1949 |

|

SU79083A1 |

| Автоматическая поилка для животных | 1951 |

|

SU96088A1 |

| КОМПЛЕКСНОЕ УСТРОЙСТВО БЕЗОПАСНОГО ИНФОРМАЦИОННОГО ОБМЕНА И КОНТРОЛЯ ЛОКОМОТИВНЫХ И СТАЦИОНАРНЫХ УСТРОЙСТВ БЕЗОПАСНОСТИ НА ЖЕЛЕЗНОДОРОЖНОМ ТРАНСПОРТЕ | 2014 |

|

RU2577936C1 |

| EP 875810 A2, 04.11.1998 | |||

| WO 2009059909 A1, 14.05.2009. | |||

Авторы

Даты

2019-12-26—Публикация

2019-04-22—Подача