Изобретение относится к области радиотехники и связи и может быть использовано в измерительной, вычислительной, а также в преобразовательной технике для систем управления с широтно-импульсной модуляцией, устройствах временной задержки, в преобразователях «напряжение - временной интервал» и т.д.

Известно устройство [1], содержащее источник квадратурных гармонических сигналов, два вычислителя модуля и сумматор, на выходе которого формируется сигнал треугольной формы, имеющий значительную нелинейность на участках «прямого» и «обратного» хода формируемого сигнала.

Известно устройство [2], содержащее аналого-цифровой фазовращатель, два вычислителя модуля и сумматор, на выходе которого формируется сигнал квазитреугольной S-образной формы, имеющий значительную нелинейность на участках «прямого» и «обратного» хода формируемого сигнала.

Наиболее близким устройством к заявленному изобретению по совокупности существенных признаков является, принятый за прототип, аддитивный формирователь сигнала треугольной формы [3], содержащий два вычислителя модуля, два перемножителя, квадратор, амплитудный компаратор, вычитатель, коммутатор и суммирующий блок, выполненный из второго вычитателя и сумматора, при этом выход суммирующего блока соединен с выходом аддитивного формирователя сигнала треугольной формы, первый вход которого соединен с входом первого вычислителя модуля и первым входом первого перемножителя, второй вход аддитивного формирователя сигнала треугольной формы соединен с входом второго вычислителя модуля, входом квадратора и вторым входом первого перемножителя, к выходу которого подключены неинвертирующий вход амплитудного компаратора, первый вход вычитателя и первый вход второго перемножителя, выход которого соединен с вторым входом вычитателя, к выходу которого подключен второй вход коммутатора, выход которого соединен с третьим входом суммирующего блока, первый и второй входы которого соединены с выходами первого и второго вычислителей модулей соответственно, причем к выходу квадратора подключен второй вход второго перемножителя, первый вход коммутатора соединен с выходом амплитудного компаратора, инвертирующий вход которого соединен с общей шиной.

На выходе устройства формируется улучшенный квазилинейный сигнал треугольной формы, но блок коррекции содержит большое количество прецизионных, а следовательно, дорогостоящих микросхем (два перемножителя и квадратор, который также может быть выполнен из перемножителя).

Задачей, на решение которой направлено изобретение, является упрощение устройства и сохранение высокой линейности формируемого сигнала треугольной формы при изменении частоты входного источника гармонических колебаний в широких пределах.

Указанный технический результат при осуществлении изобретения достигается тем, что в формирователь сигнала треугольной формы, содержащий первый и второй вычислители модуля, перемножитель, суммирующий блок и вычитатель, при этом выходы первого и второго вычислителей модулей соединены соответственно с первым и вторым входами суммирующего блока, выход которого соединен с выходом формирователя сигнала треугольной формы, первый и второй входы которого соединены с соответствующими входами перемножителя, введен сумматор, при этом первые входы вычитателя и сумматора соединены с первым входом формирователя сигнала треугольной формы, второй вход которого соединен с вторыми входами вычитателя и сумматора, входы первого и второго вычислителей модулей подключены к выходам соответственно вычитателя и сумматора, причем третий вход суммирующего блока соединен с выходом перемножителя.

Проведенный заявителем анализ уровня техники, включающий поиск по патентным и научно-техническим источникам информации, позволил установить, что заявитель не обнаружил аналог, характеризующийся признаками, тождественными всем существенным признакам заявленного изобретения. Следовательно, заявленное изобретение соответствует условию «новизна».

Введение в предлагаемый формирователь сигнала треугольной формы сумматора, а также организация новых связей между функциональными элементами позволило упростить устройство и сохранить высокую линейность сигнала треугольной формы при изменении частоты квадратурных гармонических сигналов в широких пределах.

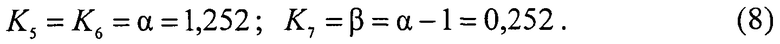

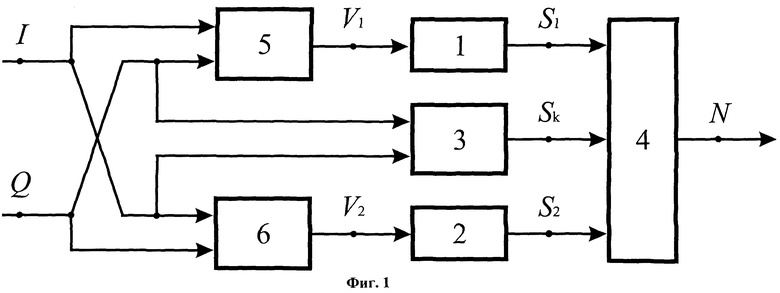

Изобретение поясняется структурной схемой формирователя сигнала треугольной формы (фиг.1) и графиками (фиг.2 - фиг.5), поясняющими принцип работы формирователя сигнала треугольной формы.

Формирователь сигнала треугольной формы содержит первый 1 и второй 2 вычислители модуля, перемножитель 3, суммирующий блок 4, вычитатель 5 и сумматор 6, при этом первые входы вычитателя 5, сумматора 6 и перемножителя 3 соединены с первым входом формирователя сигнала треугольной формы, второй вход которого соединен с вторыми входами вычитателя 5, сумматора 6 и перемножителя 3, к выходу которого подключен третий вход суммирующего блока 4, выход которого соединен с выходом формирователя сигнала треугольной формы, причем первый вычислитель модуля 1 включен между выходом вычитателя 5 и первым входом суммирующего блока 4, а второй вычислитель модуля 2 включен между выходом сумматора 6 и вторым входом суммирующего блока 4.

Формирователь сигнала треугольной формы работает следующим образом.

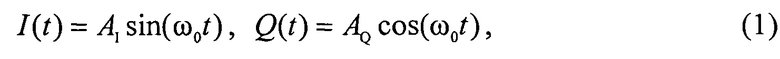

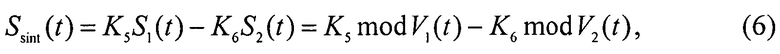

На первый и второй входы формирователя сигнала треугольной формы поступают (фиг.2а) гармонические колебания I(t) и Q(t), сдвинутые друг относительно друга на 90 эл. градусов

где AI и AQ - амплитудные значения входных сигналов I(t) и Q(t), а ω0 - круговая частота сигналов I(t) и Q(t), связанная с циклической частотой f0 известным соотношением ω0=2 πf0.

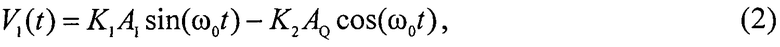

На выходе вычитателя 5 формируется (фиг.2б) сигнал

а на выходе сумматора 6 будет сформирован сигнал (фиг.2б)

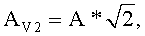

где K1 и K2 - коэффициенты передачи вычитателя 5 соответственно по первому и второму входам; K3 и K4 - коэффициенты передачи сумматора 6 соответственно по первому и второму входам.

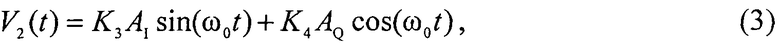

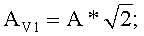

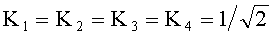

Сумма двух синусоидальных величин с одной и той же частотой ω0 является также синусоидальной величиной с той же самой частотой, причем амплитудное значение результирующего колебания

где AV1 - амплитудное значение формируемого сигнала V1(t);

φI и φQ - начальные фазы сигналов I(t) и Q(t).

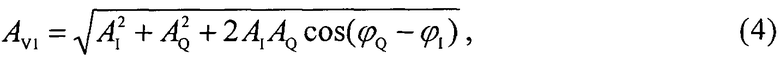

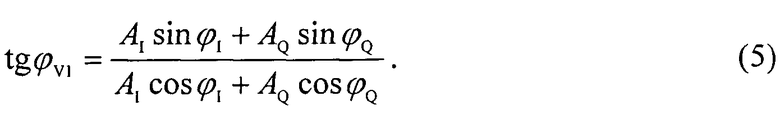

Значение фазы φV1 результирующего сигнала V1(t) можно найти с помощью выражения

Для нормированного значения амплитуд AI=AQ=A*=1 и для φI=0, φQ=π/2 с помощью (4) и (5) получим

На выходе сумматора 6 формируется (фиг.2б) также гармонический сигнал V2(t), для которого

Таким образом, на выходах вычитателя 5 и сумматора 6 формируются квадратурные сигналы V1(t) и V2(t), то есть сдвинутые друг относительно друга на 90 эл. градусов. По отношению к входным сигналам эти сигналы сдвинуты на 45 эл. градусов (фиг.2б).

При

Рассмотрим принцип формирования квазилинейного сигнала треугольной формы N(t).

На вход первого вычислителя модуля 1 подается сигнал V1(t), а на вход второго вычислителя модуля 2 - сигнал V2(t).

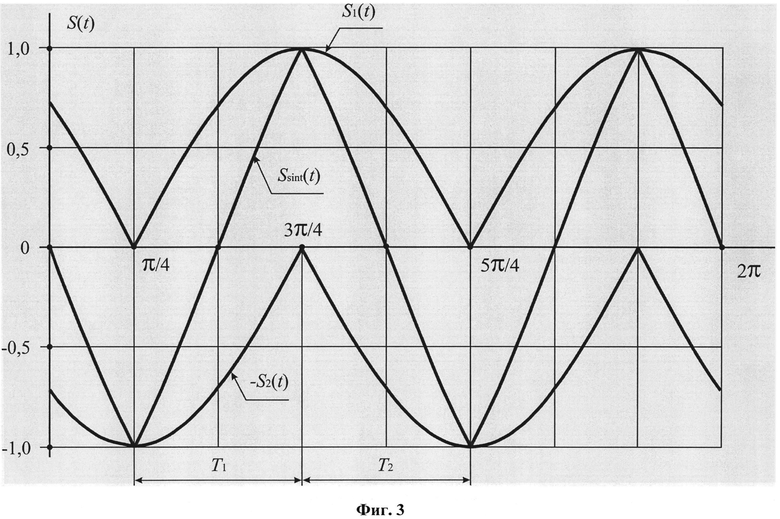

Вычислители модулей 1 и 5 обеспечивают (фиг.3) получение модулей сигналов V1(t) и V2(t), которые поступают соответственно на первый неинвертирующий и второй инвертирующий входы суммирующего блока 4.

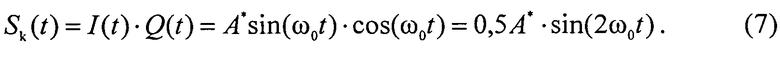

При отсутствии компенсирующего сигнала Sk(t) на выходе суммирующего блока 4 будет сформирован (фиг.3) «виртуальный» синтезированный сигнал

где K5 и K6 - коэффициенты передачи суммирующего блока 4 по первому неинвертирующему и второму инвертирующему входам соответственно.

При K5=K6=1 на выходе суммирующего блока 4 амплитуда сигнала Ssint(t) будет равна нормированному значению амплитуды A* сигналов S1 (t) и S2(t). Частота основной гармоники Ω1 синтезированного сигнала треугольной формы Ssint(t) равна удвоенному значению частоты ω0 квадратурных сигналов I(t) и Q(t).

На участках «прямого хода» (интервал T1 от π/4 до 3π/4) и «обратного хода» (интервал T2 от 3π/4 до 5π/4) сигнал Ssint(t) имеет S-образные характеристики, то есть является «квазилинейным».

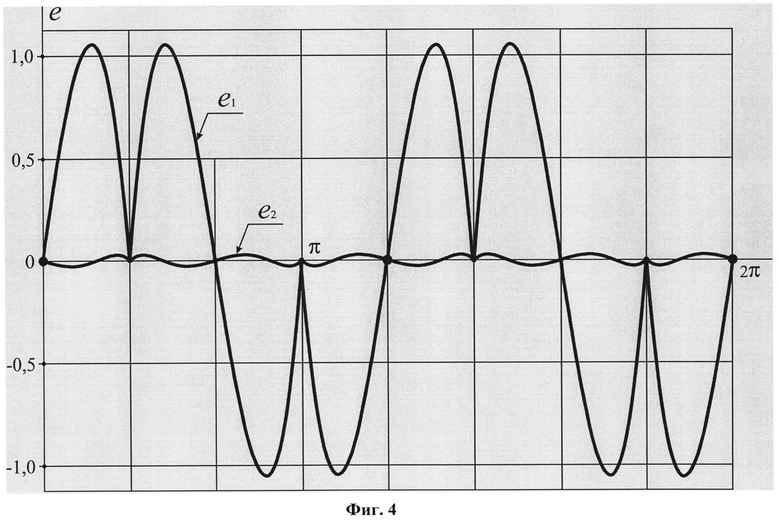

Погрешность e1 синтезированного сигнала Ssint(t) найдем с помощью следующего выражения: e1=S0(t)-Ssint(t), где S0(t) - эталонный сигнал треугольной формы.

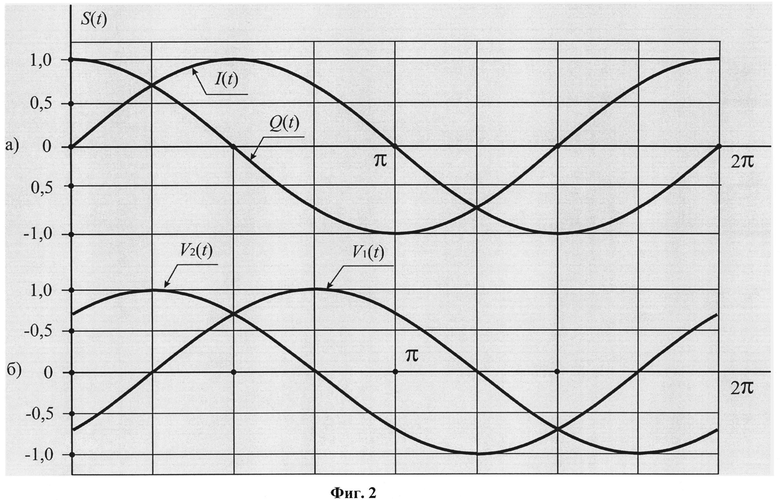

График зависимости e1 от угла x=ω0t приведен на фиг.4. Максимальное отклонение e1 по модулю превышает 4% (e1=42,5 мВ при нормированном значении амплитуды A*=1000 мВ).

Для уменьшения нелинейности сигнала треугольной формы N(t) в прототипе используется большое количество прецизионных, а следовательно, дорогостоящих микросхем (два перемножителя и квадратор, который также может быть выполнен из перемножителя).

В настоящем изобретении предлагается формировать корректирующий сигнал с помощью только одного перемножителя 3

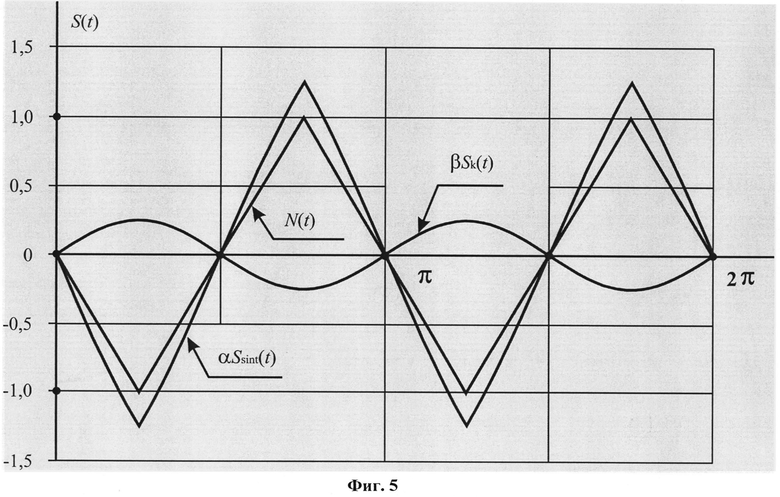

На фиг.5. приведены графические зависимости, поясняющие принцип уменьшения нелинейности формируемого сигнала треугольной формы N(t).

Синтезированный сигнал Ssint(t) умножается на коэффициент α, а корректирующий сигнал Sk(t) - на коэффициент β. При этом необходимо выполнить следующие условия:

Коэффициенты α и β, входящие в (8), обеспечивают минимизацию остаточной погрешности (нелинейности) e2 формируемого сигнала треугольной формы N(t), то есть являются оптимальными.

Погрешность e2=S0(t)-N(t) после введения корректирующего сигнала составляет примерно 1,1 мВ, то есть уменьшается почти в 40 раз.

Введение в формирователь сумматора, а также организация новых связей между функциональными элементами, позволило упростить (по сравнению с прототипом) устройство, снизить его себестоимость и сохранить высокую линейность формируемого сигнала треугольной формы при изменении частоты входного источника гармонических колебаний в широких пределах.

Источники информации

1. Шустов М.А. Схемотехника. 500 устройств на аналоговых микросхемах. Функциональный генератор инверсного построения - (стр.239 - Рис.36.12).

2. Пат. 81859 Российская Федерация, МПК7 H03K 4/06. Аналого-цифровой аддитивный формирователь сигнала треугольной формы / Дубровин B.C., Зюзин A.M.; заявитель и патентообладатель Негосударственное научно-образовательное учреждение «Саранский Дом науки и техники Российского Союза научных и инженерных общественных организаций» (ННОУ «Саранский Дом науки и техники РСНИИОО»). №2008146321/22; заявл. 24.11.2008; опубл. 27.03.2009, Бюл. №9. - 2 с.: 1 ил.

3. Пат. 83669 Российская Федерация, МПК7 H03K 4/06. Аддитивный формирователь сигнала треугольной формы / Дубровин B.C., Зюзин A.M.; заявитель и патентообладатель Негосударственное научно-образовательное учреждение «Саранский Дом науки и техники Российского Союза научных и инженерных общественных организаций» (ННОУ «Саранский Дом науки и техники РСНИИОО»). №2009103327/22; заявл. 02.02.2009; опубл. 10.06.2009, Бюл. №16. - 2 с.: 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОЧАСТОТНЫЙ ФУНКЦИОНАЛЬНЫЙ ГЕНЕРАТОР | 2013 |

|

RU2534938C1 |

| ФУНКЦИОНАЛЬНЫЙ ГЕНЕРАТОР | 2013 |

|

RU2534939C1 |

| ФУНКЦИОНАЛЬНЫЙ ГЕНЕРАТОР | 2013 |

|

RU2541147C1 |

| Формирователь сигнала треугольной формы | 2016 |

|

RU2628434C1 |

| Формирователь сигнала треугольной формы | 2016 |

|

RU2622866C1 |

| ФОРМИРОВАТЕЛЬ ГАРМОНИЧЕСКОГО СИГНАЛА | 2015 |

|

RU2565424C1 |

| Функциональный генератор | 2016 |

|

RU2625555C1 |

| ФУНКЦИОНАЛЬНЫЙ ГЕНЕРАТОР | 2015 |

|

RU2582557C1 |

| ФОРМИРОВАТЕЛЬ ГАРМОНИЧЕСКОГО СИГНАЛА | 2015 |

|

RU2577205C1 |

| ФУНКЦИОНАЛЬНЫЙ ГЕНЕРАТОР КВАДРАТУРНЫХ СИГНАЛОВ | 2015 |

|

RU2582556C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в измерительной, вычислительной технике. Достигаемый технический результат - сохранение высокой линейности формируемого сигнала треугольной формы при изменении частоты входного источника гармонических колебаний в широких пределах. Формирователь сигнала треугольной формы содержит первый и второй вычислители модуля, перемножитель, суммирующий блок, вычитатель и сумматор. 5 ил.

Формирователь сигнала треугольной формы, содержащий первый и второй вычислители модуля, перемножитель, суммирующий блок и вычитатель, при этом выходы первого и второго вычислителей модулей соединены соответственно с первым и вторым входами суммирующего блока, выход которого соединен с выходом формирователя сигнала треугольной формы, первый и второй входы которого соединены с соответствующими входами перемножителя, отличающийся тем, что в него введен сумматор, при этом первые входы вычитателя и сумматора соединены с первым входом формирователя сигнала треугольной формы, второй вход которого соединен с вторыми входами вычитателя и сумматора, входы первого и второго вычислителей модулей подключены к выходам соответственно вычитателя и сумматора, причем третий вход суммирующего блока соединен с выходом перемножителя.

| Способ импульсной телеметрии с применением пассивных датчиков | 1948 |

|

SU83670A1 |

Авторы

Даты

2014-12-20—Публикация

2013-11-12—Подача