Устройство относится к области электротехники и может быть использовано в качестве температурно-стабильного источника опорного напряжения (ИОН).

Известны температурно-стабильные источники опорного напряжения, определяемого удвоенной шириной запрещенной зоны полупроводника, к недостатком которых относится излишняя сложность, вызванная использованием большого количества элементов [U.S. Patent 4380706. Voltage reference circuit / Robert S. Wrathall. - Dec. 24, 1980], и необходимость дополнительного подключения к источнику питающего напряжения, а не только к источнику тока [Соклоф С. Аналоговые интегральные схемы: Пер. с англ. - М.: Мир, 1988. - С.240, рис.33.27], что существенно затрудняет их использование в качестве опорного диода.

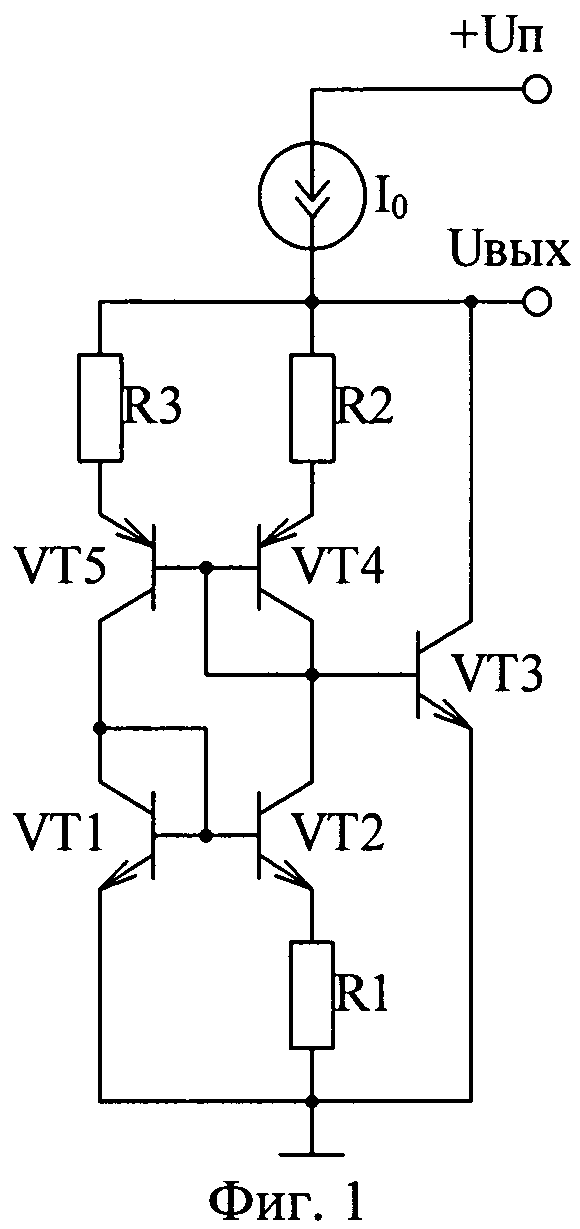

Наиболее близким техническим решением, принятым за прототип, является ИОН, приведенный на фиг.1 [Патент RU 2488874 C1, МПК G05F 1/56; H03F 1/30 (2006.01). - Опубл. 27.07.2013, Бюл. №21]. Недостатком прототипа является относительно высокий температурный дрейф выходного напряжения (около 10 мВ на 100°C).

Задача, на решение которой направлено предлагаемое изобретение, заключается в обеспечении заявляемого технического результата - снижении температурного коэффициента выходного напряжения ИОН.

Для достижения заявляемого технического результата в схему прототипа, содержащую источник тока, включенный между шиной питания и выходной клеммой, первый резистор, подключенный первым выводом к общей шине, второй и третий резисторы, подключенные первыми выводами к выходной клемме, первый транзистор, эмиттер которого подключен к общей шине, второй транзистор, эмиттер которого подключен ко второму выводу первого резистора, третий транзистор, коллектор которого подключен к выходной клемме, а эмиттер - к общей шине, четвертый и пятый транзисторы, базы которых соединены, коллектор пятого транзистора соединен с коллектором первого и базами первого и второго транзисторов, эмиттер четвертого транзистора подключен ко второму выводу второго резистора, эмиттер пятого транзистора подключен ко второму выводу третьего резистора, коллекторы четвертого и второго транзисторов подключены к базе третьего транзистора, введено соединение базы четвертого транзистора с коллектором первого транзистора.

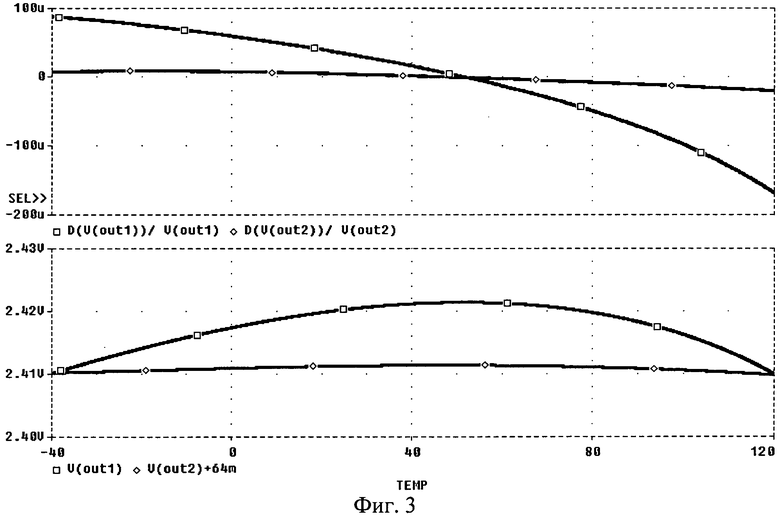

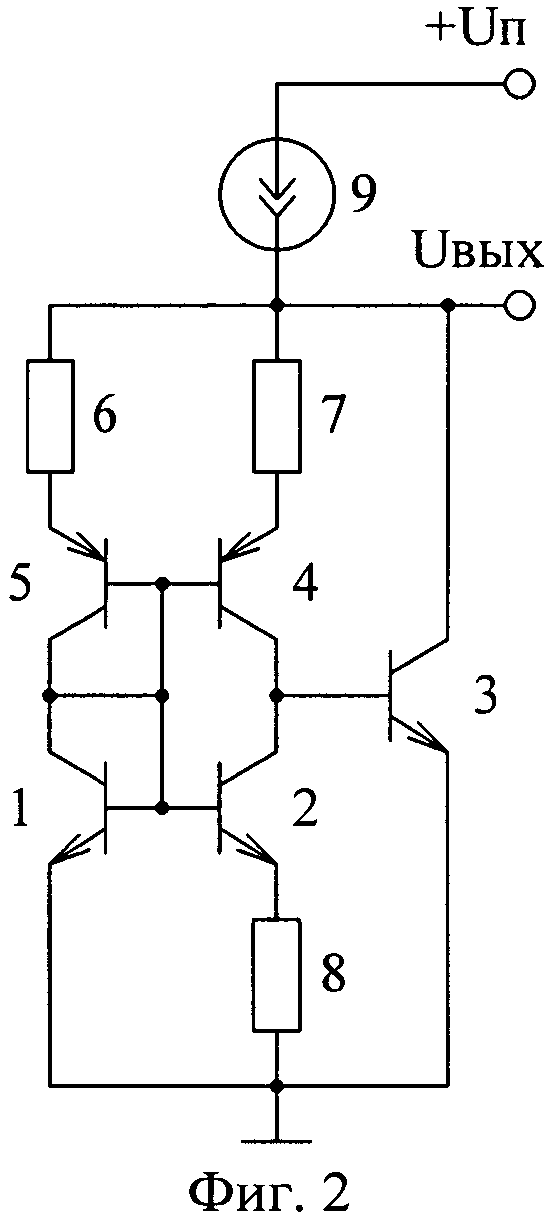

Схема прототипа приведена на фиг.1. Схема заявляемого устройства представлена на фиг.2. На фиг.3 приведены результаты моделирования.

Заявляемый ИОН (фиг.2) содержит пять транзисторов (с первого по пятый), обозначенных, соответственно, цифрами 1-5, и три резистора (с первого по третий), обозначенные, соответственно, цифрами 6, 7 и 8, и источник тока 9, включенный между шиной питания и выходной клеммой, резисторы 6 и 7 подключены первыми выводами к выходной клемме, базы транзисторов 1, 2, 4 и 5 соединяются с коллекторами транзисторов 1 и 5, резистор 8 включен между общей шиной и эмиттером транзистора 2, эмиттеры транзисторов 1 и 3 подключены к общей шине, коллектор транзистора 3 подключен к выходной клемме, база транзистора 3 соединяется с коллекторами транзисторов 2 и 4, эмиттер транзистора 4 подключен ко второму выводу резистора 7, эмиттер транзистора 5 подключен ко второму выводу резистора 6.

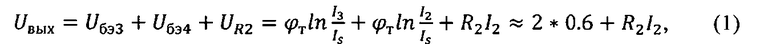

Прежде чем рассмотреть работу заявляемого устройства, рассмотрим работу схемы прототипа (фиг.1), так как это необходимо для сопоставительного анализа. При этом допустим, что токи баз транзисторов пренебрежимо малы, а ток нагрузки отсутствует. Выходное напряжение Uвых прототипа определяется суммой напряжений база-эмиттер Uбэ3 и Uбэ4 транзисторов VT3 и VT4, а также падением напряжения UR2 на резисторе R2, что может быть описано следующим выражением:

где φт≈26 мВ - температурный потенциал; I2 и I3 - токи эмиттеров транзисторов VT2 и VT3 соответственно; Is - ток насыщения обратносмещенного p-n перехода, пропорциональный его площади; R2 - сопротивление резистора R2.

Для нахождения тока I2 следует учесть напряжения база-эмиттер Uбэ1 и Uбэ2, соответственно, транзисторов VT1 и VT2 и падение напряжения UR1 на резисторе R1, записав выражение:

или

где R1 - сопротивление резистора R1; I1 - ток эмиттера транзистора VT1; N - отношение площадей эмиттеров транзисторов VT2 и VT1.

Приближенное соотношение (2) справедливо при равенстве токов I1 и I2. Отсюда можно определить ток

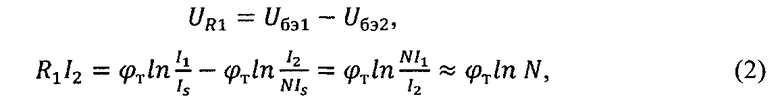

Дифференцируя выражение (3), можно определить зависимость приращения тока I2 от температуры T:

где φт=kT/q; k - постоянная Больцмана; T - абсолютная температура; q - заряд электрона.

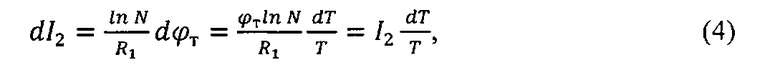

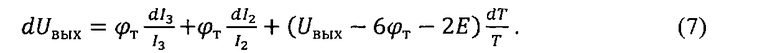

Дифференцируя выражение (1), получим

Для нахождения приращений dUбэ следует учесть зависимость

где C - постоянный коэффициент, определяемый технологией производства интегрального транзистора; Е - энергетическая ширина запрещенной зоны при абсолютном нуле, полученная линейной экстраполяцией от комнатной температуры к абсолютному нулю, равная для кремния 1,205 В.

Можно показать, что выражение (5), с учетом (1), (3), (6), приводится к виду

Первое и второе слагаемое в выражении (7) обусловлены, соответственно, изменением напряжений Uбэ3 и Uбэ4.

Так как сумма токов I1, I2 и I3 постоянна, то приращение dl3=-dI1-dI2, а при равных токах I1, I2, I3 и приближенном равенстве приращений dI1 и dI2, с учетом (4), получаем

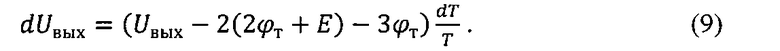

Выражение (7), с учетом (8), можно привести к следующему виду:

Приравнивая (9) к нулю, получаем условие настройки, при котором нестабильность выходного напряжения по температуре близка к нулю:

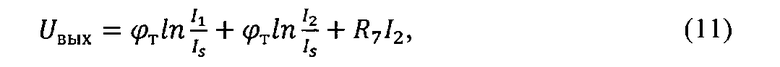

Работа заявляемого устройства аналогична работе прототипа. Однако выходное напряжение определяется суммой напряжений база-эмиттер транзисторов 1 и 4, что описывается следующим выражением:

где R7 - сопротивление резистора 7; I1 и I2 - токи эмиттеров транзисторов 1 и 4 соответственно.

Токи I1 и I2 равны току эмиттера транзистора 2 и определяются выражением:

где R8 - сопротивление резистора 8; N - отношение площадей эмиттеров транзисторов 2 и 1.

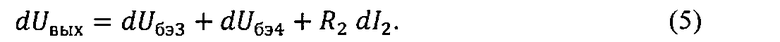

Дифференцируя выражение (10), можно вывести равенства:

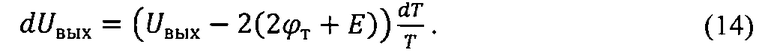

Дифференцируя выражение (11), с учетом (6), (12) и (13), получим:

Откуда следует условие настройки:

Сравнивая выражения (10) и (15), можно сделать вывод о близости температурно-стабильного выходного напряжения к удвоенной ширине запрещенной зоны для обеих схем. А поскольку напряжение база-эмиттер транзистора 3 практически не влияет на выходное напряжение, схема заявляемого устройства обеспечивает более высокую стабильность выходного напряжения, чем схема прототипа.

Представленные на фиг.3 результаты моделирования отображают зависимость выходного напряжения прототипа (out1) и заявляемого устройства (out2) от температуры. При этом для удобства сравнения напряжение out2 увеличено на 64 мВ (нижняя диаграмма). На верхней диаграмме представлены соответствующие относительные нестабильности выходного напряжения.

Таким образом, и проведенный анализ, и данные схемотехнического моделирования подтверждают, что для заявляемого устройства достигается заявляемый технический результат - получается температурно-стабильное выходное напряжение при значениях, близких к удвоенной ширине запрещенной зоны.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИСТОЧНИК ОПОРНОГО НАПРЯЖЕНИЯ | 2012 |

|

RU2518974C2 |

| ИСТОЧНИК ОПОРНОГО НАПРЯЖЕНИЯ, ОПРЕДЕЛЯЕМОГО УДВОЕННОЙ ШИРИНОЙ ЗАПРЕЩЕННОЙ ЗОНЫ | 2012 |

|

RU2488874C1 |

| ИСТОЧНИК ОПОРНОГО НАПРЯЖЕНИЯ | 2012 |

|

RU2504817C1 |

| ИСТОЧНИК ОПОРНОГО НАПРЯЖЕНИЯ | 2011 |

|

RU2461048C1 |

| ТЕМПЕРАТУРНО СТАБИЛЬНЫЙ РАДИАЦИОННО СТОЙКИЙ ИСТОЧНИК ОПОРНОГО НАПРЯЖЕНИЯ НА ОСНОВЕ ДИФФЕРЕНЦИАЛЬНОЙ ПАРЫ ПОЛЕВЫХ ТРАНЗИСТОРОВ | 2014 |

|

RU2546083C1 |

| ИСТОЧНИК ОПОРНОГО НАПРЯЖЕНИЯ | 2013 |

|

RU2523121C1 |

| ИСТОЧНИК ОПОРНОГО НАПРЯЖЕНИЯ | 2011 |

|

RU2461864C1 |

| ИСТОЧНИК ОПОРНОГО НАПРЯЖЕНИЯ | 2015 |

|

RU2580458C1 |

| ИСТОЧНИК ОПОРНОГО НАПРЯЖЕНИЯ | 2011 |

|

RU2449342C1 |

| ИСТОЧНИК ОПОРНОГО НАПРЯЖЕНИЯ | 2012 |

|

RU2519270C1 |

Изобретение относится к области электротехники и может быть использовано в качестве температурно-стабильного источника опорного напряжения, определяемого удвоенной шириной запрещенной зоны. Технический результат заключается в получении температурно-стабильного выходного напряжения, значение которого близко к удвоенной ширине запрещенной зоны используемого полупроводника. Устройство содержит пять транзисторов, три резистора и источник тока, включенный между шиной питания и выходной клеммой, первый резистор подключен первым выводом к общей шине, второй и третий резисторы подключены первыми выводами к выходной клемме, базы первого и второго транзисторов соединяются с коллекторами первого и пятого и базами четвертого и пятого транзисторов, второй вывод первого резистора подключен к эмиттеру второго транзистора, эмиттеры первого и третьего транзисторов подключены к общей шине, коллектор третьего транзистора подключен к выходной клемме, база третьего транзистора соединяется с коллекторами второго и четвертого транзисторов, эмиттер четвертого транзистора подключен ко второму выводу второго резистора, эмиттер пятого транзистора подключен ко второму выводу первого резистора. 3 ил.

Стабилизатор напряжения, содержащий источник тока, включенный между шиной питания и выходной клеммой, первый резистор, подключенный первым выводом к общей шине, второй и третий резисторы, подключенные первыми выводами к выходной клемме, первый транзистор, эмиттер которого подключен к общей шине, второй транзистор, эмиттер которого подключен ко второму выводу первого резистора, третий транзистор, коллектор которого подключен к выходной клемме, а эмиттер - к общей шине, четвертый и пятый транзисторы, базы которых соединены, коллектор пятого транзистора соединен с коллектором первого и базами первого и второго транзисторов, эмиттер четвертого транзистора подключен ко второму выводу второго резистора, эмиттер пятого транзистора подключен ко второму выводу третьего резистора, коллекторы четвертого и второго транзисторов подключены к базе третьего транзистора, отличающийся тем, что база четвертого транзистора соединяется с коллектором первого транзистора.

| СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ | 2002 |

|

RU2211477C1 |

| ИСТОЧНИК ОПОРНОГО НАПРЯЖЕНИЯ | 2011 |

|

RU2461048C1 |

| Станок для изготовления деревянных ниточных катушек из цилиндрических, снабженных осевым отверстием, заготовок | 1923 |

|

SU2008A1 |

| US 5808507 A, 15.09.1998 | |||

Авторы

Даты

2015-02-20—Публикация

2014-03-18—Подача