Изобретение относится к области электротехники. Технический результат, на достижение которого направлено заявляемое изобретение, заключается в расширении функциональных возможностей за счет передачи n-фазного напряжения по двухпроводной сети.

Цель изобретения - расширение функциональных возможностей устройства.

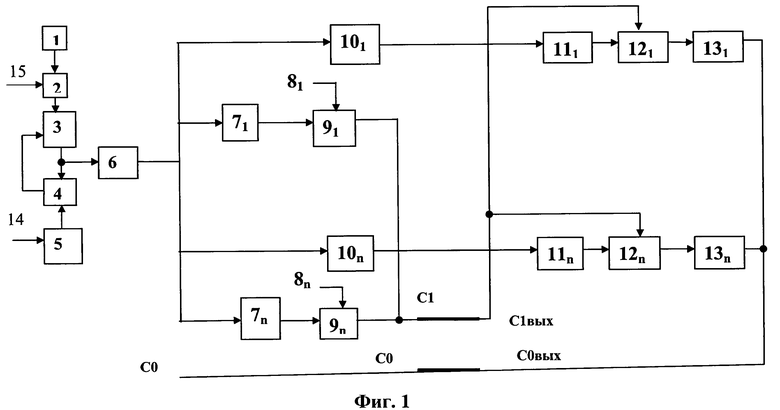

Устройство в своем составе содержит: генератор тактовых импульсов 1, логический элемент И 2; счетчик числа фаз 3, схему сравнения 4, регистр 5, дешифратор 6, формирователи управляющих сигналов 7i (i=1…n, n - число фаз в сети), фазы многофазного источника синусоидального ЭДС 8i (i=1…n), управляемые симисторы 9i (i=1…n), элементы задержки 10i (i=1…n), формирователи управляющих сигналов 11i (i=1…n, n - число фаз в сети), управляемые симисторы 12i (i=1…n), фазы многофазной нагрузки сети 13i (i=1…n), входы 14 и 15, линию передачи сигналов с полюсами С1-С0 на входе и С1вых-С0вых на выходе линии 20 вместе со связями.

Известные устройства для передачи напряжений [1] не позволяют передавать n-фазное напряжение по двухпроводной сети.

Наиболее близким по технической сущности к заявляемому устройству является устройство [1], содержащее нагрузку 13i (i=1…n), нулевой провод С0-С0вых, подключенный к нулевой точке многофазной системы ЭДС по схеме «звезда», первую группу ключей 9i (i=1…n), n входов 8i (i=1…n) фаз многофазной системы ЭДС, каждая из которых подсоединена к первому входу одноименного ключа 9i (i=1…n) первой группы.

Недостатком данного устройства является невозможность передачи n-фазного напряжения по двухпроводной сети.

Задача изобретения - создать устройство, обеспечивающее возможность передачи n-фазного напряжения по двухпроводной сети.

Сущность изобретения состоит в том, что в известное устройство [1], содержащее нагрузку 13i (i=1…n), нулевой провод С0-С0вых, подключенный к нулевой точке многофазной системы ЭДС по схеме «звезда», первую группу ключей 9i (i=1…n), n входов 8i (i=1…n) фаз многофазной системы ЭДС, каждая из которых подсоединена к первому входу одноименного ключа 9i (i=1…n) первой группы, дополнительно включены вторая группа ключей 12i (i=1…n), генератор тактовых импульсов (ГТИ) 1, элемент И 2, счетчик 3, схема сравнения 4, регистр 5, дешифратор 6, первые формирователи сигналов 7i (i=1…n), группа элементов задержки 10i (i=1…n), вторые формирователи сигналов 11i (i=1…n), выход ГТИ 1 подсоединен к первому входу элемента И 2, второй вход которого подсоединен к первому входу 15 устройства, а выход - к первому входу счетчика 3, выход которого подсоединен к входу дешифратора 6 и к первому входу схемы сравнения 4, второй вход которой подсоединен к выходу регистра 5, а выход - к второму входу счетчика 3, вход регистра 5 подсоединен к входу 14 устройства, выходы дешифратора 6 подсоединены к входам одноименных первых формирователей сигналов 7i (i=1…n) и через одноименные элементы задержки 10i (i=1…n) к входам одноименных вторых формирователей сигналов 11i (i=1…n), выходы первых формирователей сигналов 7i (i=1…n) подсоединены к управляющим входам ключей 9i (i=1…n) первой группы, выход каждого из которых подсоединен к входной линии передачи С1, выход которой подсоединен к выходной линии передач С1вых, выход которой подсоединен к первым входам второй группы ключей 12i (i=1…n), управляющий вход каждого из которых подсоединен к выходу одноименных вторых формирователей сигналов 11i (i=1…n), а выход - к нагрузке 13i (i=1…n).

Проведенный поиск в известной научно-технической литературе не выявил наличие подобных технических решений.

Новизна предлагаемого устройства заключается в том, что новое техническое устройство отличается от прототипа тем, что дополнительно в него введены вторая группа ключей 12i (i=1…n), генератор тактовых импульсов (ГТИ) 1, элемент И 2, счетчик 3, схема сравнения 4, регистр 5, дешифратор 6, первые формирователи сигналов 7i (i=1…n), группа элементов задержки 10i (i=1…n), вторые формирователи сигналов 11i (i=1…n), выход ГТИ 1 подсоединен к первому входу элемента И 2, второй вход которого подсоединен к первому входу 15 устройства, а выход - к первому входу счетчика 3, выход которого подсоединен к входу дешифратора 6 и к первому входу схемы сравнения 4, второй вход которой подсоединен к выходу регистра 5, а выход - к второму входу счетчика 3, вход регистра 5 подсоединен к входу 14 устройства, выходы дешифратора 6 подсоединены к входам одноименных первых формирователей сигналов 7i (i=1…n) и через одноименные элементы задержки 10i (i=1…n) к входам одноименных вторых формирователей сигналов 11i (i=1…n), выходы первых формирователей сигналов 7i (i=1…n) подсоединены к управляющим входам ключей 9i (i=1…n) первой группы, выход каждого из которых подсоединен к входной линии передачи С1, выход которой подсоединен к выходной линии передач С1вых, выход которой подсоединен к первым входам второй группы ключей 12i (i=1…n), управляющий вход каждого из которых подсоединен к выходу одноименных вторых формирователей сигналов 11i (i=1…n), а выход - к нагрузке 13i (i=1…n).

Изобретательский уровень достигается тем, что ввод соответствующих элементов в известный прототип вместе со связями позволяет решить новую техническую задачу, решение которой в известных компьютерах и в литературе в настоящее время не отражено. Предлагаемое устройство позволяет расширить функциональные возможности за счет передачи n-фазного напряжения по двухпроводной сети.

Сущность изобретения поясняется чертежом. На чертеже (фиг.1) представлена структурная схема предлагаемого устройства, где на фиг.1 где представлены: генератор тактовых импульсов 1, логический элемент И 2; счетчик числа фаз 3, схема сравнения 4, регистр 5, дешифратор 6, формирователи управляющих сигналов 7i (i=1…n, n - число фаз в сети), фазы многофазного источника синусоидального ЭДС 8i (i=1…n), управляемые ключи (симисторы) 9i (i=1…n), элементы задержки 10i (i=1…n), формирователи управляющих сигналов 11i (i=1…n, n - число фаз в сети), управляемые ключи (симисторы) 12i (i=1…n), фазы многофазной нагрузки сети 13i (i=1…n), входы 14 и 15, линия передачи сигналов с полюсами С1-С0 на входе и С1вых-С0вых на выходе линии.

Точка С0 подключена к нулевой точке многофазной системы ЭДС, включенной по схеме «звезда». Точка С0вых подключена к нулевой точке многофазной нагрузки, включенной также по схеме «звезда».

Симистор 9i (i=1…n) в каждой фазе является управляемым силовым ключом, коммутирующим сигналы произвольной (положительной или отрицательной) полярности. Он включается последовательно в цепь для передачи импульса сигнала фазы положительной или отрицательной полярности длительностью ∇t от многофазного источника 8i в линию С1-С0, а симистор 12i (i=1…n) коммутирует сигнал на выходе линии для последующей передачи импульсов в нагрузку 13i.

Частота генератора 1 задается таким образом, чтобы появление очередного сигнала на его выходе соответствовало суммарной задержке сигнала элементами И 2, счетчика 3, дешифратора 6 и формирователя управляющего сигнала 7i.

Устройство работает следующим образом.

В исходном состоянии на регистре 5 по входу 14 записан код числа фаз n. К входам 8i симисторов 9 подключены соответствующие фазы источников напряжения ei (i=1…n). На счетчике 3 хранится код нуля (вход сброса в ноль на счетчик 3 на фиг.1 не показан).

Работа устройства начинается после подачи пускового сигнала по входу 15 логического элемента И 2, после чего импульсы с выхода генератора тактовых импульсов 1 через открытый элемент И 2 начинают поступать на вход счетчика 3. Код с выхода счетчика 3 поступает на вход дешифратора 6, на выходе которого появляется единичный сигнал только на одном из n его выходов. Единичный сигнал на i-м (i=1…n) выходе дешифратора 6 подается на вход одноименного формирователя сигнала 7i, выход которого подсоединен к управляющему электроду симистора 9i, который работает в режиме ключа. Симистор 9i в свою очередь обеспечивает передачу входного напряжения i-й фазы в линию передачи С1.

Одновременно сигнал с i-го (i=1…n) выхода дешифратора 6 поступает на вход элемента задержки 10i, с выхода которого через элемент 11i сформированный сигнал поступает на управляющий электрод симистора 12i.

Элемент задержки 10i обеспечивает задержку сигнала на время срабатывания элементов 7i и 9i. Таким образом сигнал одноименной фазы ui (i=1…n) длительностью ∇t передается на i-ю фазу нагрузки 13i (i=1…n). Очередной сигнал на эту же фазу поступит через интервал времени T=∇t*n.

При достижении счетчиком 3 числа n на выходе схемы сравнения 4 появляется единичный сигнал, который сбрасывает счетчик 3 в нулевое состояние, после чего цикл передачи импульсов сигналов фаз в линию передачи С1-С0 повторяется.

Источники информации

1. Патент №2400914, кл. H02M 5/16, 2010.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ПЕРЕДАЧИ МНОГОФАЗНОЙ СИСТЕМЫ НАПРЯЖЕНИЙ ПО ОДНОПРОВОДНОЙ ЛИНИИ | 2016 |

|

RU2616585C1 |

| УСТРОЙСТВО ПЕРЕДАЧИ N-ФАЗНОЙ СИСТЕМЫ НАПРЯЖЕНИЙ ПО БЕСПРОВОДНОЙ СЕТИ | 2015 |

|

RU2594290C1 |

| Устройство для передачи многофазной системы напряжений по оптоволоконной линии | 2017 |

|

RU2646618C1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ СИСТЕМЫ ЗАЩИТЫ ВЫЧИСЛИТЕЛЬНОЙ СЕТИ | 2007 |

|

RU2335016C1 |

| Устройство для формирования потенциала инновационного проекта | 2017 |

|

RU2669071C1 |

| МНОГОВЫХОДНОЕ УСТРОЙСТВО ПРИОРИТЕТА | 2015 |

|

RU2613536C1 |

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ЗАДАЧИ О РЮКЗАКЕ | 2014 |

|

RU2542661C1 |

| Генератор многофазной системы ЭДС | 2016 |

|

RU2633662C1 |

| Устройство для регулирования натяжения материала в многосекционной непрерывно-поточной линии | 1988 |

|

SU1664712A1 |

| Способ синхронизации работы элементарных процессоров мажоритарно-резервированных вычислительных комплексов | 2024 |

|

RU2835006C1 |

Изобретение относится к области электротехники. Технический результат заключается в расширении функциональных возможностей за счет передачи n-фазного напряжения по двухпроводной сети. Устройство передачи n-фазной системы напряжений по двухпроводной сети, содержащее нагрузку 13i (i=1…n), нулевой провод С0-С0вых, подключенный к нулевой точке многофазной системы ЭДС по схеме «звезда», первую группу ключей 9i (i=1…n), n входов 8i (i=1…n) фаз многофазной системы ЭДС, каждая из которых подсоединена к первому входу одноименного ключа 9i (i=1…n) первой группы, дополнительно включены вторая группа ключей 12i (i=1…n), генератор тактовых импульсов (ГТИ) 1, элемент И 2, счетчик 3, схема сравнения 4, регистр 5, дешифратор 6, первые формирователи сигналов 7i (i=1…n), группа элементов задержки 10i (i=1…n), вторые формирователи сигналов 11i (i=1…n), выход ГТИ 1 подсоединен к первому входу элемента И 2, второй вход которого подсоединен к первому входу 15 устройства, а выход - к первому входу счетчика 3, выход которого подсоединен к входу дешифратора 6 и к первому входу схемы сравнения 4, второй вход которой подсоединен к выходу регистра 5, а выход - к второму входу счетчика 3, вход регистра 5 подсоединен к входу 14 устройства, выходы дешифратора 6 подсоединены к входам одноименных первых формирователей сигналов 7i (i=1…n) и через одноименные элементы задержки 10i (i=1…n) к входам одноименных вторых формирователей сигналов 11i (i=1…n), выходы первых формирователей сигналов 7i (i=1…n) подсоединены к управляющим входам ключей 9i (i=1…n) первой группы, выход каждого из которых подсоединен к входной линии передачи С1, выход которой подсоединен к выходной линии передач С1вых, выход которой подсоединен к первым входам второй группы ключей 12i (i=1…n), управляющий вход каждого из которых подсоединен к выходу одноименных вторых формирователей сигналов 11i (i=1…n), а выход - к нагрузке 13i (i=1…n). 1 ил.

Устройство передачи n-фазной системы напряжений по двухпроводной сети, содержащее нагрузку 13i(i=1…n), нулевой провод С0-С0вых, подключенный к нулевой точке многофазной системы ЭДС по схеме «звезда», первую группу ключей 9i(i=1…n), n входов 8i(i=1…n) фаз многофазной системы ЭДС, каждая из которых подсоединена к первому входу одноименного ключа 9i(i=1…n) первой группы, отличающееся тем, что в него дополнительно включены вторая группа ключей 12i(i=1…n), генератор тактовых импульсов (ГТИ) 1, элемент И 2, счетчик 3, схема сравнения 4, регистр 5, дешифратор 6, первые формирователи сигналов 7i(i=1…n), группа элементов задержки 10i(i=1…n), вторые формирователи сигналов 11i(i=1…n), выход ГТИ 1 подсоединен к первому входу элемента И 2, второй вход которого подсоединен к первому входу 15 устройства, а выход - к первому входу счетчика 3, выход которого подсоединен к входу дешифратора 6 и к первому входу схемы сравнения 4, второй вход которой подсоединен к выходу регистра 5, а выход - к второму входу счетчика 3, вход регистра 5 подсоединен к входу 14 устройства, выходы дешифратора 6 подсоединены к входам одноименных первых формирователей сигналов 7i(i=1…n) и через одноименные элементы задержки 10i(i=1…n) к входам одноименных вторых формирователей сигналов 11i(i=1…n), выходы первых формирователей сигналов 7i(i=1…n) подсоединены к управляющим входам ключей 9i(i=1…n) первой группы, выход каждого из которых подсоединен к входной линии передачи С1, выход которой подсоединен к выходной линии передач С1вых, выход которой подсоединен к первым входам второй группы ключей 12i(i=1…n), управляющий вход каждого из которых подсоединен к выходу одноименных вторых формирователей сигналов 11i(i=1…n), а выход - к нагрузке 13i(i=1…n).

| Непосредственный преобразователь частоты | 1990 |

|

SU1750002A1 |

| Электропривод переменного тока | 1990 |

|

SU1767687A1 |

| US5214366A, 25.05.1992 | |||

Авторы

Даты

2015-03-10—Публикация

2012-10-29—Подача