Изобретение относится к автоматике и вычислительной технике и может быть использовано для непрерывного контроля работоспособности средств вычислительной техники, функционирующих в условиях непрерывной динамики и постоянных изменений параметров внешних условий и с учетом повышенных требований к их надежности, а также с синхронизацией работы элементарных процессоров (ЭП) мажоритарно-резервированных вычислительных комплексов.

Известен способ синхронизации работы элементарных процессоров мажоритарно-резервированных вычислительных комплексов [1]. Согласно известному способу мажоритирования формируют отказоустойчивую вычислительную систему, содержащую отказоустойчивый вычислительный комплекс в составе группы элементарных центральных процессоров, выходная информация с выходов которых мажоритируется способом «n и более из (2n-1)».

Недостатком данного способа является отсутствие устойчивой синхронизации совместной работы элементарных центральных процессоров, выходная информация с выходов которых мажоритируется способом «n и более из (2n-1)».

Наиболее близким к предложенному решению является способ мажоритирования в вычислительной системе [1], в соответствии с которым в вычислительной системе формируют отказоустойчивую вычислительную систему, содержащую группу центральных процессоров, выходная информация с выходов которых мажоритируется одним из способов: 2 из 3, 3 и более из 5, 4 и более из 7 или 5 и более из 9 и т.д.

Технический результат предлагаемого изобретения - непрерывный контроль работоспособности средств вычислительной техники, функционирующих в условиях непрерывной динамики и постоянных изменений параметров внешних условий и с учетом повышенных требований к их надежности, а также с синхронизацией работы элементарных процессоров мажоритарно - резервированных вычислительных комплексов.

Технический результат достигается тем, что в способе синхронизации работы элементарных процессоров мажоритарно-резервированных вычислительных комплексов формируют отказоустойчивый вычислительный комплекс, содержащий группу элементарных центральных процессоров, выходная информация с выходов которых мажоритируется способом n и более из (2n-1), при этом мажоритирование входных сигналов осуществляется путем формирования тактирующих сигналов, ведется подсчет поступивших входных сигналов из каналов вычислительного комплекса и при достижении числа поступивших сигналов n>((2n-1)/2) выдается выходной мажоритированный сигнал с выхода мажоритарного органа.

Способ включает следующие операции:

1. Формируют отказоустойчивый вычислительный комплекс, содержащий группу (2n-1) элементарных центральных процессоров, выходная информация с выходов которых мажоритируется способом «n и более из (2n-1)».

2. Формируют серию тактирующих сигналов для последующего мажоритирования входных сигналов.

3. Ведут подсчет поступивших входных сигналов из каналов вычислительного комплекса.

4. При достижении числа поступивших сигналов «n>((2n-1)/2)» выдают выходной мажоритированный сигнал с выхода мажоритарного органа.

Способ синхронизации работы элементарных процессоров мажоритарно-резервированных вычислительных комплексов, функционирующих в условиях непрерывной динамики и постоянных изменений параметров внешних условий обеспечивает устойчивую синхронизацию работы элементарных процессоров мажоритарно-резервированных вычислительных комплексов.

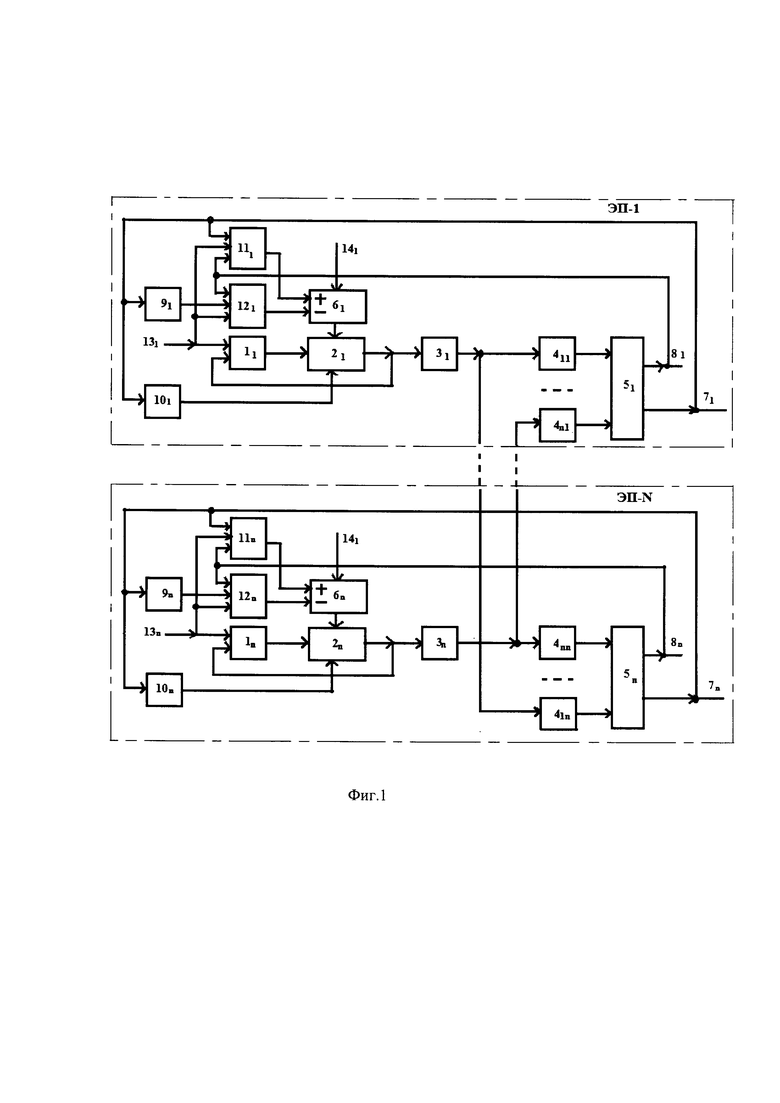

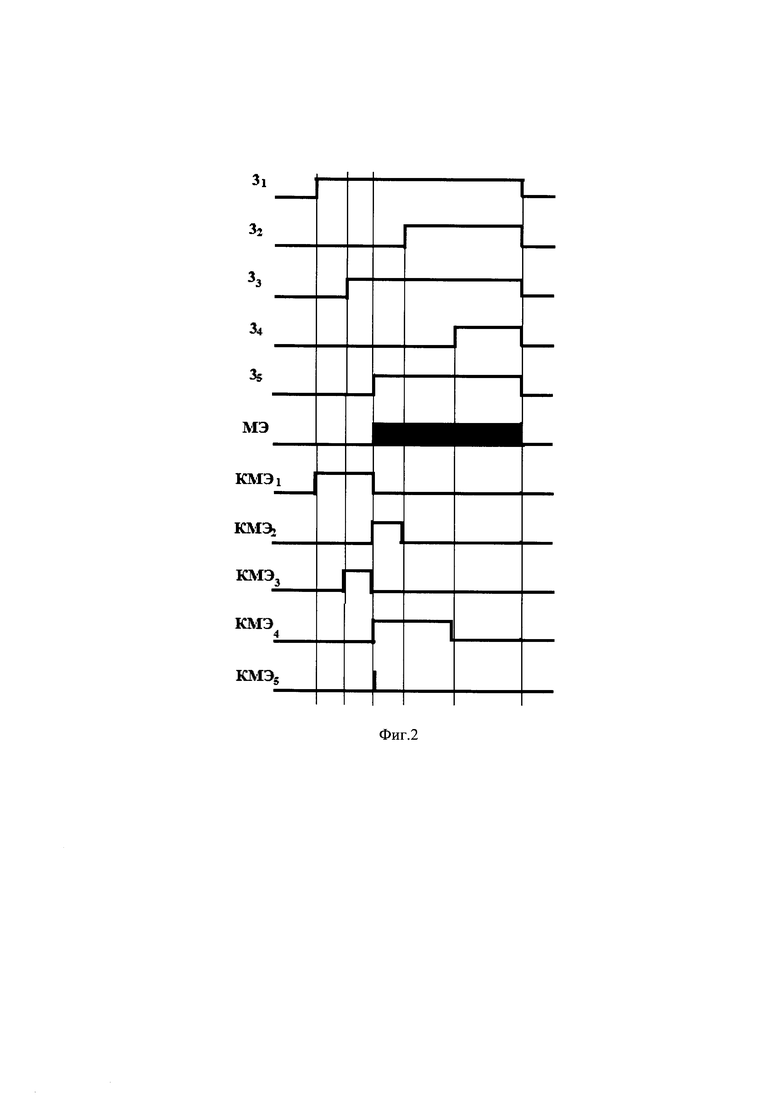

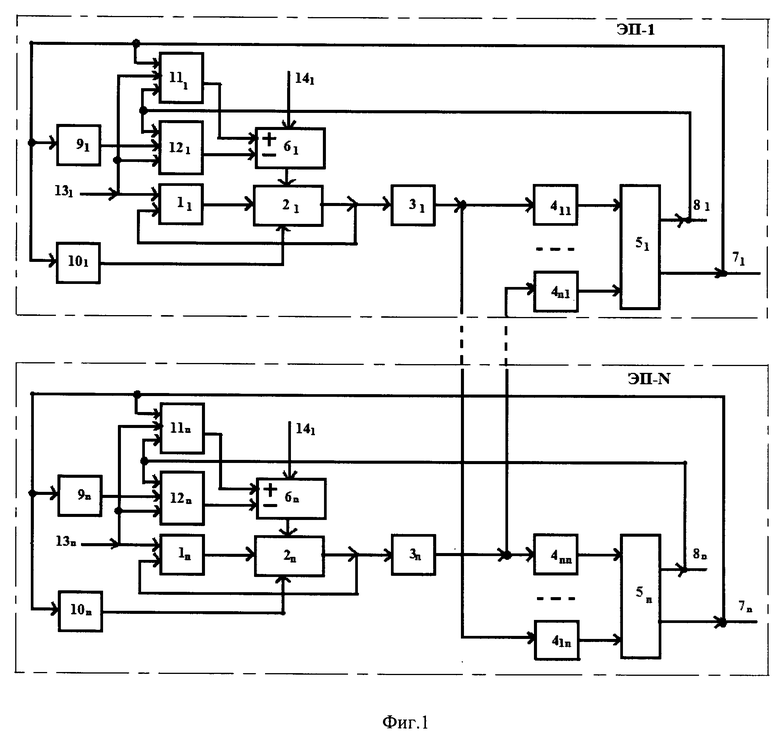

Одной из проблем работы схемы, представленной на фиг. 1, является компенсация времени перекоса сигналов между комплектами комплекса, так как длина межкомплектных связей в расположении вычислительного комплекса, а значит и время распространения сигналов между ними, различны. Время перекоса при этом приводит к ложному срабатыванию цепей контроля мажоритарных элементов и расхождению сигналов на выходах мажоритарных элементов различных комплектов. Формирование сигналов на входах мажоритарных элементов в различных комплектах (в качестве примера) для варианта «3 из 5» показано на фиг. 2.

Работу способа синхронизации работы элементарных процессоров мажоритарно - резервированных вычислительных комплексов ниже рассмотрим на примере работы вычислительного комплекса (см. фиг. 1).

Устройство содержит:

- элементы И 11 - 1n;

- счетчики 21 - 2n;

- элементы НЕ 31 - 3n;

- повторители 41 - 4n;

- мажоритарные элементы 51 - 5n;

- счетчики 61 - 6n;

- выходы мажоритарных элементов 71 - 7n;

- выходы контроля работы мажоритарных элементов 81 - 8n;

- элементы НЕ 91 - 9n;

- элементы задержки 101 - 10n;

- элементы И 111 - 11n;

- элементы И 121 - 12n;

- входы тактовой частоты 131 - 13n;

- входы кодов допустимых времен перекоса 141 - 14n.

В исходном состоянии по входам 14i (i=1…n) от процессоров комплекса устанавливается код допустимого времени перекоса поступающих мажоритируемых сигналов на счетчиках 6i (i=1…n). По входам 13i (i=1…n) поступают тактирующие сигналы опорного генератора на первые входы элементов И 11i, И 12i и И 1i. На второй вход элемента И 1i поступает сигнал с выхода счетчика 2i, который в процессе работы устройства после заполнения выдает сигнал сброса на второй вход элемента И 1i. Кроме того сигнал сброса с выхода счетчика 2i поступает на вход элемента НЕ 3i, с выхода которого сигнал через повторители 4ij (i=1…n, j=1…n) поступает на соответствующие входы всех мажоритарных элементов 5i и на вход повторителя 4ij.

Тактирующие сигналы опорного генератора по входам 131 - 13n, если счетчик 2i (i=1…n) не находится в нулевом состоянии, через элемент И 1i поступает на вход этого счетчика 2i до тех пор пока счетчик 2i (i=1…n) не переполнится (перейдет в нулевое состояние) и не заблокирует поступление тактовой частоты через элемент И 1i на свой вход. Сигнал переполнения с выхода счетчика 2i также поступает на вход инвертора 3i, с выхода которого сигнал предается всем соседним процессорам комплекса, а также через повторители 4ij (i=1…n, j=1…n) подается на вход мажоритарного элемента 5i.

С выхода 7i мажоритарного элемента 5i сигнал поступает на вход элемента НЕ 9i, второй вход элемента И11i и на вход элемента задержки 10i который задерживает сигнал на время надежного срабатывания элемента И 1i и счетчика 2i. С выхода элемента НЕ 9i сигнал поступает на третий вход элемента И 12i и при наличии единичного сигнала на втором входе элемента И 12i обеспечивает работу счетчика 6i в режиме на вычитание. Наличие единичного сигнала на выходе 8i элемента 5i через третий вход элемента И 11i обеспечивает работу счетчика 6i (i=1…n) в режиме на увеличение числа поступивших импульсов.

Кроме того, сигнал с выхода 7i мажоритарного элемента 5i используется как опорный для одного из таймеров ЭП или как сигнал прерываний таймера в качестве опорного сигнала для формирования периода возмущения своего ЭП.

На выходе 8i мажоритарного элемента 5i появится сигнал контроля работы элемента 5i, который далее поступает на входы элементов И 11i и И 12i (третий и второй соответственно) и запускает инкремент или декремент счетчика 6;, используемого для накопления времени перекоса относительно кода временной установки с выхода 14i, предварительно записанного в счетчик 6i из ЭП. По сигналу 7i с выхода элемента 5i, задержанному элементом 10i, содержимое счетчика 6i записывается в счетчик 2i, тем самым деблокируя его работу.

Временные диаграммы формирования сигнала на выходе 8i представлены на фиг. 2, где показан процесс устранения ложных срабатываний цепей контроля мажоритарных элементов и получение синхронных сигналов на выходах мажоритарных элементов различных ЭП. Так при наличии сигнала КМЭ1 71 и отсутствии сигнала МЭ (81) будет выполнено вычитание из содержимого счетчика 61, что в следующем цикле счета приведет к увеличению времени заполнения счетчика 21 до его переполнения, то есть до принятия им нулевого значения. Это позволяет скорректировать временную диаграмму в части сдвига фронта сигнала 31 вправо и уменьшении времени длительности сигнала КМЭ1. В случае с сигналами 32 и КМЭ2 будет происходить увеличение значения счетчика 62, что позволит в следующем цикле счета сдвинуть передний фронт сигнала 32 влево и уменьшить время длительности сигнала КМЭ2.

Таким образом, длительности сигналов КМЭ1 - КМЭ5 будут стремиться к нулевому значению, а значит времена перекосов сигналов КМЭ1 - КМЭ5 будут стремиться к нулевому значению, а значит времена перекосов сигналов на выходах 31 - 35 будут компенсированы.

Источники информации

1. SU №2785218, 2022.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ мажоритирования сигналов "2 из 3" | 2022 |

|

RU2789213C1 |

| Способ адаптивного мажоритирования элементов "n и более из (2n-1)" | 2022 |

|

RU2785218C1 |

| Адаптивный мажоритарный блок элементов "n и более из (2n-1)" | 2023 |

|

RU2818031C1 |

| Трехканальное резервированное запоминающее устройство | 1984 |

|

SU1215133A1 |

| Устройство для обмена информацией | 1986 |

|

SU1322299A1 |

| Устройство синхронизации работы граней в мажоритированных системах | 2018 |

|

RU2684198C1 |

| СПОСОБ ФОРМИРОВАНИЯ ОТКАЗОУСТОЙЧИВОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ И ОТКАЗОУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2010 |

|

RU2439674C1 |

| Устройство для мажоритарного резервирования | 1983 |

|

SU1140278A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С ВНЕКРИСТАЛЬНЫМ МАЖОРИТИРОВАНИЕМ И ВНУТРИКРИСТАЛЬНЫМ ДУБЛИРОВАНИЕМ | 2016 |

|

RU2672135C1 |

| РЕЗЕРВИРОВАННАЯ ЧЕТЫРЁХКАНАЛЬНАЯ ЦИФРОВАЯ УПРАВЛЯЮЩАЯ СИСТЕМА | 2017 |

|

RU2665252C1 |

Изобретение относится к области вычислительной техники. Технический результат заключается в обеспечении непрерывного контроля работоспособности средств вычислительной техники, функционирующих в условиях непрерывной динамики и постоянных изменений параметров внешних условий. Технический результат достигается за счет способа синхронизации работы элементарных процессоров мажоритарно-резервированных вычислительных комплексов, заключающегося в том, что в системе формируют отказоустойчивый вычислительный комплекс, содержащий группу элементарных центральных процессоров, выходная информация с выходов которых мажоритируется способом «n и более из (2n-1)», при этом мажоритирование входных сигналов осуществляют путем формирования тактирующих сигналов, ведут подсчет поступивших входных сигналов из каналов вычислительного комплекса и при достижении числа поступивших сигналов n > ((2n-1)/2) выдают выходной мажоритированный сигнал с выхода мажоритарного органа. 2 ил.

Способ синхронизации работы элементарных процессоров мажоритарно-резервированных вычислительных комплексов, заключающийся в том, что в системе формируют отказоустойчивый вычислительный комплекс, содержащий группу элементарных центральных процессоров, выходная информация с выходов которых мажоритируется способом «n и более из (2n-1)», отличающийся тем, что мажоритирование входных сигналов осуществляют путем формирования тактирующих сигналов, ведут подсчет поступивших входных сигналов из каналов вычислительного комплекса и при достижении числа поступивших сигналов n > ((2n-1)/2) выдают выходной мажоритированный сигнал с выхода мажоритарного органа.

| Способ мажоритирования сигналов "2 из 3" | 2022 |

|

RU2789213C1 |

| Мажоритарный блок элементов "два из трех" | 2019 |

|

RU2711726C1 |

| Адаптивный мажоритарный блок элементов "3 из 5" | 2021 |

|

RU2764839C1 |

| Способ адаптивного мажоритирования элементов "n и более из (2n-1)" | 2022 |

|

RU2785218C1 |

| Способ получения цианистых соединений | 1924 |

|

SU2018A1 |

Авторы

Даты

2025-02-20—Публикация

2024-05-22—Подача