Изобретение относится к области радиоэлектроники, а именно к схемам формирования сигналов произвольной, сложной формы, а также малой длительности методом цифроаналогового преобразования, и может быть использовано при проектировании высокоскоростных модуляторов/демодуляторов радиотехнических систем проводной и беспроводной цифровой передачи данных.

Обычно, в качестве устройства, формирующего сигнал для модуляции высокочастотной несущей, в беспроводных системах цифровой передачи данных применяют цифроаналоговые преобразователи и устройства прямого цифрового синтеза сигналов, которые могут формировать высокочастотное модулированное колебание сразу, без дополнительной операции модуляции. Все перечисленные устройства в дальнейшем обобщенно будем называть ЦАП - цифроаналоговый преобразователь.

Бурное развитие электроники и повсеместный переход от аналоговых систем на цифровые системы требует увеличения скорости работы последних. Например, растущие объемы передаваемой информации требуют от приемо-передающих систем как увеличения скорости обработки цифроаналогового преобразования, так и обратного аналого-цифрового преобразования. Если рассматривать радиосистему на передающей стороне, то чем выше скорость потока информации, тем более высокие требования по скорости работы предъявляются к ЦАП.

Из уровня техники известно несколько способов повышения скорости (или уменьшения времени) цифроаналогового преобразования.

Устройство, описанное в изобретении RU 2420867 "Способ цифроаналогового преобразования", достигает технического результата, заключающегося в уменьшения времени преобразования, относится к схемам ЦАП, реализованным на базе широтно-импульсной модуляции. Заявленный результат получается за счет введения в схему дополнительного амплитудного модулятора широтно-импульсного сигнала прямоугольным сигналом нормированной амплитуды и специального метода управления таким преобразованием.

Другое известное улучшение направлено на увеличение скорости цифроаналогового преобразования, как описано в патенте US 6130634 "Резистивный строковый ЦАП с улучшенной скоростью", относится к ЦАП с суммированием напряжений. Заявленный результат, указанный в названии изобретения, достигается за счет увеличения площади переключающего элемента, выполненного на основе полевого транзистора, одного лишь старшего разряда, что приводит к снижению сопротивления транзистора в открытом состоянии и как результат - увеличению скорости преобразования всего ЦАП. Реализованное устройство показало выигрыш в скорости преобразования почти в два раза, по сравнению с устройствами, не содержащими данное улучшение.

Все вышеперечисленные улучшения относятся к различным типам ЦАП и различным способам их реализации - на структурном уровне (первое изобретение) или на технологическом уровне (второе изобретение). Предлагаемое изобретение касается увеличения скорости преобразования ЦАП, состоящего из цифровой интегральной схемы, к выходу которой подключена одна из известных резистивных матриц (резистивная матрица постоянного импеданса, двоично-взвешивающая резистивная матрица, резистивный делитель Кельвина) или их комбинации и заключается в реализации специальной структуры ЦАП на цифровой интегральной схеме, а также в применении нового метода управления специальной структурой.

Прототипом данного изобретения является устройство, реализованное в виде микросхемы AD7524 и известное из литературы, например стр. 700 - Точчи Р.Дж., Уидмер Н.С. Цифровые системы. Теория и практика, 8-е издание: Пер. с англ. - М.: Издательский дом "Вильяме", 2004. - 1024 с.: ил. Схемы, подобные AD7524, реализованные на дискретных компонентах, широко используются в инженерной практике. Работа прототипа будет детально рассмотрена далее, что необходимо для понимания различий с настоящим изобретением. Прототип настоящего изобретения будем называть также "обычный ЦАП", а словосочетание "обычный метод цифроаналогового преобразования" следует соответственно относить к методу или способу его функционирования.

Любой ЦАП можно охарактеризовать множеством характеристик, однако данное изобретение направлено на улучшение представления формы аналогового сигнала на выходе ЦАП за счет увеличения скорости цифроаналогового преобразования (без увеличения тактовой частоты преобразования), что также приводит к снижению стоимости и мощности, потребляемой преобразователем.

Высокоскоростные современные ЦАП (единицы - десятки миллионов отсчетов в секунду) имеют разрешающую способность 12-16 бит, что в большинстве случаев достаточно для выполнения микросхемой ЦАП своей функции, но также имеют большую потребляемую мощность и цену (начиная от двухсот милливатт и пятисот рублей, на момент создания изобретения), что снижает область применения подобных микросхем. Кроме того, чем выше скорость преобразования, тем микросхемы ЦАП менее доступны в свободной продаже из-за их уникальности. Данные утверждения справедливы как для специализированных микросхем ЦАП, так и для устройств, реализующих функцию цифроаналогового преобразования, например, программируемых логических интегральных схем (ПЛИС) с матрицей постоянного импеданса (R-2R матрицей) на выходе.

Технический результат, достигаемый при реализации изобретения, заключается в увеличении скорости преобразования цифроаналогового преобразователя. Другой технический результат состоит в создании цифроаналогового преобразователя, более точно представляющего форму аналогового сигнала. Указанные результаты касаются реализации ЦАП на основе обычных (широко распространенных, дешевых и потребляющих небольшую мощность) микросхем ПЛИС с одной из известных резистивных матриц или их комбинаций на выходе ПЛИС.

Заявленный технический результат достигается за счет создания специальной цифровой структуры, реализованной на основе ПЛИС, являющейся цифровой частью ЦАП, и применения нового метода управления ею.

Сущность изобретения заключается в методе реализации такого ЦАП, среднеквадратическое отклонение формы сигнала, на выходе которого в несколько раз меньше по сравнению со среднеквадратическим отклонением формы сигнала на выходе обычного ЦАП, реализованного и управляемого согласно общеизвестным принципам. Имеется ввиду среднеквадратическое отклонение формы сигнала, посчитанное по известным выражениям, например стр. 178 - Боккер П. Передача данных (Техника в системах телеобработки данных). Том I. Основы: Пер. с нем./Под ред. Д.Д. Кловского. - М.: Связь, 1980. - 264 с., ил., полученного на выходе цифроаналогового преобразователя, от формы идеального сигнала, который нужно получить. В данном конкретном случае "метод реализации" подразумевает реализацию законченного устройства ЦАП, функционирующего таким образом, чтобы осуществлять заявленные функции, и включает в себя совокупность аппаратной реализации (структура ЦАП) и способа управления ей.

Обычный ЦАП, реализованный на основе ПЛИС и одной из известных резистивных матриц или их комбинаций на выходе, формирует сигнал за один период тактовой частоты. Однако благодаря возможности реализации задержек сигналов на внутренних элементах ПЛИС имеется возможность формирования сигнала, на выходе цифровой части предлагаемого ЦАП, в моменты времени, не кратные периоду тактовой частоты. Данные моменты времени могут быть как больше, так и меньше периода тактовой частоты. Если моменты времени меньше периода тактовой частоты, то увеличивается скорость преобразования и точность представления формы аналогового сигнала на выходе ЦАП. Если моменты времени больше периода тактовой частоты, то увеличивается точность представления формы аналогового сигнала на выходе ЦАП.

В дальнейшем, настоящее изобретение будет рассматривать ЦАП, сигнал на выходе цифровой части которого формируется в моменты времени, меньшие, кратные и большие, чем период тактовой частоты, однако все рассуждения соответствующим образом могут быть распространены и на ЦАП, сигнал на выходе цифровой части которого формируется в моменты времени, меньшие и кратные, а также кратные и большие, чем период тактовой частоты. Таким образом, в обычном ЦАП, момент изменения сигнала на выходе его цифровой части определяется только периодом тактовой частоты, а в предлагаемом ЦАП этот момент времени определяется как периодом тактовой частоты, так и задержкой относительно предыдущего момента изменения сигнала на выходе цифровой части ЦАП.

Для лучшего понимания предложенного изобретения далее приводится его подробное описание, а также описание прототипа с соответствующими чертежами.

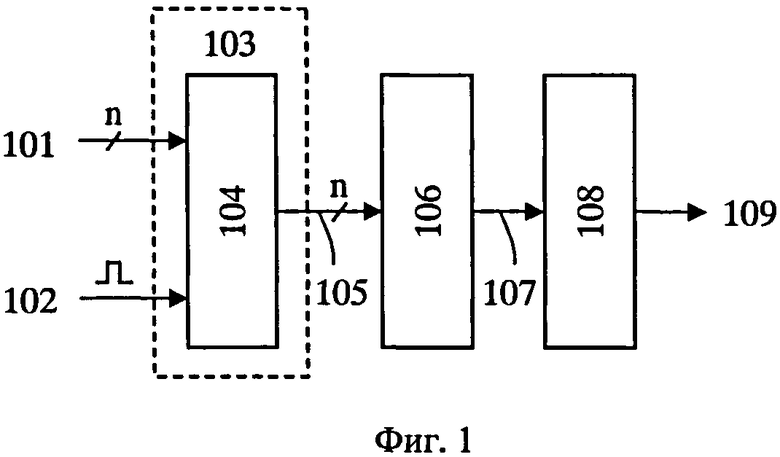

Фиг. 1. Структура обычного цифроаналогового преобразователя

Элементы

101 - входные цифровые данные (n - разрядов);

102 - сигнал тактовой частоты;

103 - программируемая логическая интегральная схема;

104 - преобразователь входных цифровых данных;

105 - сигнал после преобразователя входных данных (n - разрядов);

106 - резистивная матрица постоянного импеданса;

107 - сигнал после резистивной матрицы;

108 - аналоговый фильтр;

109 - аналоговый сигнал, действующий на выходе ЦАП.

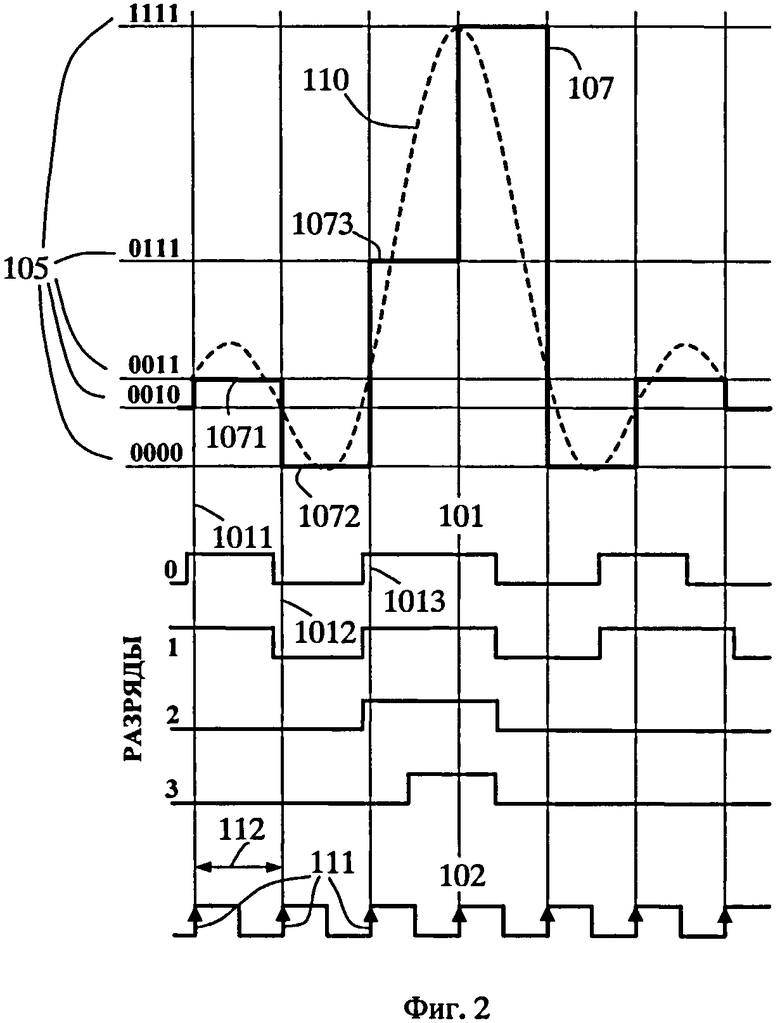

Фиг. 2. Временная диаграмма работы обычного цифроаналогового преобразователя

Элементы

101 - входные цифровые данные (в данном примере сигнал имеет четыре параллельных разряда 0, 1, 2, 3);

1011 - первый момент времени, в который происходит смена сигналов на выходе преобразователя входных данных;

1012 - второй момент времени, в который происходит смена сигналов на выходе преобразователя входных данных;

1013 - третий момент времени, в который происходит смена сигналов на выходе преобразователя входных данных;

102 - сигнал тактовой частоты (по фронту сигнала происходит смена сигналов на выходе преобразователя входных данных);

105 - сигнал после преобразователя входных данных (в данном примере сигнал имеет четыре параллельных разряда 0, 1, 2, 3);

107 - сигнал после резистивной матрицы обычного ЦАП;

1071 - уровень выходного сигнала после первого момента времени 1011, в который произошла смена сигналов на выходе преобразователя входных данных;

1072 - уровень выходного сигнала после второго момента времени 1012, в который произошла смена сигналов на выходе преобразователя входных данных;

1073 - уровень выходного сигнала после третьего момента времени 1013, в который произошла смена сигналов на выходе преобразователя входных данных;

110 - аналоговый (идеальный) сигнал, который нужно получить на выходе цифро-аналогового преобразователя (в данном примере описывается функцией sin(х)/х);

111 - фронт сигнала тактовой частоты (тактового сигнала);

112 - период сигнала тактовой частоты (тактового сигнала).

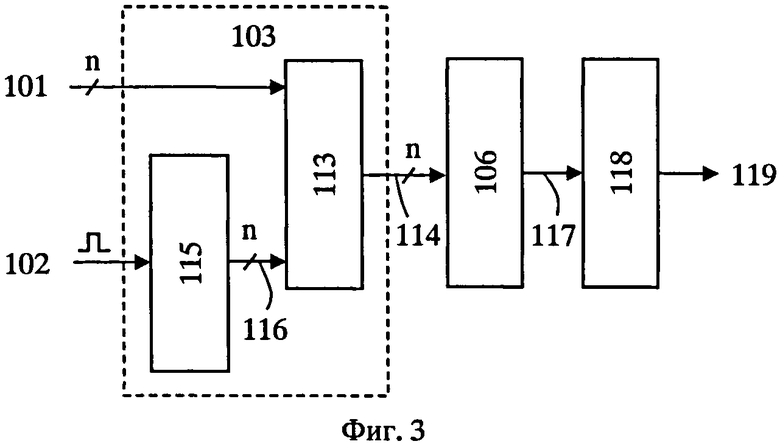

Фиг. 3. Структура предлагаемого цифроаналогового преобразователя

Элементы

101 - входные цифровые данные (n - разрядов);

102 - сигнал тактовой частоты;

103 - программируемая логическая интегральная схема;

105 - резистивная матрица постоянного импеданса;

113 - преобразователь входных цифровых данных предлагаемого ЦАП;

114 - сигнал после преобразователя входных данных предлагаемого ЦАП (n - разрядов);

115 - преобразователь тактовой частоты;

116 - многоразрядный тактовый сигнал (n - разрядов);

117 - сигнал после резистивной матрицы предлагаемого ЦАП;

118 - аналоговый фильтр предлагаемого ЦАП;

119 - аналоговый сигнал, действующий на выходе предлагаемого ЦАП.

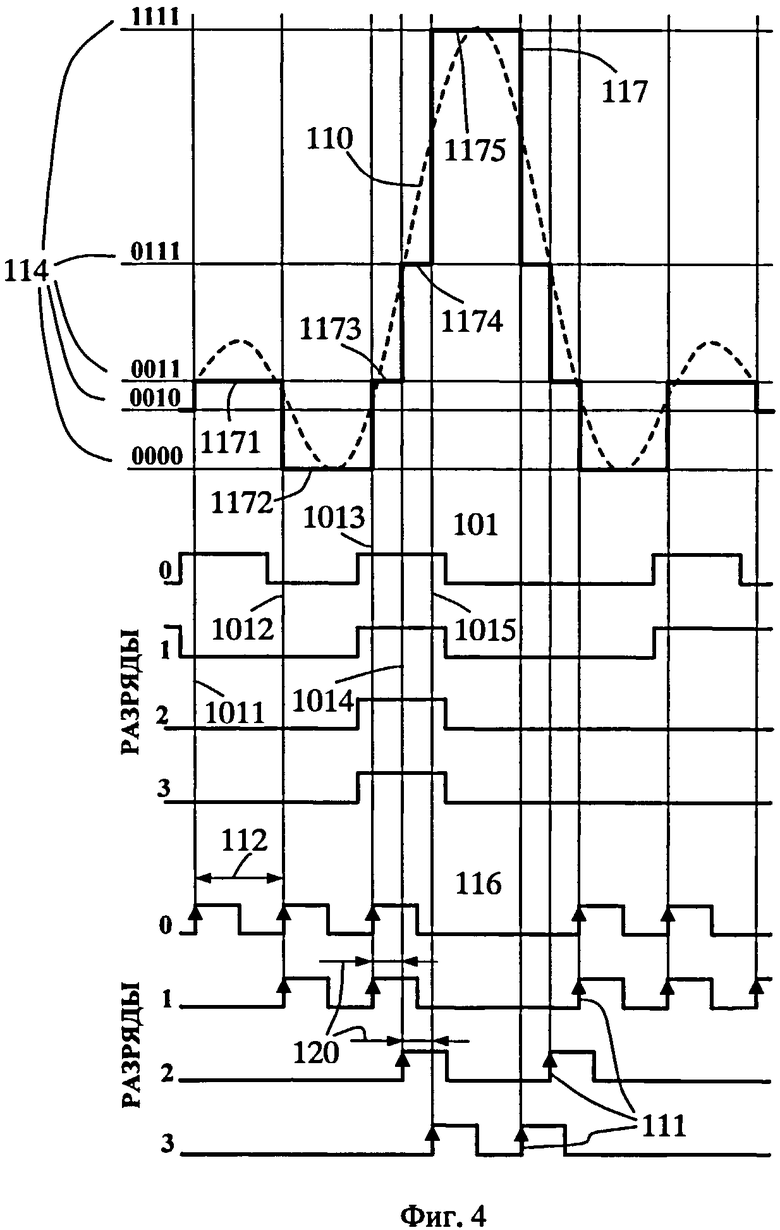

Фиг. 4. Временная диаграмма работы предлагаемого цифроаналогового преобразователя

Элементы

101 - входные цифровые данные (в данном примере сигнал имеет четыре параллельных разряда 0, 1, 2, 3);

1011 - первый момент времени, в который происходит смена сигналов на выходе преобразователя входных данных;

1012 - второй момент времени, в который происходит смена сигналов на выходе преобразователя входных данных;

1013 - третий момент времени, в который происходит смена сигналов на выходе преобразователя входных данных;

1014 - четвертый момент времени, в который происходит смена сигналов на выходе преобразователя входных данных;

1015 - пятый момент времени, в который происходит смена сигналов на выходе преобразователя входных данных;

110 - аналоговый (идеальный) сигнал, который нужно получить на выходе цифроаналогового преобразователя (в данном примере описывается функцией sin(х)/х);

111 - фронт сигнала тактовой частоты (тактового сигнала);

112 - период сигнала тактовой частоты (тактового сигнала);

114 - сигнал после преобразователя входных данных предлагаемого ЦАП (в данном примере сигнал имеет четыре параллельных разряда 0, 1, 2, 3);

116 - многоразрядный тактовый сигнал (данный пример иллюстрирует четыре параллельных тактовых сигнала 0, 1, 2, 3. По фронту тактового сигнала в каждом разряде происходит смена сигнала в соответствующем разряде на выходе преобразователя входных данных);

117 - сигнал после резистивной матрицы предлагаемого ЦАП;

1171 - уровень выходного цифрового сигнала после первого момента времени 1011, в который произошла смена сигналов на выходе преобразователя входных данных;

1172 - уровень выходного цифрового сигнала после второго момента времени 1012, в который произошла смена сигналов на выходе преобразователя входных данных;

1173 - уровень выходного цифрового сигнала после третьего момента времени 1013, в который произошла смена сигналов на выходе преобразователя входных данных;

1174 - уровень выходного цифрового сигнала после четвертого момента времени 1014, в который произошла смена сигналов на выходе преобразователя входных данных;

1175 - уровень выходного цифрового сигнала после пятого момента времени 1015, в который произошла смена сигналов на выходе преобразователя входных данных;

120 - задержка между предыдущим и последующим тактовыми сигналами в разных разрядах, не кратная периоду тактовой частоты (для данного примера величина 120 в три раза меньше величины периода сигнала тактовой частоты 102).

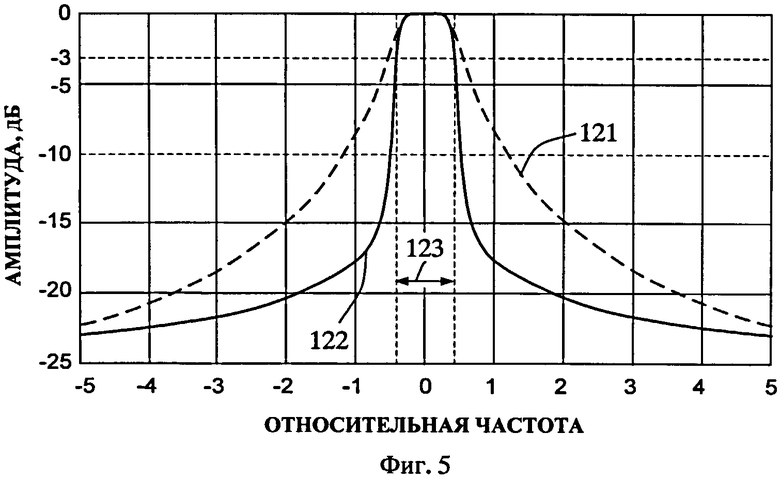

Фиг. 5. Огибающая модуля спектральной плотности энергии сигналов на выходе обычного и предлагаемого цифроаналоговых преобразователей

Элементы

121 - огибающая модуля спектральной плотности энергии сигнала на выходе обычного цифроаналогового преобразователя (после фильтра 108);

122 - огибающая модуля спектральной плотности энергии сигнала на выходе предлагаемого цифроаналогового преобразователя (после фильтра 118);

123 - полоса частот сигнала 122 по уровню минус 3 дБ.

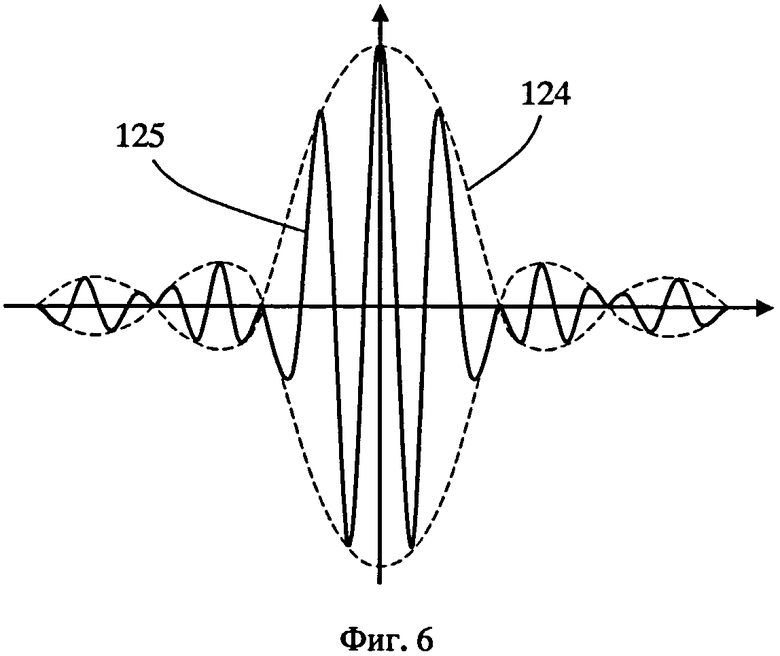

Фиг. 6. Сигнал на выходе предлагаемого цифроаналогового преобразователя, модулирующий высокочастотное колебание

Элементы

124 - модуль временной формы сигнала на выходе предлагаемого цифроаналогового преобразователя (после фильтра 118);

125 - высокочастотное колебание, модулированное сигналом 119.

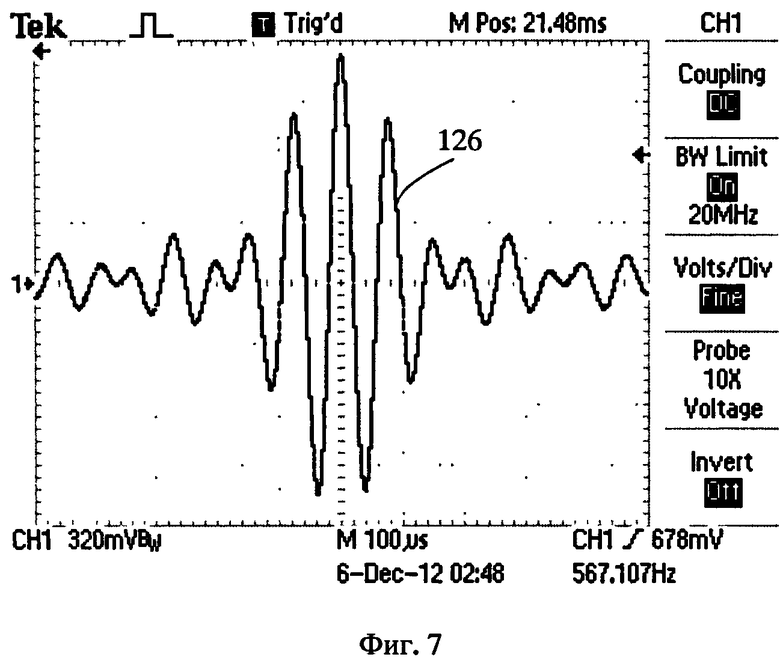

Фиг. 7. Практическая реализация сигнала согласно предлагаемому методу цифроаналогового преобразования. Сигнал модулирует высокочастотное колебание

Элементы

126 - практическая реализация сигнала согласно предложенному методу, который модулирует высокочастотное колебание.

При описании принципа работы изобретения будем использовать выражения единица и ноль, что соответствует общепринятым в цифровой технике эквивалентным выражениям - цифровая единица и цифровой ноль и характеризует два логических уровня напряжения, действующих в схеме. Например, для комплементарной логики, нулю соответствует напряжение, близкое к нулю вольт, единице - напряжение, близкое к напряжению питания цифровой схемы.

Структуру обычного ЦАП иллюстрирует фиг. 1. Блок схема состоит из ПЛИС 103, на которой реализована цифровая схема многоразрядного параллельного преобразователя входных цифровых данных 104 (далее - преобразователь), являющегося цифровой частью ЦАП, и резистивной матрицы 106 с аналоговым фильтром 108, являющимися аналоговой частью ЦАП.

Принцип работы такого ЦАП заключается в следующем. Входные цифровые данные 101 в параллельной или последовательной форме поступают на преобразователь 104. Если входные цифровые данные поступают в последовательной форме, то первоначально преобразователь 104 преобразует данные в параллельную форму. По сигналу тактовой частоты 102 (например, по его фронту 111) входные цифровые данные 101 в параллельной форме переписываются преобразователем 104 на его выход, затем происходит смена входных цифровых данных, и по фронту следующего сигнала тактовой частоты, сигналы на выходе преобразователя 104 обновляются. Входные цифровые данные 101 могут следовать со скважностью, равной единице, и с периодом, большим или равным периоду 112 сигнала тактовой частоты 102, скважность которого равна двум. Выход преобразователя 104 является выходом цифровой части ЦАП. С выхода цифровой части ЦАП, сигнал поступает на резистивную матрицу (например, R-2R матрицу постоянного импеданса), число входов которой равно числу выходов преобразователя 104. С выхода матрицы 106, сигнал поступает на аналоговый фильтр 108, выход которого является выходом ЦАП.

Временная диаграмма работы обычного ЦАП проиллюстрирована на фиг. 2. В первый момент времени 1011 входные цифровые данные 101 имеют значение единицы в нулевом и первом разряде и нуля во втором и третьем разряде (данные 101 действуют на входе преобразователя 104 в параллельной форме). При поступлении фронта сигнала тактовой частоты 102 в момент времени 1011, цифровые данные переписываются на выход преобразователя 104. Сигнал 105 на выходе преобразователя входных данных аналогично имеет значение единицы в нулевом и первом разрядах и нуля во втором и третьем разрядах (0011). На выходе резистивной матрицы 106 амплитуда сигнала 107 имеет значение 1071. К моменту времени 1012 происходит смена входных цифровых данных - значение ноль, действует с нулевого по третий разряд. При поступлении следующего фронта сигнала тактовой частоты 102 в момент времени 1012, цифровые данные переписываются на выход преобразователя 104. Сигнал 105 на выходе преобразователя 104 аналогично имеет значение нуля во всех разрядах (0000). На выходе резистивной матрицы 106 амплитуда сигнала 107 имеет значение 1072. Далее, к моменту времени 1013, происходит очередная смена входных цифровых данных - значение единицы действует в нулевом, первом и втором разрядах и нуля в третьем разряде. При поступлении третьего фронта сигнала тактовой частоты 102 в момент времени 1013, цифровые данные переписываются на выход преобразователя 104. Сигнал 105 на выходе преобразователя 104 имеет значение единицы в нулевом, первом и втором разрядах и нуля в третьем разряде (0111). На выходе резистивной матрицы 106 амплитуда сигнала 107 имеет значение 1073, и так далее.

Отметим, что смена сигналов на выходе преобразователя 104 происходит через время 112, кратное периоду сигнала тактовой частоты 102. При этом сигналы 105 на выходе преобразователя 104 для каждого последующего фронта 111 сигнала тактовой частоты 102 могут иметь любую комбинацию (для четырех разрядов - любую из шестнадцати комбинаций). Например, комбинация 0100 может быть сменять комбинацию 0011 или комбинация 1001 может сменять комбинацию 0110, то есть любая комбинация может сменять любую комбинацию.

Структуру предлагаемого ЦАП иллюстрирует фиг. 3. Структура состоит из ПЛИС 103, на которой реализована цифровая схема многоразрядного параллельного преобразователя входных цифровых данных 113 (далее - преобразователь входных данных) и преобразователя тактовой частоты 115, входящих в цифровую часть ЦАП, и резистивной матрицы 106 с аналоговым фильтром 118, являющимися аналоговой частью ЦАП. При этом преобразователь тактовой частоты 115 имеет число выходов, равное числу разрядов преобразователя входных данных 113, и каждый из этих выходов соединен со своим разрядом преобразователя входных данных 113 и управляет его работой. Выход преобразователя входных данных 113 является выходом цифровой части ЦАП. С выхода цифровой части ЦАП, сигнал поступает на резистивную матрицу (например, R-2R матрицу постоянного импеданса), число входов которой равно числу выходов преобразователя входных данных 113. С выхода матрицы 106, сигнал поступает на аналоговый фильтр 118, выход которого является выходом предлагаемого ЦАП.

Принцип работы предлагаемого ЦАП заключается в следующем. Входные цифровые данные 101 в параллельной или последовательной форме поступают на преобразователь входных данных 113. Если входные цифровые данные поступают в последовательной форме, то первоначально преобразователь входных данных преобразует данные в параллельную форму. По сигналу тактовой частоты 102 (например, по его фронту), преобразователь тактовой частоты формирует на своем выходе многоразрядный тактовый сигнал 116, причем число разрядов тактового сигнала 116 соответствует числу разрядов сигнала 114, формируемого на выходе преобразователя входных данных 113. Сигнал 116 на каждом разряде преобразователя тактовой частоты 115 является тактовым сигналом для соответствующего разряда преобразователя входных данных 113 и разрешает запись сигнала с соответствующего входа преобразователя входных данных 113 на его выход. Например, по фронту тактового сигнала с нулевого разряда преобразователя тактовой частоты 115 разрешается запись сигнала со входа нулевого разряда преобразователя входных данных 113 на выход его нулевого разряда. Выход преобразователя входных данных 113 является выходом цифровой части ЦАП. Многоразрядный тактовый сигнал 116 формируется таким образом и по таким правилам, чтобы при смене выходного цифрового сигнала 114 аналоговый сигнал 119 как можно точнее повторял форму требуемого сигнала 110.

Преобразователь тактовой частоты может быть реализован с помощью устройства, приведенного на стр. 145 (рис. 8.73) источника Хоровиц П., Хилл. У. Искусство схемотехники: В 3-х томах: Т. 2 Пер. с англ. - 4-е изд., перераб. и доп. - М.: Мир, 1993. - 371 с., ил., к выходам третьего и четвертого разрядов которого подключены буферные логические элементы (условное графическое изображение которых соответствует элементу К155ЛН4), обеспечивающие задержку прохождения сигнала на величину 120. Данный источник приведен как пример, показывающий возможность реализации преобразователя тактовой частоты. В изобретении преобразователь тактовой частоты был реализован на цифровых элементах, входящих в состав ПЛИС. Схема, показывающая пример реализации преобразователя тактовой частоты, в изобретении не приведена, поскольку временная диаграмма, приведенная на фиг. 4, дает исчерпывающую информацию о работе преобразователя тактовой частоты и подразумевает множество схемных реализаций, зависящих от квалификации инженера-разработчика.

Правила формирования многоразрядного тактового сигнала 116 детально характеризуют сущность изобретения и будут рассмотрены далее.

Отметим, что входные цифровые данные могут следовать со скважностью, равной единице, и с периодом, большим или равным минимальному периоду 112 многоразрядного тактового сигнала 116, скважность которого равна двум.

Временная диаграмма работы предлагаемого ЦАП проиллюстрирована на фиг. 4. В первый момент времени 1011 входные цифровые данные 101 имеют значение единицы в нулевом разряде и нуля в первом, втором и третьем разрядах (данные 101 действуют на входе преобразователя входных данных 113 в параллельной форме). Сигнал тактовой частоты 102, после преобразователя имеет временную диаграмму 116. Многоразрядный тактовый сигнал 116 (его фронт) на каждом из разрядов разрешает запись сигнала соответствующего разряда преобразователя входных данных 113 с его входа на его выход. Таким образом, в момент времени 1011 по фронту нулевого разряда многоразрядного тактового сигнала 116, значение единицы во входных цифровых данных 101, действующее в нулевом разряде, переписывается на выход преобразователя входных данных 113 в нулевой разряд. Сигнал 114 на выходе преобразователя входных данных 113 имеет значение единицы в нулевом и первом разрядах и нуля во втором и третьем разрядах (0011). Единица в первом разряде сохранилась с предыдущего момента времени. На выходе резистивной матрицы 106 амплитуда сигнала 117 имеет значение 1171. К моменту времени 1012 происходит смена входных цифровых данных - значение ноль, действует с нулевого по третий разряд. В этот момент времени фронты многоразрядного тактового сигнала 116 действуют в нулевом и первом разрядах, записывая, таким образом, значение нуля на выход преобразователя входных данных 113 в нулевой и первый разряды. Сигнал 114 на выходе преобразователя входных данных 113 имеет значение нуля во всех разрядах (0000). Отметим, что разница между моментами времени 1011 и 1012 меньше, чем период тактовой частоты 112. В данном примере разница 120 в три раза меньше, чем период тактовой частоты 112. На выходе резистивной матрицы 106 амплитуда сигнала 117 имеет значение 1172. Далее, к моменту времени 1013 происходит очередная смена входных цифровых данных - значение единицы действует в с нулевого по третий разряды. В этот момент времени фронты многоразрядного тактового сигнала 116 аналогично действуют в нулевом и первом разрядах, записывая, таким образом, значение единицы на выходе преобразователя входных данных 113 в нулевой и первый разряды. Сигнал 114 на выходе преобразователя входных данных 113 имеет значение единицы в нулевом и первом разрядах и нуля во втором и третьем разрядах (0011). На выходе резистивной матрицы 106 амплитуда сигнала 117 имеет значение 1173. В момент времени 1014 значения входных цифровых данных сохраняются, при этом фронт многоразрядного тактового сигнала 116 действует только во втором разряде, записывая, таким образом, значение единицы на выходе преобразователя входных данных 113 во второй разряд. Сигнал 114 на выходе преобразователя входных данных 113 имеет значение единицы в нулевом, первом и втором разрядах и нуля в третьем разряде (0111). На выходе резистивной матрицы 106 амплитуда сигнала 117 имеет значение 1174. Далее, при сохранении значения входных цифровых данных фронт многоразрядного тактового сигнала 116, действуя только в третьем разряде, записывает значение единицы на выходе преобразователя входных данных 113 в третий разряд. Сигнал 114 на выходе преобразователя входных данных имеет значение единицы во всех разрядах (1111). На выходе резистивной матрицы 106 амплитуда сигнала 117 имеет максимальное значение 1175. Далее процесс происходит согласно фиг. 4.

Анализируя существующий и предлагаемый методы цифро-аналогового преобразования можно отметить, что сигнал тактовой частоты 102 в обоих методах, равно как и многоразрядный тактовый сигнал 116 во всех разрядах, имеют одинаковый период повторения 112 и этот период минимален по сравнению с периодами остальных сигналов, действующих на входах ПЛИС. Это означает, что ПЛИС, реализующая тот или иной метод цифроаналогового преобразования, работает с одинаковой тактовой частотой. Если частота тактового сигнала является максимальной частотой, которая может действовать на входе ПЛИС согласно ее спецификации, то предлагаемый метод реализации ЦАП позволяет увеличить скорость преобразования и более точно сформировать форму аналогового сигнала. В рассмотренном примере, сигнал 119, полученный с использованием более высокой скорости преобразования в некоторые моменты времени - это сигнал, более точно представляющий форму сигнала 110, по сравнению с сигналом 109, что достигается за счет распараллеливания сигнала тактовой частоты 102 в сигнал 116. Для формирования сигнала, аналогичного сигналу 119, с помощью обычного цифроаналогового преобразователя, выбранного в качестве прототипа - необходимо увеличивать частоту тактового сигнала 102 и, как следствие, использовать более высокочастотную и поэтому дорогостоящую ПЛИС. Для данного конкретного примера, чтобы получить сигнал 119 с помощью обычного цифроаналогового преобразования - необходимо использовать микросхему ПЛИС, которая допускает на своих входах частоту, в три раза большую, по сравнению с ПЛИС, которая реализует сигнал 119 с помощью предлагаемого метода цифроаналогового преобразования.

На фиг. 5 показано, что огибающая модуля спектральной плотности энергии сигнала 119 на выходе аналогового фильтра 118 уже, чем огибающая модуля спектральной плотности энергии сигнала 109 на выходе аналогового фильтра 108, что достигается за счет более точного представления формы требуемого сигнала 110.

Если сравнивать спектральные плотности энергий 121 и 122 по уровню минус 3 дБ (фиг. 5), то разница в их ширине полосы частот является незначительной, однако по уровню минус 10 дБ существует двукратная разница. Таким образом, очевидно, что сигнал со спектром 122 имеет меньшее внеполосное излучение по сравнению с сигналом, имеющим спектр 121. Если сравнивать полосы спектров 121 и 122 далее, то разница в их ширине начинает уменьшаться. Однако фиг. 5 иллюстрирует спектр сигнала 119 на выходе четырехразрядного ЦАП. При использовании предлагаемого метода управления цифроаналоговым преобразователем с большим числом разрядов и увеличении длительности преобразуемого сигнала 110 (не масштабирования его во времени, а преобразование бесконечного сигнала 110 на большем интервале времени) - спектр 122 будет стремится к прямоугольной П-образной форме в пределах полосы частот 123 и к нулю вне полосы частот.

Огибающая 124 в положительной области оси ординат (фиг. 6) представляет собой модуль сигнала 119. Использование сигнала 119 в качестве модулирующего высокочастотное колебание 125 (фиг. 6) также дает меньший уровень внеполосного излучения в спектре модулированного сигнала. В результате чего снижаются требования к крутизне фронтов полосовых фильтров передатчика для подавления внеполосного излучения, снижается уровень помехи по соседнему каналу, появляется возможность уменьшения величины защитного интервала между соседними радиочастотными каналами, увеличения числа каналов и, таким образом - более эффективного использования спектра радиочастот.

На фиг. 7 показан результат эксперимента по практической реализации сигнала 110, согласно предложенному методу, которым затем было промодулировано высокочастотное колебание 124. Здесь, как и во всем описании изобретения, сигнал 110 представлен функцией sin(х)/х.

При реализации сигнала 110, на выходе предложенного ЦАП, был получен сигнал 119 (фиг. 7), частота которого составляет сотни герц, при этом модулируемый сигнал 126 имеет частоту порядка десятка килогерц. Однако область применения предлагаемого метода - реализация сигналов с полосой частот в несколько сотен мегагерц для использования в сверхширокополосных системах радиосвязи, в качестве сигналов, модулирующих колебание с частотами в единицы-десятки гигагерц. Данный эксперимент был проведен на низких частотах с целью показать правильность предлагаемого метода цифроаналогового преобразования.

Анализируя фиг. 2 и фиг. 4, можно заключить, что предлагаемый метод преобразования цифрового сигнала в аналоговый имеет некоторые отличия от обычного метода преобразования. Все отличия касаются формирования многоразрядного тактового сигнала 116, перечислим их.

1. В обычном методе цифроаналогового преобразования один и тот же сигнал тактовой частоты служит для одновременной смены сигналов на выходе всех разрядов цифровой части ЦАП.

В предлагаемом методе цифроаналогового преобразования по сигналу тактовой частоты формируется многоразрядный тактовый сигнал (число разрядов или число тактовых сигналов равно числу разрядов цифровой части ЦАП), каждый из тактовых сигналов поступает на свой разряд цифровой части ЦАП и служит для смены сигнала на его выходе.

2. В обычном методе цифроаналогового преобразования один и тот же сигнал тактовой частоты с одинаковым периодом подается одновременно на все разряды цифровой части ЦАП.

В предлагаемом методе цифроаналогового преобразования формируется временная диаграмма работы многоразрядного тактового сигнала, для каждого разряда тактового сигнала - своя, при этом на каждый разряд цифровой части ЦАП тактовый сигнал может подаваться в разное время как кратное, так и не кратное периоду (больше, меньше периода) тактового сигнала. Минимальный период тактовых сигналов во всех разрядах многоразрядного тактового сигнала - одинаковый.

3. В обычном методе цифроаналогового преобразования сигнал тактовой частоты всегда воздействует на все разряды цифровой части ЦАП.

В предлагаемом методе цифроаналогового преобразования тактовый сигнал для каждого конкретного разряда цифровой части ЦАП формируется только в том случае, если необходимо изменение сигнала на выходе этого разряда. Предложенный метод работы цифроаналогового преобразования имеет также некоторые особенности, касающиеся условий смены сигнала на выходе цифровой части ЦАП, которым служит выход преобразователя входных данных 113, и на который соответственно воздействует сигнал 114. Все особенности проиллюстрированы на фиг. 4, перечислим их.

1. Изменение сигнала на выходе цифровой части ЦАП возможно, если должна произойти смена единицы на ноль в одном выходном разряде (нескольких выходных разрядах) или смена ноля на единицу в одном разряде (нескольких разрядах).

2. Если происходит смена единицы на ноль (ноля на единицу) в каком-либо разряде (разрядах) на выходе цифровой части ЦАП, то последующая смена ноля на единицу (единицы на ноль) в этом же разряде (разрядах) возможна лишь через время, равное или большее, чем период тактового сигнала этого разряда (разрядов).

3. Изменение сигнала на выходе цифровой части ЦАП невозможно, если должна произойти смена единицы на ноль в одном разряде (нескольких разрядах) при одновременной смене ноля на единицу в другом разряде (нескольких разрядах).

4. Изменение сигнала на выходе цифровой части ЦАП невозможно, если должна произойти смена ноля на единицу в одном разряде (нескольких разрядах) при одновременной смене единицы на ноль в другом разряде (нескольких разрядах).

Настоящее изобретение может быть использовано в схемах формирования сигналов произвольной, сложной формы, а также малой длительности методом цифроаналогового преобразования, в высокоскоростных модуляторах /демодуляторах радиотехнических систем проводной и беспроводной цифровой передачи данных, в особенности в сверхширокополосных системах радиосвязи, для формирования сигналов, модулирующих колебание с частотами в единицы-десятки гигагерц, а также в цифро-аналоговых преобразователях, где необходимо увеличить скорость преобразования и/или точность представления сигнала на выходе ЦАП, без увеличения максимальной тактовой частоты преобразования, при сохранении на том же уровне стоимости и мощности потребляемой преобразователем.

Изобретение касается улучшения потребительских свойств изделий, использующих высокоскоростное цифроаналоговое преобразование, в частности сверхширокополосных систем радио и проводной связи.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ РЕГУЛИРОВАНИЯ УРОВНЯ ГРОМКОСТИ | 2014 |

|

RU2562371C1 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2012 |

|

RU2485681C1 |

| Система цифрового управления вибрационными испытаниями | 1985 |

|

SU1265729A1 |

| УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1992 |

|

RU2042269C1 |

| Устройство для аналого-цифрового преобразования импульсных сигналов | 1987 |

|

SU1564725A1 |

| СПОСОБ ЭЛЕКТРОННОЙ ОБРАБОТКИ СИГНАЛОВ ФОТОПРИЕМНИКА ПРИ ФОРМИРОВАНИИ ИЗОБРАЖЕНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2009 |

|

RU2423016C1 |

| СПОСОБ ЦИФРОАНАЛОГОВОГО ПРЕОБРАЗОВАНИЯ | 2012 |

|

RU2497276C1 |

| Цифроаналоговый преобразователь | 1988 |

|

SU1547069A1 |

| МУЛЬТИПЛЕКСОР ПЕРЕДАЧИ ДАННЫХ | 2005 |

|

RU2295148C1 |

| УСТРОЙСТВО МОНИТОРИНГА ВЫСОКОВОЛЬТНЫХ ВВОДОВ И СИГНАЛИЗАЦИИ О СОСТОЯНИИ ИХ ИЗОЛЯЦИИ | 2006 |

|

RU2328009C1 |

Группа изобретений относится к области радиоэлектроники и может быть использовано при создании высокоскоростных модуляторов/демодуляторов радиотехнических систем проводной и беспроводной цифровой передачи данных. Техническим результатом является увеличение скорости преобразования цифрового сигнала в аналоговый и более точное представление формы аналогового сигнала на выходе цифроаналогового преобразователя. Устройство содержит многоразрядный параллельный преобразователь входных цифровых данных, преобразователь тактовой частоты, резистивную матрицу, аналоговый фильтр. 2 н. и 5 з.п. ф-лы, 7 ил.

1. Структура цифро-аналогового преобразователя, состоящая из цифровой части, включающей многоразрядный параллельный преобразователь входных цифровых данных, выход которого является выходом цифровой части, и аналоговой части, включающей резистивную матрицу, число входов которой равно числу разрядов многоразрядного параллельного преобразователя входных цифровых данных, и аналоговый фильтр; где каждый выход многоразрядного параллельного преобразователя входных цифровых данных соединен со своим входом резистивной матрицы, выход которой в свою очередь подключен к аналоговому фильтру, отличающаяся тем, что

цифровая часть дополнительно содержит преобразователь тактовой частоты, имеющий число выходов, равное числу разрядов многоразрядного параллельного преобразователя входных цифровых данных, и каждый из этих выходов соединен со своим разрядом упомянутого многоразрядного параллельного преобразователя входных цифровых данных.

2. Структура по п.1, отличающаяся тем, что многоразрядный параллельный преобразователь входных цифровых данных выполнен с возможностью дополнительного преобразования последовательных входных данных в параллельную форму.

3. Структура по п.1 или 2, отличающаяся тем, что резистивная матрица является одной из резистивных матриц (резистивная матрица постоянного импеданса, двоично-взвешивающая резистивная матрица, резистивный делитель Кельвина) или комбинацией из перечисленных резистивных матриц.

4. Структура по п.3, отличающаяся тем, что цифровая часть выполнена на программируемой логической интегральной схеме.

5. Способ цифро-аналогового преобразования, заключающийся в том, что входные цифровые данные преобразуются в параллельную форму в цифровой части ЦАП и по сигналу тактовой частоты одновременно поступают на резистивную матрицу, число входов которой равно числу выходов цифровой части ЦАП, где преобразуются в аналоговый сигнал с последующей фильтрацией, отличающийся тем, что

сигнал тактовой частоты преобразуется в многоразрядный тактовый сигнал таким образом, чтобы аналоговый сигнал как можно точнее повторял форму требуемого сигнала, а число разрядов тактового сигнала при этом равно числу разрядов цифровой части ЦАП, и тактовый сигнал каждого из разрядов подается на свой разряд цифровой части ЦАП, разрешая изменение сигнала на выходе своего разряда независимо от других разрядов.

6. Способ согласно п.5, отличающийся тем, что

а) на каждый разряд цифровой части ЦАП тактовый сигнал может подаваться в моменты времени как кратные, так и не кратные периоду (больше, меньше периода) тактового сигнала;

б) тактовый сигнал для каждого разряда цифровой части ЦАП формируется только в том случае, если необходимо изменение сигнала на выходе этого разряда.

7. Способ согласно п.6, отличающийся тем, что многоразрядный тактовый сигнал формируется таким образом, чтобы смена сигнала на выходе цифровой части ЦАП подчинялась следующим условиям:

а) изменение сигнала на выходе цифровой части ЦАП возможно, если должна произойти смена единицы на ноль в одном разряде (нескольких разрядах) или смена ноля на единицу в одном разряде (нескольких разрядах);

б) если происходит смена единицы на ноль (ноля на единицу) в каком-либо разряде (разрядах) на выходе цифровой части ЦАП, то последующая смена ноля на единицу (единицы на ноль) в этом же разряде (разрядах) возможна лишь через время, равное или большее, чем период тактового сигнала этого разряда (разрядов);

в) изменение сигнала на выходе цифровой части ЦАП невозможно, если должна произойти смена единицы на ноль в одном разряде (нескольких разрядах) при одновременной смене ноля на единицу в другом разряде (нескольких других разрядах);

г) изменение сигнала на выходе цифровой части ЦАП невозможно, если должна произойти смена ноля на единицу в одном разряде (нескольких разрядах) при одновременной смене единицы на ноль в другом разряде (нескольких других разрядах).

| СПОСОБ ЦИФРОАНАЛОГОВОГО ПРЕОБРАЗОВАНИЯ | 2009 |

|

RU2420867C2 |

| Цифро-аналоговый преобразователь | 1981 |

|

SU1019622A1 |

| US 6130634 A, 10.10.2000 | |||

| US 6344816 B1, 05.02.2002 | |||

| US 2002097175 A1, 25.07.2002 | |||

| US 7321328 B1, 22.01.2008 | |||

Авторы

Даты

2015-03-20—Публикация

2012-12-10—Подача