Изобретение относится к способам регулирования уровня громкости и может найти применение в регуляторах громкости цифрового звукового кода [H03M 1/66].

Известны различные типы цифроаналоговых преобразователей (ЦАП) [1], построенные как на резистивных матрицах различного типа, так и на основе преобразования частоты в напряжение, которые используют как регуляторы громкости.

К недостаткам известных ЦАП можно отнести технологическую сложность и дороговизну изготовления прецизионных резистивных матриц, а второго типа ЦАП - недостаточную точность и линейность характеристики преобразования. Известно, что прецизионные резистивные матрицы можно изготовить только по тонкопленочной технологии, включающей функциональную подгонку сопротивлений резисторов, а не по полупроводниковой, что и определяет указанные недостатки.

Известен цифроаналоговый преобразователь (патент РФ №2275740), содержащий, регистр, входы которого являются входами ЦАП, и операционный усилитель, выход которого является выходом ЦАП. Выходы регистра подключены к входам блока импульсных усилителей, выходы которого подключены к входам матрицы светодиодов, которая оптически связана с фотоприемником, соединенным с операционным усилителем.

Недостатками описанного устройства являются: низкое быстродействие из-за применения импульсных усилителей, а также значительные массогабаритные показатели, обусловленные применением матрицы светодиодов, на которую, кроме того, приходится основное потребление мощности.

Наиболее близким по технической сущности является патент EP 0287312. Сущность этого решения основана на том, что ЦАП содержит дополнительный n разрядный регистр, к входам регистров подключены соответствующие выходы блока управления, а к выходам регистров подключены n разрядные резисторные R-матрицы.

Недостатком решения является то, что в классической R-2R матрице при преобразовании переменного звукового сигнала необходимо сформировать виртуальный "0", т.е. поставить матрицу в среднее значение выходного напряжение, равного половине напряжения питания, что соответствует абсолютному "0" в звуковом сигнале. Этот недостаток требует использовать на выходе матрицы разделительный конденсатор для фильтрации постоянной составляющей. Также налицо различная логика при формировании положительного и отрицательного полупериода, для максимального уровня положительного полупериода все разряды необходимо поставить в положение "1", а для максимального уровня отрицательного полупериода - в "0".

Целью изобретения является устранение недостатков прототипа и улучшение эксплуатационных показателей цифроаналогового преобразователя как регулятора громкости.

Технический результат состоит в отсутствии необходимости фильтровать постоянную составляющую и использовать разделительный конденсатор, совмещении трансформатором функции сумматора, что в целом обеспечивает: увеличение быстродействия преобразования и повышение точности преобразования. Выходной сигнал формируется в трансформаторе, который реализует функцию сумматора и позволяет изменить уровень выходного сигнала по уровню и дать гальваническую развязку между преобразователем (цап) и потребителем переменного звукового сигнала. В отличие от прототипа в заявленном нами изобретении при отсутствии звукового сигнала обе матрицы находятся в положении полного нуля и логика формирования полупериодов одинаковая.

Технический результат достигается за счет того, что в способе регулирования уровня громкости, характеризующемся использованием ЦАП, содержащего n разрядный регистр, дополнительный n разрядный регистр, к входам регистров подключены соответствующие выходы блока управления, а к выходам регистров подключены n разрядные резисторные R-2R матрицы, отличающемся тем, что исходный параллельный цифровой код подают на блок переменных резисторов таким образом, что каждому биту соответствует свой резистор, причем резисторы управляются программно и синхронно по команде внешнего управляющего устройства; уровень звукового сигнала изменяют посредством изменения уровня опорного напряжения (логической "1") и измененный по уровню код направляют на повторитель, выполненный на операционных усилителях, причем каждому биту назначают свой соответствующий операционный усилитель.

В частности, трансформатор выполняют с возможностью изменения коэффициента трансформации.

В частности, n разрядную R-2R матрицу оснащают n параллельными резисторами с сопротивлением 2R Ом, которые соединяют между собой n-1 резисторами с сопротивлением R Ом и через резистор с сопротивлением 2R Ом подключают к заземлению.

В частности, к входам R-2R матрицы подключают ключи, один вход которых подключают к заземлению, а другой к источнику напряжения.

Краткое описание чертежей

На фиг. 1 представлена структурная схема цифроаналогового преобразователя, реализующего способ.

На фиг. 2 представлено схематичное изображение параллельного четырехразрядного ЦАП.

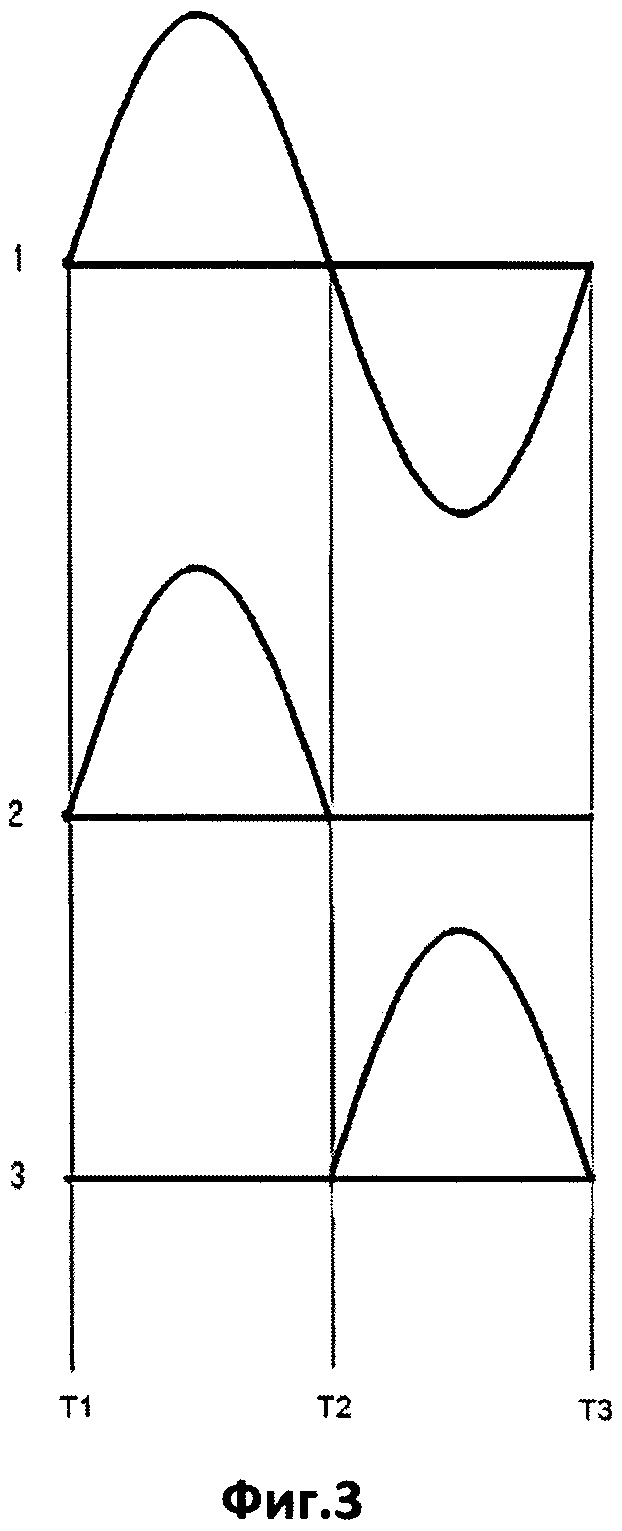

На фиг. 3 представлены эпюры, поясняющие принцип работы способа.

Осуществление изобретения

Способ может быть реализован посредством выполнения цифроаналогового преобразователя, который содержит блок управления 1, который соединен с n разрядным регистром 2 и n разрядным регистром 3. Выходы регистров 2 и 3 соответственно подключены к входам n разрядных резисторных матриц 4 и 5. Одна пара выходов резисторных R-2R матриц 4 и 5 через резисторы 6 и 7 подключена к заземлению 8, другая пара выходов матриц 4 и 5 подключена к трансформатору 9.

Четырехразрядный цифроаналоговый преобразователь (фиг. 2) содержит резисторную матрицу 10 с 4 параллельными резисторами, сопротивление которых составляет 2-R Ом, которые сообщаются между собой 3 сопротивлениями с номиналом R Ом. К параллельным резисторам подключены ключи 11-14. К одному входу ключей 11-14 подключен источник питания, а к другому входу подключено заземление 15. Ключу 11 соответствует значение младшего разряда цифрового кода. К выходу параллельного резистора, соответствующего младшему разряду цифрового кода, подключено сопротивление 16, выход которого подключен к заземлению 15. К выходу параллельного резистора, соответствующего старшему разряду цифрового кода, подключена клемма выходного напряжения.

Сопротивление резисторов 6, 7 и 16 составляет 2R Ом.

Блок управления 1 реализует поочередное подключение входного цифрового кода к регистру 2 или 3. В зависимости от знака преобразуемого цифрового кода. Если старший бит цифрового кода «1», то блок управления 1 подает цифровой код на соответствующие входы регистра 2, а если старший бит «0», то блок управления 1 подает цифровой код на соответствующие входы регистра 3. Тем самым реализуется смена полярности аналогового сигнала на выходе трансформатора 9. Логическому «0» старшего бита преобразуемого цифрового кода соответствует положительная полярность на выходе трансформатора 9, логической «1» старшего бита соответствует отрицательная полярность сигнала на выходе трансформатора 9.

Выходной сигнал формируется в трансформаторе 9, который реализует функцию сумматора, и тем самым обеспечивает восстановление исходного цифрового сигнала, а также обеспечивает гальваническую развязку между преобразователем и потребителем.

Изменение коэффициента трансформации трансформатора 9 позволяет изменять уровень выходного сигнала.

Способ работает следующим образом.

Преобразуемый цифровой код подают на вход блока управления 1.

В период времени от Т1 до Т2 (фиг. 3) блок управления 1 направляет цифровой код на соответствующие разряды регистра 3. Напряжение в точке «а» иллюстрирует эпюра 2 на фиг. 3. На выходах регистра 3 в этот момент напряжение равно нулю. Ток протекает через выходной трансформатор 9 от точки «а» к точке «б», формируя положительную полуволну выходного напряжения на вторичной обмотке трансформатора 9.

В период времени от Т2 до Т3 блок управления 1 направляет цифровой код на соответствующие входы регистра 2. Напряжение в точке «б» соответствует эпюре 3 на графике. Напряжение на выходах регистра 2 в данный момент времени равно нулю. Ток через выходной трансформатор протекает в направлении от точки «б» к точке «а», формируя отрицательную полуволну выходного напряжения на вторичной обмотке выходного трансформатора 9.

В результате поочередной работы регистра 2 и 3 и двух матриц 4 и 5 на вторичной обмотке выходного трансформатора 9 формируется полноценное переменное выходное напряжение преобразователя - эпюра 1 на фиг. 3.

Расчет значений выходного напряжения продемонстрируем на примере работы аналогичного четырехразрядного ЦАП (фиг. 2).

Если ключи 11-14 находятся в положении "0", то выходное напряжение будет равно нулю.

Если ключ 11 младшего разряда цифрового кода установлен в положение "1", а все остальные в положение "0", то

Uвых=V*1/16.

Если ключ 12 первого разряда установлен в положение "1", а все остальные в положение "0", то

Uвых=V*1/8.

Если ключи 11 и 12 установлены в положение "1", а все остальные в положение "0", то

Uвых=V*(1/16+1/8).

В общем случае получим:

Uвых=V*(А0*1/16+A1*1/8+А2*1/4+А3*1/2),

где Аi=1, если соответствующий ключ (Ki) находится в положении "1", и Ai=0, если соответствующий ключ находится в положении "0".

То есть, замыкая различными способами ключи К0…К3, то есть подавая на вход четырехбитный код A3A2A1A0, можно получить 24=16 различных значений выходного напряжения (от Uвых=0 до Uвых=V*(1-1/16) с шагом Δ=V*1/16).

Таким образом, данная схема представляет собой простейший параллельный четырехбитный цифроаналоговый преобразователь.

Аналогично можно построить восьми-, десяти-, двенадцати- и n-битный ЦАП.

В общем случае, для n-битного ЦАП будем иметь

Uвых=V*Σ(A1*/2n-1),

где i - номер разряда (i=0, 1, 2…n-1), Ai=1, если соответствующий ключ замкнут на шину питания, и Аi=0, если соответствующий ключ замкнут на общий провод.

Шаг определяется по формуле: Δ=V/2n, где n - общее число разрядов.

Рассматриваемый цифроаналоговый преобразователь (фиг. 1) можно реализовать на микроконтроллере с достаточным количеством неиспользуемых ножек.

В классической R-2R матрице при преобразовании переменного звукового сигнала необходимо сформировать виртуальный "0", то есть поставить матрицу в среднее значение выходного напряжения, равного половине напряжения питания, что соответствует "0" в звуковом сигнале.

Этот недостаток требует использования на выходе резисторной матрицы разделительного конденсатора для подавления постоянной составляющей. Также в классическом варианте реализации резисторной матрицы различается логика при формировании положительного и отрицательного полупериода, для максимального уровня положительного полупериода все разряды необходимо поставить в положение "1", а для максимального уровня отрицательного полупериода - в "0".

В предлагаемом ЦАП при отсутствии звукового сигнала обе матрицы находятся в положении полного нуля и соответственно логика формирования полупериодов резисторными матрицами 4 и 5 одинакова.

К положительным эффектам от использования ЦАМ можно отнести следующее:

- увеличение быстродействия преобразования, ограничиваемого скоростью переключения блока управления 1; оно реализуется за счет уменьшения количества компонентов электрической схемы;

- повышение точности преобразования за счет линеаризации характеристики преобразователя, которая достигается за счет того, что используемая резисторная матрица не формирует виртуальный ноль и тем самым выпрямляет характеристику в районе нулевого положения.

В качестве положительных эффектов можно выделить снижение стоимости преобразователя за счет того, что можно использовать резисторы с меньшей точностью.

Источник информации

1. Федорков Б.Г., Телец В.А. Микросхемы ЦАП и АЦП: функционирование, параметры, применение. - М.: Энергоатомиздат, 1990. - 320 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2019 |

|

RU2713758C1 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2023 |

|

RU2824647C1 |

| СПОСОБ ЦИФРОАНАЛОГОВОГО ПРЕОБРАЗОВАНИЯ | 2015 |

|

RU2622623C1 |

| ЦИФРО-АНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2013 |

|

RU2546557C2 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2029430C1 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2066924C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2002 |

|

RU2240649C2 |

| Функциональный генератор | 1979 |

|

SU822213A1 |

| Обращенный цифроаналоговый преобразователь с резистивной матрицей R-2R | 1986 |

|

SU1345347A1 |

| СЛЕДЯЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1989 |

|

RU2028731C1 |

Изобретение относится к области регулирования уровня громкости. Технический результат - обеспечение повышения быстродействия и точности преобразования. Способ регулирования уровня громкости характеризуется использованием ЦАП, содержащего n разрядный регистр, дополнительный n разрядный регистр, к входам регистров подключены соответствующие выходы блока управления, а к выходам регистров подключены n разрядные резисторные R-2R матрицы; исходный параллельный цифровой код подают на блок переменных резисторов таким образом, что одна пара выходов резисторных R-2R матриц через резисторы подключена к заземлению, другая пара выходов матриц подключена к трансформатору, каждому биту соответствует свой резистор, причем резисторы управляются программно и синхронно по команде внешнего управляющего устройства; уровень звукового сигнала изменяют посредством изменения уровня опорного напряжения (логической "1") и измененный по уровню код направляют на повторитель, выполненный на операционных усилителях, причем каждому биту назначают свой соответствующий операционный усилитель. 3 з.п. ф-лы, 3 ил.

1. Способ регулирования уровня громкости, характеризующийся использованием ЦАП, содержащего n разрядный регистр, дополнительный n разрядный регистр, к входам регистров подключены соответствующие выходы блока управления, а к выходам регистров подключены n разрядные резисторные R-2R матрицы, отличающийся тем, что исходный параллельный цифровой код подают на блок переменных резисторов таким образом, что одна пара выходов резисторных R-2R матриц через резисторы подключена к заземлению, другая пара выходов матриц подключена к трансформатору, каждому биту соответствует свой резистор, причем резисторы управляются программно и синхронно по команде внешнего управляющего устройства; уровень звукового сигнала изменяют посредством изменения уровня опорного напряжения (логической "1") и измененный по уровню код направляют на повторитель, выполненный на операционных усилителях, причем каждому биту назначают свой соответствующий операционный усилитель.

2. Способ по п. 1, отличающийся тем, что трансформатор выполняют с возможностью изменения коэффициента трансформации.

3. Способ по п. 1, отличающийся тем, что n разрядную R-2R матрицу оснащают n параллельными резисторами с сопротивлением 2·R Ом, которые соединяют между собой n-1 резисторами с сопротивлением R Ом и через резистор с сопротивлением 2·R Ом подключают к заземлению.

4. Способ по п. 1, отличающийся тем, что к входам R-2R матрицы подключают ключи, один вход которых подключают к заземлению, а другой к источнику напряжения.

| ЛИГАТУРА ДЛЯ ЛЕГИРОВАНИЯ СТАЛЕЙ и СПЛАВОВ | 0 |

|

SU287312A1 |

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2004 |

|

RU2275740C1 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2012 |

|

RU2485681C1 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2009 |

|

RU2390929C1 |

| Б.Г | |||

| ФЕДОРКОВ и др., "Микросхемы ЦАП и АЦП: функционирование, параметры, применение", Москва, Энергоатомиздат, 1990, 320с | |||

Авторы

Даты

2015-09-10—Публикация

2014-04-25—Подача