Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных устройствах, а также в устройствах цифровой обработки сигналов и в криптографических приложениях.

Известен накапливающий сумматор, содержащий 3 сумматора и 3 регистра (см. Тарабрин Б.В. Справочник по интегральным микросхемам / Б.В. Тарабрин, С.В. Якубовский, Н.А. Барканов и др. Под ред. Б.В. Тарабрина. - 2-е изд., перераб. и доп. - М.: Энергия, 1981, рис.5-250, стр.741).

Недостатком указанного устройства является низкое быстродействие.

Наиболее близким по технической сущности и достигаемому результату к заявляемому изобретению является накапливающий сумматор, содержащий 2 сумматора и регистр (см. Пухальский Г.И., Новосельцева Т.Я. Проектирование дискретных устройств на интегральных микросхемах: Справочник. - М.: Радио и связь, 1990, рис.4.80, стр.263).

Недостатком данного устройства является низкое быстродействие.

Техническим результатом изобретения является повышение быстродействия.

Для достижения поставленного технического результата в накапливающий сумматор, содержащий первый и второй n-разрядные сумматоры и 2n-разрядный регистр, причем первые информационные входы первого сумматора соединены с k/2 младшими разрядами информационных входов устройства, где k=2n - разрядность входных чисел, информационные выходы первого сумматора соединены с первыми n информационными входами регистра, первые n информационных выходов которого соединены со вторыми информационными входами первого сумматора, на вход переноса которого подается сигнал логического нуля, первые информационные входы второго сумматора соединены с k/2 старшими разрядами информационных входов устройства, тактовый вход регистра является тактовым входом устройства, вход обнуления регистра является входом обнуления устройства, введены третий n-разрядный сумматор и мультиплексор, причем выход переноса первого сумматора соединен с управляющим входом мультиплексора, первые информационные входы третьего сумматора соединены с k/2 старшими разрядами информационных входов устройства и с первыми информационными входами второго сумматора, на вход переноса второго сумматора подается сигнал логического нуля, а на вход переноса третьего сумматора подается сигнал логической единицы, информационные выходы второго сумматора соединены с первыми n информационными входами мультиплексора, а выход переноса соединен с его первым n+1 информационным входом, информационные выходы третьего сумматора соединены со вторыми n информационными входами мультиплексора, а выход переноса соединен с его вторым n+1 информационным входом, первые n выходов которого соединены с (n+1)…2n информационными входами регистра, выходы которого являются информационными выходами устройства, а (n+1)…2n выходы соединены со вторыми информационными входами второго и третьего сумматоров, n+1 выход мультиплексора является выходом переноса устройства.

Поставленный технический результат достигается за счет параллельного суммирования младших и старших k/2 разрядов входного k-разрядного числа.

Сущность изобретения заключается в реализации следующего способа накопительного суммирования чисел Ai, поступающих последовательно в параллельном коде с разрядностью k на вход накапливающего сумматора. Младшие k/2 разрядов входного числа поступают на один сумматор, а старшие k/2 разрядов входного числа поступают на два сумматора одновременно, один из которых осуществляет суммирование с учетом входного сигнала переноса, равного логическому нулю, а второй осуществляет суммирование с учетом входного сигнала переноса, равного логической единице. В итоге результат суммирования для младших k/2 разрядов и для старших k/2 разрядов вычисляется одновременно, т.е. исключается необходимость начала процесса суммирования старших k/2 разрядов по окончании суммирования младших k/2 разрядов. Сигналом переноса по результатам суммирования младших k/2 разрядов выбирается один из результатов суммирования старших k/2 разрядов.

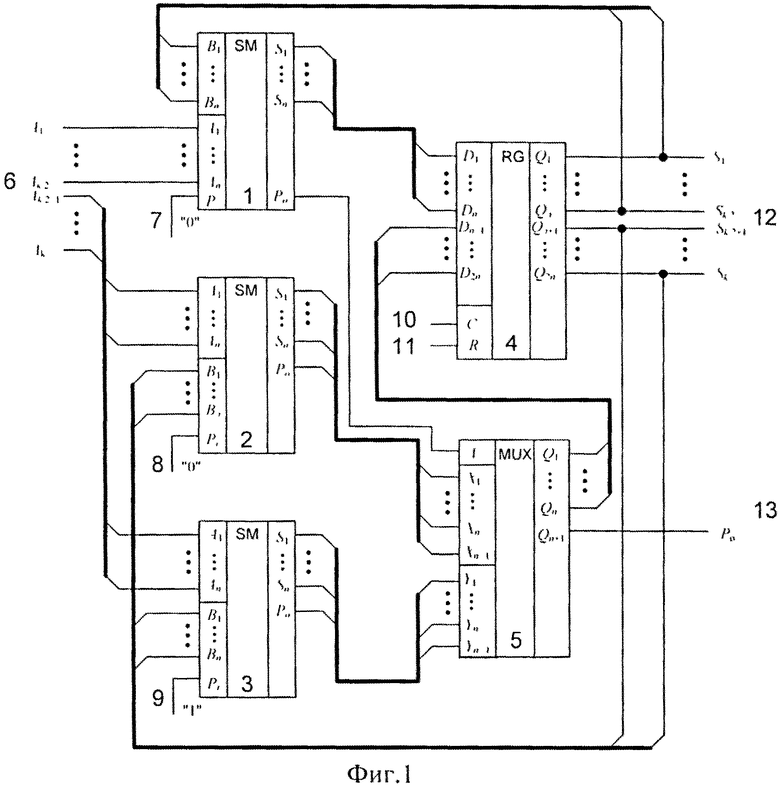

На фиг.1 представлена схема накапливающего сумматора.

Накапливающий сумматор содержит первый 1, второй 2 и третий 3 сумматоры, регистр 4, мультиплексор 5, информационные входы 6 устройства, вход переноса 7 устройства, входы 8 и 9 переноса сумматоров 2 и 3 соответственно, тактовый вход 10 устройства, вход обнуления 11 устройства, информационные выходы 12 устройства, выход переноса 13 устройства. Информационный вход 6 является k-разрядным входом устройства, на который подаются последовательно в параллельном коде суммируемые числа. Младшие k/2-разрядов входа 6 устройства соединены с первыми информационными входами первого 1 сумматора, а старшие k/2-разрядов соединены с первыми информационными входами второго 2 и третьего 3 сумматоров. На входы переноса 7 и 8 первого 1 и второго 2 сумматоров подается сигнал логического нуля, а на вход переноса 9 третьего сумматора 3 подается сигнал логической единицы. Информационные выходы первого сумматора 1 соединены с первыми n информационными входами регистра 4, а выход переноса первого сумматора 1 соединен с управляющим входом мультиплексора 5. Информационные выходы второго сумматора 2 соединены с первыми n информационными входами мультиплексора 5, а выход переноса соединен с его первым n+1 информационным входом. Информационные выходы третьего сумматора 3 соединены со вторыми n информационными входами мультиплексора 5, а выход переноса соединен с его вторым n+1 информационным входом. Первые n выходов мультиплексора 5 соединены с (n+1)…2n информационными входами регистра 4, выходы которого являются информационными выходами 12 устройства, причем первые n информационных выходов регистра 4 соединены со вторыми информационными входами первого сумматора 1, а (n+1)…2n выходы соединены со вторыми информационными входами второго 2 и третьего 3 сумматоров, при этом n+1 выход мультиплексора 5 является выходом переноса 13 устройства.

Накапливающий сумматор работает следующим образом.

Перед началом процедуры накапливающего суммирования на вход 11 обнуления устройства поступает сигнал, который обнуляет регистр 4. На информационный вход 6 устройства подаются последовательно в параллельном коде суммируемые k-разрядные числа Ai.

Младшие k/2 разрядов входного числа поступают на первый сумматор 1, а старшие k/2 разрядов входного числа поступают на первые информационные входы сумматоров 2 и 3 одновременно, причем сумматор 2 осуществляет суммирование в предположении, что сигнал условного переноса при суммировании младших разрядов будет равен нулю, а сумматор 3 осуществляет суммирование в предположении, что сигнал условного переноса при суммировании младших разрядов будет равен единице. В итоге результат суммирования для младших k/2 разрядов и для старших k/2 разрядов вычисляется одновременно, т.е. исключается необходимость начала процесса суммирования старших k/2 разрядов по окончании суммирования младших k/2 разрядов. Сигнал переноса по результатам суммирования младших k/2 разрядов с выхода переноса первого сумматора 1 поступает на управляющий вход мультиплексора 5. Если сигнал переноса равен нулю, то на выход мультиплексора 5 коммутируются сигналы с его первых информационных входов, а если сигнал переноса равен единице, то со вторых информационных входов. На информационных входах регистра 4 всегда будет сумма чисел, записанных в регистр 4 и поступающих па вход 6 устройства.

Тактовые импульсы, следующие синхронно с входными числами, записывают результат суммирования в регистр 4. Результат накапливающего суммирования Si с выхода регистра 4 поступает на выход 12 устройства, а на выход 13 устройства поступает сигнал переноса Po с (n+1)-го выхода мультиплексора 5.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДВУХКАНАЛЬНЫЙ НАКАПЛИВАЮЩИЙ СУММАТОР ПО МОДУЛЮ | 2024 |

|

RU2823898C1 |

| Накапливающий сумматор | 2017 |

|

RU2642366C1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР-ВЫЧИТАТЕЛЬ ПО МОДУЛЮ ПРОИЗВОЛЬНОГО НАТУРАЛЬНОГО ЧИСЛА | 2021 |

|

RU2764876C1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР-ВЫЧИТАТЕЛЬ ПО МОДУЛЮ ПРОИЗВОЛЬНОГО НАТУРАЛЬНОГО ЧИСЛА | 2021 |

|

RU2763988C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ НАКАПЛИВАЮЩИЙ СУММАТОР ПО МОДУЛЮ ПРОИЗВОЛЬНОГО НАТУРАЛЬНОГО ЧИСЛА | 2020 |

|

RU2754122C1 |

| Многоканальный накапливающий сумматор по произвольным модулям | 2024 |

|

RU2837596C1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР ДЛЯ СИНТЕЗАТОРОВ ЧАСТОТ | 2020 |

|

RU2753594C1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОСТАТКА ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ ОТ ЧИСЛА | 2018 |

|

RU2696223C1 |

| КОНВЕЙЕРНЫЙ СУММАТОР ПО МОДУЛЮ | 2023 |

|

RU2799035C1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ, ВЫЧИТАНИЯ И УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 2019 |

|

RU2711051C1 |

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных устройствах, а также в устройствах цифровой обработки сигналов и в криптографических приложениях. Техническим результатом является повышение быстродействия устройства за счет параллельного суммирования младших и старших k/2 разрядов входного k-разрядного числа, где k=2n - разрядность входных чисел. Устройство содержит три n-разрядных сумматора, 2n-разрядный регистр и мультиплексор. 1 ил.

Накапливающий сумматор, содержащий первый и второй n-разрядные сумматоры и 2n-разрядный регистр, причем первые информационные входы первого сумматора соединены с k/2 младшими разрядами информационных входов устройства, где k=2n - разрядность входных чисел, информационные выходы первого сумматора соединены с первыми n информационными входами регистра, первые n информационных выходов которого соединены со вторыми информационными входами первого сумматора, на вход переноса которого подается сигнал логического нуля, первые информационные входы второго сумматора соединены с k/2 старшими разрядами информационных входов устройства, тактовый вход регистра является тактовым входом устройства, вход обнуления регистра является входом обнуления устройства, отличающийся тем, что в него введены третий n-разрядный сумматор и мультиплексор, причем выход переноса первого сумматора соединен с управляющим входом мультиплексора, первые информационные входы третьего сумматора соединены с k/2 старшими разрядами информационных входов устройства и с первыми информационными входами второго сумматора, на вход переноса второго сумматора подается сигнал логического нуля, а на вход переноса третьего сумматора подается сигнал логической единицы, информационные выходы второго сумматора соединены с первыми n информационными входами мультиплексора, а выход переноса соединен с его первым n+1 информационным входом, информационные выходы третьего сумматора соединены со вторыми n информационными входами мультиплексора, а выход переноса соединен с его вторым n+1 информационным входом, первые n выходов которого соединены с (n+1)…2n информационными входами регистра, выходы которого являются информационными выходами устройства, а (n+1)…2n выходы соединены со вторыми информационными входами второго и третьего сумматоров, n+1 выход мультиплексора является выходом переноса устройства.

| ПУХАЛЬСКИЙ Г.И | |||

| и др | |||

| ПРОЕКТИРОВАНИЕ ДИСКРЕТНЫХ УСТРОЙСТВ НА ИНТЕГРАЛЬНЫХ МИКРОСХЕМАХ | |||

| СПРАВОЧНИК | |||

| Москва, "Радио и связь", 1990, с | |||

| Способ изготовления гибких труб для проведения жидкостей (пожарных рукавов и т.п.) | 1921 |

|

SU268A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР | 2006 |

|

RU2381546C2 |

| Накапливающий сумматор | 1990 |

|

SU1829031A1 |

| Накапливающий сумматор | 1988 |

|

SU1597880A1 |

| JP 61109140 A, 27.05.1986 | |||

| СМЫВНОЕ УСТРОЙСТВО | 1997 |

|

RU2131499C1 |

| JP 3109670 A, 09.05.1991 | |||

Авторы

Даты

2015-03-20—Публикация

2014-03-27—Подача