Предлагаемое техническое решение относится к сумматорам двух многоразрядных чисел и может быть использовано для выполнения математических операций над числами большой разрядности или при требовании повышенного быстродействия.

Известно множество схем сумматоров с разным количеством разрядности чисел и с разным выполнением схемы переноса из младших в старшие разряды.

Известен сумматор с параллельным переносом (см. У.Титце, К.Шенк, 1983, Полупроводниковая схемотехника, Москва, Мир, Перевод с немецкого под редакцией д.т.н. А.Г.Алексенко», стр.332-333), в котором сумматор разбит на группы, в которых перенос осуществляется параллельно для уменьшения времени суммирования.

Известен сумматор (см. У.Титце, К.Шенк, 1983, Полупроводниковая схемотехника, Москва, Мир, Перевод с немецкого под редакцией д.т.н. А.Г.Алексенко, стр.334), в котором перенос из каждой группы суммирования в группу суммирования более старших разрядов производится также параллельным способом, как и внутри групп, что повышает быстродействие устройства.

Недостатком вышеуказанных устройств является низкое быстродействие, обусловленное процессом суммирования, выполняемым в одном тактовом интервале, поскольку результат суммирования обычно запоминается в оперативном запоминающем устройстве или параллельном регистре, которые тактируются.

Наиболее близким по технической сущности и достигаемому результату является накапливающий сумматор (см. Ю.В.Новиков, О.А.Калашников, С.Э.Гуляев, 1997, Разработка устройств сопряжения для персонального компьютера типа IBM PC, Москва, Издательство «Эком», стр.103), содержащий источник сигнала, выход которого подключен к первому входу сумматора, выход которого подключен ко входу параллельного регистра, тактовый вход которого подключен к выходу источника тактовых частот, а выход подключен ко второму входу сумматора.

В известном техническом решении низкое быстродействие обусловлено суммированием в одном тактовом интервале, а также увеличением нагрузок элементов схемы за счет увеличения разрядности накапливающего сумматора, что увеличивает его задержки и, как следствие, уменьшает быстродействие устройства.

Цель изобретения - повышение быстродействия накапливающего сумматора.

Достичь поставленную цель можно за счет разделения процесса суммирования на два и более тактовых интервалов, величина которых определяется источником тактовой частоты. При этом абсолютное время, потраченное на процесс суммирования, увеличивается за счет задержек, однако задержки на суммирование в каждом тактовом интервале уменьшаются, что позволяет увеличить тактовую частоту источника тактовой частоты, что, соответственно, увеличивает быстродействие накапливающего сумматора.

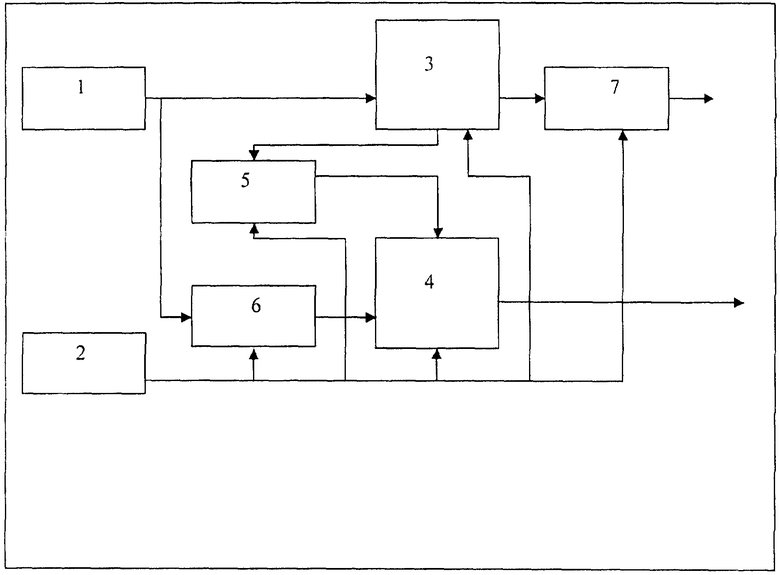

Структурная схема накапливающего сумматора при разделении процесса суммирования на два периода тактовой частоты приведена на чертеже.

Накапливающий сумматор содержит источник сигнала 1, источник тактовой частоты 2, накапливающие сумматоры 3 и 4 и три тактируемые линии задержки 5, 6 и 7. Выход источника тактовой частоты 2 подключен к тактовым входам накапливающих сумматоров 3 и 4, а также к тактовым входам тактируемых линий задержек 5, 6 и 7.

Устройство работает следующим образом. Источник сигнала 1 формирует данные младших и старших разрядов, включая старшие разряды знака сигнала, причем количество старших разрядов знака сигнала зависит от количества слагаемых, необходимых для суммирования в накапливающем сумматоре. Младшие разряды суммируются в накапливающем сумматоре 3, выход которого через линию задержки 7 поступает на выход младших разрядов накапливающего сумматора. Старшие разряды источника сигнала 1 поступают на второй накапливающий сумматор 4 через линию задержки 6, в частности это может быть знаковый разряд и часть старших разрядов источника сигнала 1, в зависимости от необходимого усреднения сигнала, что проявляется в количестве старших знаковых разрядов, которые необходимо ввести в накапливающий сумматор. Выход сигнала переполнения накапливающего сумматора 3 через линию задержки 5 поступает на вход сигнала переноса второго накапливающего сумматора 4, который суммирует старшие разряды, включая знаковый разряд, и сигнал переноса из первого накапливающего сумматора 3 через тактовый интервал источника тактовой частоты 2, что обеспечивается линиями задержки 5 и 6.

Таким образом, суммирование младших разрядов и старших разрядов происходит в разных тактовых интервалах, причем суммирование младших разрядов заканчивается раньше старших разрядов источника сигнала 1, поэтому с помощью линии задержки 7 результат суммирования младших разрядов выравнивается с задержкой старших разрядов. Выход накапливающего сумматора 4 является выходом старших разрядов накапливающего сумматора.

Тактируемая линия задержки 5 может быть реализована в виде D-триггера, а тактируемые линии задержки 6 и 7- в виде параллельных регистров, задерживающих сигнал на один тактовый интервал, для выравнивания входных и выходных сигналов накапливающего сумматора (см. И.И.Петровский, А.В.Прибыльский, А.А.Троян, B.C.Чувелев, 1993, Логические ИС КР 1554, Справочник, Москва, ТОО «Бином», стр.393).

Разделение суммирования накапливающего сумматора на разные тактовые интервалы, несмотря на увеличение общих затрат времени, позволяет увеличить частоту источника тактовой частоты, что и обеспечивает увеличение быстродействия накапливающего сумматора, причем чем больше групп, на которые разбит накапливающий сумматор для работы в разных тактовых интервалах, тем больше выигрыш в быстродействии.

Сравнение предлагаемого решения с известными техническими решениями показывает, что оно обладает новой совокупностью существенных признаков, которые совместно с известными признаками позволяют успешно реализовать поставленную цель.

| название | год | авторы | номер документа |

|---|---|---|---|

| НАКАПЛИВАЮЩИЙ СУММАТОР ДЛЯ СИНТЕЗАТОРОВ ЧАСТОТ | 2020 |

|

RU2753594C1 |

| Преобразователь кода | 1981 |

|

SU1014144A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ НАКАПЛИВАЮЩИЙ СУММАТОР ПО МОДУЛЮ ПРОИЗВОЛЬНОГО НАТУРАЛЬНОГО ЧИСЛА | 2020 |

|

RU2754122C1 |

| Цифровое сглаживающее устройство | 1974 |

|

SU643884A1 |

| СПОСОБ УПРАВЛЕНИЯ ГРУППОЙ ИМПУЛЬСНЫХ ПРЕОБРАЗОВАТЕЛЕЙ | 1983 |

|

SU1284443A1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР-ВЫЧИТАТЕЛЬ ПО МОДУЛЮ ПРОИЗВОЛЬНОГО НАТУРАЛЬНОГО ЧИСЛА | 2021 |

|

RU2764876C1 |

| МНОГОЧАСТОТНЫЙ ФАЗОЦИФРОВОЙ ДЕТЕКТОР | 1988 |

|

RU2040851C1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР-ВЫЧИТАТЕЛЬ ПО МОДУЛЮ ПРОИЗВОЛЬНОГО НАТУРАЛЬНОГО ЧИСЛА | 2021 |

|

RU2763988C1 |

| Устройство для алгебраического накопительного суммирования двоичных чисел | 1988 |

|

SU1658144A1 |

| Устройство для умножения | 1981 |

|

SU1007101A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения сумматоров. Техническим результатом является повышение быстродействия. Устройство содержит источник сигнала, источник тактовой частоты, два накапливающих сумматора, три тактируемые линии задержки. 1 ил.

Накапливающий сумматор, содержащий источник сигнала, выход которого подключен к входу первого накапливающего сумматора, тактовый вход которого подключен к выходу источника тактовой частоты, отличающийся тем, что дополнительно введены второй накапливающий сумматор и три линии задержки, тактовые входы которых подключены к источнику тактовой частоты, причем вход первой линии задержки подключен к выходу переполнения первого накапливающего сумматора, а выход - к входу сигнала переноса второго накапливающего сумматора, вход которого подключен к выходу второй линии задержки, а выход является выходом старших разрядов накапливающего сумматора, вход третьей линии задержки подключен к выходу первого накапливающего сумматора, а выход является выходом младших разрядов накапливающего сумматора, вход второй линии задержки подключен к выходу источника сигнала.

| RU 2002297 С1, 30.10.1993 | |||

| НАКАПЛИВАЮЩИЙ СУММАТОР | 1993 |

|

RU2043650C1 |

| Накапливающий сумматор | 1988 |

|

SU1597880A1 |

| 1972 |

|

SU416869A1 | |

| JP 3113671 А, 15.05.1991. | |||

Авторы

Даты

2010-02-10—Публикация

2006-05-04—Подача