Предпосылки создания изобретения

Настоящее изобретение относится в целом к трансляции (преобразованию или переводу) адресов в вычислительной среде, более точно, к трансляции адреса ввода-вывода в адрес ячейки памяти, применимый при доступе к системной памяти среды.

Системная память доступна посредством запросов чтения и записи. Эти запросы могут поступать от различных компонентов вычислительной среды, включая центральные процессоры, а также адаптеры. Каждый запрос содержит адрес, который должен использоваться для доступа к системной памяти. Тем не менее, этот адрес обычно не находится во взаимно однозначном соответствии с физическим местоположением в системной памяти. Соответственно, осуществляется трансляция адреса.

Трансляция адреса используется, чтобы преобразовать адрес, который находится в одной форме, непосредственно неприменимой для доступа к системной памяти, в другую форму, непосредственно применимую для доступа к физическому местоположению в системной памяти. Например, виртуальный адрес, содержащийся в запросе, выдаваемом центральным процессором, транслируется в действительный или абсолютный адрес в системной памяти. В качестве одного из дополнительных примеров, адрес шины межсоединения периферийных компонентов (PCI), содержащийся в запросе от адаптера, может быть транслирован в абсолютный адрес в системной памяти.

В заявке US 2008/0168208 A1 под названием "I/O Adaptet LPAR Isolation In A Hypertransport Environment With Assigned Memory Space Indexing A TVT Via Unit Ids", опубликованной 10 июля 2008 г. (заявитель - Gregg), описана система обработки данных и способ обособления множества адаптеров ввода-вывода в системе. В систему обработки данных также входит набор процессоров, мост между хостами и системная шина, соединяющая набор процессоров и мост между хостами. Каждый из адаптеров ввода-вывода имеет соответствующий идентификатор (ID) и выдает мосту между хостами команды, которые содержат один или несколько из ID адаптеров ввода-вывода. В предпочтительном варианте осуществления этими ID являются определяемые протоколом пересылки гипертекста идентификаторы устройства, а команды, выдаваемые адаптерами ввода-вывода, включают поле ID устройства, в котором содержится один или несколько из ID адаптеров ввода-вывода. Каждый ID устройств используется для индексации TVT с целью идентификации уникальных и независимых пространств системной памяти.

В заявке US 2009/0182966 A1 под названием "Dynamic Address Translation with Frame Management", опубликованной 16 июля 2009 г. (заявитель - Greiner и др.), описана функция управления кадрами, определенная для архитектуры компьютерной системы. В одном из вариантов осуществления принимают команду управления кадрами, в которой определен первый и второй общий регистр. В первом общем регистре содержится поле управления кадрами, имеющее ключевое поле с битами защиты доступа и индикатор размера блока. Если в индикаторе размера блока указан блок большого размера, из второго общего регистра получают адрес операнда блока данных большого размера. Блок данных большого размера содержит множество блоков небольшого размера, каждый из которых связан с соответствующим ключом хранения, содержащим множество битов защиты доступа. Если в индикаторе размера блока указан блок большого размера, в качестве битов защиты доступа для каждого соответствующего ключа хранения каждого блока небольшого размера в блоке большого размера устанавливают биты защиты доступа ключевого поля.

Краткое изложение сущности изобретения

Преодоление недостатков известного уровня техники и достижение дополнительных преимуществ обеспечивается в способ трансляции адресов в вычислительной среде. Предлагаемый в изобретении способ может быть реализован в компьютерном программном продукте, содержащем машиночитаемую среду, которая может считываться устройством обработки данных и в которой хранятся команды для выполнения устройством обработки данных с целью осуществления способа. Способ включает, например, получение от адаптера подлежащего трансляции адреса, содержащего множество разрядов, в которое входит первая часть разрядов и вторая часть разрядов; прием значения диапазона адресов, указывающего диапазон допустимых адресов; проверку достоверности адреса с использованием по меньшей мере первой части разрядов и принятого диапазона адресов; и преобразование адреса в адрес ячейки памяти, применимый при доступе к памяти вычислительной среды, причем в ходе преобразования первая часть разрядов не учитывается, а вторая часть разрядов используется для получения информации об адресе из одного или нескольких уровней таблиц трансляции адресов для осуществления преобразования.

Объектом изобретения является также компьютерная система, содержащая компоненты, необходимые для трансляции адресов в вычислительной среде.

Дополнительные признаки и преимущества настоящего изобретения реализуются за счет предложенной в нем методики. В изобретении подробно описаны другие его варианты осуществления и особенности, считающиеся входящими в заявленное изобретение.

Краткое описание чертежей

Одна или несколько особенностей настоящего изобретения конкретно охарактеризованы и отдельно заявлены в формуле изобретения, следующей за описанием. Перечисленные выше и другие задачи, признаки и преимущества изобретения станут ясны из следующего далее подробного описания в сочетании с сопровождающими его чего чертежами, на которых:

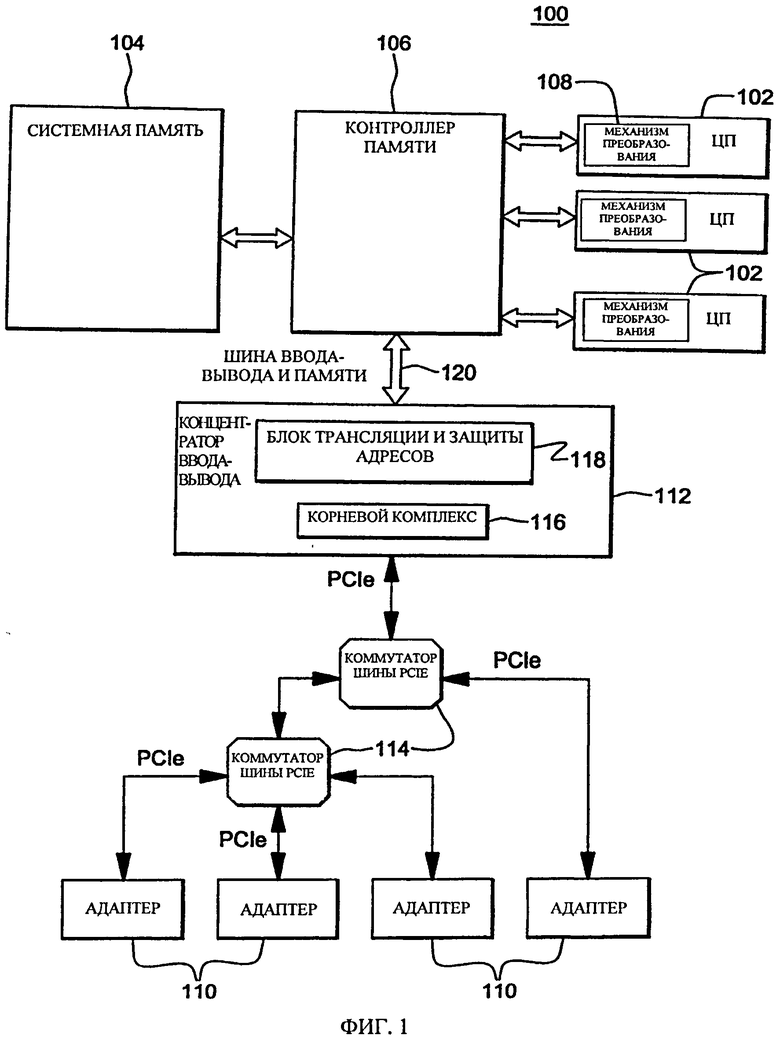

на фиг.1 проиллюстрирован один из вариантов осуществления вычислительной среды, в которой содержится и используется одна или несколько особенностей настоящего изобретения,

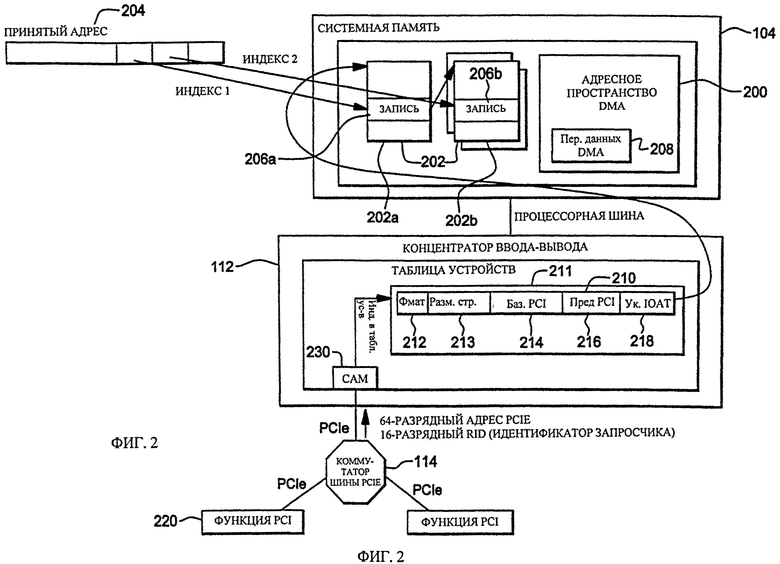

на фиг.2 - один из вариантов осуществления дополнительных подробностей показанных на фиг.1 системной памяти и концентратора ввода-вывода согласно одной из особенностей настоящего изобретения,

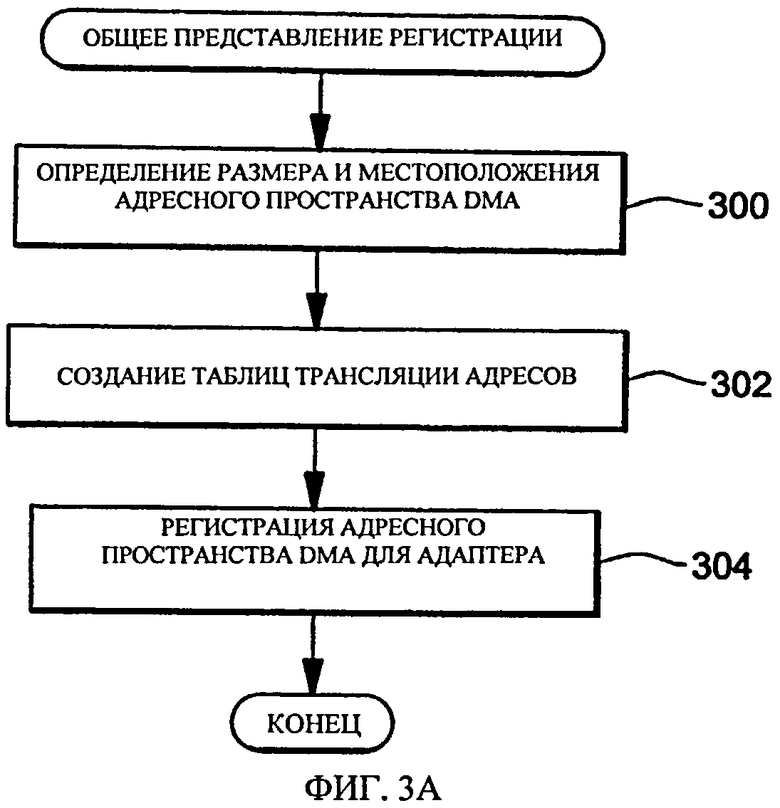

на фиг.3A - один из вариантов осуществления общего представления логики для регистрации адресного пространства прямого доступа к памяти (DMA) для адаптера согласно одной из особенностей настоящего изобретения,

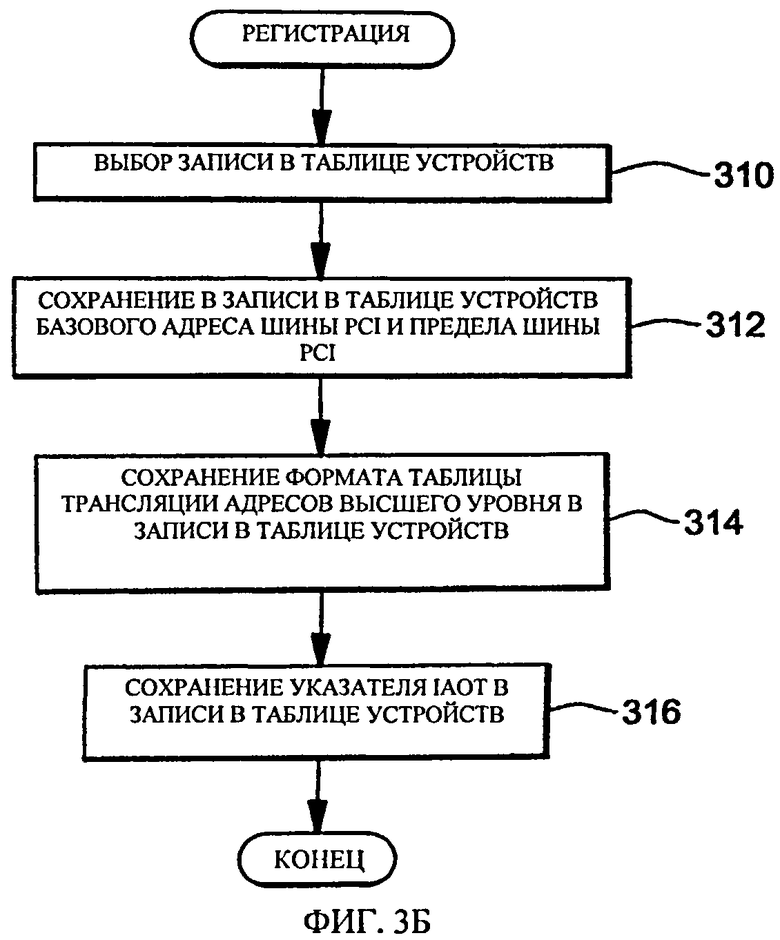

на фиг.3Б - один из вариантов осуществления различных подробностей регистрации адресного пространства DMA для адаптера согласно одной из особенностей настоящего изобретения,

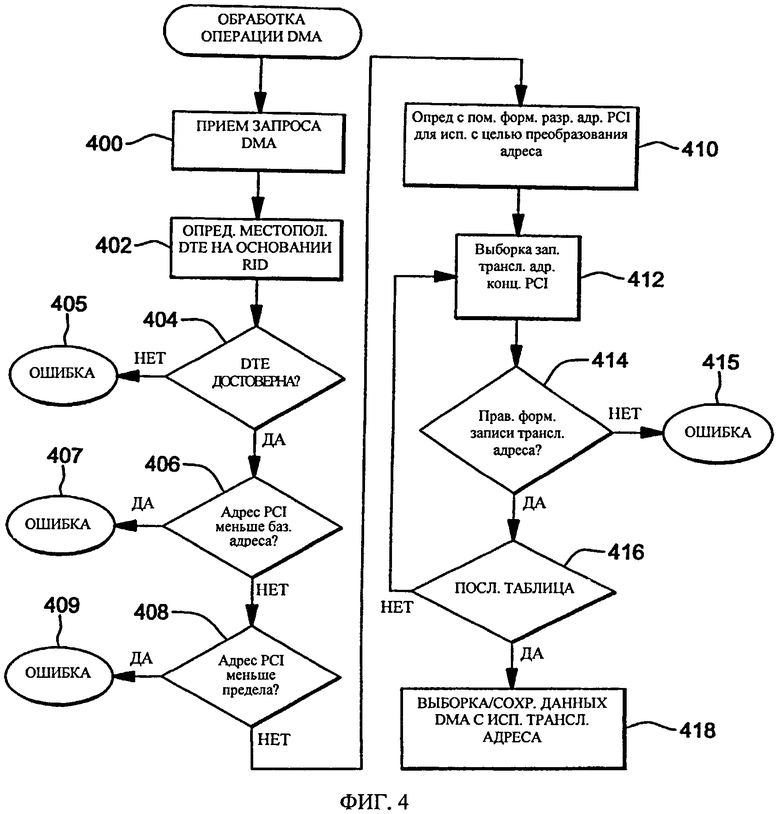

на фиг.4 - один из вариантов осуществления логики для обработки операции DMA согласно одной из особенностей настоящего изобретения,

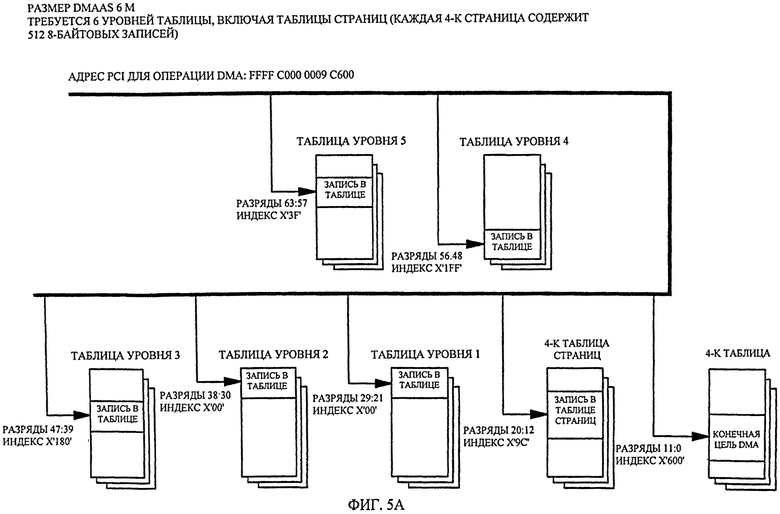

на фиг.5A - один из примеров уровней трансляции, применяемой, когда при индексации в таблицах трансляции адресов используется весь адрес с целью трансляции адреса и доступа к странице,

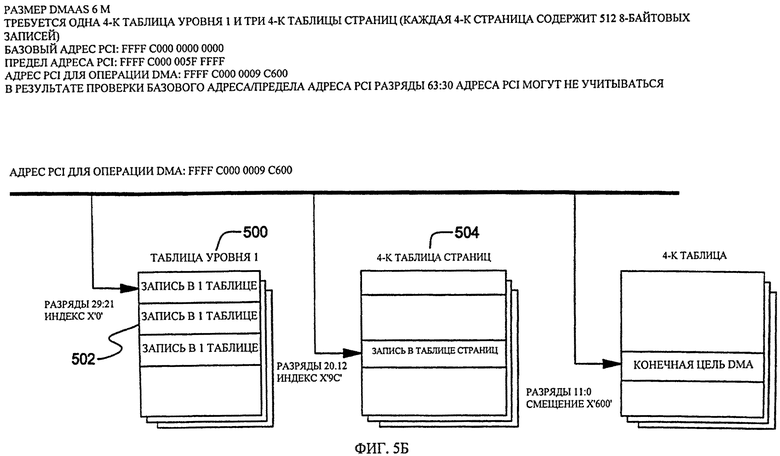

на фиг.5Б - один из примеров уровней трансляции, применяемой, когда при индексации в таблицах трансляции адресов не учитывается часть адреса согласно одной из особенностей настоящего изобретения,

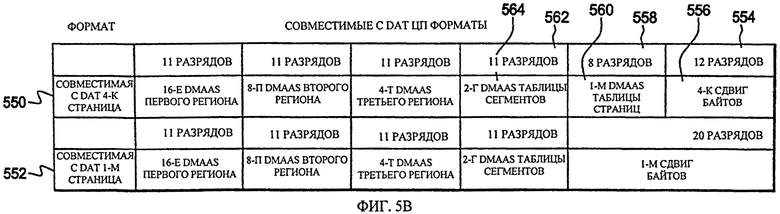

на фиг.5В - примеры различных совместимых с динамической трансляцией адреса (DAT) ЦП форматов, применимых согласно одной или нескольким особенностям настоящего изобретения,

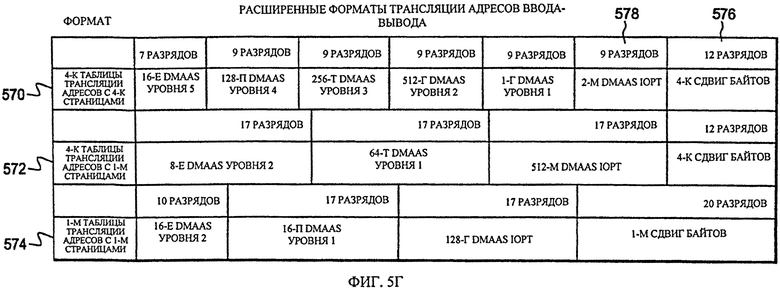

на фиг.5Г - примеры различных расширенных форматов трансляции адреса ввода-вывода, применимых согласно одной или нескольким особенностям настоящего изобретения,

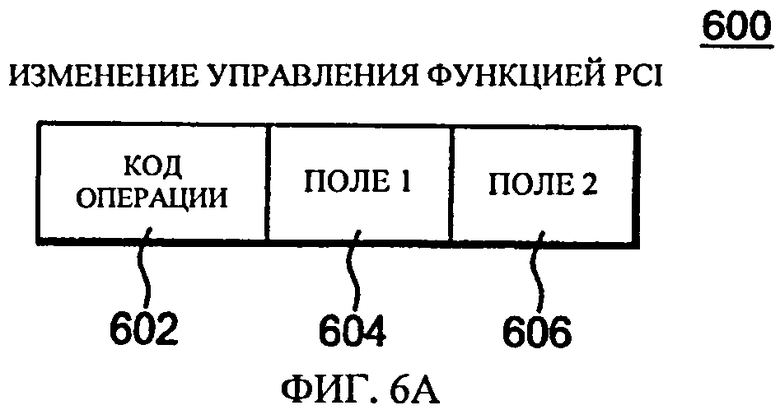

на фиг.6A - один из вариантов осуществления команды изменения управления функцией шины PCI (Modify PCI Function Controls), используемой согласно одной из особенностей настоящего изобретения,

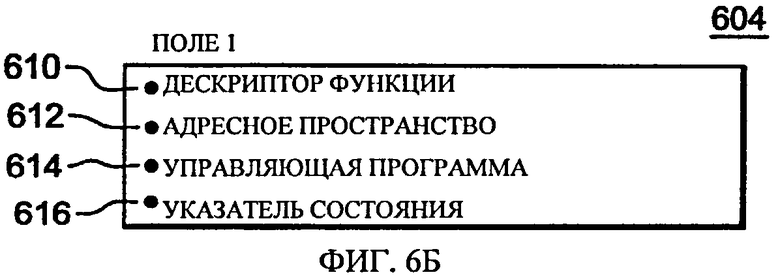

на фиг.6Б - один из вариантов осуществления поля, используемого проиллюстрированной на фиг.6A командой изменения управления функцией шины PCI согласно одной из особенностей настоящего изобретения,

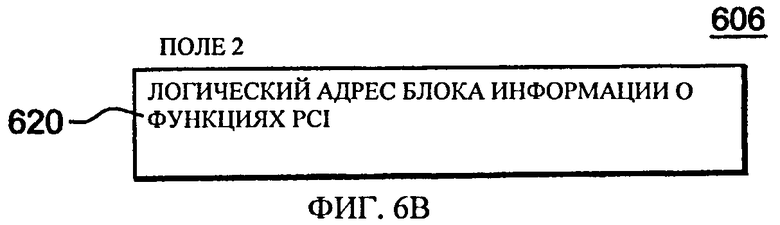

на фиг.6В - один из вариантов осуществления другого поля, используемого проиллюстрированной на фиг.6A командой изменения управления функцией шины PCI согласно одной из особенностей настоящего изобретения,

на фиг.6Г - один из вариантов осуществления содержимого блока информации о функциях (function information block (FIB)), используемого согласно одной из особенностей настоящего изобретения,

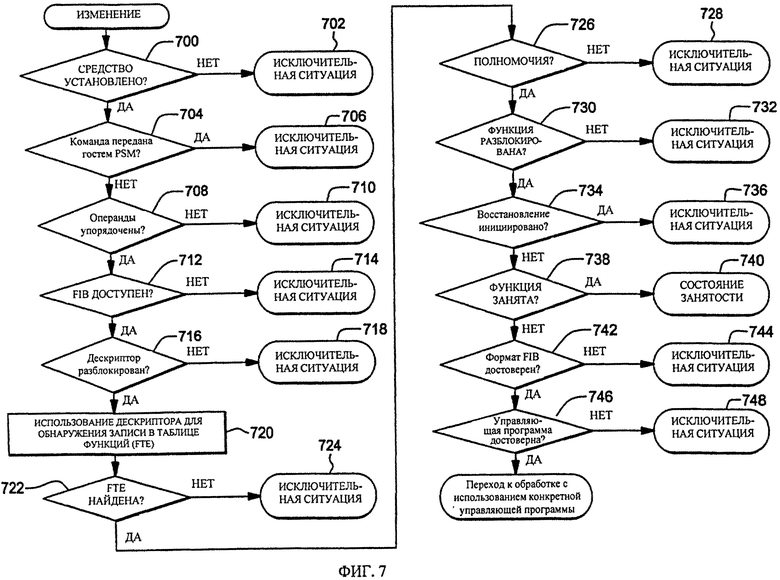

на фиг.7 - один из вариантов осуществления общего представления логики команды изменения управления функцией шины PCI согласно одной из особенностей настоящего изобретения,

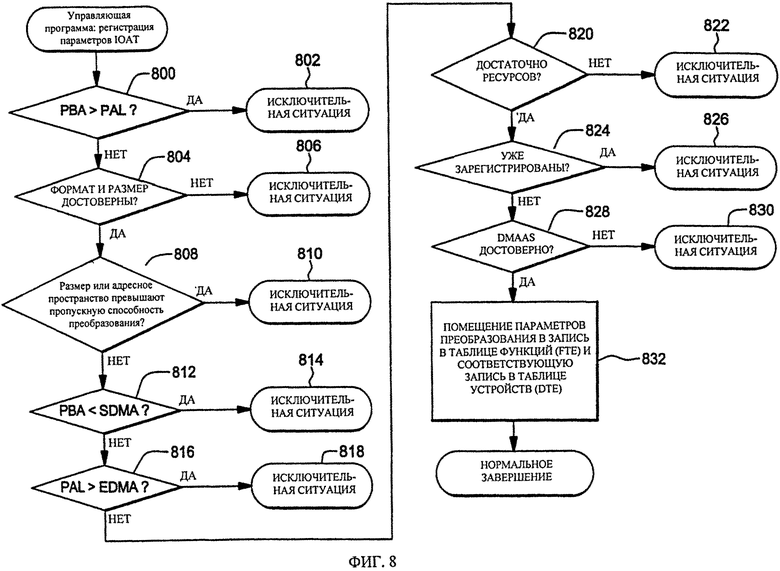

на фиг.8 - один из вариантов осуществления логики, связанной с операцией регистрации параметров трансляции адресов ввода-вывода, которая может быть определена командой изменения управления функцией шины PCI, согласно одной из особенностей настоящего изобретения,

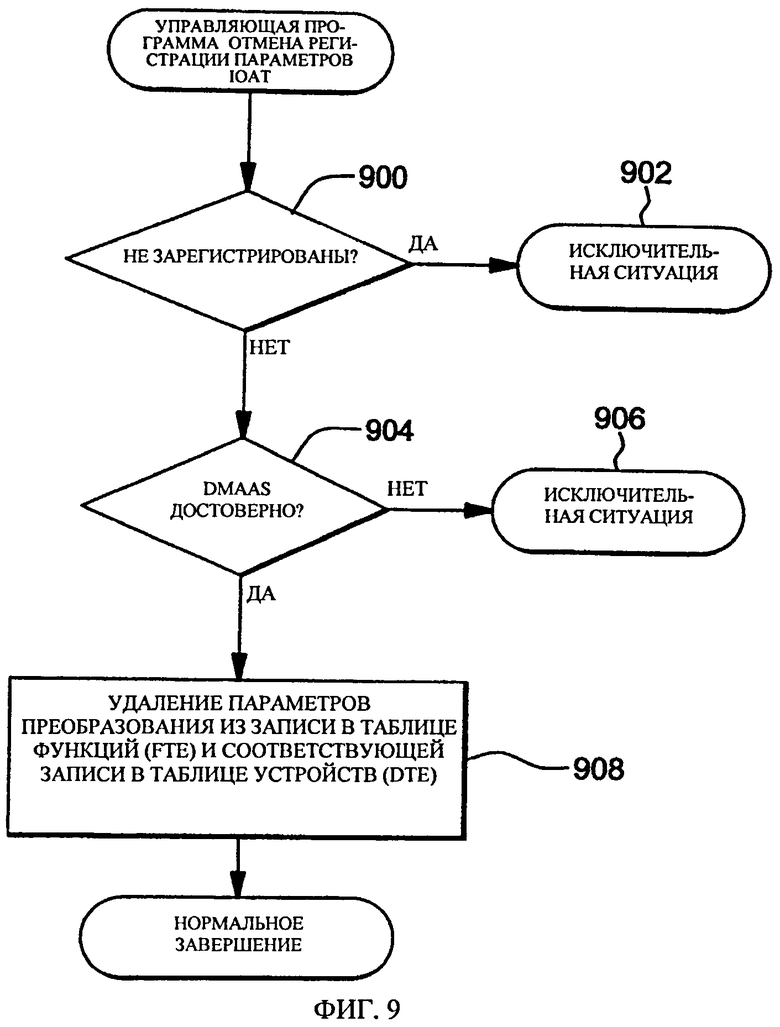

на фиг.9 - один из вариантов осуществления логики, связанной с операцией отмены регистрации параметров трансляции адресов ввода-вывода, которая может быть определена командой изменения управления функцией шины PCI, согласно одной из особенностей настоящего изобретения,

на фиг.10 - один из вариантов осуществления компьютерного программного продукта, в котором содержится одна или несколько особенностей настоящего изобретения,

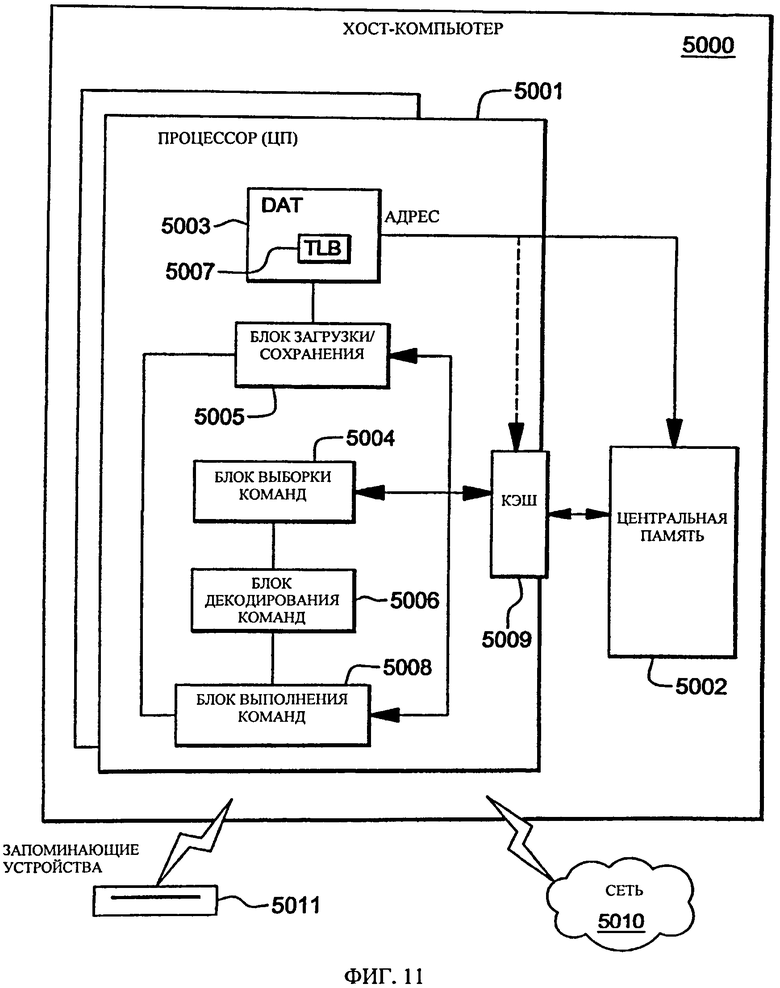

на фиг.11 - один из вариантов осуществления хост-компьютерной системы, в которой содержится и используется одна или несколько особенностей настоящего изобретения,

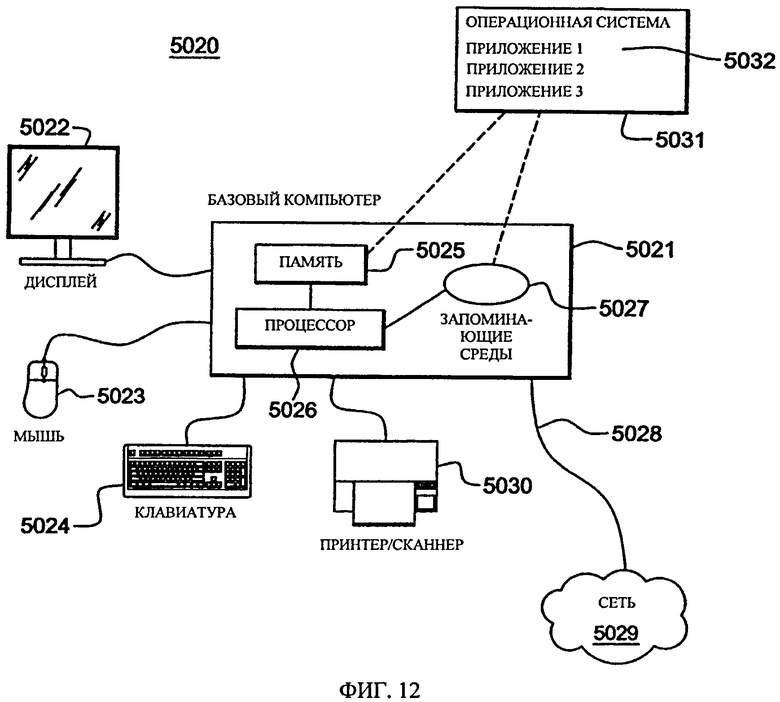

на фиг.12 - один из дополнительных примеров компьютерной системы, в которой содержится и используется одна или несколько особенностей настоящего изобретения,

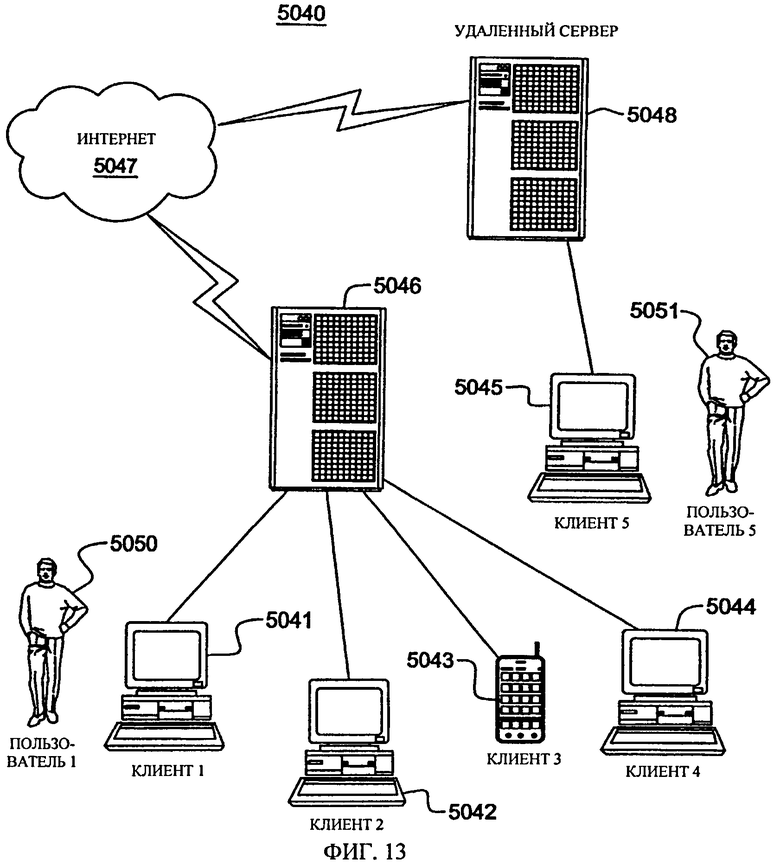

на фиг.13 - другой пример компьютерной системы, представляющей собой компьютерную сеть, в которой содержится и используется одна или несколько особенностей настоящего изобретения,

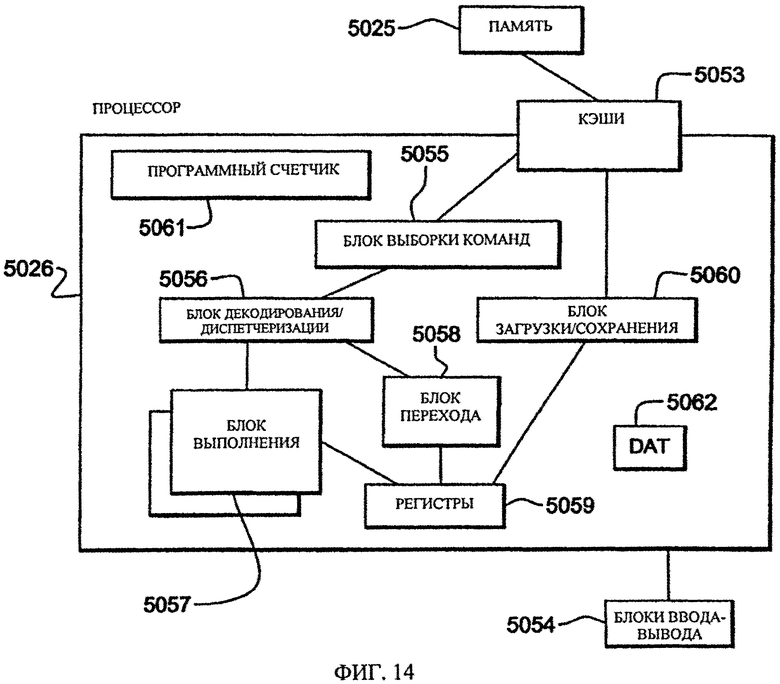

на фиг.14 - один из вариантов осуществления различных элементов компьютерной системы, в которой содержится и используется одна или несколько особенностей настоящего изобретения,

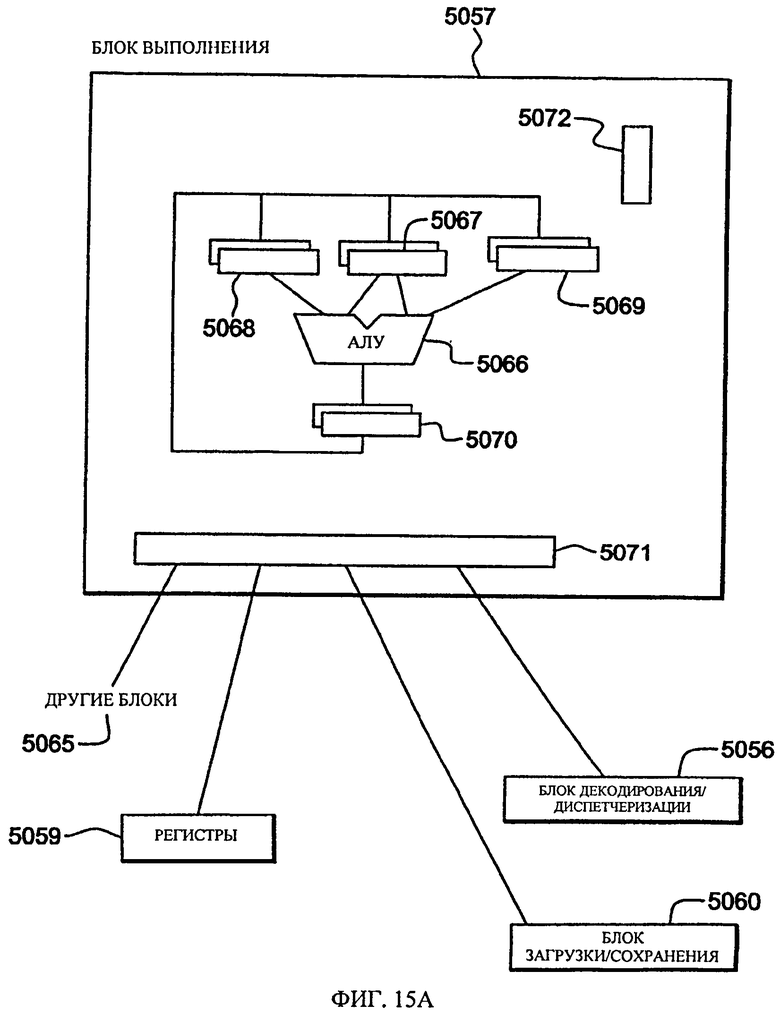

на фиг.15A - один из вариантов осуществления блока выполнения проиллюстрированной на фиг.14 компьютерной системы, в которой содержится и используется одна или несколько особенностей настоящего изобретения,

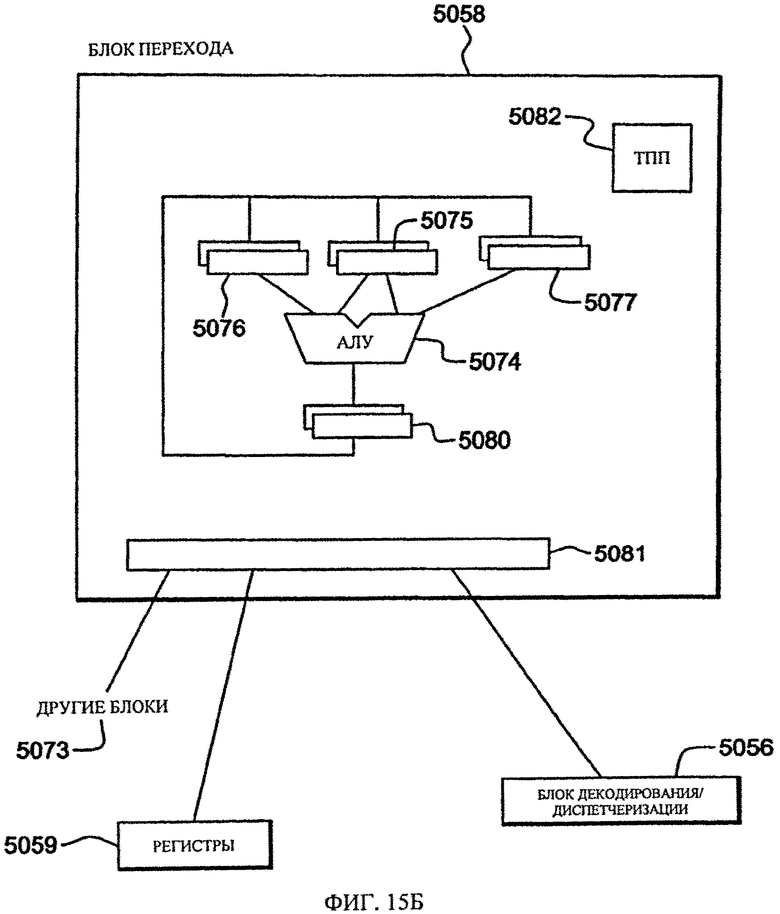

на фиг.15Б - один из вариантов осуществления блока перехода проиллюстрированной на фиг.14 компьютерной системы, в которой содержится и используется одна или несколько особенностей настоящего изобретения,

на фиг.15В - один из вариантов осуществления блока загрузки/сохранения проиллюстрированной на фиг.14 компьютерной системы, в которой содержится и используется одна или несколько особенностей настоящего изобретения, и

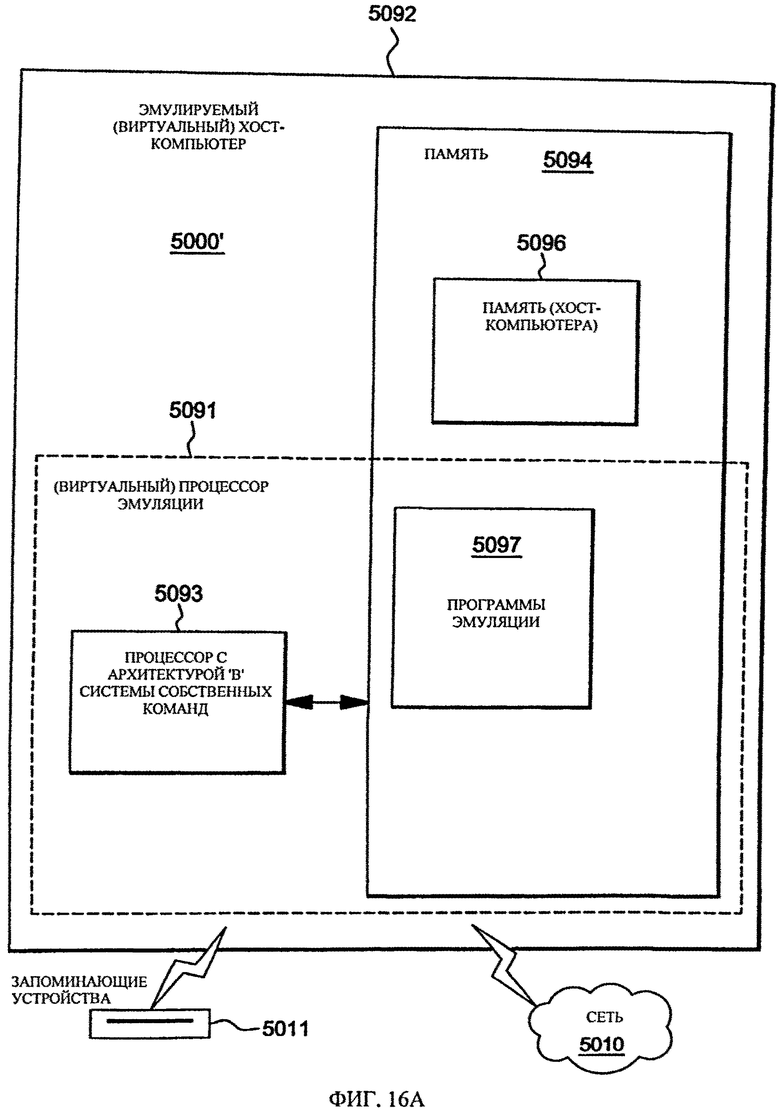

на фиг.16 - один из вариантов осуществления эмулируемой хост-компьютерной системы, в которой содержится и используется одна или несколько особенностей настоящего изобретения.

Подробное описание

Согласно одной из особенностей настоящего изобретения предложено средство трансляции адресов в вычислительной среде. В одном из примеров транслируемыми адресами являются адреса, предоставленные адаптером (называемые в описании адресами ввода-вывода), которые должны быть переведены в адреса, применимые для доступа к системной памяти. Для осуществления трансляции адреса используется несколько уровней трансляции адреса, исходя, например, из размера адресного пространства памяти, присвоенного адаптеру, размера одной или нескольких таблиц трансляции адресов, используемых при трансляции, и/или размера страницы (или другого блока памяти), доступ к которой должен осуществляться.

Транслируемый адрес содержит множество разрядов, и в одном из вариантов осуществления при индексации в таблицах трансляции адресов используется лишь часть этих разрядов с целью получения транслированного адреса. Остальные разряды для трансляции не учитываются. Например, адрес содержит старшие разряды и младшие разряды (в зависимости от размера присвоенного адресного пространства). В этом примере младшие разряды используются для индексации в таблицах трансляции адресов, включая таблицу страниц, и для индексации на самой странице. Старшие разряды (независимо от значения, т.е. нулевые или ненулевые) не учитываются для трансляции и не используются для индексации в таблицах трансляции адресов. За счет этого уменьшается число уровней таблиц трансляции адресов, используемых для трансляции (обозначение младших и старших разрядов не зависит от того, как пронумерованы разряды).

В одном из примеров трансляция осуществляется наряду с обеспечением защиты, применимой для сервера корпоративного класса, такого как сервер System z®. В качестве примера, для доступа к памяти используется полный адрес (например, полный 64-разрядный адрес); однако для трансляции используется только часть адреса. Другая часть адреса, которая для трансляции не учитывается, используется для проверки достоверности (например, проверки попадания в диапазон) наряду по меньшей мере с частью адреса, используемой для трансляции. За счет использования для трансляции только части адреса сводятся к минимуму обращения к таблицам трансляции адресов. Это достигается путем осуществления трансляции нескольких уровней, исходя, например, из размера адресного пространства DMA, зарегистрированного для доступа со стороны адаптера, а не размера самого адреса.

Далее со ссылкой на фиг.1 будет описан один из вариантов осуществления вычислительной среды, в которой содержится и используется одна или несколько особенностей настоящего изобретения. В одном из примеров вычислительной средой 100 является сервер System z®, предлагаемый International Business Machines Corporation. Основой сервера System z® является z/Architecture®, предлагаемая International Business Machines Corporation. Подробности, касающиеся z/Architecture®, описаны в публикации IBM №SA22-7832-07 под названием "z/Architecture-Principles of Operation" (февраль 2009 г.). IBM®, System z® и z/Architecture® являются зарегистрированными товарными знаками International Business Machines Corporation (Армонк, штат Нью-Йорк, США). Другие названия, используемые в заявке, могут являться зарегистрированными товарными знаками, товарными знаками или названиями продуктов International Business Machines Corporation или других компаний.

В одном из примеров вычислительная среда 100 содержит один или несколько центральных процессоров (ЦП) 102, связанных с системной памятью 104 (иначе называемой основной памятью) посредством контроллера 106 памяти. Для доступа к системной памяти 104 центральный процессор 102 выдает запрос чтения или записи, в котором содержится адрес, используемый для доступа к системной памяти. Поскольку адрес, содержащийся в запросе, обычно не может непосредственно использоваться для доступа к системной памяти, он транслируется в адрес, который может непосредственно использоваться для доступа к системной памяти. Адрес транслируется посредством механизма 108 трансляции (XLATE). Например, адрес транслируется из виртуального адреса в действительный или абсолютный адрес с использованием, например, динамической трансляции адресов (DAT).

Запрос, содержащий транслированный адрес, принимается контроллером 106 памяти. В одном из примеров контроллер 106 памяти состоит из аппаратного обеспечения и используется для арбитража при доступе к системной памяти и для обеспечения непротиворечивости памяти. Этот арбитраж осуществляется применительно к запросам, принимаемым от ЦП 102, а также запросам, принимаемым от одного или нескольких адаптеров 110. Подобно центральным процессорам адаптеры выдают в системную память 104 запросы на получение доступа к системной памяти.

В одном из примеров адаптером 110 является адаптер шины межсоединения периферийных компонентов (PCI) или адаптер на основе шины PCI Express (PCIe), содержащей одну или несколько функций шины PCI. Функция шины PCI выдает запрос на доступ к системной памяти. Запрос маршрутизируется в концентратор 112 ввода-вывода (например, концентратор шины PCI) посредством одного или нескольких коммутаторов (например, коммутаторов шины PCIe) 114. В одном из примеров концентратор ввода-вывода состоит из аппаратного обеспечения, включающего один или несколько конечных автоматов.

Используемый в описании термин адаптер означает адаптер любого типа (например, адаптер памяти, сетевой адаптер, адаптер обработки, адаптер на основе шины PCI, криптографический адаптер, адаптеры ввода-вывода другого типа и т.д.). В одном из вариантов осуществления адаптер содержит одну функцию. Тем не менее, в других вариантах осуществления адаптер может содержать множество функций. В зависимости от того, содержит ли адаптер одну функцию или множество функций, применима одна или несколько особенностей настоящего изобретения. Кроме того, в представленных примерах термин адаптер используется взаимозаменяемо с термином функция адаптера (например, функция шины PCI), если не указано иное.

Концентратор ввода-вывода содержит, например, корневой комплекс 116, который принимает запрос от коммутатора. Поскольку в запросе содержится адрес ввода-вывода, подлежащий трансляции, корневой комплекс предоставляет адрес блоку 118 трансляции и защиты адресов. Этим блоком является, например, аппаратный блок, который транслирует адрес ввода-вывода в адрес, непосредственно применимый при доступе к системной памяти 104, как более подробно описано далее.

Инициированный адаптером запрос, содержащий транслированный адрес, предоставляется контроллеру 106 памяти посредством, например, шины 120 ввода-вывода и памяти. Контроллер памяти осуществляет арбитраж и в соответствующее время пересылает системной памяти запрос с транслированным адресом.

Дополнительные подробности, касающиеся системной памяти и концентратора ввода-вывода, описаны со ссылкой на фиг.2. В этом варианте осуществления контроллер памяти не показан. Тем не менее, концентратор ввода-вывода может быть связан с системной памятью напрямую или посредством контроллера памяти. В одном из примеров системная память 104 содержит одно или несколько адресных пространств 200. Адресным пространством является конкретная часть системной памяти, которая присвоена конкретному компоненту вычислительной среды, такому как конкретный адаптер. В одном из примеров адресное пространство доступно путем прямого доступа к памяти (DMA), инициированного адаптером, и, соответственно, в рассматриваемых примерах адресное пространство называется адресным пространством DMA. Тем не менее, в других примерах для доступа к адресному пространству не используется прямой доступ к памяти.

Кроме того, в одном из примеров системная память 104 содержит таблицы 202 трансляции адресов, используемые для трансляции адреса, непосредственно неприменимого для доступа к системной памяти, в непосредственно применимый адрес. В одном из вариантов осуществления адресному пространству DMA присвоена одна или несколько таблиц трансляции адресов, которые сконфигурированы, исходя, например, из размера адресного пространства, которому они присвоены, размера самих таблиц трансляции адресов и/или размера страницы (или другого блока памяти).

В одном из примеров предусмотрена определенная иерархия таблиц трансляции адресов. Например, как показано на фиг.2, предусмотрена таблица 202а первого уровня (например, таблица сегментов), на которую указывает указатель 218 IOAT (описанный далее), и таблица 202b второго, более низкого уровня (например, таблица страниц), на которую указывает запись 206а в таблице первого уровня. Один или несколько разрядов принятого адреса 204 используются для индексации в таблице 202a с целью определения местонахождения конкретной записи 206a, которая указывает на конкретную таблицу 202b низкого уровня. Затем один или несколько других разрядов адреса 204 используются для определения местонахождения конкретной записи 206b в этой таблице. В данном примере эта запись обеспечивает адрес, используемый для определения местонахождения правильной страницы, а дополнительные разряды в адресе 204 используются для определения конкретного местонахождения 208 на странице для осуществления передачи данных. Иными словами, адрес, содержащийся в записи 206b, и выбранные разряды принятого адреса 204 PCI используются для обеспечения адреса, непосредственно применимого для доступа к системной памяти. Например, непосредственно применимый адрес формируется путем конкатенации старших разрядов адреса в записи 206b (например, разрядов 63:12 на 4-килобайтовой странице) и выбранных младших разрядов из принятого адреса шины PCI (например, разрядов 11:0 на 4-килобайтовой странице).

В одном из примеров за присвоение адресного пространства DMA конкретному адаптеру отвечает операционная система. Это присвоение осуществляется посредством процесса регистрации, который приводит к инициализации (например, посредством выверенного программного обеспечения) записи 210 в таблице устройств для этого адаптера. Запись содержится в таблице 211 устройств, находящейся в концентраторе 112 ввода-вывода. Например, таблица 211 устройств находится в блоке трансляции адресов и защиты концентратора ввода-вывода.

В одном из примеров запись 210 в таблице устройств содержит несколько полей, таких как следующие поля:

поле 212 формата: в этом поле содержится множество разрядов для обозначения различной информации, включая, например, формат трансляции адреса (включая уровень) таблицы верхнего уровня из таблиц трансляции адресов (например, таблицы первого уровня в приведенном выше примере);

поле 213 размера страницы: в этом поле указан размер страницы (или другого блока памяти) для доступа;

поле 214 базового адреса шины PCI и поле 216 предела адреса шины PCI: эти значения обеспечивают диапазон, используемый для определения адресного пространства DMA и проверки достоверности принятого адреса (например, адреса шины PCI), и

поле 218 указателя IOAT (трансляции адреса ввода-вывода): в этом поле содержится указатель таблицы трансляции адресов наивысшего уровня, используемой для адресного пространства DMA.

В других вариантах осуществления в DTE может содержаться больше, меньше информации или другая информация.

В одном из вариантов осуществления местоположение записи в таблице устройств для использования при конкретной трансляции определяют с использованием идентификатора запросчика (RID), содержащегося в запросе, выдаваемом функцией 220 шины PCI, соответствующей адаптеру (и/или частью адреса). В запросе содержится идентификатор запросчика (например, 16-разрядное значение, указывающее, например, номер шины, номер устройства и номер функции), а также адрес ввода-вывода (например, 64-разрядный адрес шины PCIe) для использования с целью доступа к системной памяти. Запрос, содержащий RID и адрес ввода-вывода, выдается, например, посредством, коммутатора 114, например, ассоциативной памяти (САМ) 230, которая используется для получения заданного значения. Например, в САМ содержится множество записей, каждая из которых соответствует индексу в таблице устройств. Каждая запись в САМ содержит значение RID. Если, например, принятый RID соответствует значению, содержащемуся в записи в САМ, для определения местоположения записи в таблице устройств используется соответствующий индекс из таблицы устройств. Иными словами, выводимые из CAM данные используются для индексации в таблице 211 устройств с целью определения местоположения записи 210 в таблице устройств. Если соответствие отсутствует, принятый пакет отбрасывается и доступ к системной памяти не осуществляется (в других вариантах осуществления не требуется CAM или другое средство поиска и RID используется в качестве индекса).

Затем поля в записи в таблице устройств используются, чтобы гарантировать достоверность адреса и конфигурацию таблиц трансляции адресов. Например, аппаратное обеспечение концентратора ввода-вывода (например, блок трансляции и защиты адреса) проверяет входящий адрес в запросе, чтобы гарантировать, что он находится в границах, установленных базовым адресом 214 шины PCI и пределом 216 адреса шины PCI, которые хранятся в записи в таблице устройств, обнаруженной с использованием RID запроса, в котором содержался адрес. Тем самым гарантируется, что адрес находится в диапазоне, который был ранее зарегистрирован и для которого достоверно сконфигурированы таблицы трансляции адресов.

Согласно одной из особенностей настоящего изобретения для трансляции адреса ввода-вывода (т.е. адреса, предоставленного адаптером или другим компонентом подсистемы ввода-вывода) в системный адрес ячейки памяти (т.е. адрес, непосредственно применимый при доступе к системной памяти) в одном из вариантов осуществления сначала осуществляется процесс регистрации. В ходе этого процесса регистрации с помощью конкретного запросчика, такого как конкретный адаптер или функция адаптера, регистрируется конкретное адресное пространство. Один из примеров общего представления этого процесса регистрации описан со ссылкой на фиг.3A.

Сначала на шаге 300 операционная система, выполняемая в одном из центральных процессоров, связанных с системной памятью, определяет размер и местоположение адресного пространства, доступ к которому должен осуществить адаптер. В одном из примеров размер адресного пространства определяется на основании базового адреса шины PCI и предела шины PCI, установленных операционной системой. Операционная система определяет базовый адрес и предел с использованием одного или нескольких критериев. Например, если операционная система желает, чтобы адреса шины PCI непосредственно соответствовали виртуальным адресам ЦП, устанавливается базовый адрес и предел как таковые. В одном из дополнительных примеров, если желательно дополнительное разобщение адаптеров и/или образов операционной системы, выбираются используемые адреса, обеспечивающие неперекрывающиеся и раздельные адресные пространства. Местоположение также определяется операционной системой на основании, например, характеристик адаптера.

После этого на шаге 302 создается одна или несколько таблиц трансляции адресов, охватывающих адресное пространство DMA. Например, таблицы могут являться совместимыми с таблицами трансляции адресов ЦП, или может быть предусмотрен уникальный формат, поддерживаемый концентратором ввода-вывода. В одном из примеров создание таблиц включает построение таблиц и помещение соответствующих адресов в записи в таблице. В качестве примера, одной из таблиц трансляции является 4-килобайтовая таблица страниц, содержащая 512 64-разрядных записей, каждая из которых содержит 4-килобайтовый адрес страницы, совместимый с присвоенным адресным пространством.

После этого на шаге 304 регистрируется адресное пространство DMA для адаптера, как подробнее описано со ссылкой на фиг.3Б. Поскольку в этом примере считается, что каждому адаптеру соответствует одна функция шины PCI, каждому адаптеру соответствует один идентификатор запросчика. Логика выполняется, например, центральным процессором, связанным с системной памятью, в ответ на запрос операционной системы.

В одном из вариантов осуществления сначала на шаге 310 выбирается доступная запись в таблице устройств, которая соответствует идентификатору запросчика адаптера. Иными словами, идентификатор запросчика используется для определения местонахождения записи в таблице устройств.

Кроме того, на шаге 312 в записи в таблице устройств сохраняется базовый адрес шины PCI и предел шины PCI. Далее на шаге 314 в записи в таблице устройств также сохраняется формат таблицы трансляции адресов высшего уровня (например, поле формата), а также указатель трансляции адреса ввода-вывода (IOAT), используемый для указания таблицы трансляции адресов высшего уровня. На этом процесс регистрации завершается.

После осуществления регистрации адресное пространство DMA и соответствующие таблицы трансляции адресов, а также запись в таблице устройств готовы к использованию. Подробности обработки запроса, выдаваемого запросчиком, например, с целью получения доступа к системной памяти, описаны со ссылкой на фиг.4. Описанная далее обработка осуществляется концентратором ввода-вывода. В одном из примеров за выполнение логики отвечает блок трансляции и защиты адреса.

В одном из вариантов осуществления сначала на шаге 400 концентратор ввода-вывода принимает запрос DMA. Например, функция шины PCI выдает запрос, который пересылается концентратору шины PCI посредством, например, коммутатора шины PCI. На шаге 402 определяется местоположение соответствующей записи в таблице устройств с использованием идентификатора запросчика, содержащегося в запросе. После этого на шаге 404 проверяется, достоверна ли запись в таблице устройств. В одном из примеров достоверность проверяется путем проверки разряда достоверности в самой записи. Этот разряд устанавливается, например, в результате выполнения операционной системой запроса разрешения функции. Если функция разрешена, значение разряда приравнивается, например, к единице (т.е. он является достоверным); в противном случае его значение остается нулевым (т.е. недостоверным). В одном из дополнительных примеров значение разряда может быть установлено после завершения процесса регистрации.

Если запись в таблице устройств является недостоверной, на шаге 405 отображается ошибка. В противном случае на шаге 406 дополнительно определяется, имеет ли адрес шины PCI, содержащийся в запросе, меньшую длину, чем базовый адрес шины PCI, хранящийся в записи в таблице устройств. Если это так, адрес находится вне достоверного диапазона и на шаге 407 сообщается об ошибке. Тем не менее, если длина адреса шины PCI больше или равна длине базового адреса, на шаге 408 дополнительно определяется, не превышает ли длина адреса шины PCI предельное значение шины PCI в записи в таблице устройств. Если длина адреса шины PCI превышает предельное значение, на шаге 409 снова отображается ошибка, поскольку адрес находится вне достоверного диапазона. Тем не менее, если адрес находится в пределах достоверного диапазона, обработка продолжается.

В одном из примеров формат, содержащийся в записи в таблице устройств, используется на шаге 410 для определения разрядов адреса шины PCI в адресе для использования с целью трансляции адреса. Например, если в формате указано, что таблице верхнего уровня является таблица первого уровня, содержащая 4-килобайтовые страницы, для индексации в таблице первого уровня используются разряды 29:21 адреса; для индексации в таблице страниц используются разряды 20:12; а для индексации на 4-килобайтовой странице используются разряды 11:0. Используемые разряды зависят от того, сколько разрядов необходимо для индексации на странице или в таблице заданного размера. Например, в случае 4-килобайтовой страницы с байтовой адресацией для адресации 4096 байтов используется 12 разрядов; а в случае 4-килобайтовой таблицы страниц с 512 записями по 8 байтов каждая для адресации 512 записей используется 9 разрядов и т.д.

Затем на шаге 412 концентратор шины PCI осуществляет выборку соответствующей записи из таблицы трансляции адресов. Например, сначала с использованием указателя IOАТ записи в таблице устройств определяется местоположение таблицы трансляции наивысшего уровня. Затем разряды адреса (следующие за старшими разрядами, используемыми для проверки достоверности, а не для трансляции; например, разрядами 29:21 в приведенном выше примере) используются для определения местоположения конкретной записи в этой таблице.

Далее на основании, например, формата, содержащегося в записи в таблице устройств, на шаге 414 запроса определяется, имеет ли обнаруженная запись трансляции адреса правильный формат. Например, формат в записи в таблице устройств сравнивается с форматом, указанным в записи трансляции адреса. Если они совпадают, формат в записи в таблице устройств является достоверным. Если нет, на шаге 415 сообщается об ошибке; в противном случае обработка продолжается и на шаге 416 запроса определяется, является эта таблица последней для обработки. Иными словами, определяется, существуют ли другие таблицы трансляции адресов, необходимые для получения действительного или абсолютного адреса, или была ли обнаружена запись в таблице низшего уровня. Это определяется на основании известного формата и размера уже обработанных таблиц. Если таблица не является последней, обработка продолжается на шаге 412. В противном случае концентратор ввода-вывода продолжает обработку на шаге 418, чтобы обеспечить выборку или сохранение данных с использованием транслированного адреса. В одном из примеров концентратор ввода-вывода пересылает транслированный адрес контроллеру памяти, который использует его для выборки или сохранения данных в местоположении DMA, указанном в транслированном адресе.

Как описано выше, согласно одной из особенностей настоящего изобретения уменьшается число уровней трансляции и, соответственно, число выборок, необходимых для осуществления трансляции. Это достигается, например, за счет того, что во время трансляции не учитываются старшие разряды адреса, и для прохождения таблиц трансляции используются только младшие разряды, основанные, например, на размере адресного пространства DMA, присвоенного адаптеру. Использование части адреса, а не полного адреса дополнительно рассмотрено в следующих далее примерах.

На фиг.5A проиллюстрирован один из примеров, в котором при трансляции адреса/доступе к памяти используется полный адрес. Согласно этому известному подходу требуются таблицы трансляции шести уровней, включая таблицу страниц. Указатель IOAT указывает начало таблицы высшего уровня (например, таблицы уровня 5 в этом примере), а затем для определения местонахождения записи в таблице используются разряды адреса шины PCI. Каждая запись в таблице трансляции указывает начало таблицы трансляции более низкого уровня или страницу (например, запись в таблице уровня 5 указывает начало таблицы уровня 4 и т.д.)

В этом примере размер адресного пространства DMA (DMAAS) составляет 6 мегабайт, а каждая таблица имеет размер 4 килобайта и содержит максимально 512 8-байтовых записей (за исключением таблицы уровня 5, которая содержит 128 записей с учетом размера адреса). Адрес содержит, например, 64 разряда: FFFF С000 0009 С600. Указатель IOAT указывает начало таблицы уровня 5, а разряды 63:57 адреса шины PCI используются для индексации в таблице уровня 5 с целью определения местоположения начала таблицы уровня 4; разряды 56:48 адреса шины PCI используются для индексации в таблице уровня 4 с целью определения местоположения начала таблицы уровня 3; разряды 47:39 используются для индексации в таблице уровня 3 с целью определения местоположения начала таблицы уровня 2; разряды 38:30 используются для индексации в таблице уровня 2 с целью определения местоположения начала таблицы уровня 1; разряды 29:21 используются для индексации в таблице уровня 1 с целью определения местоположения начала таблицы страниц; разряды 20:12 используются для индексации в таблице страниц с целью определения местоположения начала страницы; и разряды 11:0 используются с целью определения местоположения записи на 4-килобайтовой странице. Таким образом, в этом примере при трансляции/доступе используются все разряды адреса.

В отличие от этого в примере, проиллюстрированном на фиг.5Б, адресное пространство имеет такой же размер (например, 6 мегабайт), а адрес имеет такую же длину, но для трансляции не учитываются некоторые разряды адреса. В этом примере для трансляции не учитываются разряды 63:30 адреса. Указатель IOАТ указывает начало таблицы уровня 1, а разряды 29:21 адреса шины PCI используются для индексации в таблице уровня 1 с целью определения местоположения начала таблицы страниц; разряды 20:12 используются для индексации в соответствующей таблице страниц с целью определения местоположения начала страницы; и разряды 11:0 используются для индексации на 4-килобайтовой странице.

Как показано, таблица 500 уровня 1 содержит три записи 502, в каждой из которых указан адрес одной из трех таблиц 504 страниц. Необходимое число таблиц страниц и, соответственно, число таблиц других уровней зависит, например, от размера адресного пространства DMA, размера таблиц трансляции и/или размера страниц. В этом примере адресное пространство DMA составляет 6 мегабайт, а каждая таблица страниц имеет размер 4 килобайта и содержит до 512 записей. Соответственно, каждая таблица страниц способна отображать до 2 мегабайт памяти (4 килобайта × 512 записей). Таким образом, для отображения 6-мегабайтного адресного пространства требуются три таблицы страниц. В таблице уровня 1 может содержаться три записи, по одной для каждой таблицы страниц, и, соответственно, в этом примере не требуются таблицы трансляции адресов дополнительных уровней.

В одном из дополнительных вариантов осуществления для трансляции адреса могут использоваться таблицы трансляции адресов отличающихся форматов, и могут быть предусмотрены разновидности форматов. Так, предусмотрены разновидности разрядов, используемых для индексации в конкретной таблице или странице. Некоторые из этих примеров описаны со ссылкой на фиг.5В и 5Г.

Например, одним из форматов является совместимый с DAT ЦП формат, в котором таблицы трансляции совместимы с таблицами трансляции, используемыми для динамического трансляции адресов ЦП. Могут существовать различные совместимые с DAT ЦП форматы, примеры которых описаны со ссылкой на фиг.5В. Как показано в качестве примеров, одним из совместимых с DAT ЦП форматов является совместимый с DAT ЦП формат 550 4-килобайтовой страницы DAT ЦП, а другим форматом является совместимый с DAT ЦП формат 552 1-мегабайтовой страницы. Числом показанных разрядов является число разрядов адреса, используемых для индексации на этой странице или таблице (или иначе для определения местоположения записи на этой странице или таблице). Например, 12 разрядов 554 адреса шины PCI используются для индексации на 4-килобайтовой странице 556; 8 разрядов 558 используются для индексации в таблице 560 страниц; 11 разрядов 562 используются для индексации в таблице 564 сегментов и т.д. В указанной таблице трансляции адресов представлен максимальный размер адресного пространства, поддерживаемый этой таблице трансляции адресов. Например, таблица 560 страниц поддерживает 1-мегабайтное адресное пространство DMA; таблица 564 сегментов поддерживает 2-гигабайтное адресное пространство DMA и т.д. На фиг.5 В, а также на фиг.5Г К означает килобайты, М - мегабайты, Г - гигабайты, Т - терабайты, П - петабайты, а Э - эксабайты.

Показано, что с увеличением размера страницы увеличивается число уровней таблиц трансляции. Например, таблица страниц требуется в случае 4-килобайтовой страницы 556, но не требуется в случае 1-мегабайтовой страницы. Возможны другие примеры и разновидности.

Другим форматом трансляции адреса является расширенный формат трансляции адреса ввода-вывода, в котором используются расширенные таблицы трансляции адресов. На фиг.5Г проиллюстрированы различные примеры расширенных форматов ввода-вывода трансляции адреса. Например, показаны следующие форматы: 4-килобайтовая таблица трансляции адресов с 4-байтовыми страницами 570; 1-мегабайтовая таблица трансляции адресов с 4-байтовыми страницами 572; и 1-мегабайтовая таблица трансляции адресов с 1-мегабайтовыми страницами 574. Как и в случае совместимых с DAT ЦП форматов, в число перечисленных разрядов входят разряды, используемые для определения местоположения записи в конкретной таблице. Например, позицией 576 обозначено 12 разрядов, которые используются для индексации на 4-килобайтовой странице. Аналогичным образом, позицией 578 обозначено 9 разрядов, которые используются для индексации в таблице страниц ввода-вывода. Эта таблица страниц ввода-вывода рассчитана на адресное пространство DMA размером 2 мегабайта. Существует множество других примеров.

В одном из конкретных вариантов осуществления для осуществления регистрации адресного пространства DMA для адаптера используется команда, называемая командой изменения управления функцией шины PCI (Modify PCI Function Controls) (MPFC)). Например, операционная система определяет, какой формат трансляции адреса желательно использовать, создает таблицы трансляции адресов для этого формата, а затем выдает команду MPFC, в которой этот формат содержится в качестве операнда команды. В одном из примеров формат и другие операнды команды содержатся в блоке информации о функциях (описанном далее), который является операндом команды. Затем блок информации о функциях используется для обновления DTE, а в одном из вариантов осуществления необязательно записи в таблице функций (РТЕ), в которой содержатся рабочие параметры адаптера.

Далее со ссылкой на фиг.6A-9 описан один из вариантов осуществления подробностей, касающихся этой команды, в частности процесса регистрации. Как показано на фиг.6A, команды 600 изменения управления функцией шины PCI содержит, например, код 602 операции, указывающий команду изменения управления функцией шины PCI; первое поле 604, указывающее местоположение, в котором находится различная информация, касающаяся функции адаптера, для которой устанавливаются рабочие параметры; и второе поле 606, указывающее местоположение, из которого осуществляется выборка блока информации о функциях шины PCI (FIB). Содержимое местоположений, указанных в полях 1 и 2, дополнительно описано далее.

В одном из вариантов осуществления в поле 1 указан общий регистр, в котором содержится различная информация. Как показано на фиг.6Б, в содержимом регистре содержится, например, дескриптор 610 функции, который идентифицирует функцию адаптера, от имени которого выполняется команда изменения; адресное пространство 612, указывающее адресное пространство в системной памяти, соответствующее функции адаптера, указанной дескриптором функции; управляющая программа 614, который определяет операцию, выполняемую для функции адаптера; и указатель 616 состояния, который указывает состояние команды при ее выполнении с использованием заданного кода.

В одном из вариантов осуществления дескриптор функции содержит, например, разрешающий индикатор, указывающий, активирован ли дескриптор, номер функции, указывающий функцию адаптера (это статический идентификатор, который может использоваться для индексации в таблице функций); и номер экземпляра, указывающий конкретный экземпляр этого дескриптора функции. Для каждой функции адаптера предусмотрен один дескриптор функции, который используется для определения местоположения записи в таблице функций (FTE). Каждая запись в таблице функций содержит рабочие параметры и/или другую информацию, связанную с функцией адаптера. В качестве одного из примеров, запись в таблице функций содержит:

номер экземпляра: в этом поле указан конкретный экземпляр дескриптора функции адаптера, соответствующий записи в таблице функций;

индекс 1…n записи в таблице устройств (DTE): может существовать один или несколько индексов таблицы устройств, каждым из которых является индекс в таблице устройств для определения местоположения записи в таблице устройств (DTE). Для каждой функции адаптера существует одна или несколько записей в таблице устройств, каждая из которых содержит информацию, связанную с функцией адаптера, включая информацию, используемую для обработки запросов функции адаптера (например, запросов DMA, запросов MSI), и информацию, касающуюся запросов, связанных с функцией адаптера (например, команд шины PCI). Каждой записи в таблице устройств соответствует одно адресное пространство в системной памяти, присвоенное функции адаптера. Функция адаптера может иметь одно или несколько адресных пространств в системной памяти, присвоенных функции адаптера;

индикатор занятости: в этом поле указано, занята ли функция адаптера;

индикатор состояния постоянной ошибки: в этом поле указано, находится ли функция адаптера в состоянии постоянной ошибки;

индикатор инициированного восстановления: в этом поле указано, инициировано ли восстановление для функции адаптера;

индикатор полномочий: в этом поле указано, имеет ли операционная система, пытающаяся управлять функцией адаптера, полномочия для этого;

разрешающий индикатор: в этом поле указано, разрешена ли функция адаптера (например, 1 = разрешена, 0 = заблокирована);

идентификатор запросчика (RID): это - идентификатор функции адаптера, содержащий, например, номер шины, номер устройства и номер функции.

В одном из примеров это поле используется для доступа к конфигурационному пространству функции адаптера (память адаптера может быть определена как адресные пространства, содержащие, например, конфигурационное пространство, область ввода-вывода и/или одну или несколько областей памяти). В одном из примеров доступ к конфигурационному пространству может осуществляться путем указания конфигурационного пространства в команде, которую операционная система (или другая конфигурация) передает функции адаптера. В команде указано смещение в конфигурационном пространстве и дескриптор функции, используемый для определения местоположения соответствующей записи в таблице функций, которая содержит RID. Аппаратно-программное обеспечение принимает команду и определяет, что она предназначена для конфигурационного пространства. Соответственно, для генерирования запроса концентратору ввода-вывода используется RID, а концентратора ввода-вывода создает запрос для доступа к адаптеру. Местоположение функции адаптера определяется на основании RID, а смещение определяет смещение в конфигурационном пространстве функции адаптера.

В контексте настоящего изобретения аппаратно-программное обеспечение содержит, например, микрокод, милликод и/или макрокод процессора. Оно содержит, например, команды аппаратного уровня и/или структуры данных, используемые при реализации высокоуровневого машинного кода. В одном из вариантов осуществления оно содержит, например, собственный код, который обычно представляет собой микрокод, содержащий выверенное программное обеспечение или характерный для базового аппаратного обеспечения и управляющий доступом операционной системы к аппаратному обеспечению системы.

Индексный регистр (BAR) (1-n): в этом поле содержится множество целых чисел без знака, обозначаемых как BAR0-BARn и соответствующих первоначально заданной функции адаптера, при этом их значения также хранятся в индексных регистрах, соответствующих функции адаптера. В каждом BAR указан начальный адрес области памяти или области ввода-вывода в функции адаптера, а также указан тип адресного пространства, то есть является ли оно, например, 64- или 32-разрядной областью памяти или 32-разрядной областью ввода-вывода.

В одном из примеров он используется для доступа к области памяти и/или области ввода-вывода функции адаптера. Например, смещение, указанное в команде доступа функции адаптера, суммируется со значением в индексном регистре, соответствующем адресному пространству, указанному в команде, чтобы получить адрес для использования с целью доступа к функции адаптера. Идентификатор адресного пространства, содержащийся в команде, идентифицирует адресное пространство в функции адаптера для доступа и соответствующий BAR для использования.

Размер 1…n: в этом поле содержится множество целых чисел без знака, обозначаемых как SIZE0-SIZEn. Значение поля размера, когда оно является ненулевым, отображает размер каждого адресного пространства, при этом каждая запись соответствует ранее описанному BAR.

Далее описаны дополнительные подробности, касающиеся поля BAR и поля размера.

1. Когда для функции адаптера не реализован BAR, значение поля BAR и значение соответствующего ему поля размера в обоих случаях сохраняются как нулевые.

2. Когда в поле BAR представлено пространство адресов ввода-вывода или 32-разрядное адресное пространство памяти, значение соответствующего поля размера является ненулевым и отображает размер адресного пространства.

3. Когда в поле BAR представлено 64-разрядное адресное пространство памяти:

а) в поле BARn представлены младшие разряды адреса;

б) в следующем по порядку поле BARn+1 представлены старшие разряды адреса;

в) значение соответствующего поля SIZEn является ненулевым и отображает размер адресного пространства;

г) значение соответствующего поля SIZEn+1 не является значащим и сохраняется как нулевое.

Информация о внутренней маршрутизации: эта информация используется для осуществления конкретной маршрутизации до адаптера. Она содержит, например, информацию об узлах, микросхемах процессора и адресации концентратора.

Указатель состояния: указывает, например, заблокированы ли операции загрузки/сохранения или находится ли адаптер в состоянии ошибки, а также содержит другую информацию.

В одном из примеров индикатор занятости, индикатор состояния постоянной ошибки и индикатор инициированного восстановления устанавливаются на основании мониторинга, осуществляемого аппаратно-программным обеспечением. Кроме того, индикатор полномочий устанавливается, например, на основании политики; а информация BAR основана на информации о конфигурации, обнаруженной во время прохода шины процессором (например, аппаратно-программным обеспечением процессора). Значения полей могут устанавливаться на основании конфигурации, инициализации и/или событиях. В других вариантах осуществления запись в таблице функций может содержать больше, меньше информации или другую информацию. Включаемая информация может зависеть от операций, поддерживаемых или обеспечиваемых функцией адаптера.

Как показано на фиг.6B, в одном из примеров в поле 2 указан логический адрес 620 блока информации о функциях шины PCI (FIB), в котором содержится информация, касающаяся соответствующей функции адаптера. Блок информации о функциях используется для обновления записи в таблице устройств и/или записи в таблице функций (или другом местоположении), связанной с функцией адаптера. Во время инициализации и/или конфигурирования адаптера информация хранится в FIB и/или зависит от конкретных событий.

Дополнительные подробности, касающиеся блока информации о функциях (FIB), описаны со ссылкой на фиг.6Г. В одном из вариантов осуществления блок 650 информации о функциях содержит следующие поля.

Поле 651 формат: в этом поле указан формат FIB.

Поле 652 управления перехватом: это поле используется, чтобы указывать, приводит ли выполнение конкретных команд гостем со страничной организацией к перехвату команд.

Поле 654 указания ошибки: в этом поле содержится указательный разряд состояния ошибки при прямом доступе к памяти и адаптерных прерываниях. Когда установлено значение разряда (например, 1), обнаруживается одна или несколько ошибок во время прямого доступа к памяти или адаптерного прерывания функции адаптера.

Поле 656 блокирования загрузки/сохранения: в этом поле указано, заблокированы ли операции загрузки/сохранения.

Контрольное 658 поле функция шины PCI: в этом поле содержится программа, разрешающая функцию адаптера. Когда установлено значение разряда (например, 1), считается, что функция адаптера разрешена для выполнения операций ввода-вывода.

Поле 660 регистрации адресного пространства: в этом поле содержится программа, разрешающая функции адаптера прямой доступ к памяти. Когда установлено значение разряда (например, 1), разрешается прямой доступ к памяти.

Поле 661 размера страницы: в этом поле указан размер страницы или другого блока памяти для доступа посредством DMA.

Поле 662 базового адреса шины PCI (РВА): в этом поле содержится базовый адрес для адресного пространства, присвоенного функции адаптера в системной памяти. Он представляет собой низший виртуальный адрес, который разрешено использовать функции адаптера с целью доступа в заданном адресном пространстве DMA.

Предел 664 адреса шины PCI (PAL): в этом поле указан высший виртуальный адрес, который разрешено использовать функции адаптера с целью доступа в заданном адресном пространстве DMA.

Поле 666 указателя трансляции адреса ввода-вывода (IOAT) 666: указатель трансляции адреса ввода-вывода указывает первую из любых таблиц трансляции, используемых для трансляции виртуального адреса шины PCI, или он может непосредственно указывать получаемый в результате трансляции абсолютный адрес кадра запоминающего устройства.

Поле 668 подкласса прерываний (ISC): в этом поле содержится подкласс прерываний, используемый для представления адаптерных прерываний функции адаптера.

Поле 670 числа прерываний (NOI): в этом поле указано число отдельных кодов прерывания, допустимых для функции адаптера. В этом поле также указан размер в разрядах вектора разрядов адаптерного прерывания, который указан в поле адреса вектора разрядов адаптерного прерывания и в полях смещения вектора разрядов адаптерного прерывания.

Поле 672 адреса вектора разрядов адаптерного прерывания (AIBV): в этом поле указан адрес вектора разрядов адаптерного прерывания для функции адаптера. Этот вектор используется при обработке прерываний.

Поле 674 смещения в векторе разрядов адаптерного прерывания: в этом поле указано смещение первого разряда в векторе разрядов адаптерного прерывания для функции адаптера.

Поле 676 адреса суммарного разряда адаптерного прерывания (AISB): в этом поле содержится адрес, указывающий суммарный разряд адаптерного прерывания, который необязательно используется при обработке прерываний.

Поле 678 смещения суммарного разряда адаптерного прерывания: в этом поле указано смещение в векторе суммарных разрядов адаптерного прерывания.

Поле 680 адреса блока вычислений функции (FMB): в этом поле содержится адрес блока вычислений функции, используемого для сбора данных, касающихся функции адаптера.

Поле 682 ключа блока вычислений функции: в этом поле содержится ключ доступа к блоку вычислений функции.

Поле 684 управления уведомлением о суммарных разрядах: в этом поле указано, используется ли вектор суммарных разрядов.

Поле 686 маркера авторизации команд: это поле используется, чтобы определять, уполномочен ли гость со страничной организацией режима записи в память выполнять команды шины PCI без вмешательства хоста.

В одном из примеров в системе z/Architecture® посредством команды начала выполнения в режиме интерпретации (Start Interpretive Execution) (SIE) в режиме интерпретации на уровне 2 выполняется гостевая программа со страничной организацией. Например, гипервизор логического разбиения (LPAR) выполняет команду SIE, чтобы начать логическое разбиение в физической постоянной памяти. Если операционной системой при этом логическом разбиении является z/VM®, она передает команду выполнения в режиме интерпретации (SIE) программ своих гостевых (виртуальных) машин в своем V=V (виртуальном) запоминающем устройстве. Соответственно, гипервизор LPAR использует SIE уровня 1, а гипервизор z/VM® использует SIE уровня 2.

Поле 687 формата трансляции адреса: в этом поле указан формат трансляции адреса, выбранный из таблицы трансляции высшего уровня, для использования при трансляции (например, указана таблица высшего уровня (например, таблица сегментов, 3-я область и т.д.)).

Блок информации о функциях, указанный в команде изменения управления функцией шины PCI, используется для изменения выбранной записи в таблице устройств, записи в таблице функций и/или других аппаратно-программных средств управления, соответствующих функции адаптера, указанной в команде. Путем изменения записи в таблице устройств, записи в таблице функций и/или других аппаратно-программных средств управления адаптеру предоставляются определенные услуги. Эти услуги включают, например, адаптерные прерывания; трансляции адреса; переустановку состояния ошибки; переустановку поля блокирования загрузки/сохранения; установку параметров вычислений функции; и установку управления перехватом.

Далее со ссылкой на фиг.7 описан один из вариантов осуществления логики, соответствующей команде изменения управления функцией шины PCI. В одном из примеров команда передается операционной системой (или другой конфигурацией) и выполняется процессором (например, аппаратно-программным обеспечением), выполняющим операционную систему. В проиллюстрированных примерах команда и функции адаптера основаны на шине PCI. Тем не менее, в других примерах может использоваться отличающаяся архитектура адаптера и соответствующие команды.

В одном из примеров в операционной системе содержатся следующие операнды команды (например, в одном или нескольких регистрах, указанных командой): дескриптор функции шины PCI; идентификатор адресного пространства DMA; управляющая программа; и адрес блока информации о функциях.

Как показано на фиг.7, сначала на шаге 700 запроса определяется, установлено ли средство, рассчитанное на команду изменения управления функцией шины PCI. Это определяется, например, путем проверки индикатора, хранящегося, например, в блоке управления. Если средство не установлено, на шаге 702 распознается исключительная ситуация. В противном случае на шаге 704 запроса определяется, была ли передана команда гостем со страничной организацией режима записи в память (PSM) (или другим гостем). Если это так, на шаге 706 операционная хост-система будет эмулировать работу этого гостя.

В противном случае на шаге 708 запроса определяется, упорядочен один или несколько из операндов. Например, определяется, находится ли адрес блока информации о функциях на границе двойного слова. В одном из примеров это необязательно. Если операнды не упорядочены, на шаге 710 распознается исключительная ситуация. В противном случае на шаге 712 запроса определяется, доступен ли блок информации о функциях (FIB). Если это не так, на шаге 714 распознается исключительная ситуация. В противном случае на шаге 716 запроса определяется, разблокирован ли дескриптор, содержащийся в операндах команды изменения управления функцией шины PCI. В одном из примеров это определяется путем проверки разрешающего индикатора в дескрипторе. Если дескриптор не разблокирован, на шаге 718 распознается исключительная ситуация.

Если дескриптор разблокирован, на шаге 720 дескриптор используется для определения местоположения записи в таблице функций. Иными словами, по меньшей мере часть дескриптора используется в качестве индекса в таблице функций с целью определения местоположения записи в таблице функций, соответствующей функции адаптера, для которой должны быть установлены рабочие параметры.

На шаге 722 запроса определяется, найдена ли запись в таблице функций. Если это не так, на шаге 724 распознается исключительная ситуация. В противном случае, если на шаге 726 запроса определено, что конфигурацией, передающей команду, является гость, на шаге 728 распознается исключительная ситуация (например, прерывание на хосте). Этот запрос может не учитываться, если конфигурацией не является гость, или могут проверяться другие полномочия, если они указаны.

Далее на шаге 730 запроса определяется, разблокирована ли функция. В одном из примеров это определяется путем проверки разрешающего индикатора в записи в таблице функций. Если она не разблокирована, на шаге 732 распознается исключительная ситуация.

Если функция разблокирована, на шаге 734 запроса определяется, инициировано ли восстановление. Если восстановление инициировано, на что указывает индикатор восстановления в записи в таблице функций, на шаге 736 распознается исключительная ситуация. Тем не менее, если восстановление не инициировано, на шаге 738 запроса дополнительно определяется, занята ли функция. Это определяется путем проверки индикатора занятости в записи в таблице функций. Если функция занята, на шаге 740 распознается состояние занятости. В случае состоянии занятости вместо отбрасывания команды может быть повторена попытка ее выполнения.

Если функция не занята, на шаге 742 запроса дополнительно определяется, достоверен ли формат блока информации о функциях. Например, проверяется поле формата FIB, чтобы определить, поддерживается ли формат системой. Если он недостоверен, на шаге 744 распознается исключительная ситуация. Если формат блока информации о функциях достоверен, на шаге 746 запроса дополнительно определяется, достоверна ли управляющая программа, указанная в операндах команды. Иными словами, является ли управляющая программа одной из управляющих программ, указанных для этой команды. Если оно недостоверно, на шаге 748 распознается исключительная ситуация. Тем не менее, если управляющая программа достоверна, обработка продолжается с использованием указанной конкретной управляющей программы.

Одной из управляющих программ, которая может быть указана, является операция регистрации параметров трансляции адресов ввода-вывода, используемая при управлении трансляцией адресов для адаптера. С помощью этой операции в DTE, FTE и/или другом местоположении из соответствующих параметров FIB, который является операндом команды, устанавливаются параметры функции шины PCI, имеющие отношение к трансляции адреса ввода-вывода. Эти параметры включают, например, базовый адрес шины PCI; предел адреса шины PCI (иначе называемый, пределом шины PCI или пределом); формат трансляции адреса; размер страницы; и указатель трансляции адреса ввода-вывода, которые являются операндами для этой операции. Существуют также подразумеваемые операнды, включающие начальный адрес DMA (SDMA) и конечный адрес DMA (EDMA), которые хранятся в местоположении, доступном для процессора, выполняющего команду.

Далее со ссылкой на фиг.8 описан один из вариантов осуществления логики установления рабочих параметров для трансляции адреса ввода-вывода. Сначала на шаге 800 запроса определяется, не превышает ли длина базового адреса шины PCI в FIB предел адреса шины PCI в FIB. Если в результате сравнения базового адреса и предела установлено, что длина базового адреса превышает предел, на шаге 802 распознается исключительная ситуация. Тем не менее, если длина базового адреса является меньшей, чем предел, или равна пределу, на шаге 804 запроса дополнительно определяется, достоверны ли формат трансляции адреса и размер страницы. Если они недостоверны, на шаге 806 распознается исключительная ситуация. Тем не менее, если они достоверны, на шаге 808 запроса дополнительно определяется, не превышает ли размер адресного пространства (исходя из базового адреса и предела адреса) пропускную способность трансляции. В одном из примеров размер адресного пространства сравнивается с максимальной возможной пропускной способностью трансляции адресов, исходя из формата таблицы верхнего уровня. Например, если таблицей верхнего уровня является совместимая с DAT таблица сегментов, максимальная пропускная способность трансляции составляет 2 гигабайта.

Если размер адресного пространства превышает пропускную способность трансляции, на шаге 810 распознается исключительная ситуация. В противном случае на шаге 812 запроса дополнительно определяется, имеет ли базовый адрес меньшую длину, чем начальный адрес DMA. Если это так, на шаге 814 распознается исключительная ситуация. В противном случае на шаге 816 запроса еще раз определяется, не превышает ли предел адреса длину конечного адреса DMA. Если это так, на шаге 818 распознается исключительная ситуация. В одном из примеров начальный адрес DMA и конечный адрес DMA зависят от политики в масштабе системы.

После этого на шаге 820 запроса определяется, доступны ли различные ресурсы, если они требуются, для осуществления трансляции адреса ввода-вывода. Если это не так, на шаге 822 распознается исключительная ситуация. В противном случае на шаге 824 запроса дополнительно определяется, были ли уже зарегистрированы параметры трансляции адреса ввода-вывода в РТЕ и DTE. Это определяется, путем проверки значений параметров в FTE/DTE. Например, если параметры в FTE/DTE равны нулю или имеют другое заданное значение, регистрация не была осуществлена. Для определения местоположения FTE используется содержащийся в команде дескриптор, а для определения местоположения DTE используется содержащийся в FTE индекс устройств.

Если функция адаптера уже была зарегистрирована для трансляции адреса, на шаге 826 распознается исключительная ситуация. Если это не так, затем на шаге 828 запроса определяется, достоверно ли адресное пространство DMA, которое указано (т.е. является ли оно адресным пространством, для которого была разблокирована DTE). Если это не так, на шаге 830 распознается исключительная ситуация. Если в результаты всех проверок являются успешными, на шаге 832 параметры трансляции вносятся в запись в таблице устройств и необязательно в соответствующую запись в таблице функций (или другое указанное местоположение). Например, параметры функции шины PCI, имеющие отношение к трансляции адреса ввода-вывода, копируются из блока информации о функциях и вносятся в DTE/FTE. Эти параметры включают, например, базовый адрес шины PCI, предел адреса шины PCI, формат трансляции, размер страницы и указатель трансляции адреса ввода-вывода. Эта операция обеспечивает осуществление DMA к заданному адресному пространству DMA. Она позволяет осуществлять трансляцию адреса ввода-вывода для функции адаптера.

Другой управляющей программой, которая может быть указана командой изменения управления функцией шины PCI, является операция отмены регистрации параметров трансляции адресов ввода-вывода, один из примеров которой описан со ссылкой на фиг.9. С помощью этой операции повторно устанавливаются на нуль параметры функции, имеющие отношение к трансляции адреса ввода-вывода. Эта операция блокирует DMA к заданному адресному пространству DMA и инициирует удаление из буфера быстрой трансляции адреса ввода-вывода записей для этого адресного пространства DMA. Она блокирует трансляцию адреса.

Как показано на фиг.9, в одном из вариантов осуществления на шаге 900 запроса определяется, не зарегистрированы ли параметры трансляции адреса ввода-вывода. В одном из примеров это определяется путем проверки значений соответствующих параметров в FTE или DTE. Если значения этих параметров равны нулю, они не зарегистрированы. Соответственно, на шаге 902 распознается исключительная ситуация. Если они зарегистрированы, на шаге 904 запроса определяется, достоверно ли адресное пространство DMA. Если оно недостоверно, на шаге 906 распознается исключительная ситуация. Если адресное пространство DMA достоверно, на шаге 908 удаляются параметры трансляции, содержащиеся в записи в таблице устройств и необязательно в соответствующей записи в таблице функций.

Выше был подробно описан эффективный механизм трансляции адреса ввода-вывода, предоставляемого адаптером, в адрес ячейки системной памяти. В одном из примеров для доступа к памяти используется полный адрес шины PCI (например, полный 64-разрядный адрес); тем не менее, за счет использования только части адреса при трансляции сводятся к минимуму обращения к таблицам трансляции адресов. Хотя использование полного адреса обеспечивает дополнительную защиту, если при трансляции используются, например, только младшие разряды, обеспечивается более эффективная трансляция за счет меньшего числа уровней таблиц трансляции. Тем самым обеспечивается гибкость операционной системы при использовании адресов, которые способны сосуществовать или совпадать с виртуальными адресами операционной системы. Кроме того, это позволяет адаптерам совместно использовать таблицы трансляции адресов ЦП и одновременно уменьшать число таблиц, которые требуется сканировать. Кроме того, обеспечивается дополнительная защита за счет того, что различные адаптеры и/или операционные системы могут использовать раздельные диапазоны адресного пространства.

В описанных вариантах осуществления адаптерами являются адаптеры на основе шины PCI. В контексте настоящего изобретения шина PCI означает любые адаптеры, реализованные согласно спецификации на шины PCI, установленной Специальной группой по межсоединению периферийных компонентов (PCI-SIG), включая без ограничения шины PCI или PCIe. В одном из частных примеров шина PCI Express (PCIe) является стандартом межсоединений на уровне компонентов, определяющим протокол двусторонней связи для транзакций между адаптерами ввода-вывода и хост-системами. Связь посредством шины PCIe оформлена в пакеты согласно стандарту PCIe на передачу посредством шины PCIe. Транзакции, исходящие из адаптеров ввода-вывода и заканчивающиеся в хост-системах, именуются восходящими транзакциями. Транзакции, исходящие из хост-систем и заканчивающиеся в адаптерах ввода-вывода, именуются нисходящими транзакциями. Топология PCIe основана на двухточечных однонаправленных каналах, которые объединены в пары (например, из одного канала восходящей связи и одного канала нисходящей связи), образующие шину PCIe. Стандарт PCIe определяется и публикуется PCI-SIG.

Как учтут специалисты в данной области техники, особенности настоящего изобретения могут быть воплощены в виде системы, способа или компьютерного программного продукта. Соответственно, особенности настоящего изобретения могут принимать форму целиком аппаратного варианта осуществления, целиком программного варианта осуществления (содержащего аппаратно-программное обеспечение, резидентное программное обеспечение, микрокод и т.д.) или варианта осуществления, сочетающего программные и аппаратные особенности, которые все могут в целом именоваться в описании "схемой", "модулем" или "системой". Кроме того, особенности настоящего изобретения могут принимать форму компьютерного программного продукта, воплощенного в одной или нескольких машиночитаемых средах, в которых записан машиночитаемый программный код.

Может использоваться любое сочетание одной или нескольких машиночитаемых сред. Машиночитаемой средой может являться машиночитаемая запоминающая среда (носитель данных). Машиночитаемой запоминающей средой может являться, например, без ограничения электронная, магнитная, оптическая, электромагнитная, инфракрасная или полупроводниковая система, аппаратура или устройство или любое применимое сочетание перечисленного. Более конкретные примеры (неисчерпывающий список) машиночитаемой запоминающей среды включают: электрическое соединение, содержащее один или несколько проводов, портативный компьютерный диск, жесткий диск, оперативное запоминающее устройство (ОЗУ), постоянное запоминающее устройство (ПЗУ), стираемое программируемое постоянное запоминающее устройство (СППЗУ или флэш-память), оптическое волокно, портативное постоянное запоминающее устройство на компакт-диске (CD-ROM), оптическое запоминающее устройство, магнитное запоминающее устройство или любое применимое сочетание перечисленного. В контексте настоящего документа машиночитаемой запоминающей средой может являться любая материальная среда, в которой содержится или хранится программа для использования системой, аппаратурой или устройством выполнения команд или применительно к ним.

Как показано на фиг.10, в одном из примеров компьютерный программный продукт 1000 содержит, например, одну или несколько машиночитаемых запоминающих сред 1002 для хранения в них машиночитаемого программного кода или логики 1004 для обеспечения и реализации одной или нескольких особенностей настоящего изобретения.

Программный код, воплощенный в машиночитаемой среде, может передаваться с использованием соответствующей среды, включая без ограничения беспроводную, проводную среду, оптоволоконный кабель, ВЧ-среду и т.д. или любое применимое сочетание перечисленного.

Компьютерный программный код для выполнения операций, обеспечивающих особенности настоящего изобретения, может быть записан на одном или нескольких языках программирования в любом сочетании, включая объектно-ориентированный язык программирования, такой как Java, Smalltalk, C++ и т.п., и традиционных процедурных языках программирования, таких как "C" и языки ассемблера или аналогичные языки программирования. Программный код может целиком выполняться в пользовательском компьютере, частично в пользовательском компьютере, в качестве автономного пакета программного обеспечения, частично в пользовательском компьютере и частично в удаленном компьютере или целиком в удаленном компьютере или сервере. В случае последнего сценария удаленный компьютер может быть соединен с пользовательским компьютером посредством сети любого типа, включая локальную вычислительную сеть (ЛВС) или глобальную вычислительную сеть (ГВС), или может быть установлено соединение с внешним компьютером (например, по сети Интернет с использованием поставщика услуг Интернет).

Особенности настоящего изобретения описаны со ссылкой на структурные схемы и/или блок-схемы способов, оборудования (систем) и компьютерных программных продуктов согласно вариантам осуществления изобретения. Подразумевается, что каждый блок на структурных схемах и/или блок-схемах и сочетания блоков на структурных схемах и/или блок-схемах могут быть реализованы посредством команд управления компьютерной программой. Эти команды управления компьютерной программой могут передаваться процессору универсального компьютера, специализированного компьютера или другой программируемого аппаратуры для обработки данных с целью формирования механизма, в котором команды, выполняемые посредством процессора компьютера или другого программируемого оборудования обработки данных, создают средство реализации функций/действий, обозначенных блоком или блоками на структурных схемах и/или блок-схемах.

Эти команды управления компьютерной программой также могут храниться в машиночитаемой среде, которая способна предписывать компьютеру, другому программируемому оборудованию обработки данных или другим устройствам действовать конкретным способом, в результате чего команды, хранящиеся в машиночитаемой среде, формируют продукт, содержащий команды, в которых реализуется функция/действие, обозначенное блоком или блоками на структурных схемах и/или блок-схемах.

Команды управления компьютерной программой также могут загружаться в компьютер, другое программируемое оборудование обработки данных или другие устройства, чтобы инициировать выполнение последовательности оперативных шагов компьютером, другим программируемым оборудованием или другими устройствами с целью формирования реализованного в компьютере процесса, при этом команды, выполняемые компьютером или другим программируемым оборудованием, обеспечивают процессы реализации функций/действий, обозначенных блоком или блоками на структурных схемах и/или блок-схемах.

Приведенные на чертежах структурные схемы и блок-схемы иллюстрируют архитектуру, функциональные возможности и действие возможных вариантов реализации систем, способов и компьютерных программных продуктов согласно различным вариантам осуществления настоящего изобретения. В связи с этим каждым блоком на структурных схемах или блок-схемах может быть представлен определенный модуль, сегмент или часть кода, которая содержит одну или несколько выполняемых команд для реализации заданной логической функции(-й). Следует также отметить, что в некоторых альтернативных вариантах реализации указанные в блоке функции могут выполняться не в том порядке, в котором они представлены на чертежах. Например, функции, указанные двумя последовательно показанными блоками, в действительности могут выполняться преимущественно одновременно, или функции иногда могут выполняться в обратном порядке в зависимости от соответствующих функциональных возможностей. Следует также отметить, что каждый блок на блок-схемах и/или структурных схемах и сочетания блоков на блок-схемах и/или структурных схемах могут быть реализованы посредством специализированных аппаратных систем, выполняющих заданные функции или действия, или посредством сочетаний специализированных аппаратных систем и компьютерных команд.

Помимо вышесказанного одна или несколько особенностей настоящего изобретения может обеспечиваться, предлагаться, применяться, координироваться, обслуживаться и т.д. поставщиком услуг, который предлагает управление пользовательскими средами. Например, поставщик услуг способен создавать, вести, поддерживать и т.д. для одного или нескольких пользователей машинный код и/или вычислительную инфраструктуру, в которой выполняется одна или несколько особенностей настоящего изобретения. В ответ поставщик услуг может получать оплату от пользователя на основании соглашения о подписке и/или абонентской плате в качестве примеров. Дополнительно или в качестве альтернативы, поставщик услуг может получать плату за рекламное содержание, продаваемое одному или нескольким третьим лицам.

Согласно одной из особенностей настоящего изобретения для выполнения одной или нескольких особенностей настоящего изобретения может быть развернуто приложение. В качестве одного из примеров, развертывание приложения включает использование вычислительной инфраструктуры, способной выполнять одну или несколько особенностей настоящего изобретения.

В качестве одной из дополнительных особенностей настоящего изобретения развертывание вычислительной инфраструктуры может включать интегрирование машиночитаемого кода в вычислительную систему, при этом код в сочетании с вычислительной системой способен выполнять одну или несколько особенностей особенности настоящего изобретения.

В качестве еще одной дополнительной особенности настоящего изобретения может быть предложен способ интегрирования вычислительной инфраструктуры, включающий интегрирование машиночитаемого кода в компьютерную систему. Компьютерная система содержит машиночитаемую среду, содержащую одну или несколько особенностей настоящего изобретения. Код в сочетании с компьютерной системой способен выполнять одну или несколько особенностей особенности настоящего изобретения.

Хотя выше описаны различные варианты осуществления, они являются лишь примерами. Например, одна или несколько особенностей настоящего изобретения могут содержаться и использоваться в вычислительных средах других архитектур. Например, одна или несколько особенностей настоящего изобретения могут содержаться, использоваться и/или быть полезными в отличающихся от серверов System z® серверах, таких как серверы Power Systems или другие серверы, предлагаемые International Business Machines Corporation, или одна или несколько особенностей настоящего изобретения могут содержаться, использоваться и/или быть полезными в серверах других компаний. Кроме того, хотя в описании приведенном примере адаптеры и концентратор шины PCI считаются частью сервера, в других вариантах осуществления они необязательно должны считаться частью сервера, и могут просто считаться связанными с системной памятью и/или другими компонентами вычислительной среды. Вычислительной средой необязательно является сервер. Помимо этого, хотя в изобретении описаны таблицы трансляции, может использоваться любая структура данных, и термин таблица должен охватывать все такие структуры данных. К тому же, хотя адаптеры основаны на шине PCI, одна или несколько особенностей настоящего изобретения применимы с использованием других адаптеров или других компонентов ввода-вывода. Адаптер и адаптер на основе шины PCI являются лишь примерами. Кроме того, могут использоваться адресные пространства, таблицы адресов и/или страницы других размеров, не выходящих за пределы объема настоящего изобретения. Более того, в DTE может содержаться больше, меньше информации или другая информация. При этом с использованием одной или нескольких особенностей настоящего изобретения можно транслировать адреса других типов. Возможно множество других разновидностей.

Кроме того, одна или несколько особенностей настоящего изобретения могут выгодно применяться в вычислительных средах других типов. В качестве примера, может использоваться система обработки данных, применимая для хранения и/или выполнения программного кода и содержащая по меньшей мере два процессора, прямо или косвенно связанных с средствами памяти посредством системной шины. Элементы памяти включают, например, локальную память, применяемую во время фактического выполнения программного кода, массовую память и кэш-память, которая обеспечивает временное хранение по меньшей мере части программного кода для уменьшения необходимого числа случаев извлечения кода из массовой памяти во время выполнения.