Область техники, к которой относится изобретение

[0001] Один раскрытый аспект вариантов осуществления относится к схеме вывода линейно изменяющихся сигналов, схеме аналого-цифрового преобразования и устройству формирования изображений, включающему в себя схему аналого-цифрового преобразования.

Уровень техники

[0002] Традиционно известны схемы аналого-цифрового преобразования (в дальнейшем называемые "ADC (аналого-цифровыми преобразователями)"), которые преобразуют аналоговый сигнал в цифровой сигнал. В дальнейшем в этом документе термин "аналого-цифровое преобразование" используется как означающий операцию для преобразования аналогового сигнала в цифровой сигнал. Одним известным примером такого ADC является ADC, включающий в себя модуль сравнения, выполненный с возможностью выводить сигнал результата сравнения посредством сравнения аналогового сигнала и линейно изменяющегося сигнала, имеющего потенциал, варьирующийся в зависимости от времени, счетчик, выполненный с возможностью выводить сигнал отсчета посредством отсчета сигнала тактового импульса, и запоминающее устройство, в которое вводятся сигнал результата сравнения и сигнал отсчета. В этом типе ADC запоминающее устройство хранит сигнал отсчета, который является цифровым сигналом, согласно сигналу результата сравнения, посредством которого аналоговый сигнал преобразуется в цифровой сигнал.

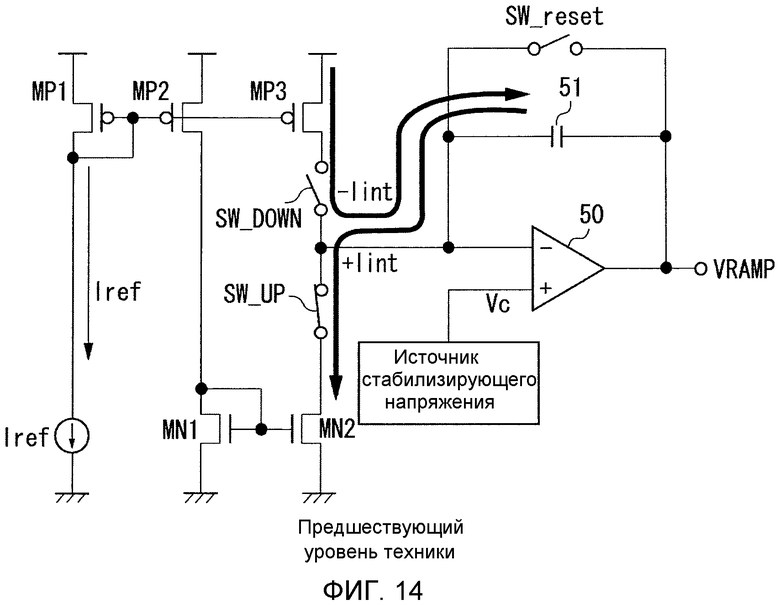

[0003] Выложенная заявка на патент Японии номер 2008-187420 поясняет способ для выполнения аналого-цифрового преобразования при изменении потенциала линейно изменяющегося сигнала в зависимости от времени. Фиг. 14 иллюстрирует конфигурацию схемы вывода линейно изменяющихся сигналов, выполненной с возможностью формировать линейно изменяющийся сигнал, поясненной в выложенной заявке на патент Японии номер 2008-187420. Фиг. 14, прилагаемая к настоящей заявке, соответствует фиг. 19 выложенной заявки на патент Японии номер 2008-187420, хотя проиллюстрированные компоненты обозначены другими ссылочными позициями на фиг. 14. Схема вывода линейно изменяющихся сигналов, поясненная в выложенной заявке на патент Японии номер 2008-187420, заряжает и разряжает интегральную емкость 51, тем самым сдвигая потенциал линейно изменяющегося сигнала от потенциала уровня автоматического сброса на нуль к предварительно определенному потенциалу, который начинает варьироваться в зависимости от времени.

[0004] В ADC, поясненном в выложенной заявке на патент Японии номер 2008-187420, ток прикладывается к интегральной емкости 51, расположенной между входными и выходными контактными выводами интегрирующего усилителя 50, чтобы заряжать и разряжать интегральную емкость 51 таким образом, чтобы сдвигать потенциал линейно изменяющегося сигнала к предварительно определенному потенциалу, который начинает варьироваться в зависимости от времени. Следовательно, этот ADC требует некоторого времени для зарядки и разрядки интегральной емкости 51 таким образом, чтобы сдвигать потенциал линейно изменяющегося сигнала от некоторого потенциала к предварительно определенному потенциалу, который начинает варьироваться в зависимости от времени.

Сущность изобретения

[0005] Согласно аспекту вариантов осуществления схема вывода линейно изменяющихся сигналов, выполненная с возможностью выводить линейно изменяющийся сигнал, имеющий потенциал, варьирующийся в зависимости от времени, включает в себя модуль подачи напряжения, выполненный с возможностью подавать множество напряжений, имеющих разные амплитуды, модуль подачи тока, интегральную схему, выполненную с возможностью выводить линейно изменяющийся сигнал, и емкостной элемент. Модуль подачи напряжения электрически подключен к одному контактному выводу емкостного элемента. Интегральная схема и модуль подачи тока электрически подключены к другому контактному выводу емкостного элемента.

[0006] Согласно другому аспекту вариантов осуществления способ для возбуждения схемы вывода линейно изменяющихся сигналов, которая выполнена с возможностью выводить линейно изменяющийся сигнал, имеющий потенциал, варьирующийся в зависимости от времени, и которая включает в себя модуль подачи тока, интегральную схему и емкостной элемент, включает в себя подачу напряжения в интегральную схему через емкостной элемент, сдвиг потенциала сигнала, выведенного из интегральной схемы, от первого потенциала к потенциалу, отличающемуся от первого потенциала, посредством изменения значения напряжения, которое должно подаваться в интегральную схему через емкостной элемент, подачу тока из модуля подачи тока в интегральную схему и емкостной элемент и вывод линейно изменяющегося сигнала, который имеет потенциал, варьирующийся относительно потенциала, отличающегося от первого потенциала, из интегральной схемы.

[0007] Согласно примерным вариантам осуществления можно уменьшать время, требуемое на то, чтобы сдвигать потенциал линейно изменяющегося сигнала к предварительно определенному потенциалу, который начинает варьироваться в зависимости от времени.

[0008] Дополнительные признаки и аспекты вариантов осуществления должны стать очевидными из последующего подробного описания примерных вариантов осуществления со ссылкой на прилагаемые чертежи.

Краткое описание чертежей

[0009] Прилагаемые чертежи, которые содержатся и составляют часть описания изобретения, иллюстрируют примерные варианты осуществления, признаки и аспекты вариантов осуществления и вместе с описанием служат для того, чтобы пояснять принципы вариантов осуществления.

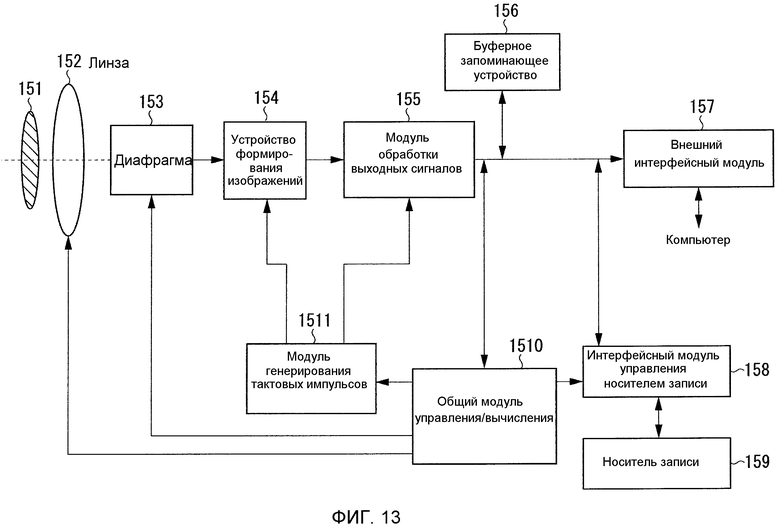

[0010] Фиг. 1 является блок-схемой, иллюстрирующей пример устройства формирования изображений.

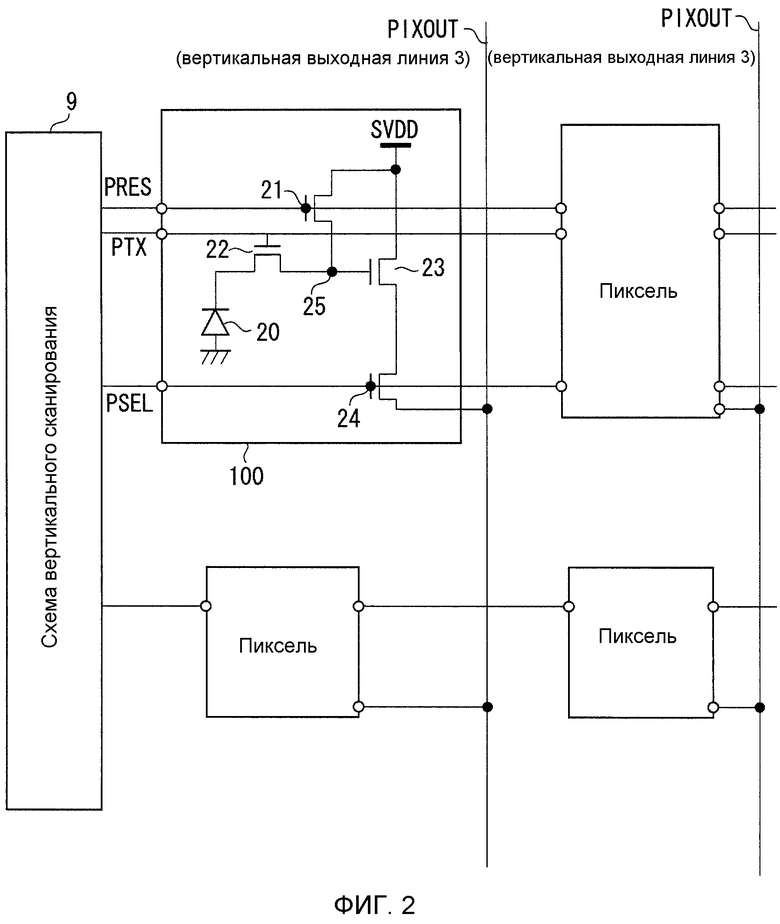

[0011] Фиг. 2 является эквивалентной принципиальной схемой, иллюстрирующей пример пикселя.

[0012] Фиг. 3A является эквивалентной принципиальной схемой, иллюстрирующей пример модуля сравнения.

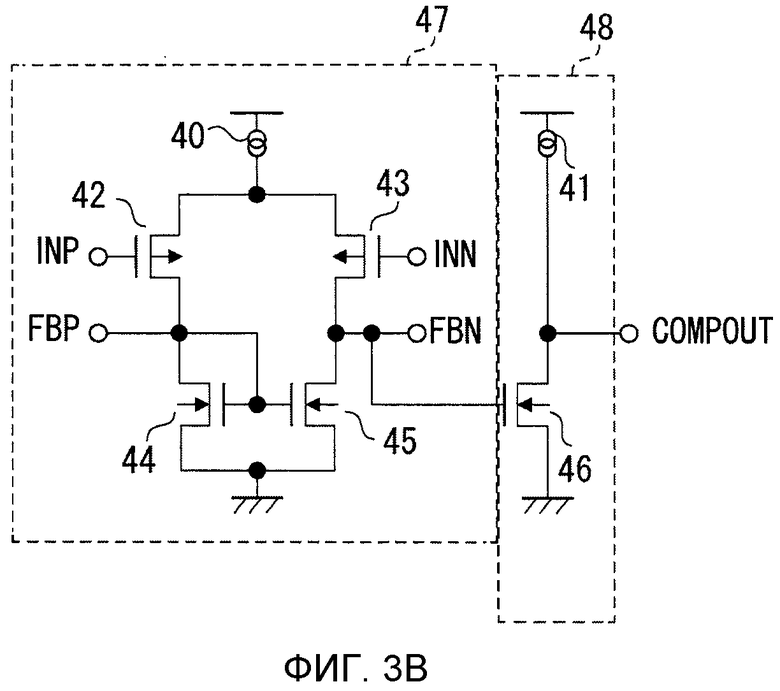

[0013] Фиг. 3B является эквивалентной принципиальной схемой, иллюстрирующей пример модуля сравнения.

[0014] Фиг. 4A является блок-схемой, иллюстрирующей пример схемы вывода линейно изменяющихся сигналов.

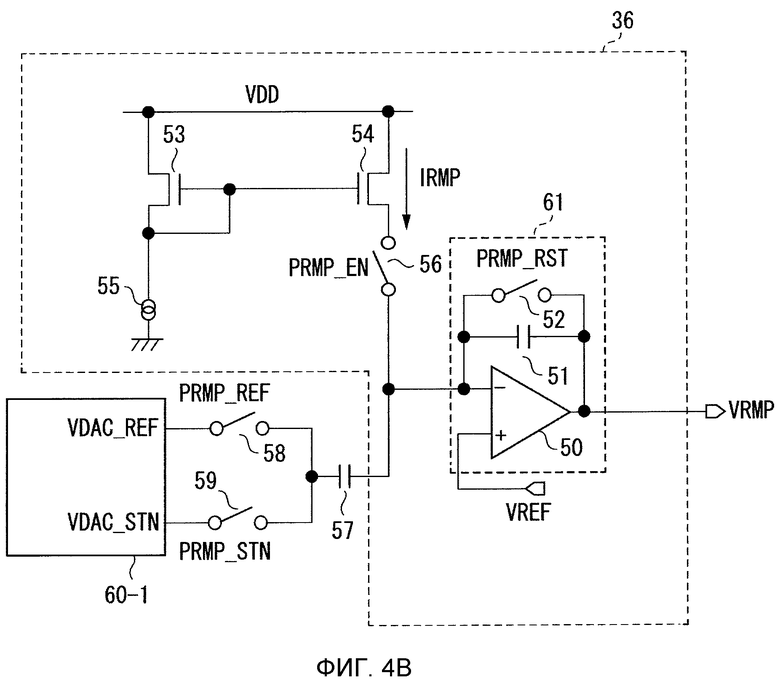

[0015] Фиг. 4B является эквивалентной принципиальной схемой, иллюстрирующей пример схемы вывода линейно изменяющихся сигналов.

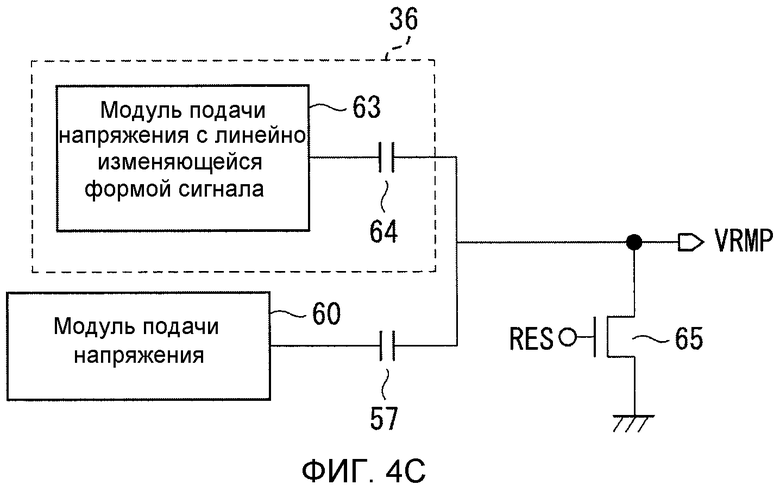

[0016] Фиг. 4C является блок-схемой, иллюстрирующей пример схемы вывода линейно изменяющихся сигналов.

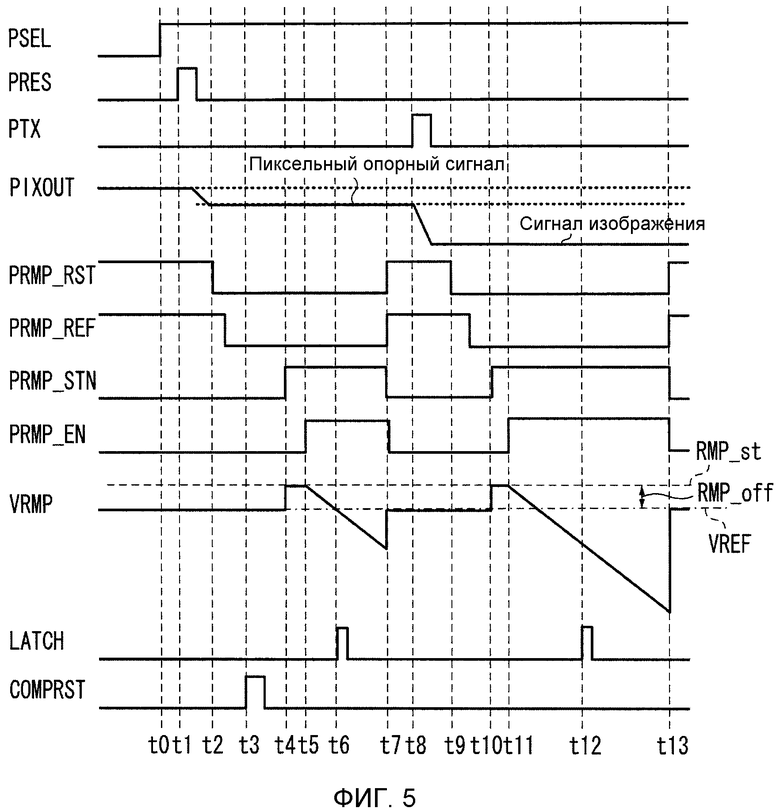

[0017] Фиг. 5 является функциональной временной диаграммой, иллюстрирующей пример работы устройства формирования изображений.

[0018] Фиг. 6 является блок-схемой, иллюстрирующей другую конфигурацию устройства формирования изображений.

[0019] Фиг. 7A является эквивалентной принципиальной схемой, иллюстрирующей пример схемы вывода линейно изменяющихся сигналов.

[0020] Фиг. 7B является эквивалентной принципиальной схемой, иллюстрирующей пример модуля подачи напряжения.

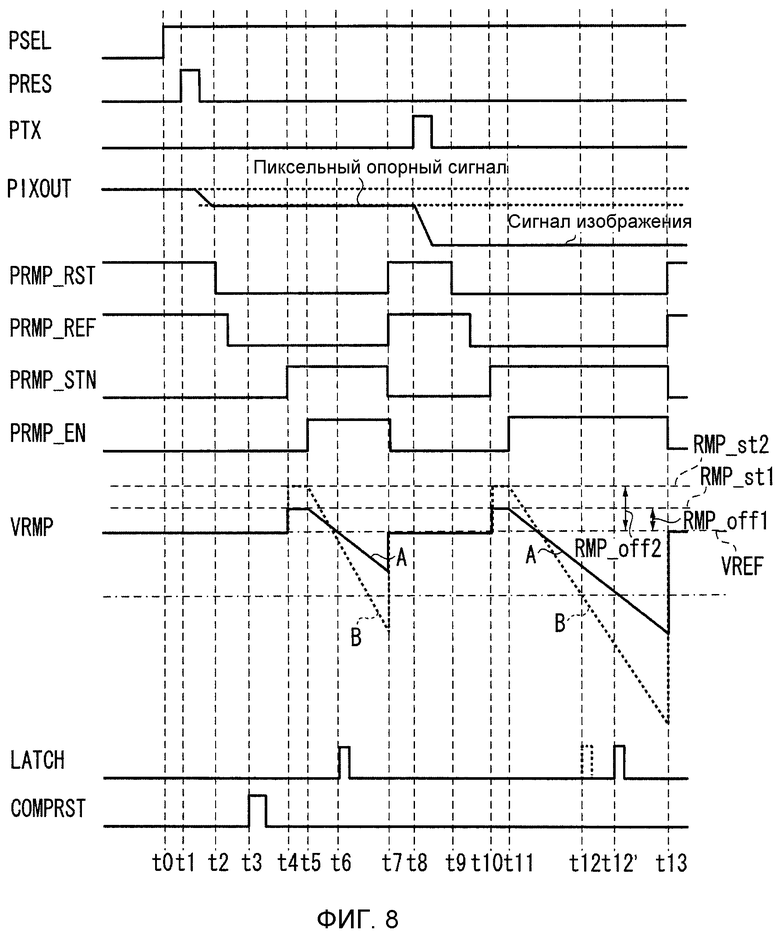

[0021] Фиг. 8 является функциональной временной диаграммой, иллюстрирующей другой пример работы устройства формирования изображений.

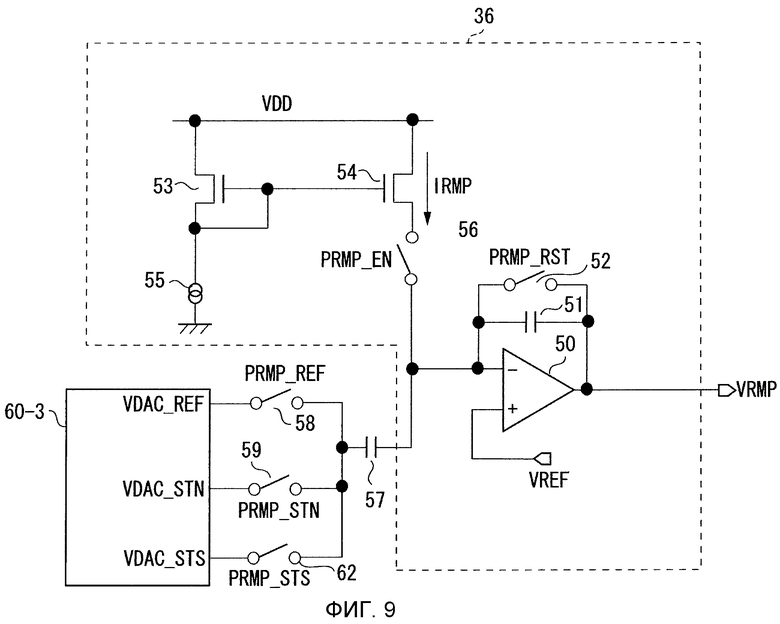

[0022] Фиг. 9 является эквивалентной принципиальной схемой, иллюстрирующей пример схемы вывода линейно изменяющихся сигналов.

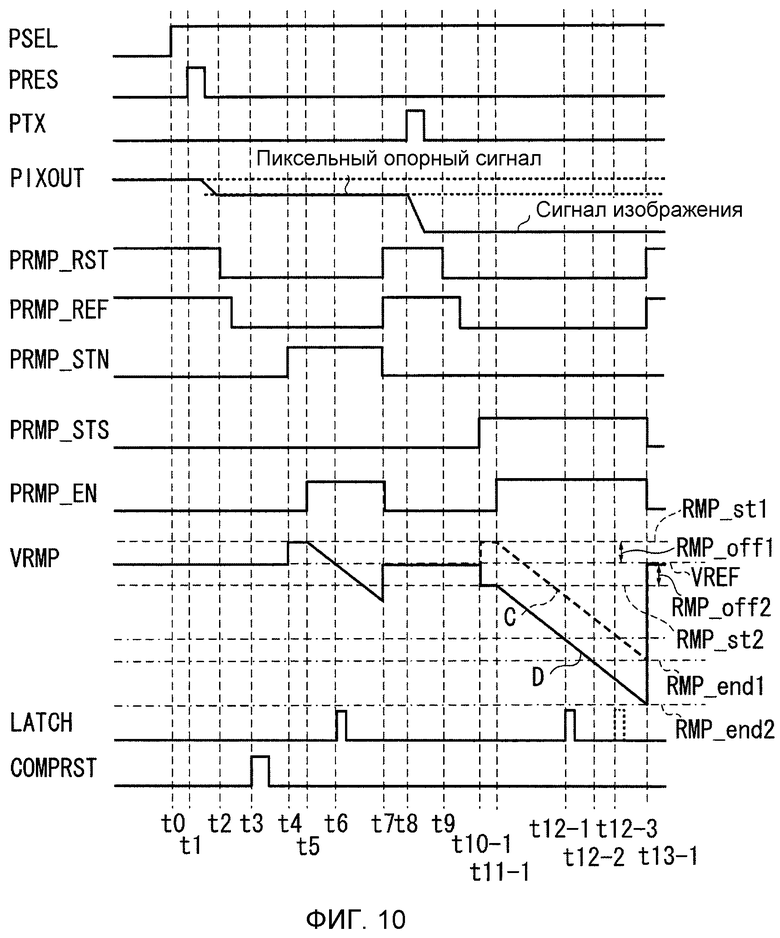

[0023] Фиг. 10 является функциональной временной диаграммой, иллюстрирующей другой пример работы устройства формирования изображений.

[0024] Фиг. 11A является блок-схемой, иллюстрирующей пример устройства формирования изображений.

[0025] Фиг. 11B является блок-схемой, иллюстрирующей пример модуля усиления.

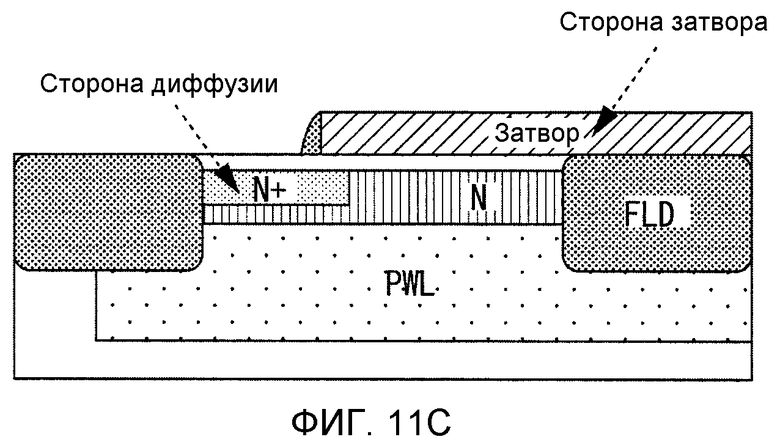

[0026] Фиг. 11C схематично иллюстрирует пример структуры емкостного элемента обратной связи и интегрального емкостного элемента.

[0027] Фиг. 12 является функциональной временной диаграммой, иллюстрирующей другой пример работы устройства формирования изображений.

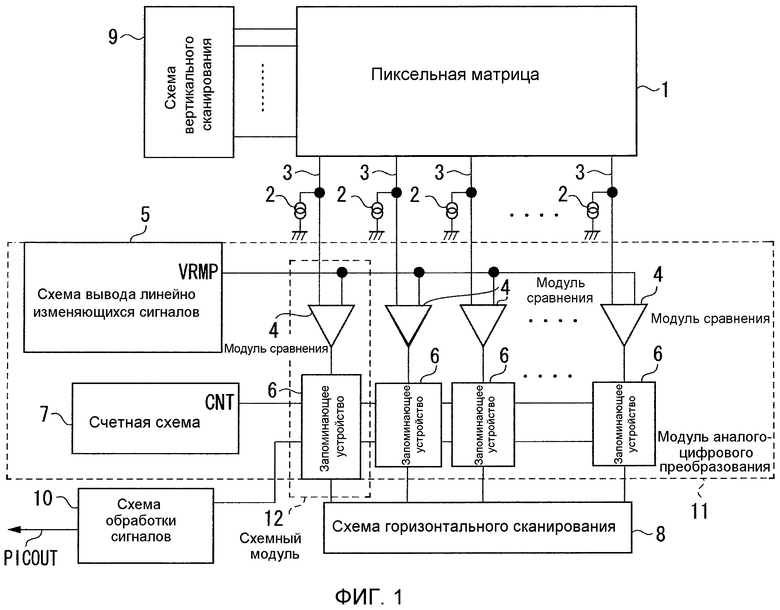

[0028] Фиг. 13 является блок-схемой, иллюстрирующей пример системы формирования изображений.

[0029] Фиг. 14 является эквивалентной принципиальной схемой, иллюстрирующей традиционную схему вывода линейно изменяющихся сигналов.

Подробное описание вариантов осуществления

[0030] Различные примерные варианты осуществления, признаки и аспекты вариантов осуществления описаны подробно ниже со ссылкой на чертежи.

[0031] Фиг. 1 является блок-схемой, иллюстрирующей пример конфигурации устройства формирования изображений согласно первому примерному варианту осуществления. Устройство формирования изображений согласно первому примерному варианту осуществления включает в себя пиксельную матрицу 1, источник 2 тока постоянной величины для вертикальной выходной линии, вертикальную выходную линию 3, модуль 4 сравнения, схему 5 вывода линейно изменяющихся сигналов, запоминающее устройство 6, счетную схему 7, схему 8 горизонтального сканирования, схему 9 вертикального сканирования и схему 10 обработки сигналов. Дополнительно множество схемных модулей 12, каждый из которых включает в себя модуль 4 сравнения и запоминающее устройство 6, размещается в качестве столбцов. Дополнительно множество схемных модулей 12, размещаемых в качестве столбцов, схема 5 вывода линейно изменяющихся сигналов и счетная схема 7 составляют модуль 11 аналого-цифрового преобразования.

[0032] Во-первых, пиксельная матрица 1 и схема 9 вертикального сканирования описываются со ссылкой на фиг. 2. Пиксельная матрица 1 включает в себя пиксели 100, размещенные во множестве строк и множестве столбцов. Фиг. 2 частично иллюстрирует пиксели 100 в два ряда и два столбца, которые соответствуют частичной области в пиксельной матрице 1, схеме 9 вертикального сканирования и вертикальных выходных линиях 3.

[0033] Конкретная конфигурация пикселей 100, включенных в пиксельную матрицу 1, проиллюстрирована в качестве одного пикселя 100. Пиксель 100 включает в себя модуль 20 фотоэлектрического преобразования, транзистор 21 сброса со структурой "металл-оксид-полупроводник" (МОП), МОП-транзистор 22 переноса, МОП-транзистор 23 усиления и МОП-транзистор 24 выбора.

[0034] Модуль 20 фотоэлектрического преобразования преобразует падающий свет в электрический заряд. В настоящем примерном варианте осуществления модуль 20 фотоэлектрического преобразования осуществляется посредством фотодиода в качестве примера. МОП-транзистор 22 переноса переносит электрический заряд фотодиода 20 на входной узел МОП-транзистора 23 усиления. Сигнал PTX переноса подается из схемы 9 вертикального сканирования в управляющий электрод МОП-транзистора 22 переноса.

[0035] МОП-транзистор 23 усиления усиливает сигнал на основе электрического заряда, переносимого на входной узел МОП-транзистора 23 усиления, чтобы выводить усиленный сигнал. Питающее напряжение SVDD подается в МОП-транзистор 23 усиления, и МОП-транзистор 23 усиления электрически подключен к МОП-транзистору 24 выбора. МОП-транзистор 24 выбора расположен на электрическом пути между МОП-транзистором 23 усиления и вертикальной выходной линией 3. Импульс PSEL выбора подается из схемы 9 вертикального сканирования в управляющий электрод МОП-транзистора 24 выбора. Схема 9 вертикального сканирования подает импульс PSEL выбора для каждой строки пикселей 100 и сканирует строку пикселей 100.

[0036] Питающее напряжение SVDD подается в МОП-транзистор 21 сброса, и МОП-транзистор 21 сброса электрически подключен к входному узлу МОП-транзистора 23 усиления. Другими словами, общее питающее напряжение SVDD подается в каждый из МОП-транзистора 23 усиления и МОП-транзистора 21 сброса. Дополнительно импульс PRES сброса подается из схемы 9 вертикального сканирования в управляющий электрод МОП-транзистора 21 сброса. МОП-транзистор 21 сброса сбрасывает потенциал входного узла МОП-транзистора 23 усиления на основе импульса PRES сброса из схемы 9 вертикального сканирования. Сигнал, выведенный из МОП-транзистора 23 усиления, выводится в вертикальную выходную линию 3 через МОП-транзистор 24 выбора в качестве пиксельного сигнала PIXOUT.

[0037] Снова ссылаясь на фиг. 1, описывается устройство формирования изображений согласно первому примерному варианту осуществления. Источник 2 тока постоянной величины для вертикальной выходной линии электрически подключен к вертикальной выходной линии 3 и подает ток в вертикальную выходную линию 3.

[0038] Модуль 4 сравнения сравнивает пиксельный сигнал PIXOUT, введенный из пиксельной матрицы 1, и сигнал VRMP, подаваемый из схемы 5 вывода линейно изменяющихся сигналов. Сигнал VRMP, используемый в этом сравнении, является линейно изменяющимся сигналом, который подается из схемы 5 вывода линейно изменяющихся сигналов и варьируется в зависимости от времени. Модуль 4 сравнения выводит защелкивающий сигнал LATCH в запоминающее устройство 6, когда возникает изменение значения сигнала для сигнала COMPOUT результата сравнения в качестве результата сравнения между пиксельным сигналом PIXOUT и сигналом VRMP.

[0039] Счетная схема 7 отсчитывает сигнал CLK тактового импульса, подаваемый из непроиллюстрированного модуля подачи тактовых импульсов с момента, когда сигнал VRMP из схемы 5 вывода линейно изменяющихся сигналов начинает варьироваться в зависимости от времени, и выводит сигнал CNT отсчета в качестве результата этого отсчета. Другими словами, счетная схема 7 отсчитывает сигнал CLK тактового импульса параллельно с изменением потенциала сигнала VRMP и формирует и выводит сигнал CNT отсчета. Сигнал CNT отсчета совместно подается в запоминающие устройства 6 соответствующих столбцов.

[0040] Сигнал CNT отсчета подается из счетной схемы 7 в запоминающее устройство 6. Дополнительно запоминающее устройство 6 предоставляется для каждого столбца, соответствующего модулю 4 сравнения каждого столбца. Запоминающее устройство 6 хранит сигнал CNT отсчета, подаваемый из счетной схемы 7, когда возникает изменение значения сигнала для защелкивающего сигнала LATCH, подаваемого из модуля 4 сравнения. В дальнейшем в этом документе термин "сигнал, хранимый в запоминающем устройстве" используется как означающий сигнал CNT отсчета, сохраняемый посредством запоминающего устройства 6, когда возникает изменение значения сигнала для защелкивающего сигнала LATCH.

[0041] Схема 8 горизонтального сканирования сканирует запоминающее устройство 6 каждого столбца по порядку и переносит сигнал, хранимый в запоминающем устройстве, хранимый в запоминающем устройстве 6 каждого столбца, в схему 10 обработки сигналов.

[0042] Схема 10 обработки сигналов выполняет, например, обработку для преобразования значения уровня серого в двоичное значение для сигнала, хранимого в запоминающем устройстве, переносимого из запоминающего устройства 6 каждого столбца посредством схемы 8 горизонтального сканирования, и выводит сигнал PICOUT изображения. Сигнал PICOUT изображения является сигналом формирования изображений, выводимым из устройства формирования изображений согласно первому примерному варианту осуществления для формирования изображений.

[0043] Далее описывается модуль 4 сравнения, проиллюстрированный на фиг. 1, со ссылкой на фиг. 3A и 3B. Фиг. 3A является эквивалентной принципиальной схемой модуля 4 сравнения. Модуль 4 сравнения включает в себя схему 30 дифференциального усилителя, переключатели 31 и 32 сброса модуля сравнения, входные емкости 33 и 34 модуля сравнения и схему 35 определения инверсии сигнала.

[0044] Сигнал VRMP вводится на входной контактный вывод INP схемы 30 дифференциального усилителя через входную емкость 33 модуля сравнения. Термин "потенциал V-INP" используется как означающий потенциал, введенный на входной контактный вывод INP на основе сигнала VRMP. Пиксельный сигнал PIXOUT вводится на входной контактный вывод INN схемы 30 дифференциального усилителя через входную емкость 34 модуля сравнения. Термин "потенциал V-INN" используется как означающий потенциал, введенный на входной контактный вывод INN на основе пиксельного сигнала PIXOUT.

[0045] Переключатель 31 сброса модуля сравнения переключает проводимость и непроводимость пути обратной связи от контактного вывода FBP обратной связи к входному контактному выводу INP посредством импульса COMPRST сброса модуля сравнения. Переключатель 32 сброса модуля сравнения переключает проводимость и непроводимость пути обратной связи от контактного вывода FBN обратной связи к входному контактному выводу INN посредством идентичного импульса COMPRST сброса модуля сравнения. Когда импульс COMPRST сброса модуля сравнения задается равным высокому уровню (в дальнейшем называемому "H-уровень"; аналогично низкий уровень называется "L-уровнем"), путь обратной связи от контактного вывода FBP обратной связи к входному контактному выводу INP и путь обратной связи от контактного вывода FBN обратной связи к входному контактному выводу INN переводятся в проводящее состояние.

[0046] Схема 30 дифференциального усилителя выводит сигнал COMPOUT результата сравнения в схему 35 определения инверсии сигнала. Когда возникает изменение значения сигнала для сигнала COMPOUT результата сравнения, также возникает изменение значения сигнала для защелкивающего сигнала LATCH, выведенного из схемы 35 определения инверсии сигнала.

[0047] Фиг. 3B является эквивалентной принципиальной схемой для схемы 30 дифференциального усилителя. Схема 30 дифференциального усилителя включает в себя двухкаскадные усилители, т.е. модуль 47 дифференциального усиления, который включает в себя источник 40 тока постоянной величины, транзисторы 42 и 43 со структурой "металл-оксид-полупроводник" с каналом p-типа (P-МОП) дифференциального входного каскада и нагрузочные транзисторы 44 и 45 со структурой "металл-оксид-полупроводник" с каналом n-типа (N-МОП) и каскад 48 с общим истоком, который включает в себя источник 41 тока постоянной величины и N-МОП-транзистор 46 с общим истоком.

[0048] Когда потенциал V-INP на основе сигнала VRMP, вводимого на входной контактный вывод INP, ниже потенциала V-INN на основе пиксельного сигнала PIXOUT, вводимого на входной контактный вывод INN, N-МОП-транзистор 46 с общим истоком включается и сигнал COMPOUT результата сравнения поддерживается на L-уровне. Когда потенциал V-INP становится больше потенциала V-INN, N-МОП-транзистор 46 с общим истоком выключается и сигнал COMPOUT результата сравнения задается равным H-уровню. Когда сигнал COMPOUT результата сравнения изменяется с L-уровня на H-уровень, защелкивающий сигнал LATCH выводится в запоминающее устройство 6.

[0049] Фиг. 4A схематично иллюстрирует схему 5 вывода линейно изменяющихся сигналов согласно первому примерному варианту осуществления. Схема 5 вывода линейно изменяющихся сигналов включает в себя, по меньшей мере, модуль 60 подачи напряжения, входной емкостной элемент 57 и модуль 36 формирования линейно изменяющихся форм сигнала. Сигнал VRMP, выведенный из модуля 36 формирования линейно изменяющихся форм сигнала, соответствует линейно изменяющемуся сигналу. Модуль 60 подачи напряжения выводит, по меньшей мере, два напряжения VDAC_REF и VDAC_STN, имеющие разные амплитуды, в модуль 36 формирования линейно изменяющихся форм сигнала через входной емкостной элемент 57. Потенциал начала линейного изменения, от которого начинает варьироваться потенциал сигнала VRMP в зависимости от времени, определяется на основе выходного напряжения из модуля 60 подачи напряжения. Модуль 36 формирования линейно изменяющихся форм сигнала формирует линейно изменяющийся сигнал, имеющий линейно изменяющуюся форму сигнала, варьирующуюся относительно потенциала начала линейного изменения в зависимости от времени.

[0050] Далее описывается пример схемы 5 вывода линейно изменяющихся сигналов, проиллюстрированной на фиг. 4A, со ссылкой на фиг. 4B. Фиг. 4B иллюстрирует пример схемной конфигурации для схемы 5 вывода линейно изменяющихся сигналов. В схеме 50 дифференциального усиления опорный сигнал VREF усиления подается на неинвертирующий контактный вывод. Интегральная емкость 51 и переключатель 52 сброса интегрального усиления электрически подключены между инвертирующим контактным выводом и выходным контактным выводом. Инвертирующий контактный вывод соответствует первому входному контактному выводу схемы 50 дифференциального усиления, а неинвертирующий контактный вывод соответствует второму входному контактному выводу схемы 50 дифференциального усиления. Опорный сигнал VREF усиления является опорным напряжением для обнаружения разности относительно сигнала, вводимого на инвертирующий контактный вывод. Схема 50 дифференциального усиления является модулем дифференциального усиления, включенным в схему 5 вывода линейно изменяющихся сигналов. Схема 50 дифференциального усиления, интегральная емкость 51 и переключатель 52 сброса интегрального усиления составляют схему 61 усиления с емкостной обратной связью.

[0051] Ток IRMP постоянной величины, подаваемый из P-МОП-транзисторов 53 и 54 токового зеркала, подается на инвертирующий контактный вывод через переключатель 56 подачи линейно изменяющегося тока. Переключатель 56 подачи линейно изменяющегося тока включается, когда управляющий импульс PRMP_EN задается равным H-уровню, и выключается, когда управляющий импульс PRMP_EN задается равным L-уровню. Опорный ток подается из источника 55 тока постоянной величины в P-МОП-транзистор 53 токового зеркала. Модуль подачи тока в первом примерном варианте осуществления включает в себя P-МОП-транзисторы 53 и 54 токового зеркала, источник 55 тока постоянной величины и переключатель 56 подачи линейно изменяющегося тока.

[0052] Дополнительно входной емкостной элемент 57 электрически подключен к инвертирующему контактному выводу. Модуль 60-1 подачи напряжения электрически подключен к другому контактному выводу входного емкостного элемента 57 через переключатели 58 и 59 на два направления со смещением. Переключатель 58 на два направления со смещением включается, когда управляющий импульс PRMP_REF задается равным H-уровню, и выключается, когда управляющий импульс PRMP_REF задается равным L-уровню. Переключатель 59 на два направления со смещением включается, когда управляющий импульс PRMP_STN задается равным H-уровню, и выключается, когда управляющий импульс PRMP_STN задается равным L-уровню.

[0053] Модуль 60-1 подачи напряжения подает сигналы, имеющие разные значения напряжения, в соответствующие переключатели 58 и 59 на два направления со смещением. Более конкретно, модуль 60-1 подачи напряжения подает напряжение VDAC_REF в переключатель 58 на два направления со смещением. С другой стороны, модуль 60-1 подачи напряжения подает напряжение VDAC_STN в переключатель 59 на два направления со смещением. Можно сдвигать потенциал сигнала VRMP от некоторого потенциала к потенциалу начала линейного изменения, который является потенциалом до того, как начинает варьироваться потенциал в зависимости от времени, посредством включения и выключения каждого из переключателей 58 и 59 на два направления со смещением. Ниже подробно описывается операция для сдвига потенциала сигнала VRMP к потенциалу начала линейного изменения со ссылкой на фиг. 5.

[0054] Фиг. 5 является функциональной временной диаграммой, иллюстрирующей пример работы устройства формирования изображений согласно первому примерному варианту осуществления. Функциональная временная диаграмма по фиг. 5 иллюстрирует работу, когда пиксель 100 одной строки выводит пиксельный сигнал PIXOUT, и работу модуля 11 аналого-цифрового преобразования.

[0055] Во время t0 импульс PSEL выбора задается равным H-уровню, тем самым выбирая строку пикселя 100, из которой выводится пиксельный сигнал PIXOUT. Дополнительно во время t0 управляющий импульс PRMP_RST поддерживается на H-уровне. Интегральная емкость 51 схемы 5 вывода линейно изменяющихся сигналов сбрасывается посредством задания управляющего импульса PRMP_RST равным H-уровню, чтобы включать переключатель 52 сброса интегрального усиления. В это время схема 50 дифференциального усиления находится в состоянии буферизации опорного сигнала VREF усиления, вводимого на неинвертирующий контактный вывод. Во время t0 потенциал сигнала VRMP, выведенного из схемы 50 дифференциального усиления, равен потенциалу опорного сигнала VREF усиления. Потенциал сигнала VRMP во время t0 соответствует первому потенциалу сигнала VRMP. Дополнительно во время t0 управляющий импульс PRMP_REF поддерживается на H-уровне, а управление PRMP_STN поддерживается на L-уровне. В это время напряжение VDAC_REF подается из модуля 60-1 подачи напряжения во входной емкостной элемент 57 через переключатель 58 на два направления со смещением.

[0056] Во время t1 импульс PRES сброса задается равным H-уровню, тем самым сбрасывая потенциал входного узла МОП-транзистора 23 усиления. После этого импульс PRES сброса задается равным L-уровню. Термин "опорный пиксельный сигнал" используется как означающий пиксельный сигнал PIXOUT, выведенный, когда импульс PRES сброса задается равным L-уровню таким образом. Опорный пиксельный сигнал является сигналом, включающим в себя составляющую шума пикселя 100.

[0057] Во время t2 после того, как управляющий импульс PRMP_RST задается равным L-уровню, управляющий импульс PRMP_REF задается равным L-уровню. Электрический заряд, когда управляющий импульс PRMP_RST задается равным L-уровню, хранится в интегральной емкости 51. Дополнительно электрический заряд, когда управляющий импульс PRMP_REF задается равным L-уровню, хранится во входном емкостном элементе 57.

[0058] Во время t3 импульс COMPRST сброса модуля сравнения задается равным H-уровню и затем задается равным L-уровню. Как результат, потенциал сигнала VRMP, когда импульс COMPRST сброса модуля сравнения задается равным L-уровню, т.е. потенциалу опорного сигнала VREF усиления, хранится во входной емкости 33 модуля сравнения. Следовательно, в ходе работы после этого сигнал разности между сигналом VRMP и опорным сигналом VREF усиления вводится на входной контактный вывод INP схемы 30 дифференциального усиления до тех пор, пока импульс COMPRST сброса модуля сравнения не задается равным H-уровню в следующий раз. С другой стороны, электрический заряд на основе потенциала опорного пиксельного сигнала для пиксельного сигнала PIXOUT, когда импульс COMPRST сброса модуля сравнения задается равным L-уровню, хранится во входной емкости 34 модуля сравнения. Следовательно, в ходе работы после этого, сигнал разности между опорным пиксельным сигналом и пиксельным сигналом PIXOUT вводится на входной контактный вывод INN схемы 30 дифференциального усиления до тех пор, пока импульс COMPRST сброса модуля сравнения не задается равным H-уровню в следующий раз.

[0059] Во время t4 управляющий импульс PRMP_STN задается равным H-уровню. Напряжение Voff, которое является разностью напряжений между напряжением VDAC_STN и напряжением VDAC_REF, подается на инвертирующий контактный вывод схемы 50 дифференциального усиления. Напряжение Voff усиливается посредством схемы 50 дифференциального усиления на величину, соответствующую усилению емкости для интегральной емкости 51 и входного емкостного элемента 57, и затем выводится из схемы 50 дифференциального усиления. Разность между сигналом, выводимым из схемы 50 дифференциального усиления в это время, и опорным сигналом VREF усиления представляет собой величину RMP_off смещения потенциала RMP_st начала линейного изменения, который является потенциалом до того, как начинает варьироваться потенциал сигнала VRMP, от опорного сигнала VREF усиления. Таким образом, определяется потенциал потенциала RMP_st начала линейного изменения. Потенциал RMP_st начала линейного изменения соответствует второму потенциалу сигнала VRMP.

[0060] Во время t5 управляющий импульс PRMP_EN задается равным H-уровню, тем самым включая переключатель 56 подачи линейно изменяющегося тока. Как результат сигнал VRMP начинает демонстрировать линейно изменяющуюся форму сигнала, имеющую наклон, определенный посредством значения емкости для интегральной емкости 51 и значения тока для линейно изменяющегося тока IRMP. Другими словами, сигнал VRMP в это время является линейно изменяющимся сигналом, имеющим потенциал, варьирующийся в зависимости от времени. Наклон сигнала VRMP является величиной изменения потенциала сигнала VRMP в единицу времени. Дополнительно одновременно с тем, когда управляющий импульс PRMP_EN задается равным H-уровню, счетная схема 7 начинает отсчитывать сигнал тактового импульса.

[0061] Во время t6 изменяется значение сигнала для защелкивающего сигнала LATCH. Запоминающее устройство 6 хранит значение сигнала для сигнала CNT отсчета в это время. Термин "N-сигнал" используется как означающий значение сигнала для сигнала CNT отсчета, хранимого посредством запоминающего устройства 6 в это время. N-сигнал является сигналом, включающим в себя составляющую шума модуля 4 сравнения, к примеру, смещение модуля 4 сравнения каждого столбца.

[0062] Во время t7 управляющий импульс PRMP_EN задается равным L-уровню, тем самым прекращая изменение в потенциале сигнала VRMP в зависимости от времени. Дополнительно во время t7 управляющий импульс PRMP_STN задается равным L-уровню и управляющий импульс PRMP_REF задается равным H-уровню. Дополнительно управляющий импульс PRMP_RST задается равным H-уровню, тем самым сбрасывая электрические заряды интегральной емкости 51 и входного емкостного элемента 57 к состояниям во время t0. Счетная схема 7 прекращает подсчет сигнала тактового импульса и возвращает сигнал CNT отсчета к начальному значению.

[0063] Во время t8 импульс PTX переноса задается равным H-уровню. Как результат электрический заряд сигнала, который формирует фотодиод 20 посредством фотоэлектрического преобразования падающего света, переносится на входной узел МОП-транзистора 23 усиления. МОП-транзистор 23 усиления выводит сигнал на основе потенциала входного узла МОП-транзистора 23 усиления, в который переносится электрический заряд сигнала, сформированный посредством фотодиода 20. Этот сигнал выводится в вертикальную выходную линию 3 через МОП-транзистор 24 выбора. Этот сигнал является сигналом изображения, который представляет собой один пиксельный сигнал PIXOUT.

[0064] Электрический заряд, когда импульс COMPRST сброса модуля сравнения задается равным H-уровню во время t3 и затем задается равным L-уровню, хранится во входной емкости 34 модуля сравнения. Другими словами, потенциал опорного пиксельного сигнала, который представляет собой один пиксельный сигнал PIXOUT, хранится во входной емкости 34 модуля сравнения. Следовательно, сигнал разности между сигналом изображения и опорным пиксельным сигналом вводится на входной контактный вывод INN схемы 30 дифференциального усиления. Составляющая шума пикселя 100 включается в опорный пиксельный сигнал, как описано выше. Следовательно, сигнал, представляющий собой результат вычитания составляющей шума из сигнала изображения, вводится из входной емкости 34 модуля сравнения в схему 30 дифференциального усиления.

[0065] Во время t9 управляющий импульс PRMP_RST задается равным L-уровню, аналогично работе во время t2. Затем управляющий импульс PRMP_REF задается равным L-уровню.

[0066] Во время 10 управляющий импульс PRMP_STN задается равным H-уровню аналогично работе во время t4. Сигнал VRMP изменяется от опорного сигнала VREF усиления на величину RMP_off смещения, тем самым получая потенциал RMP_st начала линейного изменения.

[0067] Во время t11 управляющий импульс PRMP_EN задается равным H-уровню, аналогично работе во время t5, в результате чего потенциал сигнала VRMP начинает варьироваться в зависимости от времени. Счетная схема 7 начинает отсчитывать сигнал тактового импульса.

[0068] Допустим, что взаимосвязь абсолютных величин обращается во время t12 между сигналом, вводимым на входной контактный вывод INN схемы 30 дифференциального усиления, и сигналом, вводимым на входной контактный вывод INP. В этом случае возникает изменение значения сигнала для защелкивающего сигнала LATCH, выведенного из модуля 4 сравнения. После этого изменения значения сигнала для защелкивающего сигнала LATCH запоминающее устройство 6 хранит значение сигнала для сигнала CNT отсчета во время t12. Термин "S-сигнал" используется как означающий сигнал CNT отсчета, хранимый посредством запоминающего устройства 6 в это время.

[0069] Во время t13 управляющий импульс PRMP_EN задается равным L-уровню, аналогично работе во время t7, в результате чего потенциал сигнала VRMP прекращает варьирование в зависимости от времени. Дополнительно во время t13 управляющий импульс PRMP_STN задается равным L-уровню и управляющий импульс PRMP_REF задается равным H-уровню. Дополнительно управляющий импульс PRMP_RST задается равным H-уровню, тем самым сбрасывая электрические заряды интегральной емкости 51 и входного емкостного элемента 57 к состояниям во время t0. Счетная схема 7 прекращает подсчет сигнала тактового импульса и возвращает сигнал CNT отсчета к начальному значению.

[0070] В первом примерном варианте осуществления первое сравнение, которое представляет собой сравнение между сигналом VRMP и аналоговым сигналом, соответствует работе, выполняемой в течение периода между временем t11 и временем t13. Дополнительно второе сравнение, которое представляет собой сравнение между сигналом VRMP и опорным пиксельным сигналом, соответствует работе, выполняемой в течение периода между временем t5-t7.

[0071] N-сигнал и S-сигнал, хранимые в запоминающем устройстве 6 каждого столбца, переносятся в схему 10 обработки сигналов по порядку посредством схемы 8 горизонтального сканирования. Схема 10 обработки сигналов выполняет, например, обработку для обнаружения разности между S-сигналом и N-сигналом. Составляющая шума модуля 4 сравнения, к примеру, смещение модуля 4 сравнения каждого столбца, может вычитаться из S-сигнала посредством вычитания N-сигнала из S-сигнала. Следовательно, можно уменьшать влияние варьирования характеристик модулей 4 сравнения соответствующих столбцов на S-сигнал. Схема 10 обработки сигналов выводит сигнал, представляющий собой результат вычитания N-сигнала из S-сигнала, в качестве сигнала PICOUT изображения.

[0072] Схема 5 вывода линейно изменяющихся сигналов согласно первому примерному варианту осуществления включает в себя модуль 60-1 подачи напряжения, который подает множество напряжений, и входной емкостной элемент 57. Можно сдвигать потенциал сигнала VRMP от потенциала опорного напряжения Vref усиления посредством приложения напряжения VDAC_STN к схеме 50 дифференциального усиления после сохранения потенциала напряжения VDAC_REF во входном емкостном элементе 57. Следовательно, схема 5 вывода линейно изменяющихся сигналов согласно первому примерному варианту осуществления имеет такой положительный результат, что она может сдвигать потенциал сигнала VRMP с высокой скоростью по сравнению с конфигурацией, которая сдвигает потенциал сигнала VRMP посредством зарядки и разрядки интегральной емкости 51 посредством приложения тока к интегральной емкости 51.

[0073] Дополнительно в конфигурации, которая сдвигает потенциал сигнала VRMP посредством зарядки и разрядки интегральной емкости 51 посредством приложения тока к интегральной емкости 51, изменение значения тока для тока, прикладываемого к интегральной емкости 51, влияет на величину смещения сигнала VRMP. Другими словами, даже если ток, имеющий идентичное значение тока, прикладывается к интегральной емкости 51, величина смещения сигнала VRMP изменяется в зависимости от того, как изменяется значение тока. Следовательно, эта традиционная конфигурация имеет такой недостаток, что точность аналого-цифрового преобразования снижается, поскольку изменяется значение потенциала RMP_st начала линейного изменения.

[0074] Схема 5 вывода линейно изменяющихся сигналов согласно первому примерному варианту осуществления может сдвигать сигнал VRMP без базирования на зарядке и разрядке интегральной емкости 51. Следовательно, можно предотвращать изменение значения потенциала RMP_st начала линейного изменения. Следовательно, можно повышать точность аналого-цифрового преобразования по сравнению с конфигурацией, которая сдвигает сигнал VRMP посредством зарядки и разрядки интегральной емкости 51 посредством приложения тока к интегральной емкости 51.

[0075] Первый примерный вариант осуществления описан на основе примера, в котором модуль 36 формирования линейно изменяющихся форм сигнала включает в себя схему 61 усиления с емкостной обратной связью, имеющую схему 50 дифференциального усиления и интегральную емкость 51 в качестве примера. Тем не менее первый примерный вариант осуществления не ограничивается этой конфигурацией, включающей в себя схему 61 усиления с емкостной обратной связью, и может быть эффективно выполнен с помощью любой конфигурации, включающей в себя интегральную схему. Дополнительно первый примерный вариант осуществления может быть эффективно выполнен даже с конфигурацией без интегральной схемы, такой как конфигурация, в которой модуль 36 формирования линейно изменяющихся форм сигнала состоит из схемы истокового повторителя. Даже эта конфигурация позволяет формировать линейно изменяющийся сигнал VRMP, имеющий линейно изменяющуюся форму сигнала, и позволяет определять потенциал начала линейного изменения вследствие наличия модуля 60 подачи напряжения и входного емкостного элемента 57.

[0076] Дополнительно как проиллюстрировано на фиг. 4C, модуль 36 формирования линейно изменяющихся форм сигнала может включать в себя модуль 63 подачи напряжения с линейно изменяющейся формой сигнала и емкость 64. Когда импульс RES сброса подается в управляющий электрод транзистора 65, транзистор 65 сбрасывает электрические заряды емкости 64 и входного емкостного элемента 57. Модуль 63 подачи напряжения с линейно изменяющейся формой сигнала может, например, включать в себя матрицу сопротивлений, имеющую значение переменного сопротивления, и может быть выполнен с возможностью выводить напряжение на основе значения сопротивления.

[0077] Первый примерный вариант осуществления описан с использованием устройства формирования изображений в качестве примера устройства, включающего в себя модуль 11 аналого-цифрового преобразования. Тем не менее первый примерный вариант осуществления не ограничивается этой конфигурацией. Первый примерный вариант осуществления может применяться к схеме вывода линейно изменяющихся сигналов ADC, выполненного с возможностью преобразовывать аналоговый сигнал в цифровой сигнал на основе результата сравнения между аналоговым сигналом и линейно изменяющимся сигналом, имеющим потенциал, варьирующийся в зависимости от времени.

[0078] Дополнительно первый примерный вариант осуществления описан на основе примера, в котором устройство формирования изображений включает в себя схему 10 обработки сигналов. Тем не менее устройство формирования изображений не обязательно должно включать в себя схему 10 обработки сигналов. Схема 10 обработки сигналов может предоставляться для устройства, отличного от устройства формирования изображений, и сигнал может выводиться из устройства формирования изображений в схему 10 обработки сигналов.

[0079] Дополнительно первый примерный вариант осуществления описан на основе примера, в котором счетная схема 7 совместно выводит сигнал CNT отсчета в запоминающие устройства 6 соответствующих столбцов. Тем не менее в качестве другого примера, как проиллюстрировано на фиг. 6, запоминающие устройства 6 соответствующих столбцов могут включать в себя счетные схемы 7, каждая из которых формирует сигнал CNT отсчета. В этом случае защелкивающий сигнал LATCH выводится из модулей 4 сравнения соответствующих столбцов в счетные схемы 7 соответствующих столбцов. Запоминающие устройства 6 хранят сигнал CNT отсчета, когда возникает изменение значения сигнала для защелкивающего сигнала LATCH. Схема 5 вывода линейно изменяющихся сигналов, выполненная так, как пояснено в описании первого примерного варианта осуществления, может эффективно применяться даже к этому примеру.

[0080] Дополнительно первый примерный вариант осуществления описан на основе примера, в котором потенциал сигнала VRMP сдвигается от опорного сигнала VREF усиления к потенциалу RMP_st начала линейного изменения. Тем не менее потенциал сигнала VRMP может сдвигаться от потенциала, отличного от опорного сигнала VREF усиления, к потенциалу RMP_st начала линейного изменения.

[0081] Второй примерный вариант осуществления описывается со ссылкой на чертежи, при этом внимание обращается на отличия от первого примерного варианта осуществления. Фиг. 7A является эквивалентной принципиальной схемой для схемы 5 вывода линейно изменяющихся сигналов согласно второму примерному варианту осуществления. На фиг. 7A, компоненты, которые функционируют аналогично компонентам, проиллюстрированным на фиг. 4B, указываются посредством ссылочных позиций, идентичных ссылочным позициям на фиг. 4B.

[0082] Источник 72 тока переменной величины может подавать ток при варьировании значения тока. Транзистор 71 является P-МОП-транзистором токового зеркала. Модуль 60-2 подачи напряжения является примером модуля 60 подачи напряжения во втором примерном варианте осуществления. P-МОП-транзистор 54 токового зеркала является первым транзистором, который подает ток из источника тока в схему 50 дифференциального усиления. Дополнительно P-МОП-транзистор 71 токового зеркала подает ток IDAC в модуль 60-2 подачи напряжения на основе тока, подаваемого из P-МОП-транзистора 53 токового зеркала и источника 72 тока переменной величины. Другими словами, P-МОП-транзистор 71 токового зеркала является вторым транзистором, который подает ток из источника тока в модуль 60-2 подачи напряжения.

[0083] Во втором примерном варианте осуществления ток совместно подается в управляющие электроды P-МОП-транзисторов 54 и 71 токового зеркала из P-МОП-транзистора 53 токового зеркала и источника 72 тока переменной величины. Следовательно, значение тока для тока IDAC, подаваемого в модуль 60-2 подачи напряжения, и значение тока для тока IRMP, подаваемого в схему 50 дифференциального усиления, имеют пропорциональную взаимосвязь. Модуль подачи тока во втором примерном варианте осуществления включает в себя P-МОП-транзисторы 53, 54, 71 токового зеркала, источник 72 тока переменной величины и переключатель 56 подачи линейно изменяющегося тока.

[0084] Фиг. 7B иллюстрирует подробную конфигурацию модуля 60-2 подачи напряжения во втором примерном варианте осуществления. Матрица 81 сопротивлений включает в себя множество сопротивлений. Множество буферов 82-1 и 82-2 электрически подключено к матрице 81 сопротивлений. Дополнительно P-МОП-транзистор 71 токового зеркала подает ток IDAC в матрицу 81 сопротивлений. Матрица 81 сопротивлений преобразует ток IDAC в напряжение и выводит преобразованное напряжение во множество буферов 82-1 и 82-2.

[0085] Буфер 82-1 выводит напряжение DACOUT_A, и буфер 82-2 выводит напряжение DACOUT_B. Значение сопротивления электрического пути от P-МОП-транзистора 71 токового зеркала к буферу 82-1 отличается от значения сопротивления электрического пути от P-МОП-транзистора 71 токового зеркала к буферу 82-2. Следовательно, значение напряжения, подаваемого в буфер 82-1, отличается от значения напряжения, подаваемого в буфер 82-2. Соответственно, напряжение DACOUT_A, выводимое из буфера 82-1, и DACOUT_B, выводимое из буфера 82-2, имеют разные значения напряжения. Таким образом, модуль 60-2 подачи напряжения может выводить множество значений напряжения. То, как назначать напряжения DACOUT_A и DACOUT_B для напряжения VDAC_REF и VDAC_STN, может быть определено на основе того, следует задавать направление сдвига сигнала VRMP идентично или отлично от направления, в котором сигнал VRMP варьируется в ходе аналого-цифрового преобразования.

[0086] Фиг. 8 является функциональной временной диаграммой, иллюстрирующей пример работы устройства формирования изображений, проиллюстрированного на фиг. 1, с использованием схемы 5 вывода линейно изменяющихся сигналов согласно второму примерному варианту осуществления. Устройство формирования изображений, включающее в себя схему 5 вывода линейно изменяющихся сигналов согласно второму примерному варианту осуществления, может функционировать аналогично функциональному распределению по времени, описанному в описании первого примерного варианта осуществления со ссылкой на фиг. 5.

[0087] В схеме 5 вывода линейно изменяющихся сигналов согласно второму примерному варианту осуществления значение тока для тока IDAC, подаваемого в модуль 60-2 подачи напряжения и значение тока для тока IRMP, подаваемого в схему 50 дифференциального усиления, имеют пропорциональную взаимосвязь, как описано выше. Допустим, что значение тока для тока IRMP составляет I ампер. Линейно изменяющаяся форма сигнала для сигнала VRMP в это время представляет собой наклон A, проиллюстрированный на фиг. 8. Дополнительно когда значение тока для тока IRMP составляет I ампер, разность между потенциалом RMP_st начала линейного изменения и опорным сигналом VREF усиления представляет собой величину RMP_off1 смещения. Допустим, что I' ампер является значением тока для тока IDAC, когда значение тока для тока IRMP составляет I ампер. Затем допустим, что значение тока для тока IRMP изменяется на 2I ампер, что в два раза превышает I ампер, при сохранении сопротивления модуля 60-2 подачи напряжения идентичным сопротивлению во время формирования сигнала VRMP, имеющего линейно изменяющуюся форму A сигнала. Поскольку ток IDAC имеет пропорциональную взаимосвязь с током IRMP, значение тока для тока IDAC также удваивается до 2I' ампер. Следовательно, разность между потенциалами напряжения VDAC_REF и напряжения VDAC_STN, выведенного из модуля 60-2 подачи напряжения, удваивается по сравнению с разностью во время формирования сигнала VRMP, имеющего вышеописанную линейно изменяющуюся форму A сигнала. Соответственно, величина RMP_off2 смещения, которая является разностью между потенциалом RMP_st начала линейного изменения сигнала VRMP и потенциалом опорного сигнала VREF усиления, удваивается по сравнению с величиной RMP_off1 смещения. Дополнительно поскольку значение тока для тока IRMP составляет 2I ампер, наклон сигнала VRMP, выведенного из схемы 50 дифференциального усиления, удваивается по сравнению с сигналом VRMP, имеющим вышеописанную линейно изменяющуюся форму A сигнала. Фиг. 8 иллюстрирует линейно изменяющуюся форму сигнала для сигнала VRMP, сформированного, когда значение тока для тока IRMP удваивается до 2I ампер, в качестве наклона B.

[0088] В схеме 5 вывода линейно изменяющихся сигналов согласно второму примерному варианту осуществления ток IRMP и ток IDAC имеют пропорциональную взаимосвязь. Схеме 5 вывода линейно изменяющихся сигналов согласно второму примерному варианту осуществления имеет положительные результаты, поясненные выше в описании первого примерного варианта осуществления. Дополнительно схема 5 вывода линейно изменяющихся сигналов согласно второму примерному варианту осуществления дает возможность увязанных заданий величины RMP_off смещения, которая является разностью между потенциалом RMP_st начала линейного изменения и опорным сигналом VREF усиления, и наклона сигнала VRMP в ходе аналого-цифрового преобразования.

[0089] Дополнительно изменение наклона сигнала VRMP может изменять усиление сигнала, выведенного из модуля 11 аналого-цифрового преобразования, относительно пиксельного выходного сигнала PIXOUT, и этот механизм описывается далее. В случае если сигнал VRMP варьируется согласно линейно изменяющейся форме B сигнала, допустим, что значение сигнала для защелкивающего сигнала LATCH изменяется во время t12. В случае если сигнал VRMP варьируется согласно линейно изменяющейся форме A сигнала при условии, что идентичный электронный потенциал подается на входной контактный вывод INN схемы 30 дифференциального усиления, значение сигнала для защелкивающего сигнала LATCH изменяется во время t12', позднее времени t12. Следовательно, S-сигнал, хранимый в запоминающем устройстве 6, когда сигнал VRMP варьируется согласно линейно изменяющейся форме A сигнала, превышает S-сигнал, когда сигнал VRMP варьируется согласно линейно изменяющейся форме B сигнала. Таким образом, значение сигнала для сигнала, хранимого в запоминающем устройстве 6, может быть изменено посредством наклона варьирования сигнала VRMP. Как результат можно изменять усиление сигнала, выведенного из модуля 11 аналого-цифрового преобразования, относительно пиксельного выходного сигнала PIXOUT.

[0090] Схема 5 вывода линейно изменяющихся сигналов согласно второму примерному варианту осуществления выполнена так, что модуль 60-2 подачи напряжения формирует множество напряжений с использованием идентичного значения сопротивления для формирования соответствующих сигналов VRMP, имеющих линейно изменяющуюся форму A сигнала и линейно изменяющуюся форму B сигнала соответственно. Тем не менее модуль 60-2 подачи напряжения может использовать другое значение сопротивления для формирования сигнала VRMP, имеющего линейно изменяющуюся форму сигнала, отличную от линейно изменяющейся формы A сигнала. В этом случае величина RMP_off смещения может задаваться независимо от наклона сигнала VRMP.

[0091] Третий примерный вариант осуществления описывается со ссылкой на чертежи, при этом внимание обращается на отличия от первого примерного варианта осуществления. Фиг. 9 является эквивалентной принципиальной схемой для схемы 5 вывода линейно изменяющихся сигналов согласно третьему примерному варианту осуществления. На фиг. 9 компоненты, которые функционируют аналогично компонентам, проиллюстрированным на фиг. 4B, указываются посредством ссылочных позиций, идентичных ссылочным позициям на фиг. 4B.

[0092] Модуль 60-3 подачи напряжения согласно третьему примерному варианту осуществления выводит три напряжения, VDAC_REF, VDAC_STN и VDAC_STS. Следовательно, модуль 60-3 подачи напряжения дополнительно включает в себя контактный вывод для вывода напряжения VDAC_STS, в дополнение к конфигурации, поясненной в описании первого примерного варианта осуществления. Дополнительно взаимосвязь абсолютных величин между тремя значениями напряжения удовлетворяет выражению отношения (VDAC_STS>VDAC_REF>VDAC_STN). Дополнительно переключатель 62 на два направления со смещением расположен на электрическом пути между контактным выводом для вывода напряжения VDAC_STS и входным емкостным элементом 57. Переключатель 62 на два направления со смещением включается, когда управляющий импульс PRMP_STS задается равным H-уровню, и выключается, когда управляющий импульс PRMP_STS задается равным L-уровню.

[0093] Фиг. 10 является функциональной временной диаграммой, иллюстрирующей пример работы устройства формирования изображений, проиллюстрированного на фиг. 1, включающего в себя схему 5 вывода линейно изменяющихся сигналов согласно третьему примерному варианту осуществления. Соответствующие операции, выполняемые от времени t1 до времени t9, могут быть аналогичными соответствующим операциям, выполняемым от времени t1 до времени t9, поясненным в описании первого примерного варианта осуществления со ссылкой на фиг. 5. Термин "RMP_st1" используется в третьем примерном варианте осуществления как означающий потенциал начала линейного изменения, обнаруженный посредством задания управляющего импульса PRMP_STN равным H-уровню во время t5. Дополнительно термин "RMP_off1" используется как означающий величину смещения, которая является разностью между потенциалом RMP_st1 начала линейного изменения и опорным сигналом VREF усиления.

[0094] В первом примерном варианте осуществления управляющий импульс PRMP_STN задается равным H-уровню во время t10, но в третьем примерном варианте осуществления, управляющий импульс PRMP_STS задается равным H-уровню, в то время как управляющий импульс PRMP_STN поддерживается на L-уровне во время t10-1. Как упомянуто выше, три напряжения, подаваемые посредством модуля 60-3 подачи напряжения, удовлетворяют выражению отношения (VDAC_STS>VDAC_REF>VDAC_STN). Следовательно, потенциал сигнала VRMP сдвигается относительно опорного сигнала VREF усиления в противоположном направлении относительно сдвига, вызываемого, когда управляющий импульс PRMP_STN задается равным H-уровню. Другими словами, потенциал сигнала VRMP переключается в направлении, идентичном направлению, в котором сигнал VRMP варьируется в зависимости от времени в ходе аналого-цифрового преобразования. Термин "RMP_st2" используется как означающий потенциал начала линейного изменения в это время. Дополнительно термин "RMP_off2" используется как означающий величину смещения, которая является разностью между потенциалом RMP_st2 начала линейного изменения и опорным сигналом VREF усиления. Потенциал RMP_st2 начала линейного изменения соответствует третьему потенциалу, который является потенциалом, отличным как от опорного сигнала VREF усиления в качестве первого потенциала, так и от потенциала RMP_st1 начала линейного изменения в качестве второго потенциала.

[0095] Во время t11-1 управляющий импульс PRMP_EN задается равным H-уровню. Как результат потенциал сигнала VRMP начинает варьироваться относительно потенциала RMP_st2 начала линейного изменения в зависимости от времени. Сформированная линейно изменяющаяся форма сигнала для сигнала VRMP представляет собой наклон D, проиллюстрированный на фиг. 8. Пунктирная линия C указывает линейно изменяющуюся форму сигнала для сигнала VRMP, который должен быть сформирован, если управляющий импульс PRMP_STS не задается равным H-уровню, в то время как управляющие импульсы PRMP_STN и PRMP_EN задаются равными H-уровню во время t10-1, и эта линейно изменяющаяся форма сигнала проиллюстрирована на фиг. 8 с целью сравнения.

[0096] Допустим, что взаимосвязь абсолютных величин между сигналом, вводимым на входной контактный вывод INN схемы дифференциального усиления 30, и сигналом, вводимым на входной контактный вывод INP, обращается во время t12-1, когда потенциал сигнала VRMP варьируется согласно линейно изменяющейся форме D сигнала. В это время возникает изменение значения сигнала защелкивающего сигнала LATCH, выведенного посредством модуля сравнения 4. Запоминающее устройство 6 удерживает S-сигнал, который является значением сигнала для сигнала CNT отсчета в это время. С другой стороны, допустим, что потенциал сигнала VRMP варьируется согласно линейно изменяющейся форме C сигнала при условии, что идентичное значение сигнала вводится на входной контактный вывод INN схемы 30 дифференциального усиления. В этом случае возникает изменение значения сигнала для защелкивающего сигнала LATCH, выведенного из модуля 4 сравнения во время t12-3. Следовательно, сигнал VRMP, имеющий потенциал, варьирующийся согласно линейно изменяющейся форме D сигнала, может ускорять распределение по времени, когда значение сигнала для защелкивающего сигнала LATCH изменяется по сравнению с сигналом VRMP, имеющим потенциал, варьирующийся согласно линейно изменяющейся форме C сигнала.

[0097] Во время t13-1 потенциал сигнала VRMP достигает потенциала RMP_end2. В это время управляющий импульс PRMP_EN задается равным L-уровню, в результате чего потенциал сигнала VRMP прекращает варьирование. Дополнительно во время t13-1 управляющий импульс PRMP_STS задается равным L-уровню и управляющий импульс PRMP_REF задается равным H-уровню. В случае если потенциал сигнала VRMP варьируется согласно линейно изменяющейся форме C сигнала, потенциал достигает потенциала RMP_end1 во время t13-1. Следовательно, даже если потенциал между потенциалом RMP_end2 и потенциалом RMP_end1 подается на входной контактный вывод INP схемы 30 дифференциального усиления, значение сигнала для защелкивающего сигнала LATCH может быть изменено посредством принудительного варьирования потенциала сигнала VRMP согласно линейно изменяющейся форме D сигнала.

[0098] Значение величины RMP_off2 смещения в третьем примерном варианте осуществления может быть задано произвольно. В одном варианте осуществления взаимосвязь абсолютных величин между потенциалами, соответственно подаваемыми на входные контактные выводы INP и INN схемы 30 дифференциального усиления, обращается во время между временем t11-1 и временем t13-1. Если потенциал, подаваемый на входной контактный вывод INP, уже меньше потенциала, подаваемого на входной контактный вывод INN во время t11-1, взаимосвязь абсолютных величин не может быть изменена в течение периода, в котором варьируется сигнал VRMP.

[0099] Чтобы не допускать этого случая, например, оптический черный пиксель (в дальнейшем называемый "OB-пикселем") может подготавливаться посредством блокирования света в части пикселей, размещаемых во множестве строк и множестве столбцов, и значение величины RMP_off2 смещения может задаваться на основе сигнала, выведенного из OB-пикселя. Сигнал, выведенный из OB-пикселя, является сигналом, содержащим составляющую шума пикселя 100. Другими словами, OB-пиксель выводит сигнал, имеющий потенциал, практически идентичный потенциалу опорного пиксельного сигнала. Составляющая шума накладывается на сигнал изображения, выведенный из пикселя 100. Поскольку пиксельный сигнал PIXOUT является сигналом на основе электрического заряда, потенциал сигнала изображения, в общем, меньше вследствие составляющей шума, накладываемой на него, по сравнению с опорным пиксельным сигналом. Следовательно, можно уменьшать вероятность того, что значение сигнала для защелкивающего сигнала LATCH может не иметь изменения в течение периода от времени t11-1 до времени t13-1 посредством задания значения величины RMP_off2 смещения на основе потенциала сигнала, выведенного из OB-пикселя.

[0100] Дополнительно помимо сигнала, выведенного из OB-пикселя, величина RMP_off смещения может задаваться на основе значения сигнала N-сигнала, обнаруженного посредством аналого-цифрового преобразования, выполняемого до времени t0, проиллюстрированного на фиг. 10 (например, аналого-цифрового преобразования, выполняемого для строки перед строкой пикселя 100, для которой выполняется аналого-цифровое преобразование на фиг. 10).

[0101] Третий примерный вариант осуществления описан на основе примера, в котором потенциал сигнала VRMP варьируется до потенциала RMP_end2 согласно линейно изменяющейся форме D сигнала. Тем не менее потенциал сигнала VRMP может варьироваться до потенциала RMP_end1, хотя сигнал VRMP имеет линейно изменяющуюся форму D сигнала. Другими словами, управляющий импульс PRMP_EN может задаваться равным L-уровню во время 12-2. В этом случае период аналого-цифрового преобразования может быть уменьшен посредством периода от времени t13-1 до времени 12-2.

[0102] Дополнительно источник 55 тока в третьем примерном варианте осуществления может быть источником тока переменной величины. Источник 55 тока, выполненный как источник тока переменной величины, может изменять наклон сигнала VRMP. Изменение наклона сигнала VRMP может изменять усиление сигнала, выведенного из модуля 11 аналого-цифрового преобразования, относительно пиксельного выходного сигнала PIXOUT.

[0103] Четвертый примерный вариант осуществления описывается со ссылкой на чертежи, при этом внимание обращается на отличия от первого примерного варианта осуществления. Фиг. 11A является блок-схемой, иллюстрирующей пример устройства формирования изображений согласно четвертому примерному варианту осуществления. На фиг. 11A компоненты, которые функционируют аналогично компонентам, проиллюстрированным на фиг. 1, указываются посредством ссылочных позиций, идентичных ссылочным позициям на фиг. 1.

[0104] Устройство формирования изображений согласно четвертому примерному варианту осуществления выполнено так, что пиксельный выходной сигнал PIXOUT, выведенный из пиксельной матрицы 1, выводится в модуль 4 сравнения через модуль 13 усиления. Схема 5 вывода линейно изменяющихся сигналов в четвертом примерном варианте осуществления может быть сконфигурирована аналогично первому примерному варианту осуществления.

[0105] Фиг. 11B является эквивалентной принципиальной схемой, иллюстрирующей подробности модуля 13 усиления. Модуль 13 усиления включает в себя схему 13-1 дифференциального усиления, входную емкость C0 модуля усиления и емкость C1 обратной связи. Схема 13-1 дифференциального усиления соответствует второй схеме дифференциального усиления. Пиксельный выходной сигнал PIXOUT вводится на инвертирующий контактный вывод схемы 13-1 дифференциального усиления через входную емкость C0 модуля усиления. Емкость C1 обратной связи электрически подключена к выходному контактному выводу схемы 13-1 дифференциального усиления через переключатель SW2 на два направления с усилением. Дополнительно емкость C1 обратной связи электрически подключена к инвертирующему контактному выводу схемы 13-1 дифференциального усиления.

[0106] Термин "выходной сигнал AmpOUT модуля усиления" используется как означающий сигнал, выведенный из схемы 13-1 дифференциального усиления. Усиление выходного сигнала AmpOUT модуля усиления относительно пиксельного выходного сигнала PIXOUT предоставляется на основе отношения входной емкости C0 модуля усиления и суммы значения емкости для емкости C1 обратной связи, которая электрически подключена к выходному контактному выводу схемы 13-1 дифференциального усиления. В дальнейшем в этом документе описание приводится при условии, что переключатель SW2 на два направления с усилением включен. Когда переключатель SW1 схемы 13-1 дифференциального усиления задается в проводящее состояние, потенциалы схемы 13-1 дифференциального усиления и входной емкости C0 модуля усиления сбрасываются. Переключатель SW1 включается, когда импульс Amp_rst сброса модуля усиления задается равным H-уровню, и выключается, когда импульс Amp_rst сброса модуля усиления задается равным L-уровню.

[0107] Фиг. 11C иллюстрирует структуру емкости C1 обратной связи и интегральной емкости 51 согласно четвертому примерному варианту осуществления. В четвертом примерном варианте осуществления как емкость C1 обратной связи модуля 13 усиления, так и интегральная емкость 51 схемы 5 вывода линейно изменяющихся сигналов используют диффузионную емкость. Диффузионная емкость имеет структуру "металл-диэлектрик-полупроводник" (МДП). Электрод на стороне затвора (GATE) является металлом или поликристаллическим кремнием. Электрод на стороне диффузионного слоя (N+ и N) является полупроводниковой областью n-типа. Карман p-типа (PWL) является полупроводниковой областью p-типа. Поле (FLD) является изолирующим слоем.

[0108] Дополнительно емкость C1 обратной связи электрически подключена в любом из своего электрода на стороне затвора и электрода на стороне диффузионного слоя к входному контактному выводу схемы 13-1 дифференциального усиления. Другой электрод электрически подключен к выходному контактному выводу схемы 13-1 дифференциального усиления. Дополнительно интегральная емкость 51 электрически подключена в своем электроде, идентичном электроду емкости C1 обратной связи, электрически подключенной к входному контактному выводу схемы 13-1 дифференциального усиления, к входному контактному выводу схемы 50 дифференциального усиления. Другими словами, емкость C1 обратной связи электрически подключена в униполярном электроде к схеме 13-1 дифференциального усиления. Например, в случае если емкость C1 обратной связи электрически подключена в своем электроде на стороне затвора к входному контактному выводу схемы 13-1 дифференциального усиления, интегральная емкость 51 также электрически подключена в своем электроде на стороне затвора к входному контактному выводу схемы 50 дифференциального усиления. Другой электрод интегральной емкости 51 электрически подключен к выходному контактному выводу схемы 50 дифференциального усиления.

[0109] Таким образом, емкость C1 обратной связи и интегральная емкость 51 имеют аналогичную конфигурацию, и их униполярные электроды электрически подключены к входным контактным выводам схем 13-1 и 50 дифференциального усиления соответственно. Аналогично другие униполярные электроды электрически подключены к выходным контактным выводам схем 13-1 и 50 дифференциального усиления соответственно. Как результат можно унифицировать зависимость значения емкости от напряжения между модулем 13 усиления и схемой 5 вывода линейно изменяющихся сигналов. Дополнительно можно унифицировать линейность, которая представляет собой взаимосвязь выходного сигнала с входным сигналом, между модулем 13 усиления и схемой 5 вывода линейно изменяющихся сигналов посредством конфигурирования схем из схем 13-1 и 50 дифференциального усиления аналогичным образом. Соответственно, можно унифицировать линейность между выходным сигналом AmpOUT модуля усиления и сигналом VRMP.

[0110] Фиг. 12 является функциональной временной диаграммой, иллюстрирующей пример работы устройства формирования изображений, проиллюстрированного на фиг. 11A. Операция, когда пиксель 100 выводит пиксельный выходной сигнал PIXOUT, может быть выполнена аналогично функциональному распределению по времени, проиллюстрированному на фиг. 5. Предоставляется последующее описание, в котором внимание обращается, главным образом, на отличия от функционального распределения по времени, проиллюстрированного на фиг. 5.

[0111] Во время t1 импульс Amp_rst сброса модуля усиления задается равным H-уровню, тем самым сбрасывая потенциалы схемы 13-1 дифференциального усиления и входной емкости C0 модуля усиления. После этого импульс Amp_rst сброса модуля усиления задается равным L-уровню. Как результат электрический заряд на основе потенциала пиксельного выходного сигнала PIXOUT, когда импульс Amp_rst сброса модуля усиления задается равным L-уровню, хранится во входной емкости C0 модуля усиления.

[0112] Во время t2 опорный пиксельный сигнал выводится в вертикальную выходную линию 3. Потенциал в качестве разности между потенциалом, хранимым во входной емкости C0 модуля усиления, и пиксельным опорным сигналом подается на инвертирующий контактный вывод схемы 13-1 дифференциального усиления. Этот потенциал усиливается и затем выводится в качестве выходного сигнала AmpOUT модуля усиления. Дополнительно управляющий импульс PRMP_RST изменяется с H-уровня на L-уровень.

[0113] Во время t3 импульс COMPRST сброса модуля сравнения задается равным H-уровню и затем задается равным L-уровню. Как результат выходной сигнал AmpOUT модуля усиления во время t3 хранится во входной емкости 34 модуля сравнения. Другими словами, составляющая смещения модуля 13 усиления каждого столбца хранится во входной емкости 34 сравнения в это время. Опорный сигнал VREF усиления хранится во входной емкости 33 сравнения аналогично первому примерному варианту осуществления.

[0114] Во время t4 управляющий импульс PRMP_STN задается равным H-уровню. В четвертом примерном варианте осуществления пиксельный выходной сигнал PIXOUT подается в модуль 4 сравнения после того, как модуль 13 усиления обращает и усиливает пиксельный выходной сигнал PIXOUT. Следовательно, в ходе аналого-цифрового преобразования наклон изменения сигнала VRMP наклоняется в противоположном направлении относительно наклона в первом примерном варианте осуществления. Соответственно, сигнал VRMP также сдвигается к потенциалу RMP_st начала линейного изменения в противоположном направлении относительно направления в первом примерном варианте осуществления.

[0115] Во время t5 управляющий импульс PRMP_EN задается равным H-уровню. Как результат потенциал сигнала VRMP начинает варьироваться в зависимости от времени. Как описано выше, направление изменения сигнала VRMP является противоположным направлением относительно первого примерного варианта осуществления. Другими словами, потенциал варьируется в направлении повышения в зависимости от времени.

[0116] После этого операции в моменты t6 и t7 времени могут выполняться аналогично операциям в моменты t6 и t7 времени в первом примерном варианте осуществления, проиллюстрированном на фиг. 5, соответственно.

[0117] Во время t8 импульс PTX переноса задается равным H-уровню. Затем сигнал изображения выводится в вертикальную выходную линию 3. Потенциал, соответствующий разности между сигналом изображения и потенциалом, хранимым во входной емкости C0 модуля усиления, подается на инвертирующий контактный вывод схемы 13-1 дифференциального усиления. Схема 13-1 дифференциального усиления выводит выходной сигнал AmpOUT модуля усиления, сформированный посредством обращения и усиления входного потенциала. Термин "усиленный сигнал изображения" используется как означающий выходной сигнал AmpOUT модуля усиления в это время. Потенциал, соответствующий разности между усиленным сигналом изображения и потенциалом, хранимым во входной емкости 34 модуля сравнения, подается на входной контактный вывод INN схемы 30 дифференциального усиления. Следовательно, можно вычитать составляющую смещения модуля 13 усиления каждого столбца из усиленного сигнала изображения.

[0118] Операции в моменты t9-t13 времени могут быть выполнены аналогично операциям в моменты t9-t13 времени в первом примерном варианте осуществления, проиллюстрированном на фиг. 5, соответственно. Таким образом, можно выполнять аналого-цифровое преобразование для сигнала, который формирует модуль 13 усиления, посредством обращения и усиления пиксельного выходного сигнала PIXOUT.

[0119] Модуль 13 усиления в четвертом примерном варианте осуществления включает в себя емкость C1 обратной связи. Модуль 13 усиления конфигурируется аналогично схеме 61 усиления с емкостной обратной связью из схемы 5 вывода линейно изменяющихся сигналов. Емкость C1 обратной связи и интегральная емкость 51 имеют аналогичную конфигурацию, и их униполярные электроды электрически подключены к входным контактным выводам схем 13-1 и 50 дифференциального усиления соответственно. Аналогично, другие их униполярные электроды также электрически подключены к выходным контактным выводам схем 13-1 и 50 дифференциального усиления соответственно. Как результат можно унифицировать зависимость от напряжения, с которой емкость зависит от напряжения включения между модулем 13 усиления и схемой 5 вывода линейно изменяющихся сигналов. Дополнительно можно унифицировать линейность, которая представляет собой взаимосвязь выходного сигнала с входным сигналом, между модулем 13 усиления и схемой 5 вывода линейно изменяющихся сигналов посредством конфигурирования соответствующих схем из схем 13-1 и 50 дифференциального усиления аналогичным образом. Соответственно, можно унифицировать линейность между выходным сигналом AmpOUT модуля усиления и сигналом VRMP. Как результат можно поддерживать точность аналого-цифрового преобразования, которая в противном случае должна снижаться вследствие разности в линейности между выходным сигналом AmpOUT модуля усиления и сигналом VRMP.

[0120] Четвертый примерный вариант осуществления описан на основе примера, в котором емкость C1 обратной связи и интегральная емкость 51 конфигурируются как МДП-емкости в качестве примера. В качестве другого примера, каждая из емкости C1 обратной связи и интегральной емкости 51 может конфигурироваться как емкость структуры "металл-диэлектрик-металл" (MIM) или емкость структуры "поликристаллический кремний-поликристаллический кремний", включающая в себя два слоя поликристаллического кремния с размещенным между ними изолирующим слоем. Также в данном примере емкость C1 обратной связи и интегральная емкость 51 имеют аналогичную конфигурацию и униполярные электроды электрически подключены к входным и выходным контактным выводам схем 13-1 и 50 дифференциального усиления соответственно. Их аналогичное конфигурирование означает, что, например, емкость C1 обратной связи и интегральная емкость 51 конфигурируются как MIM-емкости. Можно унифицировать зависимость значения емкости от напряжения между модулем 13 усиления и схемой 5 вывода линейно изменяющихся сигналов посредством их конфигурирования таким образом.

[0121] В качестве примера описывается пятый примерный вариант осуществления, в котором вышеописанное устройство формирования изображений применяется к системе формирования изображений. Примеры систем формирования изображений включают в себя цифровой фотоаппарат, цифровую записывающую видеокамеру и камеру для слежения. Фиг.13 схематично иллюстрирует цифровой фотоаппарат, к которому применяется устройство формирования изображений, в качестве примера систем формирования изображений.

[0122] Ссылаясь на фиг. 13, перегородка 151 защищает линзу 152. Линза 152 фокусирует оптическое изображение объекта на устройстве 154 формирования изображений. Диафрагма 153 варьирует количество света, пропущенное через линзу 152. Модуль 155 обработки выходных сигналов обрабатывает выходной сигнал, выведенный из устройства 154 формирования изображений. Модуль 155 обработки выходных сигналов включает в себя модуль обработки цифровых сигналов и при необходимости выполняет различные типы коррекций и сжатий для сигнала, выведенного из устройства 154 формирования изображений, чтобы выводить сигнал.

[0123] Ссылаясь на фиг. 13, буферное запоминающее устройство 156 временно сохраняет данные изображений. Интерфейсный модуль 158 предоставляет запись и считывание с носителя записи. Носитель 159 записи, например полупроводниковое запоминающее устройство, съемно присоединен к цифровому фотоаппарату, и сформированные данные изображений записываются и считываются из носителя 159 записи. Интерфейсный модуль 157 предоставляет связь, например, с внешним компьютером. Общий модуль 1510 управления/вычисления выполняет различные типы вычислений и управляет всем цифровым фотоаппаратом. Модуль 1511 генерирования тактовых импульсов выводит различные типы синхронизирующих сигналов в устройство 154 формирования изображений и модуль 155 обработки выходных сигналов. Тем не менее например, синхронизирующий сигнал может вводиться извне, и система формирования изображений должна включать в себя только, по меньшей мере, устройство 154 формирования изображений и модуль 155 обработки выходных сигналов для обработки выходного сигнала, выведенного из устройства 154 формирования изображений.

[0124] Таким образом, система формирования изображений согласно пятому примерному варианту осуществления может выполнять операцию формирования изображений посредством использования устройства 154 формирования изображений.

[0125] Хотя раскрытие сущности описано со ссылкой на примерные варианты осуществления, следует понимать, что раскрытие сущности не ограничено раскрытыми примерными вариантами осуществления. Объем нижеприведенной формулы изобретения должен согласовываться с самой широкой интерпретацией так, что он охватывает все модификации, эквивалентные структуры и функции.

Изобретение относится к области вывода линейно изменяющихся сигналов, аналого-цифрового преобразования этого сигнала и формирования изображений. Достигаемый технический результат - возможность выводить линейно изменяющиеся сигналы, имеющие потенциал, варьирующийся в зависимости от времени. Устройство содержит модуль подачи напряжения, выполненный с возможностью подавать множество напряжений, имеющих разные амплитуды, модуль подачи тока, интегральную схему, выполненную с возможностью выводить линейно изменяющиеся сигналы, и емкостной элемент, при этом модуль подачи напряжения подключен к одному контактному выводу емкостного элемента, а интегральная схема и модуль подачи тока подключены к другому контактному выводу емкостного элемента. 12 н. и 8 з.п. ф-лы, 19 ил.

1. Схема вывода линейно изменяющихся сигналов, выполненная с возможностью выводить линейно изменяющийся сигнал, имеющий потенциал, варьирующийся в зависимости от времени, причем схема содержит:

- модуль подачи напряжения, выполненный с возможностью подавать множество напряжений, имеющих разные амплитуды;

- модуль подачи тока;

- интегральную схему, выполненную с возможностью выводить линейно изменяющийся сигнал; и

- емкостной элемент,

при этом модуль подачи напряжения подключен к одному контактному выводу емкостного элемента и

при этом интегральная схема и модуль подачи тока подключены к другому контактному выводу емкостного элемента.

2. Схема вывода линейно изменяющихся сигналов по п.1, в которой интегральная схема включает в себя модуль дифференциального усиления и интегральную емкость, расположенную на пути обратной связи, соединяющем выходной контактный вывод и входной контактный вывод модуля дифференциального усиления,

при этом линейно изменяющийся сигнал выводится из выходного контактного вывода модуля дифференциального усиления.

3. Схема вывода линейно изменяющихся сигналов по п.2, в которой модуль дифференциального усиления включает в себя второй входной контактный вывод, в который вводится опорное напряжение, в дополнение к упомянутому входному контактному выводу, и

при этом модуль подачи тока подключен к упомянутому входному контактному выводу.

4. Схема вывода линейно изменяющихся сигналов по п.2, в которой модуль подачи тока включает в себя источник тока, первый транзистор и второй транзистор,

при этом источник тока и упомянутый входной контактный вывод подключены друг к другу через первый транзистор и

при этом модуль подачи напряжения и источник тока подключены друг к другу через второй транзистор и источник тока подключен к управляющим электродам соответственных первого и второго транзисторов.

5. Способ для возбуждения схемы вывода линейно изменяющихся сигналов, выполненной с возможностью выводить линейно изменяющийся сигнал, имеющий потенциал, варьирующийся в зависимости от времени, причем схема содержит модуль подачи тока, интегральную схему и емкостной элемент, при этом способ содержит этапы, на которых:

- сдвигают потенциал сигнала, выведенного из интегральной схемы, от первого потенциала к потенциалу, отличающемуся от первого потенциала, посредством изменения значения напряжения, которое должно подаваться в интегральную схему через емкостной элемент;

- подают ток из модуля подачи тока в интегральную схему и емкостной элемент; и

- выводят линейно изменяющийся сигнал, который имеет потенциал, варьирующийся относительно потенциала, отличающегося от первого потенциала, из интегральной схемы.

6. Способ для возбуждения схемы вывода линейно изменяющихся сигналов по п.5, при этом схема дополнительно содержит модуль подачи напряжения, выполненный с возможностью подавать множество значений напряжения в интегральную схему через емкостной элемент,

при этом интегральная схема включает в себя модуль дифференциального усиления и интегральную емкость, расположенную на пути обратной связи, соединяющем выходной контактный вывод и входной контактный вывод модуля дифференциального усиления,

при этом линейно изменяющийся сигнал выводится из выходного контактного вывода модуля дифференциального усиления,

при этом модуль дифференциального усиления включает в себя второй входной контактный вывод, на который вводится опорное напряжение, в дополнение к упомянутому входному контактному выводу,

при этом модуль подачи тока включает в себя источник тока, первый транзистор и второй транзистор,

при этом источник тока и упомянутый входной контактный вывод подключены друг к другу через первый транзистор и

при этом модуль подачи напряжения и источник тока подключены друг к другу через второй транзистор и источник тока совместно активирует управляющие электроды соответственного первого транзистора и второго транзистора.

7. Способ для возбуждения схемы вывода линейно изменяющихся сигналов по п.5, дополнительно содержащий этапы, на которых:

- выводят сигнал, имеющий первый потенциал, из интегральной схемы посредством подачи первого напряжения в емкостной элемент;

- подают любое из множества напряжений, имеющих значения напряжения, отличающиеся друг от друга, которые отличаются от значения напряжения первого напряжения, в емкостной элемент, чтобы выводить сигнал, имеющий потенциал, отличающийся от первого потенциала, из интегральной схемы;

- выводят линейно изменяющийся сигнал, имеющий потенциал, варьирующийся на первую величину варьирования в единицу времени, из интегральной схемы в случае, если подается напряжение, имеющее значение напряжения малой амплитуды, из множества напряжений; и