Изобретение относится к области электросвязи и может быть использовано для поиска и оперативной идентификации информации в сетях передачи данных с коммутацией пакетов и в информационно-справочных (поисковых) системах.

Известны устройства поиска информации - см., например, Авт.Св. СССР №1711185 «Устройство поиска информации» МПК G06F 15/40, опубликованное 05.04.89 и Патент РФ №2115952 «Устройство поиска информации» МПК G06F 17/40, опубликованное 20.07.98.

Известные аналоги содержат регистры границ, суммирующие и вычитающие счетчики, схемы сравнения, блоки памяти, блоки вычисления и ряд других элементов, позволяющих осуществлять поиск информации. В ходе приема цифрового сообщения и поиска в нем определенной цифровой последовательности необходимо определить его параметры и соответствие последовательности передачи правилам обмена данными, установленным для данного протокола. Известные аналоги не в полном объеме выполняют эти требования.

В первом аналоге недостатком является низкий уровень достоверности и вероятности идентификации коммуникационного протокола (менее 0.3), так как поиск информационных блоков реализован дихотомическим методом без учета наличия допустимой последовательности пакетов.

Во втором аналоге недостатками являются относительно большое время, необходимое для идентификации пакетов (так как идентификация осуществляется путем последовательного анализа значений признаков) и узкая область применения - только для анализа протокола TFTP на предмет соответствия наблюдаемой последовательности пакетов правилам, установленным для данного протокола. Все это ограничивает применение устройств-аналогов для анализа протоколов в современных высокоскоростных вычислительных сетях.

Из известных наиболее близким аналогом (прототипом) по своей технической сущности заявленному устройству является устройство по Патенту РФ №2313128 «Устройство поиска информации» МПК G06F 9/46, опубликованное 20.12.2007 г., бюл. 35.

Устройство-прототип включает N≥2 блоков хранения маски, N блоков селекции, делитель частоты, формирователь временных интервалов, регистр стратегии поиска, блок формирования адреса маски переходов и блок индикации.

В устройстве-прототипе тактовый вход делителя частоты является первым тактовым входом устройства, а выходы «Результат сравнения» блоков селекции соединены с соответствующими входами «Результат сравнения» регистра стратегии поиска и с соответствующими входами «Результат сравнения» блока формирования адреса маски переходов. При этом K-разрядный, где K=(log2N)+1, выход «Код события» блока формирования адреса маски переходов подключен к K-разрядным входам «Код события» регистра стратегии поиска и блока индикации. Входы разрешения записи всех блоков хранения маски соединены между собой и являются входом разрешения записи устройства. Соответствующие разряды L-разрядных информационных входов, где L≥2, блоков селекции объединены и являются соответствующими разрядами L-разрядного информационного входа устройства. Первые L-разрядные входы «Маска 1» и «Маска 2» j-го блока хранения маски, где j=1, 2, …, N, являются j-ми первыми L-разрядными входами соответственно «Маска 1» и «Маска 2» устройства. Вторые L-разрядные выходы «Маска 1» и «Маска 2» j-го блока хранения маски подключены к соответствующим вторым L-разрядным входам «Маска 1» и «Маска 2» j-го блока селекции. Выход делителя частоты соединен с тактовым входом формирователя временных интервалов. Вход «Начальный сброс» формирователя временных интервалов соединен с входом «Начальный сброс» блока формирования адреса маски переходов и является входом «Начальный сброс» устройства. При этом, M-разрядный вход «Код времени ожидания» формирователя временных интервалов, где М≥2 - разрядность кода времени ожидания, является M-разрядным входом «Код времени ожидания» устройства, а выход формирователя временных интервалов соединен с входом «Сброс» блока формирования адреса маски переходов. Сигнальный выход регистра стратегии поиска соединен с сигнальными входами формирователя временных интервалов и блока формирования адреса маски переходов. K-разрядный адресный вход, управляющий вход, N-разрядный информационный вход и разрешающий вход регистра стратегии поиска являются соответственно K-разрядным адресным входом, управляющим входом, N-разрядным информационным входом и разрешающим входом устройства. Входы «Выбор кристалла» и «Чтение/запись» регистра стратегии поиска являются соответственно входами «Выбор кристалла» и «Чтение/запись» устройства. N-разрядный вход «Правило завершения поиска» и выход «Результат поиска» блока индикации являются соответственно N-разрядным входом «Правило завершения поиска» и выходом «Результат поиска» устройства.

Такая схема, по сравнению с устройствами-аналогами, позволяет расширить область применения и быстродействие анализа входящих пакетов устройства-прототипа за счет идентификации пакетов путем параллельного анализа значений признаков идентификации и контроля последовательности обмена ими на предмет соответствия любым, априорно заданным правилам.

Однако, прототип имеет недостаток - относительно низкую вероятность своевременного поиска информации в условиях непрерывной динамики смены состояний разно-приоритетных запросов на поиск информации и с учетом влияющих факторов. Это связано с тем, что устройство-прототип не позволяет динамически корректировать максимальное время поиска информации, различного как по приоритету, так и по динамично изменяющимся требованиям к своевременности поиска информации в рамках поисковых запросов различного приоритета.

Данное устройство-прототип позволяет задавать максимально допустимый интервал времени, в течение которого ожидается очередной блок двоичной информации (БДИ), заданный сценарием поиска, но осуществляет поиск информации без ограничения максимального времени поиска, до тех пор, пока во входящем потоке данных не будет обнаружена заданная сценарием поиска последовательность БДИ для каждого конкретного поискового запроса, в то время как большое количество запросов на поиск информации, поступающих от пользователей реальной - многофункциональной, сложной и управляемой информационно-справочной (поисковой) системы, могут в динамике функционирования изменять свое состояние (могут динамично изменяться требования к качеству, объему и своевременности поиска информации в рамках поисковых запросов различного приоритета, например, текущие требования к значениям максимального времени поиска конкретной информации), под влиянием управляющих воздействий на информационно-справочную систему, исходя из текущих требований абонентов или под влиянием внешних факторов. Это исключает применение прототипа для своевременного и динамического поиска информации в реальных условиях, когда в динамике функционирования устройства поиска информации в рамках управляемой информационно-справочной (поисковой) системы объективно изменяются во времени не только свойства самой системы и окружающей среды, но и требования к качеству и своевременности реализации поиска информации [1-5].

Под «реализацией поисковых запросов» понимается совокупность действий информационно-справочной (поисковой) системы, включающая выборку запроса на поиск информации из очереди, выделение этому запросу ресурса и собственно поиск информации в соответствии с заданным сценарием поиска, а также проведение завершающих операций. Поисковый запрос - посылка сигнала на поиск, инициирующего ответ.

Под «приоритетом» понимается число, предписанное задаче, процессу или операции, определяющее очередность (место в очереди) их выполнения или обслуживания. Чем меньше число, тем выше уровень приоритета. Управлять приоритетностью поступающих поисковых запросов возможно путем изменения места в очереди и (или) динамической коррекции (в случае необходимости) максимального времени поиска.

Под «состоянием разноприоритетных запросов на поиск информации» понимается набор значений параметров, характеризующих эти запросы (их приоритет - место в очереди и соответствующее приоритету максимальное время поиска информации для каждого сценария поиска, поискового запроса) в конкретный момент времени.

Под «максимальным временем поиска» понимается максимальное время реализации поискового запроса в соответствии с заданным сценарием. Код максимального времени поиска Tn для конкретного заданного сценария, конкретного набора масок переходов - множества типов БДИ, входящих в состав конкретного сценария (где n=1, 2, …, N -соответствующий номер n-го сценария, а N - общее число типов БДИ (масок переходов)), запоминается, затем формируется сигнал поискового запроса и из таких сигналов запросов формируется очередь поиска.

Целью заявленного технического решения является создание устройства поиска информации, обеспечивающего повышение вероятности своевременного поиска информации в условиях, присущих реальному процессу функционирования современных сетей передачи данных с коммутацией пакетов, современных информационно-справочных (поисковых) систем - в условиях непрерывной динамики смены состояний разноприоритетных запросов на поиск информации и с учетом влияющих факторов, устройства, способного своевременно реализовывать поисковые запросы с учетом, как динамики управляющих воздействий или внешних факторов, так и изменяющихся во времени текущих требований абонентов к своевременности поиска информации, на основе динамически корректируемых значений (границ) максимального времени поиска для каждого поискового запроса.

Указанная цель достигается тем, что в известное устройство поиска информации, содержащее N≥2 блоков хранения маски, N блоков селекции, делитель частоты, формирователь временных интервалов, регистр стратегии поиска, блок формирования адреса маски переходов и блок индикации, дополнительно включены N идентичных селекционных контроллеров времени поиска, предназначенных для дешифровки, дополнительного сравнения и контроля S-разрядного кода, обуславливающего новое значение максимального времени поиска для каждого конкретного поискового запроса, главный контроллер времени поиска, предназначенный для динамической коррекции значений максимального времени поиска для каждого поискового запроса и генератор тактовых импульсов, предназначенный для выработки синхронизирующей последовательности импульсов. При этом тактовый вход делителя частоты является первым тактовым входом устройства, а выход делителя частоты соединен с тактовым входом формирователя временных интервалов, при этом K-разрядный, где K=(log2N)+1, выход «Код события» блока формирования адреса маски переходов подключен к K-разрядным входам «Код события» регистра стратегии поиска и блока индикации соответственно. Входы разрешения записи N блоков хранения маски объединены и являются входом разрешения записи устройства, L-разрядные информационные входы, где L≥2, N блоков селекции объединены и являются Z-разрядным информационным входом устройства. При этом первые L-разрядные входы «Маска 1» и «Маска 2» N блоков хранения маски, являются первыми L-разрядными входами соответственно «Маска 1» и «Маска 2» устройства. Вторые L-разрядные выходы «Маска 1» и «Маска 2» N блоков хранения маски подключены к вторым Z-разрядным входам «Маска 1» и «Маска 2» соответствующих блоков селекции. Вход «Начальный сброс» формирователя временных интервалов соединен с входом «Начальный сброс» блока формирования адреса маски переходов и является входом «Начальный сброс» устройства. При этом, M-разрядный вход «Код времени ожидания» формирователя временных интервалов, где М≥2 - разрядность кода времени ожидания, является M-разрядным входом «Код времени ожидания» устройства, а выход формирователя временных интервалов соединен с входом «Сброс» блока формирования адреса маски переходов, сигнальный выход регистра стратегии поиска соединен с сигнальными входами формирователя временных интервалов и блока формирования адреса маски переходов. Причем K-разрядный адресный вход, управляющий вход, N-разрядный информационный вход и разрешающий вход регистра стратегии поиска являются соответственно K-разрядным адресным входом, управляющим входом, N-разрядным информационным входом и разрешающим входом устройства, входы «Выбор кристалла» и «Чтение/запись» регистра стратегии поиска являются соответственно входами «Выбор кристалла» и «Чтение/запись» устройства, N-разрядный вход «Правило завершения поиска» и выход «Результат поиска» блока индикации являются соответственно N-разрядным входом «Правило завершения поиска» и выходом «Результат поиска» устройства. Причем выход «Результат сравнения» n-го блока селекции, где n=1, 2, …, N, соединен с входом «Результат сравнения» n-го селекционного контроллера времени поиска, выход «Результат сравнения» которого соединен с n-м входом «Результат сравнения» регистра стратегии поиска и с n-м входом «Результат сравнения» блока формирования адреса маски переходов. При этом выход генератора тактовых импульсов подключен к тактовому входу n-ого блока селекции, вход «Обнуление» которого является n-м входом «Обнуление» устройства, причем S-разрядный корректирующий вход n-ого блока селекции объединен с S-разрядным проверочным входом n-ого селекционного контроллера времени поиска и подключен к n-ому S-разрядному выходу главного контроллера времени поиска, N S-разрядных входов которого являются соответствующими N S-разрядными входами «Коррекция максимального времени поиска» устройства.

Селекционный контроллер времени поиска (СКВП) состоит из дешифратора корректированного кода максимального времени поиска и регистра сравнения-коррекции максимального времени поиска. При этом S-разрядный вход дешифратора корректированного кода максимального времени поиска является S-разрядным проверочным входом селекционного контроллера времени поиска. Причем проверочный выход дешифратора корректированного кода максимального времени поиска подключен к проверочному входу регистра сравнения-коррекции максимального времени поиска, сигнальные вход и выход которого являются соответственно сигнальным входом и выходом «Результат сравнения» селекционного контроллера времени поиска.

Главный контроллер времени поиска состоит из регистрирующего элемента времени поиска и элемента хранения нового значения времени поиска, при этом N S-разрядных входов регистрирующего элемента времени поиска являются соответствующими N S-разрядными входами главного контроллера времени поиска, причем N S-разрядных выходов регистрирующего элемента времени поиска подключены к соответствующим N S-разрядным входам элемента хранения нового значения времени поиска, N S-разрядных выходов которого являются соответствующими Генератор тактовых импульсов, входящий в общую структурную схему, является серийно выпускаемым генератором.

Блок селекции (БС) состоит из первой и второй групп двухвходовых элементов И по L элементов в каждой группе, компаратора, инвертора, счетчика, трехвходового элемента И и корректирующего регистра. При этом инверсный выход счетчика подключен к первому входу трехвходового элемента И, соединен с инверсным выходом инвертора и является выходом «Результат сравнения» блока селекции. Третий вход трехвходового элемента И является тактовым входом блока селекции, а выход трехвходового элемента И подключен к счетному входу счетчика, инверсный вход разрешения счета счетчика соединен с выходом равенства компаратора и подключен к второму входу трехвходового элемента И и к входу инвертора, при этом S-разрядный вход корректирующего регистра является S-разрядным корректирующим входом блока селекции, a S выходов корректирующего регистра подключены к соответствующим S информационным входам счетчика. Причем вход сброса счетчика является входом «Обнуление» блока селекции, при этом l-ый, где l=1, 2, …, L, вход первой группы информационных входов компаратора соединен с соответствующим выходом l-го двухвходового элемента И первой группы двухвходовых элементов И, а l-ый вход второй группы информационных входов компаратора соединен с выходом l-го двухвходового элемента И второй группы двухвходовых элементов И. При этом первый вход l-го двухвходового элемента И первой группы двухвходовых элементов И является l-ым разрядом L-разрядного информационного входа блока селекции, второй вход l-го двухвходового элемента И первой группы двухвходовых элементов И соединен с первым входом l-го двухвходового элемента И второй группы двухвходовых элементов И и является l-ым разрядом второго L-разрядного входа «Маска 1» блока селекции, а второй вход l-го двухвходового элемента И второй группы двухвходовых элементов И является l-ым разрядом второго L-разрядного входа «Маска 2» блока селекции.

Благодаря новой совокупности существенных признаков, за счет введения N≥2 идентичных селекционных контроллеров времени поиска, главного контроллера времени поиска и генератора тактовых импульсов, обеспечивающих, соответственно, дешифровку, динамическую коррекцию и синхронизацию процессов дешифровки, контроля и коррекции значений (границ) максимального времени поиска для каждого конкретного сценария (поискового запроса), в заявленном устройстве достигается возможность своевременной реализации поисковых запросов с учетом, как динамики управляющих воздействий или внешних факторов, так и изменяющихся во времени текущих требований абонентов к своевременности поиска информации. Достигается возможность, обуславливающая повышение вероятности своевременного поиска информации в условиях, присущих реальному процессу функционирования современных сетей передачи данных с коммутацией пакетов, современных информационно-справочных (поисковых) систем - в условиях непрерывной динамики смены состояний разноприоритетных запросов на поиск информации и с учетом влияющих факторов.

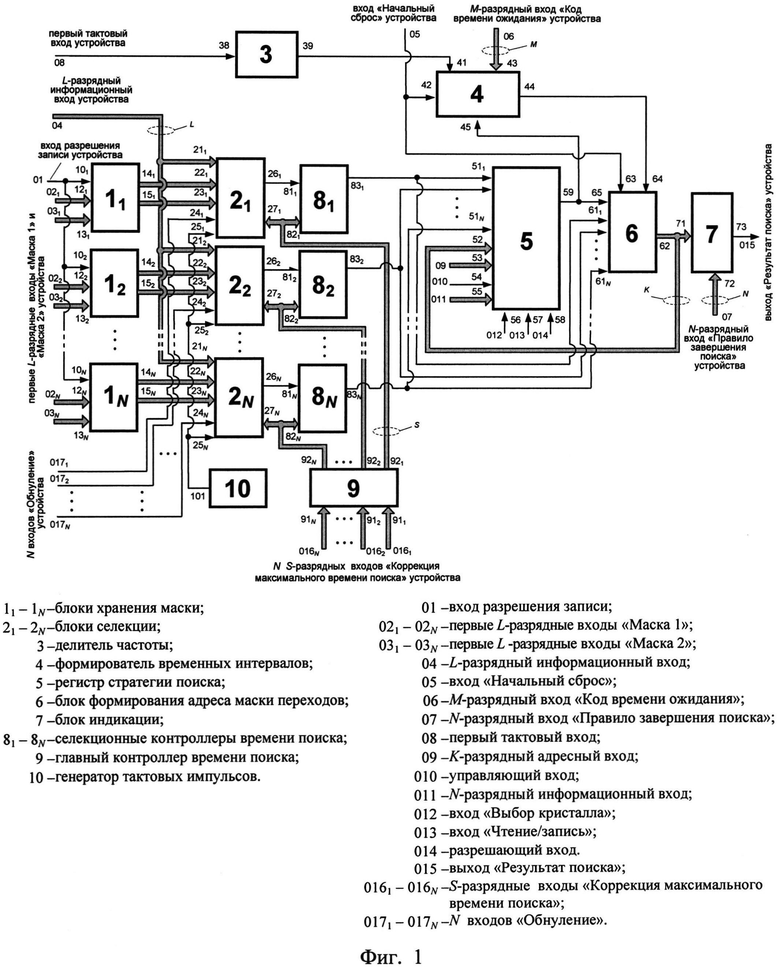

Заявленное устройство поясняется чертежами, на которых представлены:

на фиг. 1 - структурная схема устройства поиска информации;

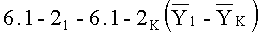

на фиг. 2 - структурная схема n-го

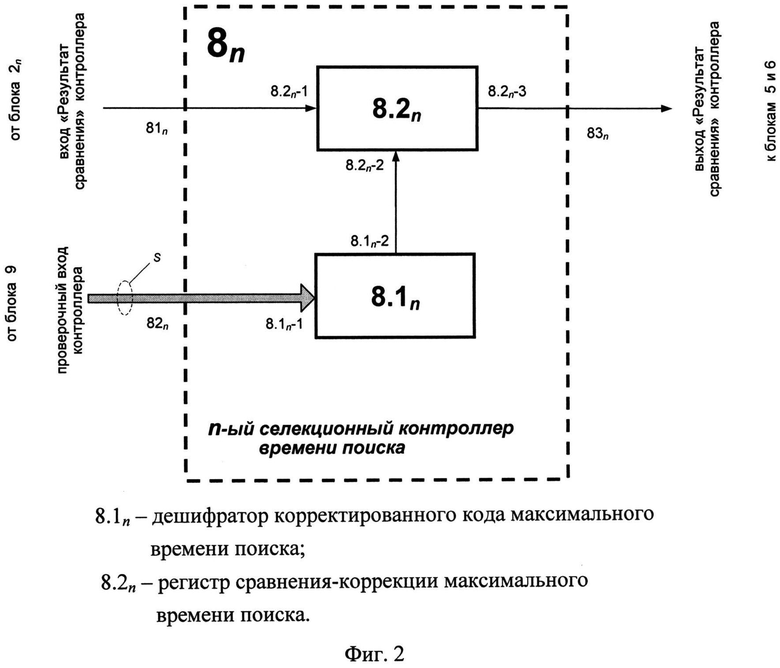

на фиг. 3 - структурная схема главного контроллера времени поиска;

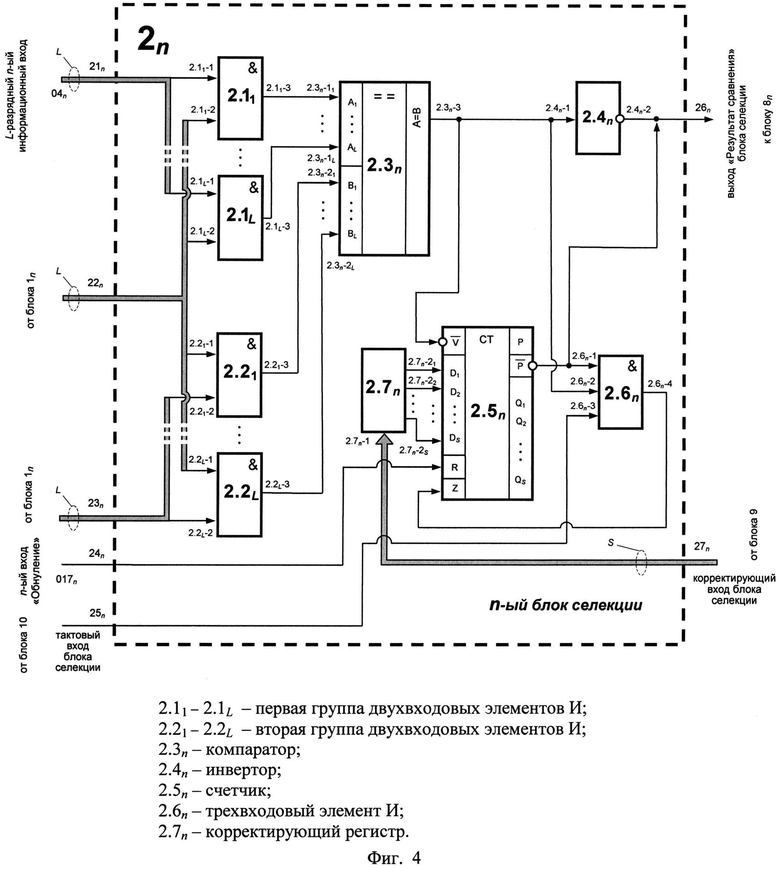

на фиг. 4 - структурная схема n-го

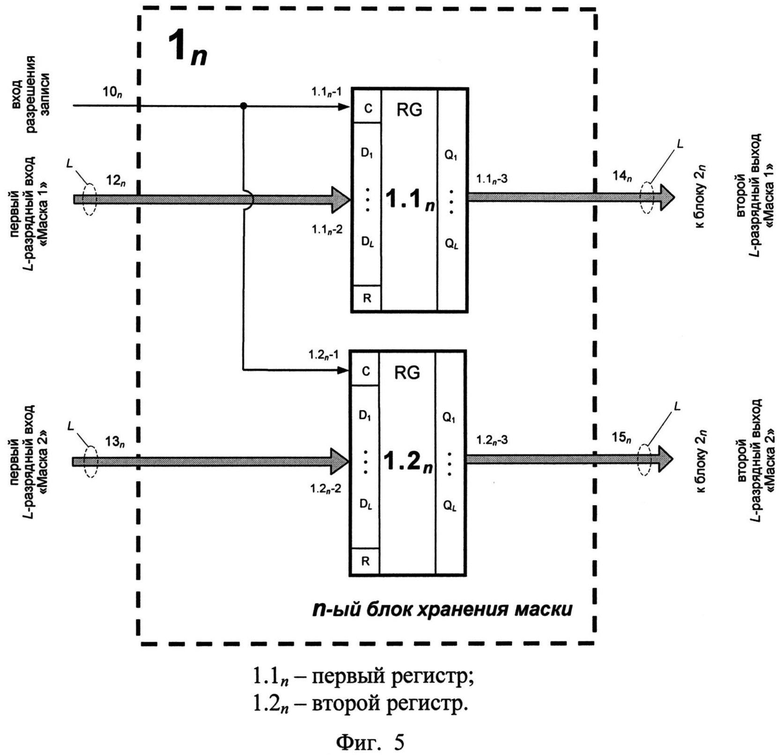

на фиг. 5 - структурная схема n-го

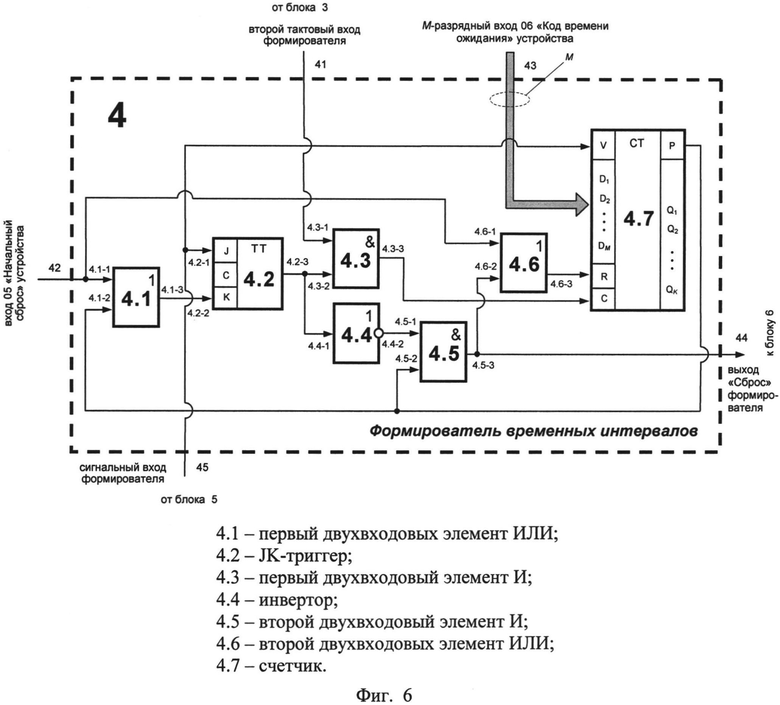

на фиг. 6 - структурная схема формирователя временных интервалов;

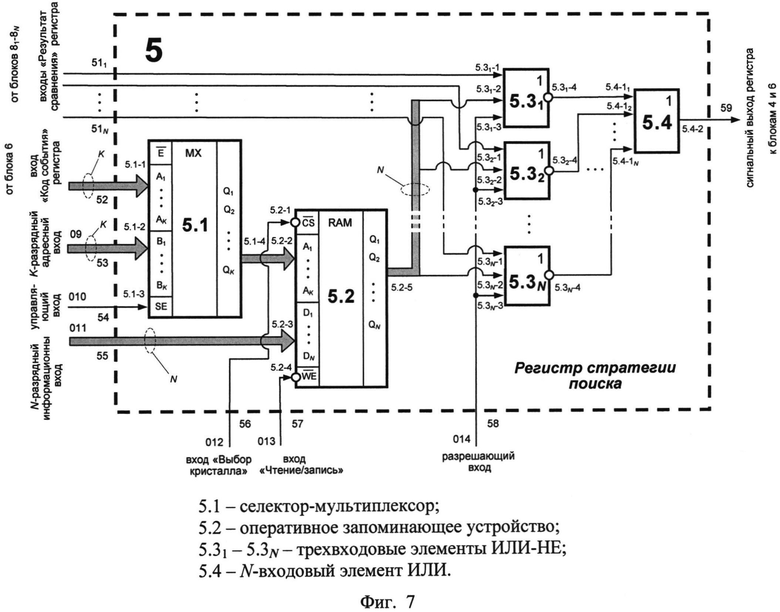

на фиг. 7 - структурная схема регистра стратегии поиска;

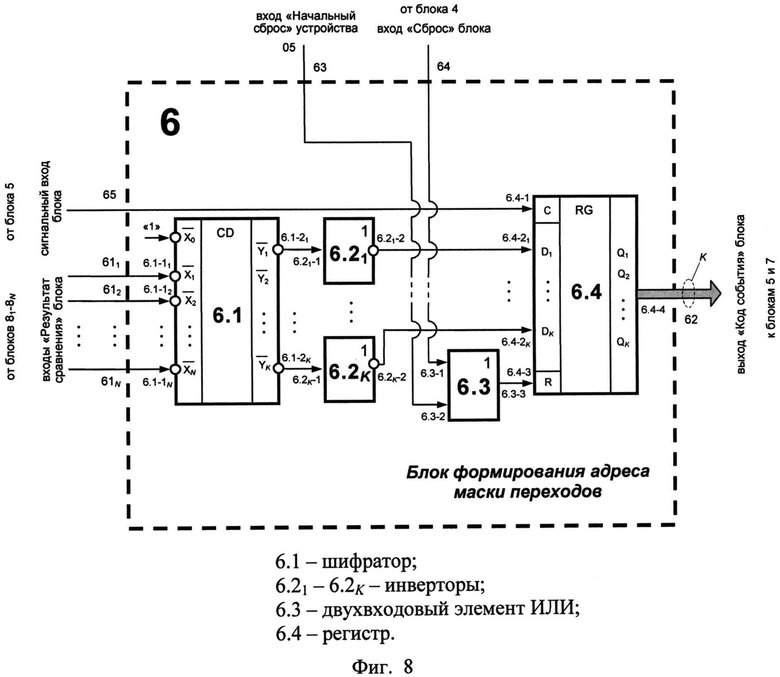

на фиг. 8 - структурная схема блока формирования адреса маски переходов;

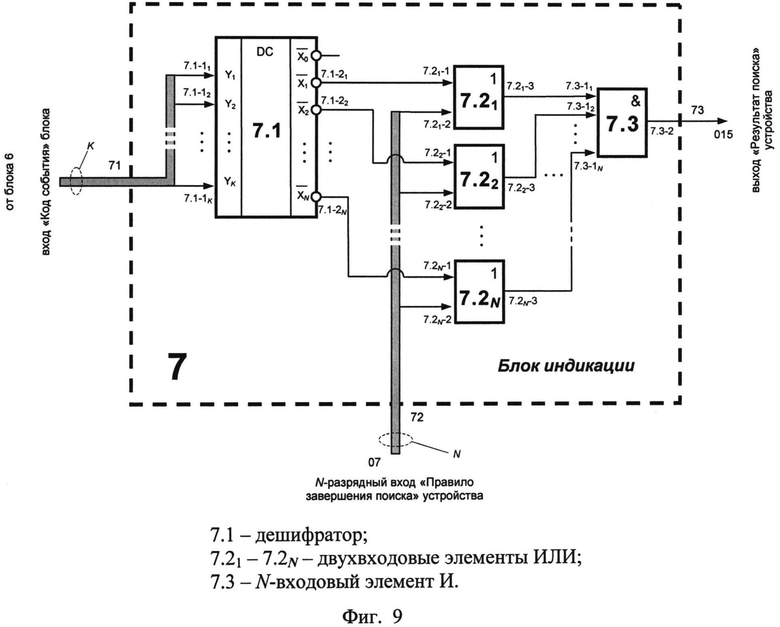

на фиг. 9 - структурная схема блока индикации;

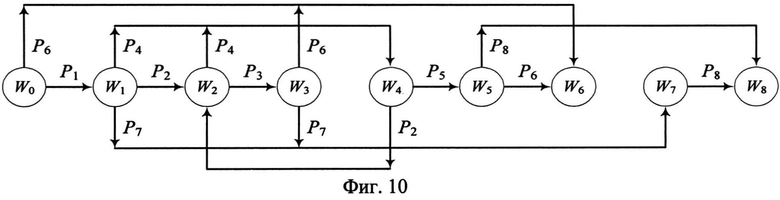

на фиг. 10 - пример сценария поиска;

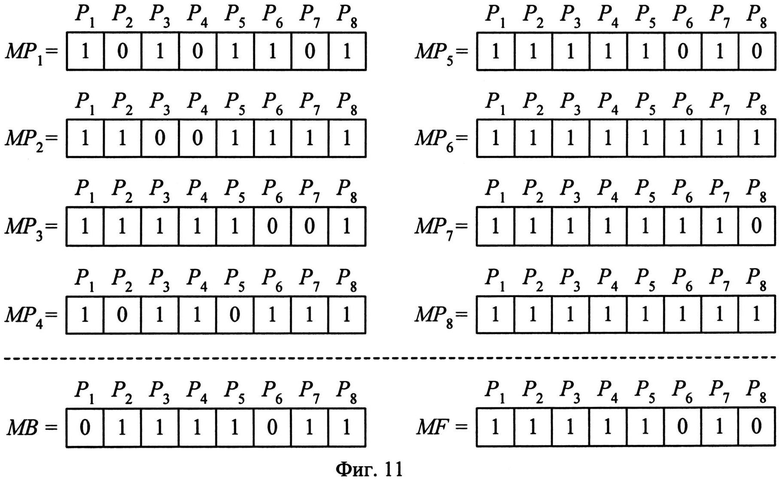

на фиг. 11 - пример заполнения масок переходов, маски начала сценария и маски окончания сценария.

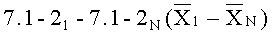

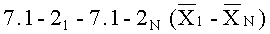

Устройство (см. фиг. 1) состоит из N, где N≥2, блоков хранения маски 11-1N, N блоков селекции 21-2N, делителя частоты 3, формирователя временных интервалов 4, регистра стратегии поиска 5, блока формирования адреса маски переходов 6, блока индикации 7, N селекционных контроллеров времени поиска 81-8N, главного контроллера времени поиска 9 и генератора тактовых импульсов 10.

Элементы соединены между собой следующим образом (см. фиг. 1). Тактовый вход 38 делителя частоты 3 является первым тактовым входом 08 устройства, а выход 39 делителя частоты 3 соединен с тактовым входом 41 формирователя временных интервалов 4. При этом. K-разрядный, где K=(log2N)+1, выход «Код события» 62 блока формирования адреса маски переходов 6 подключен к K-разрядным входам «Код события» 52 и 71 регистра стратегии поиска 5 и блока индикации 7 соответственно. Входы разрешения записи 101-10N N блоков хранения маски 11-1N объединены и являются входом разрешения записи 01 устройства. L-разрядные информационные входы 211-21N, где L≥2, N блоков селекции 21-2N объединены и являются L-разрядным информационным входом 04 устройства. Первые Z-разрядные входы «Маска 1» 12n и «Маска 2» 13n n-го блока хранения маски 1n, где n=1, 2, N, являются n-ми первыми L-разрядными входами соответственно «Маска 1» 02n и «Маска 2» 03n устройства. Вторые Z-разрядные выходы «Маска 1» 14n и «Маска 2» 15n n-го блока хранения маски 1n подключены к соответствующим вторым Z-разрядным входам «Маска 1» 22n и «Маска 2» 23n n-го блока селекции 2n. Вход «Начальный сброс» 42 формирователя временных интервалов 4 соединен с входом «Начальный сброс» 63 блока формирования адреса маски переходов 6 и является входом «Начальный сброс» 05 устройства. При этом, M-разрядный вход «Код времени ожидания» 43 формирователя временных интервалов 4, где М≥2 - разрядность кода времени ожидания, является M-разрядным входом «Код времени ожидания» 06 устройства, а выход 44 формирователя временных интервалов 4 соединен с входом «Сброс» 64 блока формирования адреса маски переходов 6. Сигнальный выход 59 регистра стратегии поиска 5 соединен с сигнальными входами 45 и 65 формирователя временных интервалов 4 и блока формирования адреса маски переходов 6 соответственно. K-разрядный адресный вход 53, управляющий вход 54, N-разрядный информационный вход 55 и разрешающий вход 58 регистра стратегии поиска 5 являются соответственно K-разрядным адресным входом 09, управляющим входом 010, N-разрядным информационным входом 011 и разрешающим входом 014 устройства. Входы «Выбор кристалла» 56 и «Чтение/запись» 57 регистра стратегии поиска 5 являются соответственно входами «Выбор кристалла» 012 и «Чтение/запись» 013 устройства. N-разрядный вход «Правило завершения поиска» 72 и выход «Результат поиска» 73 блока индикации 7 являются соответственно N-разрядным входом «Правило завершения поиска» 07 и выходом «Результат поиска» 015 устройства. Выходы «Результат сравнения» 261-26N блоков селекции 21-2N соединены с соответствующими входами «Результат сравнения» 811-81N соответствующих селекционных контроллеров времени поиска 81-8N, выходы «Результат сравнения» 831-83N которых соединены с соответствующими входами «Результат сравнения» 511-51N регистра стратегии поиска 5 и с соответствующими входами «Результат сравнения» 611-61N блока формирования адреса маски переходов 6. Выход 101 генератора тактовых импульсов 10 подключен к тактовым входам 251-25N каждого из TV блоков селекции 21-2N, входы «Обнуление» 241-24N которых являются соответствующими входами «Обнуление» 0171-017N устройства. Причем S-разрядный, где S≥2 - разрядность корректирующего кода времени поиска, корректирующий вход 27n n-ого блока селекции 2n соединен с S-разрядным проверочным входом 82n n-ого селекционного контроллера времени поиска 8n и подключен к n-ому S-разрядному выходу 92n главного контроллера времени поиска 9, N S-разрядных входов 911-91N которого являются соответствующими N S-разрядными входами «Коррекция максимального времени поиска» 016 устройства.

Число «N, (N≥2)» (блоков, разрядов, входов, выходов и т.п.) определяется в соответствии с возможным количеством типов БДИ (они определяют общее количество масок переходов, характеризующих состав сценариев поиска) и, как правило, составляет от 2 (двух) до 500 (пятисот).

Число «K, (где K=(log2N+1)» характеризует разрядность кода адреса маски переходов, адреса, по которому в оперативном запоминающем устройстве хранится маска переходов, определяющая тип (типы) ожидаемых согласно сценария поиска БДИ. Иными словами, это количество двоичных разрядов, достаточное для адресации N масок переходов и маски начала сценария поиска, как правило, составляет от 2 (двух) до 10 (десяти).

Число «М, (М≥2)» характеризует разрядность кода времени ожидания - кода допустимого интервала времени, в течение которого ожидается очередной БДИ, заданный сценарием поиска и, как правило, составляет от 2 (двух) до 10 (десяти).

Число «L, (L≥2)» характеризует максимально возможное количество разрядов в БДИ, используемых в сценарии поиска и, как правило, составляет от 2 (двух) до 10 (десяти).

Число «S, (S≥2)» характеризует разрядность корректирующего кода времени поиска, разрядность кода, обуславливающего изначальное или подвергшееся коррекции (новое) значение максимального времени поиска для каждого конкретного сценария (поискового запроса) и, как правило, составляет от 2 (двух) до 10 (десяти).

Селекционные контроллеры времени поиска 81-8N идентичны и предназначены для дешифровки, дополнительного сравнения и контроля нового, вводимого в динамике управления процессом реализации поисковых запросов, S-разрядного кода, обуславливающего новое значение (границы) максимального времени поиска для каждого конкретного поискового запроса.

Селекционный контроллер времени поиска (например, n-ый СКВП) 8n, где n=1, 2, …, N, (фиг. 2), состоит из дешифратора корректированного кода максимального времени поиска 8.1n и регистра сравнения-коррекции максимального времени поиска 8.2n. При этом S-разрядный вход 8.1n-1 дешифратора корректированного кода максимального времени поиска 8.1n является S-разрядным проверочным входом 82n селекционного контроллера времени поиска 8n. Проверочный выход 8.1n-2 дешифратора корректированного кода максимального времени поиска 8.1n подключен к проверочному входу 8.2n-2 регистра сравнения-коррекции максимального времени поиска 8.2n, сигнальный вход 8.2n-1 которого является сигнальным входом 81n селекционного контроллера времени поиска 8n. Сигнальный выход 8.2n-3 регистра сравнения-коррекции максимального времени поиска 8.2n является выходом «Результат сравнения» 83n селекционного контроллера времени поиска 8n.

Дешифратор корректированного кода максимального времени поиска 8.1n n-го селекционного контроллера времени поиска 8n предназначен для преобразования S-разрядного кода, обуславливающего новое, вводимое в процессе управления, значение (границы) максимального времени поиска для каждого поискового запроса в двоичный код. Дешифратор корректированного кода максимального времени поиска 8.1n может быть технически реализован в виде серийно выпускаемого дешифратора, описанного в книге [Богданович М.И., Грель И.Н., Прохоренко В.А. и др. Цифровые интегральные микросхемы: Справочник. - Минск: Беларусь, 1991. С. 432-436, рис. 4.46].

Регистр сравнения-коррекции максимального времени поиска 8.2n n-го селекционного контроллера времени поиска 8n предназначен для дополнительной проверки (сравнения) соответствия времени получения результатов поискового запроса с изначальным и вновь вводимым максимальным времени поиска в очереди поисковых запросов и коррекции (формирования по итогам сравнения) на выходе «Результат сравнения» 83n СКВП 8n сигнала, характеризующего соответствие получения результатов этого поискового запроса требуемому времени с учетом коррекции. Регистр сравнения-коррекции максимального времени поиска 8.2n может быть реализован технически на базе серийно выпускаемого узла сравнения (цифрового компаратора), как показано в [Гусев В.В., Лебедев О.Н., Сидоров A.M. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С. 149-152, рис. 5.19].

Главный контроллер времени поиска 9 предназначен для динамической коррекции значений (границ) максимального времени поиска для каждого поискового запроса из любого сочетания N масок переходов (сценариев поиска).

Главный контроллер времени поиска 9 (фиг. 3) состоит из регистрирующего элемента времени поиска 9.1 и элемента хранения нового значения времени поиска 9.2. При этом N S-разрядных входов 9.1-11-9.1-1N регистрирующего элемента времени поиска 9.1 являются соответствующими N S-разрядными входами 911-91N главного контроллера времени поиска 9 и соответствующими N S-разрядными входами «Коррекция максимального времени поиска» 0161-016N устройства. Причем N S-разрядных выходов 9.1-21-9.1-2N регистрирующего элемента времени поиска 9.1 подключены к соответствующим N S-разрядным входам 9.2-11-9.2-1N элемента хранения нового значения времени поиска 9.2, N S-разрядных выходов 9.2-21-9.2-2N которого являются соответствующими N S-разрядными выходами 921-92N главного контроллера времени поиска 9.

Регистрирующий элемент времени поиска 9.1 главного контроллера времени поиска 9 предназначен для контроля и регистрации в S-разрядном коде нового, вводимого в динамике управления процессом поиска информации, значения максимального времени поиска для каждого конкретного поискового запроса. Регистрирующий элемент времени поиска 9.1 может быть технически реализован в виде серийно выпускаемого многоразрядного сдвигающего регистра для сдвига влево, как показано в литературе [Гусев В.В., Лебедев О.Н., Сидоров A.M. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С. 158-160, рис. 5.28(б)].

Элемент хранения нового значения времени поиска 9.2 главного контроллера времени поиска 9 предназначен для записи и хранения в S-разрядном коде нового, вводимого в динамике управления процессом реализации поисковых запросов, значения максимального времени поиска информации. Элемент хранения нового значения времени поиска 9.2 может быть технически реализован в виде обычного запоминающего устройства на базе типового многоразрядного регистра сдвига с последовательным вводом и выводом информации, описанного в [Быстрое Ю.А., Великсон Я.М., Вогман В.Д. и др. Электроника: Справочная книга / Под ред. Быстрова Ю.А. - СПб.: Энергоатомиздат, 1996. С. 291-292, рис. 6. 7].

Генератор тактовых импульсов 10, входящий в общую структурную схему, предназначен для выработки синхронизирующей последовательности импульсов. Техническая реализация генератора тактовых импульсов 10 возможна на базе серийно выпускаемого генератора тактовых импульсов, описанного в работе [Шило В.Л. Популярные цифровые микросхемы. Справочник. - М.: Радио и связь, 1987. С. 50-53].

Блоки селекции 21-2N идентичны и предназначены для контроля и идентификации соответствующих элементов входящего потока данных, формирования результата поиска (результата идентификации), контроля оставшегося времени поиска, а также выработки управляющих сигналов по истечении установленного изначального или вновь вводимого в динамике управления времени поиска для каждого поискового запроса.

Блок селекции (например, n-ый БС) 2n, где n=1, 2, …, N, (фиг. 4), состоит из первой 2.11-2.1L и второй 2.21-2.2L, групп двухвходовых элементов И по L элементов в каждой группе, компаратора 2.3n, инвертора 2.4n, счетчика 2.5n, трехвходового элемента И 2.6n и корректирующего регистра 2.7n. Инверсный выход

Первая 2.11-2.1L и вторая 2.21-2.2L, группы двухвходовых элементов И (по L элементов в каждой группе), входящие в структурную схему блока селекции, например, 2n, идентичны, a L однотипных элементов И выполняют функции коммутирующих элементов при опросе L-разрядного информационного входа 21n блока селекции 2n и типа БДИ определяемого первой и второй битовыми масками, поступающими соответственно на второй L-разрядный вход «Маска 1» 22n и второй L-разрядный вход «Маска 2» 23n блока селекции 2n. Структура первой и второй групп двухвходовых элементов И известна, описана в прототипе (см. патент РФ №2313128 «Устройство поиска информации» МПК G06F 9/46 опубликован 20.12.2007 г., бюл. 35) и проиллюстрирована на фиг. 4, а элементы И (2.11-2.1L и 2.21-2.2L), входящие в состав этих групп, реализуются в виде известных и описанных в [Гусев В.В., Лебедев О.Н., Сидоров A.M. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С. 13-14, рис. 1.2].

Компаратор 2.3n, входящий в состав блока селекции, например, 2n, предназначен для сравнения двоичных кодов установленных на его входах и формирования результата сравнения. Описание работы и схема компаратора приведены, например, в [Шило В.Л. Популярные микросхемы ТТЛ. - М.: АРГУС, 1993, с. 183-184].

Инвертор 2.4n, входящий в состав блока селекции, например, 2n, предназначен для преобразования сигналов значения логической единицы в значение логического нуля при соответствии результатов сравнения сценарию поиска, и обратного преобразования при не соответствии. Инвертор 2.4n может быть технически реализован в виде элемента НЕ, в соответствии с описанием, приведенным в [Гусев В.В., Лебедев О.Н., Сидоров A.M. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С. 14, рис. 1.3].

Счетчик 2.5n, входящий в состав блока селекции, например, 2n, предназначен для счета поступающих на его вход импульсов (счетных импульсов), выработки управляющего сигнала, определяемого кодом начального заполнения по входам D1-DS и периодом следования тактовых импульсов, то есть является настраиваемым таймером. Описание работы и схема такого счетчика известны и приведены, например, в работе [Мальцев П.П., Долидзе Н.С.и др. Цифровые интегральные микросхемы: справочник. - М.: Радио и связь, 1994, С. 64-65].

Трехвходовый элемент И 2.6n, входящий в состав блока селекции, например, 2n, предназначен для регистрации результатов поисковых запросов (результатов сравнения), а также коммутации тактового входа 25n блока селекции 2n и инверсного выхода

Корректирующий регистр 2.1n, входящий в состав блока селекции, например, 2n, предназначен для регистрации и предварительного сравнения ранее введенного (изначального) и вновь вводимого в динамике управления S-разрядного кода, а также коррекции (формирования по итогам сравнения) на своих S выходах 2.7n-21-2.7n-3S информационных сигналов, характеризующих предварительное решение о значении максимального времени поиска для каждого конкретного поискового запроса. Корректирующий регистр 2.7n может быть технически реализован на основе серийно выпускаемого узла сравнения многоразрядных чисел, как описано в [Гусев В.В., Лебедев О.Н., Сидоров A.M. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С. 149-152, рис. 5.21].

Блоки хранения маски 11-1N, входящие в общую структурную схему, идентичны и предназначены для хранения битовых масок, используемых для идентификации элементов входящего потока данных. Структура блоков хранения маски известна, описана в прототипе (см. патент РФ №2313128 «Устройство поиска информации» МПК G06F 9/46, 20.12.2007 г., бюл. 35) и проиллюстрирована на фиг. 5. Блок хранения маски, например, 1n, состоит из первого 1.1n и второго 1.2n регистров. Разряды L-разрядного информационного выхода 1.1n-3 первого регистра 1.1n являются соответствующими разрядами второго L-разрядного выхода «Маска 1» 14n блока хранения маски 1n, а разряды L-разрядного информационного выхода 1.2n-3 второго регистра 1.2n являются соответствующими разрядами второго Z-разрядного выхода «Маска 2» 15n блока хранения маски 1n. Входы разрешения записи 1.1n-1 и 1.2n-1 соответственно первого 1.1n и второго 1.2n регистров соединены между собой и являются входом разрешения записи 10n блока хранения маски 1n и входом разрешения записи 01 устройства поиска информации. Разряды L-разрядного информационного входа 1.1n-2 первого регистра 1.1n являются соответствующими разрядами первого L-разрядного входа 12n «Маска 1» блока хранения маски 1n и соответствующими разрядами первого L-разрядного входа 02n «Маска 1» устройства поиска информации, а разряды L-разрядного информационного входа 1.2n-2 второго регистра 1.2n являются соответствующими разрядами первого L-разрядного входа 13n «Маска 2» блока хранения маски 1n и соответствующими разрядами первого L-разрядного входа 03n «Маска 2» устройства поиска информации.

Первый 1.1n и второй 1.2n, регистры блока хранения маски 1n идентичны и предназначены для хранения соответственно первой и второй битовой маски. Регистры могут быть технически реализованы на основе серийно выпускаемого регистра, как описано в [Мальцев П.П., Долидзе Н.С. и др. Цифровые интегральные микросхемы: справочник. - М.: Радио и связь, 1994, с. 57-62].

Делитель частоты 3, входящий в общую структурную схему, предназначен для увеличения периода следования поступающей на его вход последовательности импульсов. Схема реализации делителя частоты известна и описана в прототипе (см. патент РФ №2313128 «Устройство поиска информации» МПК G06F 9/46 опубликован 20.12.2007 г., бюл. 35). В частности, делитель частоты 3 может быть построен на базе счетчика, как описано в [Мальцев П.П., Долидзе Н.С. и др. Цифровые интегральные микросхемы: справочник. - М.: Радио и связь, 1994, с. 62-74]. При этом входом делителя будет счетный вход счетчика, а выходом делителя - один из выходов счетчика.

Формирователь временных интервалов 4, входящий в общую структурную схему, предназначен для контроля интервала времени между элементами входящего потока данных и формирования сигнала по его истечении. Структура формирователя временных интервалов известна, описана в прототипе (см. патент РФ №2313128 «Устройство поиска информации» МПК G06F 9/46, 20.12.2007 г., бюл. 35) и изображена на фиг. 6. Формирователь временных интервалов 4 состоит из первого двухвходового элемента ИЛИ 4.1, JK-триггера 4.2, первого двухвходового элемента И 4.3, инвертора 4.4, второго двухвходового элемента И 4.5, второго двухвходового элемента ИЛИ 4.6 и счетчика 4.7. При этом выход переполнения Р счетчика 4.7 соединен со вторыми входами 4.5-2 и 4.1-2 соответственно второго двухвходового элемента И 4.5 и первого двухвходового элемента ИЛИ 4.1. Первый вход 4.1-1 первого двухвходового элемента ИЛИ 4.1 соединен с первым входом 4.6-1 второго двухвходового элемента ИЛИ 4.6 и является входом «Начальный сброс» 42 формирователя временных интервалов 4 и входом «Начальный сброс» 05 устройства. Выход 4.1-3 первого двухвходового элемента ИЛИ 4.1 соединен со вторым информационным входом 4.2-2 (входом К) JK-триггера 4.2, первый информационный вход 4.2-1 (вход J) которого соединен с входом разрешения записи V счетчика 4.7 и является сигнальным входом 45 формирователя временных интервалов 4. При этом, m-ый, где m=1, 2, …, М, информационный вход Dm (из состава D1-DM информационных входов) счетчика 4.7 является m-ым разрядом М-разрядного входа «Код времени ожидания» 43 формирователя временных интервалов 4 и соответствующим m-ым разрядом М-разрядного входа «Код времени ожидания» 06 устройства. Вход сброса R счетчика 4.7 соединен с выходом 4.6-3 второго двухвходового элемента ИЛИ 4.6, а счетный вход С счетчика 4.7 соединен с выходом 4.3-3 первого двухвходового элемента И 4.3. Первый вход 4.3-1 первого двухвходового элемента И 4.3 является вторым тактовым входом 41 формирователя временных интервалов 4. Выход 4.2-3 JK-триггера 4.2 соединен с вторым входом 4.3-2 первого двухвходового элемента И 4.3 и входом 4.4-1 инвертора 4.4, выход 4.4-2 которого соединен с первым входом 4.5-1 второго двухвходового элемента И 4.5. Выход 4.5-3 второго двухвходового элемента И 4.5 соединен с вторым входом 4.6-2 второго двухвходового элемента ИЛИ 4.6 и является выходом «Сброс» 44 формирователя временных интервалов 4.

Первый 4.1 и второй 4.6 двухвходовые элементы ИЛИ формирователя временных интервалов 4 идентичны и предназначены для объединения сигналов определенного логического уровня, поступающих с входа «Начальный сброс» устройства, а также выхода переполнения Р счетчика 4.7 и выхода второго двухвходового элемента И 4.5 соответственно. Структура первого 4.1 и второго 4.6 двухвходовых элементов ИЛИ известна, описана в прототипе (см. патент РФ №2313128 «Устройство поиска информации» МПК G06F 9/46, 20.12.2007 г., бюл. 35), элементы могут быть технически реализованы на базе серийно выпускаемого элемента ИЛИ, подробно описанного в [Гусев В.В., Лебедев О.Н., Сидоров A.M. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С. 24-26, рис. 1.7].

JK-триггер 4.2 формирователя временных интервалов 4 предназначен для хранения логического значения, определяющего режим функционирования формирователя временных интервалов. Структура JK-триггера известна, описана в прототипе (см. патент РФ №2313128 «Устройство поиска информации» МПК G06F 9/46, 20.12.2007 г., бюл. 35), JK-триггер может быть технически реализован, как описано в [Тарабрин Б.В., Лунин Л.Ф., Смирнов Ю.Н. и др. Интегральные микросхемы: справочник. - М.: Энергоатомиз дат, 1985, с. 67].

Первый 4.3 и второй 4.5 двухвходовые элементы И формирователя временных интервалов 4 идентичны и выполняют функции коммутирующих элементов при опросе выхода JK-триггера и второго тактового входа 41 формирователя, а также выходов переполнения Р счетчика 4.7 и инвертора 4.4 соответственно. Подходы к реализации элементов И известны, описаны в прототипе (см. патент РФ №2313128 «Устройство поиска информации» МПК G06F 9/46, 20.12.2007 г., бюл. 35), эти изделия могут быть построены на базе серийно выпускаемых элементов И, подробно описанных в [Гусев В.В., Лебедев О.Н., Сидоров А.М. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С. 13-14, рис. 1.2].

Инвертор 4.4 формирователя временных интервалов 4 предназначен для преобразования сигналов значения логической единицы в значение логического нуля и обратного преобразования в зависимости от сигнала на его входе, определяемого значениями с выхода JK-триггера 4.2. Инвертор 4.4 может быть технически реализован в виде элемента НЕ, в соответствии с описанием, приведенным в [Гусев В.В., Лебедев О.Н., Сидоров A.M. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С. 14, рис. 1.3].

Счетчик 4.7 формирователя временных интервалов 4 предназначен для счета поступающих на его вход импульсов и выработки управляющего сигнала по истечении интервала времени, определяемого значением кода начального заполнения счетчика и периодом следования тактовых импульсов, то есть выполняет функцию настраиваемого таймера. Описание работы и схема такого счетчика известны и приведены, например, в [Мальцев П.П., Долидзе Н.С. и др. Цифровые интегральные микросхемы: справочник. - М.: Радио и связь, 1994, с. 71].

Регистр стратегии поиска 5, входящий в общую структурную схему, предназначен для проверки соответствия порядка следования идентифицированных элементов входящего потока данных заданным правилам и формирования сигнала при поступлении элемента, ожидаемого в соответствии с правилами. Структура регистра стратегии поиска известна, описана в прототипе (см. патент РФ №2313128 «Устройство поиска информации» МПК G06F 9/46, 20.12.2007 г., бюл. 35) и изображена на фиг. 7. Регистр стратегии поиска 5 состоит из селектора-мультиплексора 5.1, оперативного запоминающего устройства 5.2, N трехвходовых элементов ИЛИ-НЕ 5.31-5.3N, N-входового элемента ИЛИ 5.4, выход 5.4-2 которого является сигнальным выходом 59 регистра стратегии поиска 5. При этом, n-ый вход 5.4-1n (где n=1, 2, …, N) N-входового элемента ИЛИ 5.4 соединен с инверсным выходом 5.3n-4 n-го трехвходового элемента ИЛИ-НЕ 5.3n. Первый вход 5.3n-1 n-го трехвходового элемента ИЛИ-НЕ 5.3n является n-ым входом «Результат сравнения» 51n регистра стратегии поиска 5. Второй вход 5.3n-2 n-го трехвходового элемента ИЛИ-НЕ 5.3n соединен с n-ым информационным выходом 5.2-5n оперативного запоминающего устройства 5.2, а третьи входы 5.31-3-5.3N-3 всех трехвходовых элементов ИЛИ-НЕ 5.31-5.3N соединены между собой, являются разрешающим входом 58 регистра стратегии поиска 5 и разрешающим входом 014 устройства. При этом k-ый, где k=1, 2, …, K, адресный вход 5.2-2k (Ak из состава A1-AK адресных входов) оперативного запоминающего устройства 5.2 соединен с k-ым выходом 5.1-4k (Qk из состава Q1-QK выходов) селектора мультиплексора 5.1, а n-ый информационный вход 5.2-3n (Dn из состава D1-DN информационных входов) оперативного запоминающего устройства 5.2 является n-ым разрядом N-разрядного информационного входа 55 регистра стратегии поиска 5 и соответствующим n-ым разрядом N-разрядного информационного входа 011 устройства. Инверсные входы «Выбор кристалла» 5.2-1 (вход

Селектор-мультиплексор 5.1 регистра стратегии поиска 5 предназначен для коммутации одной из двух групп информационных входов на его выходы. Схема реализации такого селектора-мультиплексора известна, описана в прототипе (см. патент РФ №2313128 «Устройство поиска информации» МПК G06F 9/46, 20.12.2007 г., бюл. 35, фиг. 5) и может быть технически реализована, например, как описано в [Мальцев П.П., Долидзе Н.С.и др. Цифровые интегральные микросхемы: справочник. - М.: Радио и связь, 1994, с. 33-40].

Оперативное запоминающее устройство 5.2 регистра стратегии поиска 5 предназначено для хранения масок, содержащих правила, определяющие требуемый порядок следования идентифицированных элементов входящего потока данных. Схема реализации такого оперативного запоминающего устройства известна, описана в прототипе (см. патент РФ №2313128 «Устройство поиска информации» МПК G06F 9/46, 20.12.2007 г., бюл. 35, фиг. 5) и может быть технически реализована, например, как описано в [Шило В.Л. Популярные цифровые микросхемы. - М.: Радио и связь, 1987, с. 164-166].

Трехвходовые элементы ИЛИ-НЕ 5.31-5.3N регистра стратегии поиска 5 идентичны и предназначены для получения логического нуля на их выходах при наличии логической единицы на разрешающем входе регистра стратегии поиска 5 и для получения логической единицы на выходах в противном случае, причем вне зависимости от логических значений, установленных на первых и вторых входах трехвходовых элементов ИЛИ-НЕ. Эти элементы являются широко распространенными, серийно выпускаемыми, схема их реализации и алгоритм работы таких трехвходовых элементов ИЛИ-НЕ известны и подробно описаны в прототипе (см. патент РФ №2313128 «Устройство поиска информации» МПК G06F 9/46, 20.12.2007 г., бюл. 35, фиг. 5).

Элемент ИЛИ 5.4 с N входами, встроенный в структурную схему регистра стратегии поиска 5, предназначен для объединения сигналов определенного логического уровня, поступающих с выходов трехвходовых элементов ИЛИ-НЕ 5.31-5.3N. Этот элемент являются широко распространенным, серийно выпускаемым, схема реализации и алгоритм работы такого N-входового элемента ИЛИ известны и подробно описаны в прототипе (см. патент РФ №2313128 «Устройство поиска информации» МПК G06F 9/46, 20.12.2007 г., бюл. 35, фиг. 5).

Блок формирования адреса маски переходов 6, входящий в общую структурную схему, предназначен для формирования и хранения кода, соответствующего маске, определяющей следующий элемент, который должен быть идентифицирован во входящем потоке данных. Структура блока формирования адреса маски переходов известна, описана в прототипе (см. патент РФ №2313128 «Устройство поиска информации» МПК G06F 9/46, 20.12.2007 г., бюл. 35) и изображена на фиг. 8. Блок формирования адреса маски переходов 6 состоит из шифратора 6.1, K инверторов 6.21-6.2K, двухвходового элемента ИЛИ 6.3 и регистра 6.4, k-ый (где k=1, 2, …, K) информационный выход 6.4-4k (Qk из состава Q1-QK информационных входов) которого является k-ым разрядом K-разрядного выхода «Код события» 62 блока формирования адреса маски переходов 6. При этом, k-ый информационный вход 6.4-2k (Dk из состава D1-Dk информационных входов) регистра 6.4 соединен с инверсным выходом 6.2k-2 k-го инвертора 6.2k. Вход разрешения записи 6.4-1 (вход С) регистра 6.4 является сигнальным входом 65 блока формирования адреса маски переходов 6. Вход сброса 6.4-3 (вход R) регистра 6.4 соединен с выходом 6.3-3 двухвходового элемента ИЛИ 6.3, первый вход 6.3-1 которого является входом «Сброс» 64 блока формирования адреса маски переходов 6. Второй вход 6.3-2 двухвходового элемента ИЛИ 6.3 является входом «Начальный сброс» 63 блока формирования адреса маски переходов 6 и входом «Начальный сброс» 05 устройства. Вход 6.2k-1 k-го инвертора 6.2k (из состава 6.21-6.2K инверторов) подключен к соответствующему 6.1-2k k-му инверсному выходу (выходу

Шифратор 6.1 блока формирования адреса маски переходов 6 предназначен для формирования кода, соответствующего маске, определяющей следующий элемент, который должен быть идентифицирован во входящем потоке данных, путем преобразования сигнала низкого уровня на одном из его входов в соответствующий двоичный код на его выходах. Схема реализации такого шифратора известна, описана в прототипе (см. патент РФ №2313128 «Устройство поиска информации» МПК G06F 9/46, 20.12.2007 г., бюл. 35, фиг. 6) и может быть технически реализована, например, как описано в [Мальцев П.П., Долидзе Н.С. и др. Цифровые интегральные микросхемы: справочник. - М.: Радио и связь, 1994, с. 40-41].

Инверторы 6.21-6.2K блока формирования адреса маски переходов 6 идентичны и предназначены для преобразования сигналов значения логической единицы в значение логического нуля и обратного преобразования в зависимости от сигналов на их входах, определяемых значениями с выходов шифратора 6.1. Схема реализации таких инверторов известна, описана в прототипе (см. патент РФ №2313128 «Устройство поиска информации» МПК G06F 9/46, 20.12.2007 г., бюл. 35, фиг. 6), они могут быть технически реализован в виде элементов НЕ, в соответствии с описанием, приведенным в [Гусев В.В., Лебедев О.Н., Сидоров A.M. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С. 14, рис. 1.3].

Двухвходовый элемент ИЛИ 6.3 блока формирования адреса маски переходов 6 предназначен для объединения сигналов определенного логического уровня, поступающих с входа «Начальный сброс» устройства и входа «Сброс» 64 блока формирования адреса маски переходов 6 соответственно. Структура двухвходового элемента ИЛИ известна, описана в прототипе (см. патент РФ №2313128 «Устройство поиска информации» МПК G06F 9/46, 20.12.2007 г., бюл. 35, фиг. 6), элемент может быть технически реализован на базе серийно выпускаемого элемента ИЛИ, подробно описанного в [Гусев В.В., Лебедев О.Н., Сидоров A.M. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С. 24-26, рис. 1.7].

Регистр 6.4 блока формирования адреса маски переходов 6 предназначен для хранения кода, соответствующего маске, определяющей следующий элемент, который должен быть идентифицирован во входящем потоке данных. Схема реализации такого регистра известна, описана в прототипе (см. патент РФ №2313128 «Устройство поиска информации» МПК G06F 9/46, 20.12.2007 г., бюл. 35, фиг. 6), регистр может быть технически реализован, например, как описано в [Мальцев П.П., Долидзе Н.С. и др. Цифровые интегральные микросхемы: справочник. - М.: Радио и связь, 1994, с. 57-62].

Блок индикации 7, входящий в общую структурную схему, предназначен для обнаружения признаков, свидетельствующих о завершении заданной правилами последовательности элементов входящего потока данных и формирования соответствующего сигнала. Структура блока индикации известна, описана в прототипе (см. патент РФ №2313128 «Устройство поиска информации» МПК G06F 9/46, 20.12.2007 г., бюл. 35) и изображена на фиг. 9. Блок индикации 7 состоит из дешифратора 7.1, N двухвходовых элементов ИЛИ 7.21-7.2N и N-входового элемента И 7.3, выход 7.3-2 которого является выходом «Результат поиска» 73 блока индикации 7 и выходом «Результат поиска» 015 устройства. При этом, n-ый вход 7.3-1n (из состава 7.3-11-7.3-1N входов) N-входового элемента И 7.3 соединен с выходом 7.21-3 соответствующего n-го двухвходового элемента ИЛИ 7.2n (из состава 7.21-7.2N двухвходовых элементов ИЛИ). Первый вход 7.2n-1 n-го двухвходового элемента ИЛИ 7.2n соединен с соответствующим n-ым инверсным выходом 7.1-2n (выходом

Дешифратор 7.1 блока индикации 7 предназначен для преобразования поступающего на его вход двоичного кода в сигнал низкого уровня на соответствующем выходе. Схема реализации дешифратора известна, описана в прототипе (см. патент РФ №2313128 «Устройство поиска информации» МПК G06F 9/46, 20.12.2007 г., бюл. 35, фиг. 7), дешифратор может быть технически реализован, например, как описано в книге [Мальцев П.П., Долидзе Н.С.и др. Цифровые интегральные микросхемы: справочник. - М.: Радио и связь, 1994, с. 41-47].

Двухвходовые элементы ИЛИ 7.21-7.2N блока индикации 7 идентичны и предназначены для объединения сигналов определенного логического уровня, поступающих с инверсных выходов дешифратора 7.1 и входа «Правило завершения поиска» устройства. Структура двухвходовых элементов ИЛИ известна, описана в прототипе (см. патент РФ №2313128 «Устройство поиска информации» МПК G06F 9/46, 20.12.2007 г., бюл. 35, фиг. 7), эти элементы могут быть технически реализованы на базе серийно выпускаемого элемента ИЛИ, подробно описанного в [Гусев В.В., Лебедев О.Н., Сидоров A.M. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С. 24-26, рис. 1.7].

N-входовый элемент И 7.3, входящий в состав блока индикации 7, предназначен для регистрации результатов поисковых запросов, получения и фиксации итогового результата поиска. Схема N-входового элемента И известна, описана в прототипе (см. патент РФ №2313128 «Устройство поиска информации» МПК G06F 9/46, 20.12.2007 г., бюл. 35, фиг. 7), данный элемент может быть технически реализован на основе серийно выпускаемого многовходового элемента И, описанного в книге [Гусев В.В., Лебедев О.Н., Сидоров A.M. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С. 14, рис. 1.3].

Устройство поиска информации работает следующим образом.

Известно [1-5], что с точки зрения повышения вероятности своевременного поиска информации в условиях, присущих реальному процессу функционирования современных сетей передачи данных с коммутацией пакетов, современных информационно-справочных (поисковых) систем - в условиях непрерывной динамики смены состояний запросов на поиск информации и с учетом влияющих факторов, существует возможность варьировать временем поиска информации. Эта возможность реализуется на основе принципа динамической коррекции значений (границ) максимального времени поиска для каждого поискового запроса.

Очевидно, что при обработке поисковых запросов объективно изменяются во времени не только управляющие воздействия на информационно-справочную (поисковую) систему или внешние факторы, но и текущие требования абонентов этой системы к качеству и своевременности поиска информации. В данных условиях затруднен своевременный поиск, который напрямую зависит от динамики изменения во времени параметров, режимов и методов реализации поисковых запросов, от динамики внутренних и внешних воздействий на информационно-справочную (поисковую) систему, а также от динамики изменения требований, целей и задач поиска, обусловленных конкретной ситуацией.

Анализ работ [1-5], посвященных алгоритмам и принципам обслуживания запросов абонентов в рамках сложных технических систем, позволяет сделать вывод о возможности реализации процедур повышения вероятности своевременного поиска информации на основе технической реализации принципа динамической коррекции значений (границ) максимального времени поиска для каждого поискового запроса в условиях непрерывной динамики смены состояний поисковых запросов и с учетом влияющих факторов.

Построение устройства поиска информации на основе предложенного принципа работы позволяет получить преимущество перед прототипом, обеспечивая повышение вероятности своевременного предоставления пользователям результатов поиска в рамках реальной информационно-справочной (поисковой) системы, когда поисковые запросы абонентов в динамике функционирования данной системы могут изменять пороговые значения своих состояний под влиянием управляющих воздействий (текущих требований) абонентов или внешних факторов.

Техническая реализация принципа динамической коррекции значений (границ) максимального времени поиска в заявленном устройстве осуществлена путем введения внешнего динамического управления временем поиска (в заявленном устройстве - S-разрядные входы «Коррекция максимального времени поиска» устройства) и введения регистрации, контроля и динамической коррекции максимального времени поиска для каждого поискового запроса (в заявленном устройстве реализованы соответственно в рамках блоков селекции 21-2N, селекционных контроллеров времени поиска 81-8N и главного контроллера времени поиска 9 с помощью импульсов, вырабатываемых генератором тактовых импульсов 10).

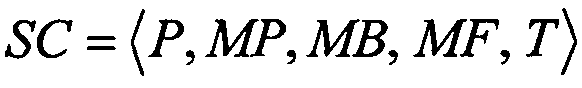

При этом, как и в прототипе, в заявленном устройстве реализован синтаксический подход к распознаванию образов [6], основанный на идентификации отдельных элементов входящего потока данных - БДИ, путем параллельного анализа значений признаков идентификации и контроля порядка их следования на предмет соответствия заданным правилам. В качестве признаков идентификации, используются значения битов в соответствующих позициях БДИ. Правила следования БДИ задаются формальной грамматикой - сценарием поиска. Для пояснения параллельного анализа значений признаков идентификации и контроля порядка их следования необходимо рассмотреть правила задания сценария поиска. Сценарий поиска SC может быть представлен следующей схемой:

где:

P={Pn},

MP={MPn},

MB - маска начала сценария поиска;

MF - маска окончания сценария поиска;

T - время ожидания очередного БДИ.

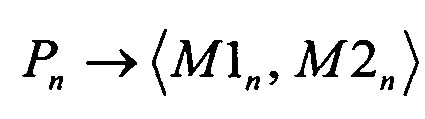

Идентификация типа БДИ в устройстве осуществляется путем сравнения значений идентификационных битов БДИ с их эталонными значениями. Под идентификационными битами понимаются биты БДИ, значения которых позволяют однозначно идентифицировать тип БДИ. Для каждого типа БДИ множество идентификационных битов может быть индивидуальным. В связи с этим каждому типу БДИ ставится в соответствие две битовые маски:

где:

M1n - первая битовая маска БДИ n-го типа;

M2n - вторая битовая маска БДИ n-го тип.

Битовые маски содержат L разрядов, где L - максимально возможное количество разрядов в БДИ, используемых в сценарии поиска. Первая битовая маска предназначена для указания позиций идентификационных битов БДИ. Значения логической единицы в разрядах первой битовой маски соответствуют позициям идентификационных битов. Во всех остальных разрядах битовой маски устанавливаются значения логического нуля. Вторая битовая маска предназначена для задания эталонных значений, которым должны соответствовать значения идентификационных битов. При этом разряды второй битовой маски, не являющиеся идентификационными, могут иметь произвольные значения, так как не влияют на процесс идентификации БДИ.

Множество масок переходов используется для задания порядка следования БДИ в рамках сценария. Множество содержит N масок переходов, каждая из которых содержит N двоичных разрядов. Таким образом каждому типу БДИ соответствует своя маска переходов. При этом, n-ая маска переходов MPn содержит информацию о типах БДИ, которые согласно сценария поиска ожидаются после наблюдения БДИ n-го типа. Указанная информация задается путем установки значения логического нуля в разрядах маски переходов, порядковые номера которых соответствуют типам ожидаемых БДИ. Во всех остальных разрядах маски переходов устанавливаются значения логической единицы.

Маска начала сценария поиска предназначена для указания типов БДИ, которые ожидаются первыми в сценарии поиска - начальных БДИ. Маска MB содержит N двоичных разрядов. В разрядах маски начала сценария поиска, номера которых соответствуют начальным типам БДИ, устанавливаются значения логического нуля. Во всех остальных разрядах маски начала сценария поиска устанавливаются значения логической единицы.

Маска окончания сценария поиска предназначена для указания типов БДИ, наблюдение которых свидетельствует о завершении сценария поиска - конечных БДИ. Маска MF содержит N двоичных разрядов. В разрядах маски окончания сценария поиска, номера которых соответствуют конечным типам БДИ, устанавливаются значения логического нуля. Во всех остальных разрядах маски окончания сценария поиска устанавливаются значения логической единицы.

В отличие от времени поиска, время ожидания очередного БДИ Т задает максимально допустимый интервал времени в течение которого ожидается очередной БДИ, заданного сценарием поиска типа. В том случае, если в течение заданного интервала времени ожидаемый тип БДИ не будет обнаружен, сценарий поиска прерывается, и осуществляется переход к ожиданию начальных БДИ. Время ожидания очередного БДИ задается в виде M-разрядного кода. При этом наименьшему времени ожидания соответствует наибольший код, являющийся дополнением до максимального числа, представимого в M-разрядном коде.

С учетом этого, в заявленном устройстве осуществляется управляемое обслуживание поисковых запросов и реализация изменяющихся во времени потребностей абонентов в идентификации элементов входящего потока данных, обуславливающие повышение вероятности своевременного поиска информации.

В целом, работу устройства поиска информации можно рассматривать как процесс перехода данного устройства из состояния в состояние. Множество состояний

W={Wn},

На фиг. 10 приведен пример сценария поиска, включающий N=8 типов БДИ. Соответствующее приведенному сценарию поиска заполнение масок переходов, маски начала сценария и маски окончания сценария приведено на фиг. 11.

Инициализация устройства включает в себя проведение следующих операций:

начальный сброс устройства;

установка первой и второй битовых масок;

установка маски начала сценария и масок переходов;

установка маски окончания сценария поиска;

установка времени ожидания очередного БДИ;

установка начального максимального времени поиска.

Начальный сброс устройства осуществляется следующим образом. На разрешающем входе 014 устройства устанавливают значение логической единицы, которая поступает на соответствующий вход 58 регистра стратегии поиска 5. Логическая единица на разрешающем входе 58 регистра стратегии поиска 5, поступая на третьи входы 5.31-3-5.3N-3 всех трехвходовых элементов ИЛИ-НЕ 5.31-5.3N (см. фиг. 7), обеспечивает наличие логического нуля на их выходах 5.31-4-5.3N-4 вне зависимости от логических значений, установленных на первых 5.31-1-5.3N-1 и вторых 5.31-2- 5.3N-2 входах. В связи с этим на сигнальном выходе 59 регистра стратегии поиска 5 будет установлено значение логического нуля. Логический ноль с сигнального выхода 59 регистра стратегии поиска 5 поступает на соответствующий вход 45 формирователя временных интервалов 4 и далее - на первый информационный вход 4.2-1 (вход J) JK-триггера 4.2. На входе «Начальный сброс" 05 устройства устанавливают значение логической единицы, которая поступает на входы 42 и 63 формирователя временных интервалов 4 и блока формирования адреса маски переходов 6 соответственно. Значение логической единицы с входа «Начальный сброс» 42 формирователя временных интервалов 4 (см. фиг. 6) через первый двухвходовый элемент ИЛИ 4.1 поступает на второй информационный вход 4.2-2 (вход K) JK-триггера 4.2, а через второй двухвходовый элемент ИЛИ 4.6 - на вход сброса (вход R) счетчика 4.7. Логическая единица на входе 4.2-2 (входе K) JK-триггера 4.2 при наличии логического нуля на его входе 4.2-1 (входе J) приводит к установке логического нуля на выходе 4.2-3 JK-триггера 4.2, который, поступая на второй вход 4.3-2 двухвходового элемента И 4.3, приводит к установке значения логического нуля на его выходе 4.3-3 вне зависимости от логических значений на его первом входе 4.3-1. Логическая единица на входе сброса R счетчика 4.7 обеспечивает установку логического нуля на его выходе переполнения Р. Значение логического нуля с выхода переполнения Р счетчика 4.7 поступает на второй вход 4.5-2 второго двухвходового элемента И 4.5, что приводит к безусловной установке на его выходе 4.5-3, а соответственно и на выходе «Сброс» 44 формирователя временных интервалов 4, значения логического нуля. Логическая единица с входа «Начальный сброс» 63 блока формирования адреса маски переходов 6 (см. фиг. 8) через двухвходовый элемент ИЛИ 6.3 поступает на вход сброса 6.4-3 (входа R) регистра 6.4, что приводит к установке логического нуля на его выходах 6.4-4 (Q1-QK), а соответственно и на всех разрядах K-разрядного выхода «Код события» 62. По завершении операции начального сброса на входе «Начальный сброс» 05 устройства устанавливают значение логического нуля, что приводит к установке значения логического нуля на втором информационном входе 4.2-2 (входе K) JK-триггера 4.2 и на входе сброса R счетчика 4.7 формирователя временных интервалов 4.

Установка первой и второй битовых масок, обеспечивающих идентификацию каждого из N типов БДИ, осуществляется в соответствующие блоки хранения маски 11-1N. Для этого на первых L-разрядных входах «Маска 1» 021-02N устройства и на соответствующих первых L-разрядных входах «Маска 1» 121-12N каждого из N блоков хранения маски 11-1N устанавливают соответствующие первые битовые маски, а на первых L-разрядных входах «Маска 2» 031-03N устройства и на соответствующих первых L-разрядных входах «Маска 2» 131-13N каждого из N блоков хранения маски 11-1N устанавливают соответствующие вторые битовые маски. На входе разрешения записи 01 устройства и на соответствующих входах разрешения записи 101-10N каждого из N блоков хранения маски 11-1N устанавливают значение логической единицы, которая поступает на входы инициализации (входы С) первых и вторых регистров 1.1 и 1.2 каждого из N блоков хранения маски (см. фиг. 5) и обеспечивает запись первых и вторых битовых масок в соответствующие регистры. По окончании операции записи на входе разрешения записи 01 устройства и на соответствующих входах разрешения записи 101-10N каждого из N блоков хранения маски 11-1N устанавливают значение логического нуля.

Установка маски начала сценария поиска и масок переходов осуществляется в оперативное запоминающее устройство 5.2 регистра стратегии поиска 5. При этом маска начала сценария поиска MB должна быть записана в оперативное запоминающее устройство по нулевому адресу, а n-ая маска перехода MPn,

Установка маски окончания сценария поиска MF заключается в установке на разрядах N-разрядного входа «Правило завершения поиска» 07 устройства и, следовательно, на разрядах N-разрядного входа «Правило завершения поиска» 72 блока индикации 7 (см. фиг. 9) соответствующих логических значений, соответствующих значениям битов маски окончания сценария поиска.

Установка времени ожидания очередного БДИ заключается в установке на разрядах M-разрядного входа «Код времени ожидания» 06 устройства и, следовательно, на разрядах M-разрядного входа «Код времени ожидания» 43 формирователя временных интервалов 4 (см. фиг. 6), логических значений, соответствующих значениям разрядов кода времени ожидания.

Установка начального максимального времени поиска заключается в установке на разрядах каждого из N S-разрядных входов «Коррекция максимального времени поиска» 0161-016N устройства (см. фиг. 3) через S-разрядные входы 271-27N блоков селекции 21-2N на S-разрядные входы 2.71-1-2.7N-1 корректирующих регистров 2.71-2.7N логических значений кода, задающего начальное максимальное время поиска для каждого n-го

После выполнения указанных операций устройство готово к работе.

В начальный период, когда подлежащие анализу БДИ не поступают на вход устройства, на вход 38 делителя частоты 3 через первый тактовый вход 08 устройства от внешнего генератора поступают тактовые импульсы. С выхода 39 делителя частоты 3 тактовые импульсы поступают на второй тактовый вход 41 формирователя временных интервалов 4. В результате проведенной операции начального сброса устройства на всех информационных выходах 6.4-4 (Q1-QN) регистра 6.4, а соответственно и на всех разрядах K-разрядного выхода «Код события» 62 блока формирования маски переходов 6 установлено значение логического нуля. На управляющем входе 54 регистра стратегии поиска 5 установлено значение логического нуля, что обеспечивает коммутацию значений логического нуля с разрядов K-разрядного входа «Код события» 52 регистра стратегии поиска 5 на соответствующие адресные входы 5.2-2 (A1-AK) оперативного запоминающего устройства 5.2. Таким образом, на адресном входе оперативного запоминающего устройства установлен нулевой адрес, указывающий на маску начала сценария поиска. Значения логического нуля с разрядов K-разрядного выхода «Код события» 62 блока формирования адреса маски переходов 6 поступают на соответствующие разряды входа «Код события» 71 блока индикации 7 и далее - на входы 7.1-11-7.1-1N(Y1-YK) дешифратора 7.1 (см. фиг. 9). При наличии значения логического нуля на всех входах 7.1-11-7.1-1K(Y1-YK) дешифратора 7.1, на всех его инверсных выходах

При поступлении БДИ, подлежащего анализу, на Z-разрядном информационном входе 04 устройства устанавливают логические значения, соответствующие значениям двоичных разрядов БДИ. Момент времени, соответствующий установке БДИ на L-разрядном информационном входе 04 устройства, обозначим как T1. С L-разрядного информационного входа 04 устройства БДИ поступает на L-разрядные информационные входы 211-21N блоков селекции 21-2N. Каждый блок селекции осуществляет идентификацию БДИ соответствующего типа. Тип БДИ определяется первой и второй битовыми масками, поступающими соответственно на вторые L-разрядные входы «Маска 1» 221-22N и вторые L-разрядные входы «Маска 2» 231-23N блоков селекции 21-2N. В компараторах 2.3 каждого блока селекции 21-2N (см. фиг. 4) происходит сравнение значений идентификационных битов поступившего БДИ с значениями соответствующих битов второй битовой маски. Выделение идентификационных битов осуществляется в первой и второй группах двухвходовых элементов И 2.11-2.1L, 2.21-2.2L каждого блока селекции на основании соответствующей первой битовой маски. В случае равенства сравниваемых значений на выходе равенства «А=В» 2.3-3 компаратора 2.3 установится значение логической единицы, в противном случае - значение логического нуля. Логическое значение, соответствующее результату сравнения, с выхода «А=В» 2.3-3 компаратора 2.3 в случае, когда задано только начальное максимальное время поиска и внешнее динамическое управление временем поиска отсутствует (нет сигналов на разрядах каждого из N S-разрядных входов «Коррекция максимального времени поиска» 0161-016N устройства), инвертируется инвертором 2.4 и поступает на выход «Результат сравнения» 26 блока селекции 2.

Иными словами, если в ходе анализа поступающих БДИ отсутствует внешнее динамическое управление временем поиска для всех N поисковых запросов, на S-разрядных корректирующих входах 271-27N блоков селекции 21-2N, а значит и на S-разрядных входах 2.71-1-2.7N-1 корректирующих регистров 2.71-2.7N, кодовые сигналы отсутствуют. В этом случае корректирующие регистры 2.71-2.7N блоков селекции 21-2N (см. фиг. 4) идентифицируют начальные коды времени поиска как некорректируемые и транслируют (перезаписывают) их каждый через свои S выходов (2.71-21-2.71-2S)-(2.7N-21-2.1N-2S) на соответствующие S информационных входов (D1-DS) соответствующих счетчиков 2.51-2.5N блоков селекции 21-2N.

Если в ходе идентификации элементов входящего потока данных инициировано внешнее динамическое управление временем поиска для любого n-го

Главный контроллер времени поиска 9 может быть реализован в соответствии со схемой, изображенной на фиг. 3. Динамическая коррекция значений (границ) максимального времени поиска для всех, нескольких из N или конкретного поискового запроса осуществляется в главном контроллере времени поиска 9 следующим образом.

Новые, дополнительно вводимые в динамике управления поиском, значения максимального времени поиска для конкретных поисковых запросов абонентов, в S-разрядном коде поступает через N S-разрядных входов 911-91N главного контроллера времени поиска 9 на N S-разрядных входов 9.1-11-9.1-1N регистрирующего элемента времени поиска 9.1 для контроля и регистрации. С N S-разрядных выходов 9.1-21-9.1-2N регистрирующего элемента времени поиска 9.1 новые значения максимального времени поиска поступают на соответствующие N S-разрядных входов 9.2-11-9.2-1N элемента хранения нового значения времени поиска 9.2, который записывает и хранит в S-разрядном коде эти значения до момента введения очередного управляющего воздействия, а также со своих N S-разрядных выходов 9.2-21-9.2-2N, через соответствующие N S-разрядных выходов 921-92N главного контроллера времени поиска 9, передает эти новые значения максимального времени поиска на корректирующие входы 271-27N соответствующих блоков селекции 21-2N и на проверочные входы 821-82N соответствующих селекционных контроллеров времени поиска 81-8N.

При этом на S-разрядных корректирующих входах 271-21N блоков селекции 21-2N, а значит и на S-разрядных входах 2.71-1-2.7N-1 корректирующих регистров 2.11-2.1N, присутствуют S-разрядные кодовые сигналы. Корректирующие регистры 2.11-2.1N блоков селекции 21-2N (см. фиг. 4) регистрируют изначальный код (записанный при подготовке устройства к работе, т.е. начальное максимальное время поиска) и предварительно сравнивают его с вновь вводимым в динамике управления S-разрядным кодом, который поступает через корректирующие входы 21-21N блоков селекции 21-2N на S-разрядные входы 2.71-1-2.7N-1 корректирующих регистров 2.71-2.7N.

Причем, коррекция (формирование по итогам предварительного сравнения) на S выходах 2.7n-21-2.7n-2S например, корректирующего регистра 2.7n блока селекции 2n кода, характеризующего предварительное решение о значении максимального времени поиска для каждого конкретного n-ого запроса осуществляется следующим образом (см. фиг. 4). Если на S-разрядном входе 2.7n-1 корректирующего регистра 2.7n есть S-разрядный сигнал, обуславливающий новое, вводимое в динамике управления максимальное время поиска, этот сигнал идентифицируется как приоритетный, и именно он с S выходов 2.7n-21-2.7n-2S корректирующего регистра 2.7n поступает на соответствующие S информационных входов (D1-DS) счетчика 2.5n n-го

Таким образом, с S выходов 2.7n-21-2.7n-2S корректирующего регистра 2.7n поступает на соответствующие S информационных входов (D1-DS) счетчика 2.5n n-го

В начальный период, когда подлежащие анализу БДИ не поступают на вход устройства, логическое значение, соответствующее результатам сравнения, на выходе «А=В» 2.3n-3 компаратора 2.3n отсутствует. Трехвходовые элементы И 2.61-2.6N всех блоков селекции закрыты, тактовые импульсы от генератора тактовых импульсов 10 через трехвходовые элементы И 2.61-2.6N на счетные входы Z счетчиков 2.51-2.5N блоков селекции 21-2N не поступают. На выходах «Результат сравнения» 261-26N блоков селекции 21-2N сигнал отсутствует.

Если логические значения, соответствующие результатам сравнения, с выходов «А=В» 2.31-3-2.3N-3 компараторов 2.31-2.3N блоков селекции 21-2N поступают, на выходах 261-26N этих блоков через инверторы 2.41-2.4N предварительно установятся сигналы низкого уровня. На счетные входы Z счетчиков 2.51-2.5N блоков селекции 21-2N, поступают импульсы с выхода 101 генератора тактовых импульсов 10 по цепи: тактовые входы 251-25N блоков селекции 21-2N, открытые трехвходовые элементы И 2.61-2.6N блоков селекции 21-2N. Счетчики 2.51 -2.5N каждого блока селекции выполняют функцию таймеров, которые контролируют истечение допустимого времени (изначального или введенного в рамках управления) поиска путем суммирования поступающих на их счетный вход Z тактовых импульсов и формируют сигнал переполнения на инверсных выходах

Сигналы с выходов «Результат сравнения» 261-26N блоков селекции 21-2N поступают через входы «Результат сравнения» 811-81N селекционных контроллеров времени поиска 81-8N (см. фиг. 2) на сигнальные входы 8.21-1-8.2N-1 регистров сравнения-коррекции максимального времени поиска 8.21-8.2N, на проверочные входы 8.21-2-8.2N-2 которых поступают в двоичном коде с проверочных выходов 8.11-2-8.1N-2 дешифраторов корректированного кода максимального времени поиска 8.11-8.1N сигналы, характеризующие новое, вводимое в процессе управления, значение (границы) максимального времени поиска для конкретного запроса. При этом дешифраторы корректированного кода максимального времени поиска 8.11-8.1N преобразуют S-разрядный код, обуславливающий новые, вводимые в процессе управления, значения (границы) максимального времени поиска в двоичный код и передают этот код для проверки истинности на регистры сравнения-коррекции максимального времени поиска 8.21-8.2N.

Регистры сравнения-коррекции максимального времени поиска 8.21-8.2N осуществляют дополнительную проверку (сравнение) выполнения требований по своевременности в соответствии с изначальным и вновь вводимым максимальным времени поиска и, выступая в качестве ретранслирующих узлов, формируют на своих выходах 8.21-3-8.2N-3 и на выходах «Результат сравнения» 831-83N селекционных контроллеров времени поиска 81-8N последовательность сигналов, описывающих логические значения, соответствующие результатам сравнения.

Таким образом, на выходах «Результат сравнения» 831-83N селекционных контроллеров времени поиска 81-8N имеем логические значения, соответствующие результатам сравнения и полученные с учетом динамической коррекции максимального времени поиска.

После удовлетворения потребности в поиске информации n-ый поисковый запрос снимается, на выходе «А=В» 2.3n-3 компаратора 2.3n сигнал отсутствует, происходит сброс счетчика 2.5n соответствующего блока селекции 2n по n-ому входу «Обнуление» 017n устройства и входу «Обнуление» 24n соответствующего блока селекции 2n.

В случае, если один или несколько поисковых запросов достигли максимального времени поиска или максимальное время поиска уменьшилось в результате динамической коррекции (управления), происходит переполнение счетчиков 2.51-2.5N соответствующих блоков селекции 21-2N, формирование на их инверсных выходах переполнения

При этом запираются соответствующие трехвходовые элементы И 2.61-2.6N (фиг. 4), запрещая поступление тактовых импульсов на счетные входы Z соответствующих счетчиков 2.51-2.5N блоков селекции 21-2N.

Логические значения, соответствующие результатам сравнения и полученные с учетом динамической коррекции максимального времени поиска с выходов «Результат сравнения» 831-83N селекционных контроллеров времени поиска 81-8N поступают на соответствующие входы «Результат сравнения» 511-51N регистра стратегии поиска 5 и соответствующие входы «Результат сравнения» 611-61N блока формирования адреса маски переходов 6.

При этом, при поступлении БДИ, тип которого соответствует одному из типов БДИ, предусмотренных в сценарии поиска, на выходе «Результат сравнения» 26n, например, блока селекции 2n и на соответствующем выходе «Результат сравнения» 83n селекционного контроллера времени поиска 8n, где обнаружено совпадение значений идентификационных битов поступившего БДИ с соответствующими значениями второй битовой маски, будет установлено значение логического нуля, а на выходах всех остальных блоков селекции и, как следствие, селекционных контроллеров времени поиска - значение логической единицы. При поступлении БДИ, не предусмотренного сценарием поиска, на выходах «Результат сравнения» всех блоков селекции и, как следствие, выходах «Результат сравнения» селекционных контроллеров времени поиска будет установлено значение логической единицы.