Изобретение относится к области электросвязи и может быть использовано для поиска и оперативной идентификации информации в сетях передачи данных с коммутацией пакетов и в информационно-справочных (поисковых) системах.

Известно устройство по Патенту РФ №РФ №2115952 «Устройство поиска информации» МПК G06F 17/40, опубликованное 20.07.98 и включающее регистры границ, суммирующие и вычитающие счетчики, схемы сравнения, блоки памяти и блоки вычисления. Этот аналог в ходе приема цифрового сообщения и поиска определенной цифровой последовательности позволяет определить параметры и соответствие последовательности передачи правилам обмена данными, установленным для данного протокола.

Недостатком данного устройства является относительно большое время, необходимое для идентификации пакетов (так как идентификация осуществляется путем последовательного анализа значений признаков) и узкая область применения - только для анализа протокола TFTP на предмет соответствия наблюдаемой последовательности пакетов правилам, установленным для данного протокола. Все это ограничивает применение устройства-аналога для анализа протоколов в современных высокоскоростных вычислительных сетях.

Известно устройство по Патенту РФ №2313128 «Устройство поиска информации» МПК G06F 9/46, опубликованное 20.12.2007 г., Бюл. №35. Это устройство содержит N≥2 блоков хранения маски, N блоков селекции, делитель частоты, формирователь временных интервалов, регистр стратегии поиска, блок формирования адреса маски переходов и блок индикации. Устройство обеспечивает расширение области применения и быстродействие анализа входящих пакетов устройства-прототипа за счет идентификации пакетов путем параллельного анализа значений признаков идентификации и контроля последовательности обмена ими на предмет соответствия любым, априорно заданным правилам.

Однако данное устройство имеет недостаток - относительно низкую вероятность своевременного поиска информации в условиях непрерывной динамики смены состояний разноприоритетных запросов на поиск информации и с учетом влияющих факторов.

Из известных наиболее близким аналогом (прототипом) по своей технической сущности заявленному устройству является устройство по Патенту РФ №2553093 «Устройство поиска информации» МПК G06F 9/46, опубликованное 10.06.2015 г., Бюл. №16.

Устройство-прототип включает N≥2 блоков хранения маски, N блоков селекции, делитель частоты, формирователь временных интервалов, регистр стратегии поиска, блок формирования адреса маски переходов, блок индикации, N селекционных контроллеров времени поиска, главный контроллер времени поиска и генератор тактовых импульсов.

В устройстве-прототипе тактовый вход делителя частоты является первым тактовым входом устройства, а выход делителя частоты соединен с тактовым входом формирователя временных интервалов, при этом K-разрядный, где К=(log2 N)+1, выход «Код события» блока формирования адреса маски переходов подключен к K-разрядным входам «Код события» регистра стратегии поиска и блока индикации соответственно, входы разрешения записи N блоков хранения маски объединены и являются входом разрешения записи устройства, L-разрядные информационные входы, где L≥2, N блоков селекции объединены и являются L-разрядным информационным входом устройства. Первые L-разрядные входы «Маска 1» и «Маска 2» N блоков хранения маски, являются первыми L-разрядными входами соответственно «Маска 1» и «Маска 2» устройства, вторые L-разрядные выходы «Маска 1» и «Маска 2» N блоков хранения маски подключены к вторым L-разрядным входам «Маска 1» и «Маска 2» соответствующих блоков селекции, вход «Начальный сброс» формирователя временных интервалов соединен с входом «Начальный сброс» блока формирования адреса маски переходов и является входом «Начальный сброс» устройства, при этом, М-разрядный вход «Код времени ожидания» формирователя временных интервалов, где М≥2 - разрядность кода времени ожидания, является М-разрядным входом «Код времени ожидания» устройства, а выход формирователя временных интервалов соединен с входом «Сброс» блока формирования адреса маски переходов, сигнальный выход регистра стратегии поиска соединен с сигнальными входами формирователя временных интервалов и блока формирования адреса маски переходов, K-разрядный адресный вход, управляющий вход, N-разрядный информационный вход и разрешающий вход регистра стратегии поиска являются соответственно K-разрядным адресным входом, управляющим входом, N-разрядным информационным входом и разрешающим входом устройства, входы «Выбор кристалла» и «Чтение/запись» регистра стратегии поиска являются соответственно входами «Выбор кристалла» и «Чтение/запись» устройства, N-разрядный вход «Правило завершения поиска» и выход «Результат поиска» блока индикации являются соответственно N-разрядным входом «Правило завершения поиска» и выходом «Результат поиска» устройства. При этом выход «Результат сравнения» n-го блока селекции, где n=1, 2, …, N, соединен с входом «Результат сравнения» n-го селекционного контроллера времени поиска, выход «Результат сравнения» которого соединен с n-м входом «Результат сравнения» регистра стратегии поиска и с n-м входом «Результат сравнения» блока формирования адреса маски переходов, выход генератора тактовых импульсов подключен к тактовому входу n-ого блока селекции, вход «Обнуление» которого является n-м входом «Обнуление» устройства, причем S-разрядный корректирующий вход, где S≥2 - разрядность корректирующего кода времени поиска, n-ого блока селекции объединен с S-разрядным проверочным входом n-ого селекционного контроллера времени поиска и подключен к n-ому S-разрядному выходу главного контроллера времени поиска, N S-разрядных входов которого являются соответствующими N S-разрядными входами «Коррекция максимального времени поиска» устройства.

Такая схема, по сравнению с устройствами-аналогами, позволяет повысить вероятность своевременного поиска информации в условиях непрерывной динамики смены состояний поисковых запросов и с учетом влияющих факторов, за счет дешифровки, динамической коррекции и синхронизации значений (границ) максимального времени поиска для каждого конкретного сценария (поискового запроса).

Однако прототип имеет недостаток - относительно низкую достоверность определения типа ожидаемых блоков двоичной информации (БДИ), в условиях, характерных для поисковых процессов, протекающих в реальных системах, когда параметры сценария поиска (значения признаков идентификации (битовых масок) и порядок их следования), могут носить недостоверный (недостаточный, неполный и противоречивый) характер.

Данное устройство позволяет реализовывать поисковые запросы с учетом динамики управляющих воздействий и внешних факторов, с учетом изменяющихся во времени текущих требований абонентов к своевременности поиска информации, в то время как при поиске информации в реальных системах, широкое применение находят нейросетевые модели [1-6], объективно основанные на недостоверно (недостаточно, неполно и противоречиво) заданных значениях параметров сценария поиска, где значения признаков идентификации (битовых масок) и порядок их следования, определяющие тип БДИ, носят недостаточный (неполный и противоречивый) характер, традиционно описываемый с привлечением математики искусственных нейронных сетей.

Под «поиском» понимается параллельный анализ значений признаков идентификации БДИ и контроль порядка их следования на предмет соответствия заданным правилам - определение кода типа БДИ.

Под «сценарием поиска» понимается классический метод формальной графики, определяющий заданные правила следования БДИ.

Под «признаком идентификации» понимаются значения битов в соответствующих позициях БДИ.

Под «кодом типа БДИ» понимается код, соответствующий сценарию поиска и, с точки зрения физики процесса, адресу, по которому в оперативном запоминающем устройстве хранится маска переходов, определяющая этот конкретный тип ожидаемых БДИ.

Под «параметрами сценария поиска» понимается набор параметров, описывающих правила следования блоков двоичной информации - набор (множество бит кода) значений признаков идентификации (битовых масок) этих блоков и порядок их следования.

Под «реализацией поисковых запросов» понимается совокупность действий информационно-справочной (поисковой) системы, включающая выборку запроса на поиск информации из очереди, выделение этому запросу ресурса и собственно поиск информации в соответствии с заданным сценарием поиска, а также проведение завершающих операций. Поисковый запрос - посылка сигнала на поиск, инициирующего ответ.

Целью изобретения является разработка устройства, обеспечивающего повышение достоверности определения типа ожидаемых блоков двоичной информации за счет обеспечения возможности поиска информации с учетом верификации (нейроанализа) данных, характеризующих неоднозначно (недостоверно, неполно) заданные значения признаков идентификации (адреса битовых масок) - значения кода типа БДИ, создание устройства поиска информации, способного с высокой достоверностью реализовывать поисковые запросы, характерные для реальных поисковых систем - когда сценарий поиска реализуются в условиях недостаточности (неполноты и противоречивости) данных об истинных значениях параметров поиска.

Указанная цель достигается тем, что в известное устройство поиска информации, содержащее N≥2 блоков хранения маски, N блоков селекции, делитель частоты, формирователь временных интервалов, регистр стратегии поиска, блок формирования адреса маски переходов, блок индикации, N селекционных контроллеров времени поиска, главный контроллер времени поиска и генератор тактовых импульсов, дополнительно включены блок проверки сценария поиска, предназначенный для предварительного анализа данных об истинных значениях кода типа БДИ, и блок коррекции сценария поиска, предназначенный для записи, хранения результатов анализа кода типа БДИ и математически корректной верификации этого кода, идентифицируемого на основе неоднозначного (недостоверного, неполного) сценария, к виду, пригодному для получения однозначных (достоверных) результатов конкретного поиска. При этом тактовый вход делителя частоты является первым тактовым входом устройства, а выход делителя частоты соединен с тактовым входом формирователя временных интервалов, входы разрешения записи N блоков хранения маски объединены и являются входом разрешения записи устройства, L-разрядные информационные входы, где L≥2, N блоков селекции объединены и являются L-разрядным информационным входом устройства. Причем первые L-разрядные входы «Маска 1» и «Маска 2» N блоков хранения маски, являются первыми L-разрядными входами соответственно «Маска 1» и «Маска 2» устройства. Вторые L-разрядные выходы «Маска 1» и «Маска 2» N блоков хранения маски подключены ко вторым L-разрядным входам «Маска 1» и «Маска 2» соответствующих блоков селекции. Вход «Начальный сброс» формирователя временных интервалов соединен с входом «Начальный сброс» блока формирования адреса маски переходов и является входом «Начальный сброс» устройства. При этом, М-разрядный вход «Код времени ожидания» формирователя временных интервалов, где М≥2 - разрядность кода времени ожидания, является М-разрядным входом «Код времени ожидания» устройства, а выход формирователя временных интервалов соединен с входом «Сброс» блока формирования адреса маски переходов, сигнальный выход регистра стратегии поиска соединен с сигнальными входами формирователя временных интервалов и блока формирования адреса маски переходов. Причем K-разрядный адресный вход, где K=(log2 N)+1, управляющий вход, N-разрядный информационный вход и разрешающий вход регистра стратегии поиска являются соответственно K-разрядным адресным входом, управляющим входом, N-разрядным информационным входом и разрешающим входом устройства, входы «Выбор кристалла» и «Чтение/запись» регистра стратегии поиска являются соответственно входами «Выбор кристалла» и «Чтение/запись» устройства, N-разрядный вход «Правило завершения поиска» и выход «Результат поиска» блока индикации являются соответственно N-разрядным входом «Правило завершения поиска» и выходом «Результат поиска» устройства. При этом выход «Результат сравнения» n-го блока селекции, где n=1, 2, …, N, соединен с входом «Результат сравнения» n-го селекционного контроллера времени поиска, выход «Результат сравнения» которого соединен с n-м входом «Результат сравнения» регистра стратегии поиска и с n-м входом «Результат сравнения» блока формирования адреса маски переходов. Выход генератора тактовых импульсов подключен к тактовому входу «n-ого блока селекции, вход «Обнуление» которого является n-м входом «Обнуление» устройства. При этом S-разрядный корректирующий вход, где S≥2 - разрядность корректирующего кода времени поиска, n-ого блока селекции объединен с S-разрядным проверочным входом n-ого селекционного контроллера времени поиска и подключен к n-ому S-разрядному выходу главного контроллера времени поиска, N S-разрядных входов которого являются соответствующими N S-разрядными входами «Коррекция максимального времени поиска» устройства. Причем K-разрядный выход «Код события» блока формирования адреса маски переходов соединен с K-разрядным входом блока проверки сценария поиска, K-разрядный корректировочный выход которого подключен K-разрядному корректировочному входу блока коррекции сценария поиска, контрольный вход которого соединен с контрольным выходом блока проверки сценария поиска. При этом K-разрядный прямой выход блока проверки сценария поиска соединен с K-разрядным прямым выходом блока коррекции сценария поиска и подключен к K-разрядным входам «Код события» регистра стратегии поиска и блока индикации соответственно.

Блок проверки сценария поиска состоит из селектора кода типа БДИ и преобразователя кода типа БДИ, предназначенных соответственно для предварительного анализа (селекции) и регистрации данных, характеризующих значения кода типа БДИ, а также преобразования этих данных из параллельного кода в последовательный. При этом К-разрядный выход преобразователя кода типа БДИ является K-разрядным корректировочным выходом блока проверки сценария поиска, выход передачи преобразователя кода типа БДИ является контрольным выходом блока проверки сценария поиска, разрешающий выход преобразователя кода типа БДИ соединен с инверсным разрешающим входом селектора кода типа БДИ, K-разрядный выход которого является K-разрядным прямым выходом блока проверки сценария поиска. Запрещающий вход преобразователя кода типа БДИ подключен к запрещающему выходу селектора кода типа БДИ, K-разрядный вход которого соединен с K-разрядным входом преобразователя кода типа БДИ и является K-разрядным входом блока проверки сценария поиска.

Блок коррекции сценария поиска состоит из программируемого вычислителя и запоминающего элемента, предназначенных соответственно для преобразования идентифицируемых недостоверно (неполно, противоречиво) значений кода типа БДИ, а также для записи и хранения верифицированных значений этого кода. При этом K-разрядный вход I программируемого вычислителя является K-разрядным корректировочным входом блока коррекции сценария поиска. Вход разрешения выходов А программируемого вычислителя является контрольным входом блока коррекции сценария поиска, К выходов А программируемого вычислителя соединены с соответствующими К входами запоминающего элемента, K-разрядный выход которого является K-разрядным прямым выходом блока коррекции сценария поиска.

Благодаря новой совокупности существенных признаков, за счет введения блока проверки сценария поиска, обеспечивающего предварительное выявление (селекцию) неоднозначно (недостоверно, неполно) идентифицируемых значений кода типа БДИ и блока коррекции сценария поиска, обеспечивающего запись, хранение результатов анализа значений кода типа БДИ и математически корректное вычислительное преобразование (распознавание) этих значений с использованием нейроматематических методов, в заявленном устройстве достигается возможность предварительного анализа и верификации кода типа БДИ, обуславливающая повышение достоверности определения типа ожидаемых блоков двоичной информации, и, как следствие, повышение достоверности выполнения поисковых запросов, характерного для реальных поисковых систем - когда сценарий поиска реализуется в условиях недостаточности (неполноты и противоречивости) данных об истинных значениях параметров данного сценария.

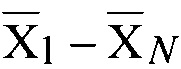

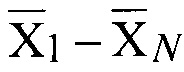

Заявленное устройство поясняется чертежами, на которых представлены:

на фиг. 1 - структурная схема устройства поиска информации;

на фиг. 2 - структурная схема блока проверки сценария поиска;

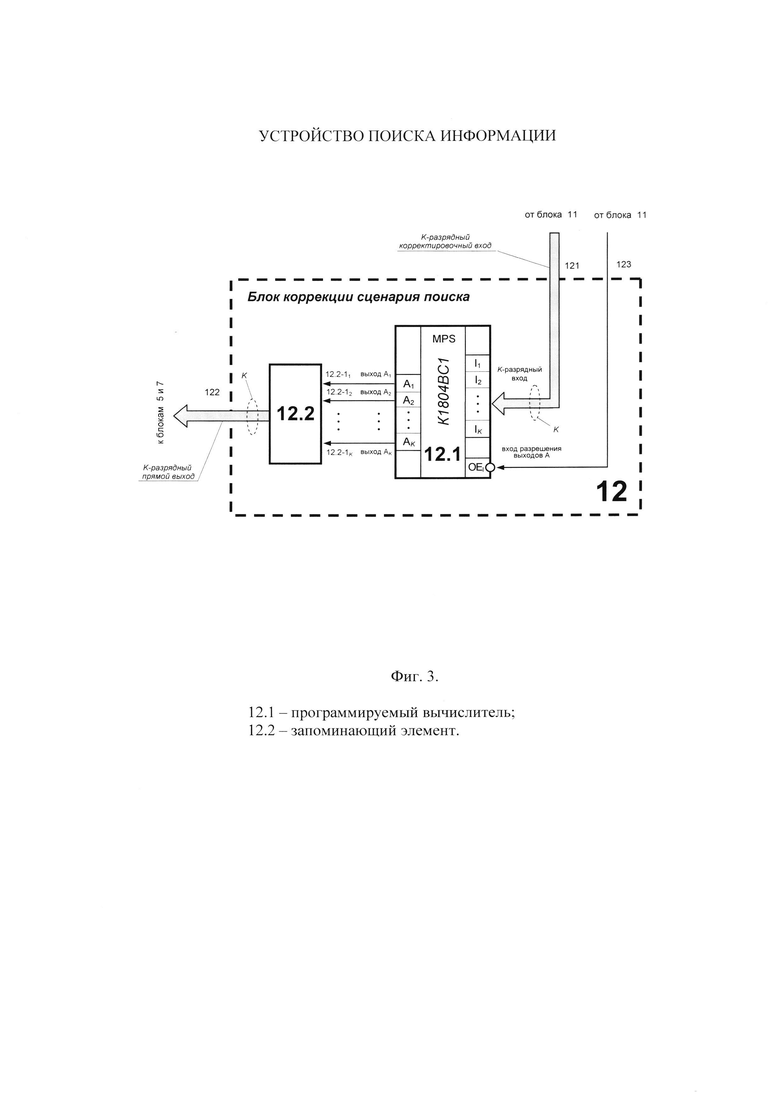

на фиг. 3 - структурная схема блока коррекции сценария поиска;

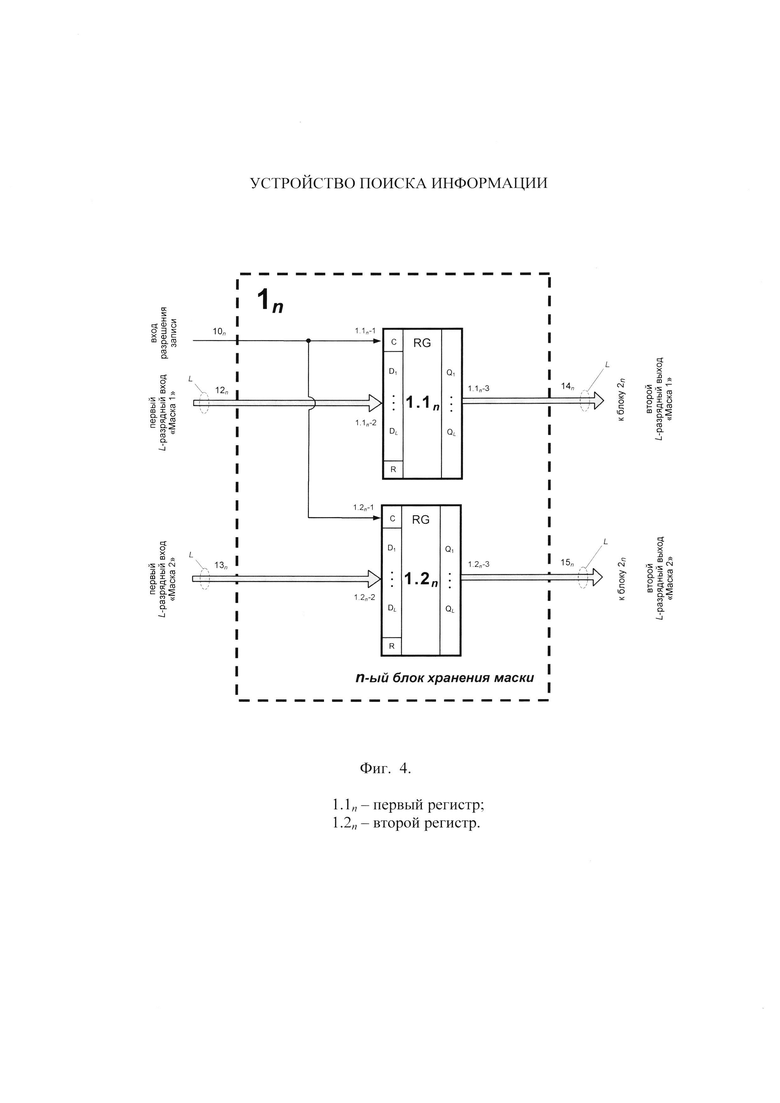

на фиг. 4 - структурная схема n-го ( ) блока хранения маски;

) блока хранения маски;

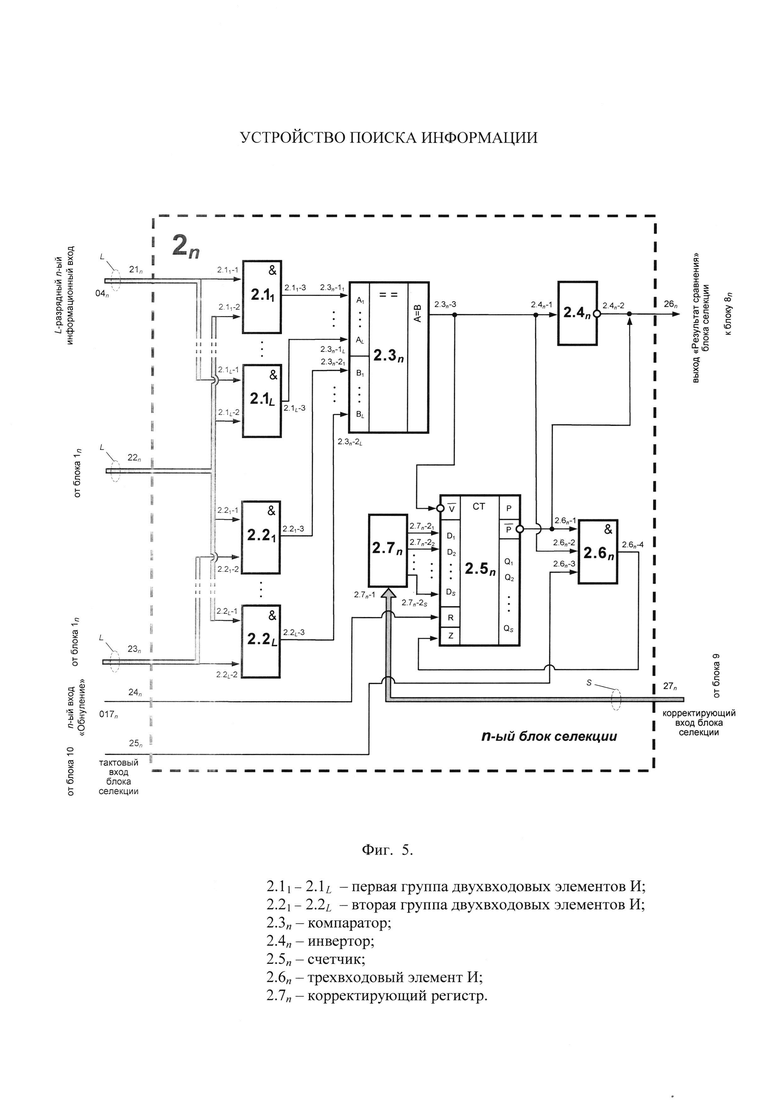

на фиг. 5 - структурная схема n-го ( ) блока селекции;

) блока селекции;

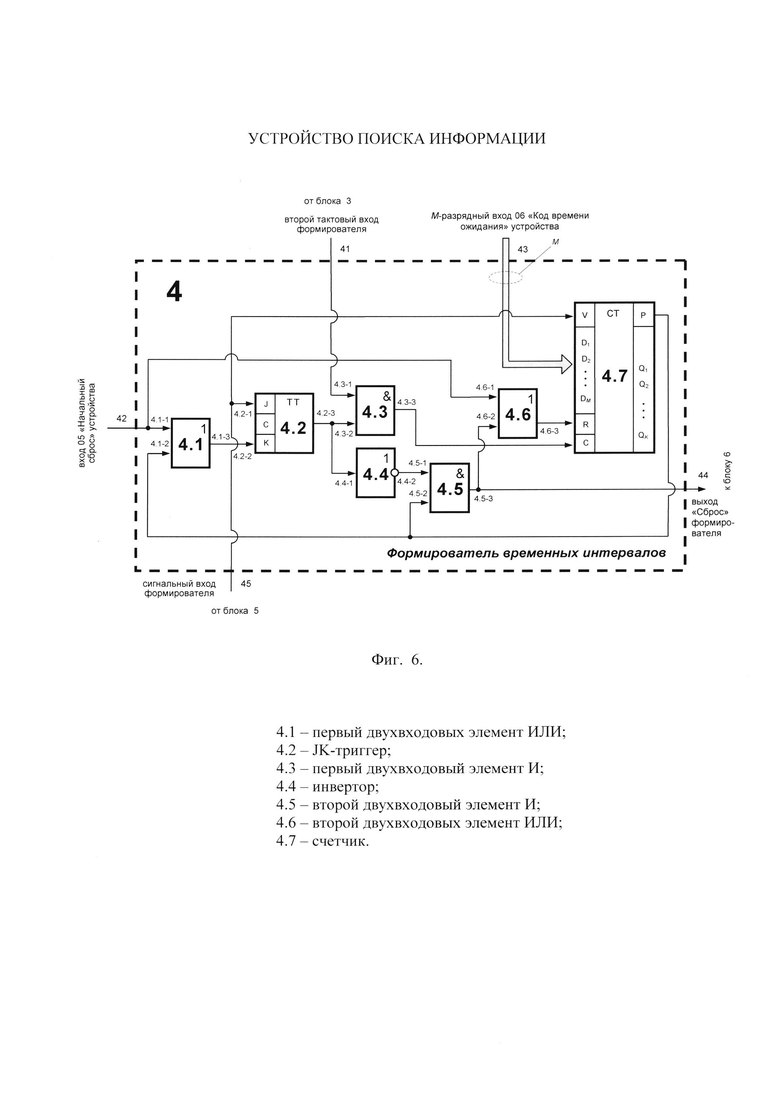

на фиг. 6 - структурная схема формирователя временных интервалов;

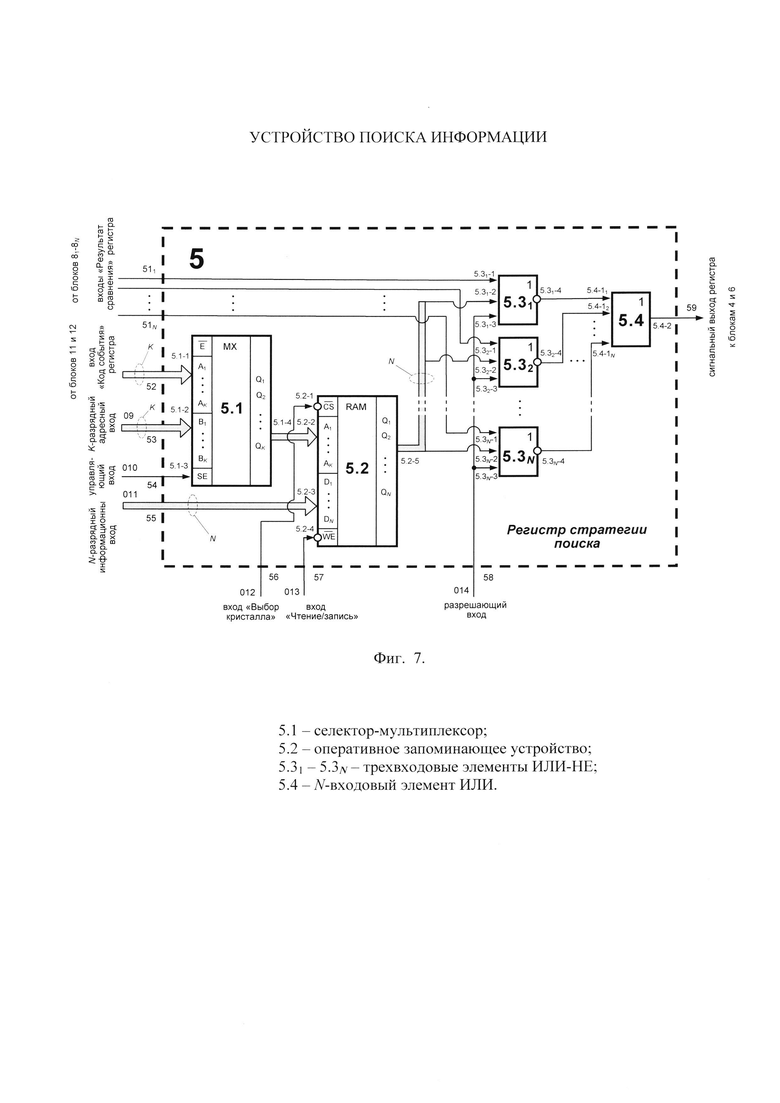

на фиг. 7 - структурная схема регистра стратегии поиска;

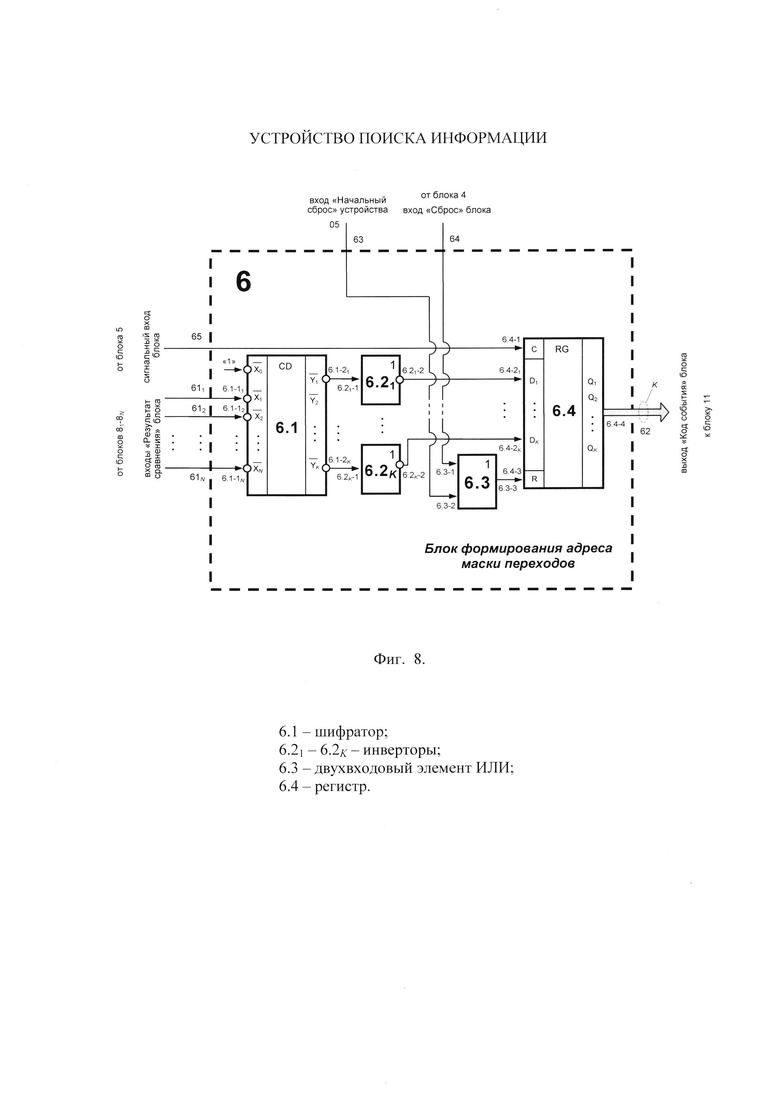

на фиг. 8 - структурная схема блока формирования адреса маски переходов;

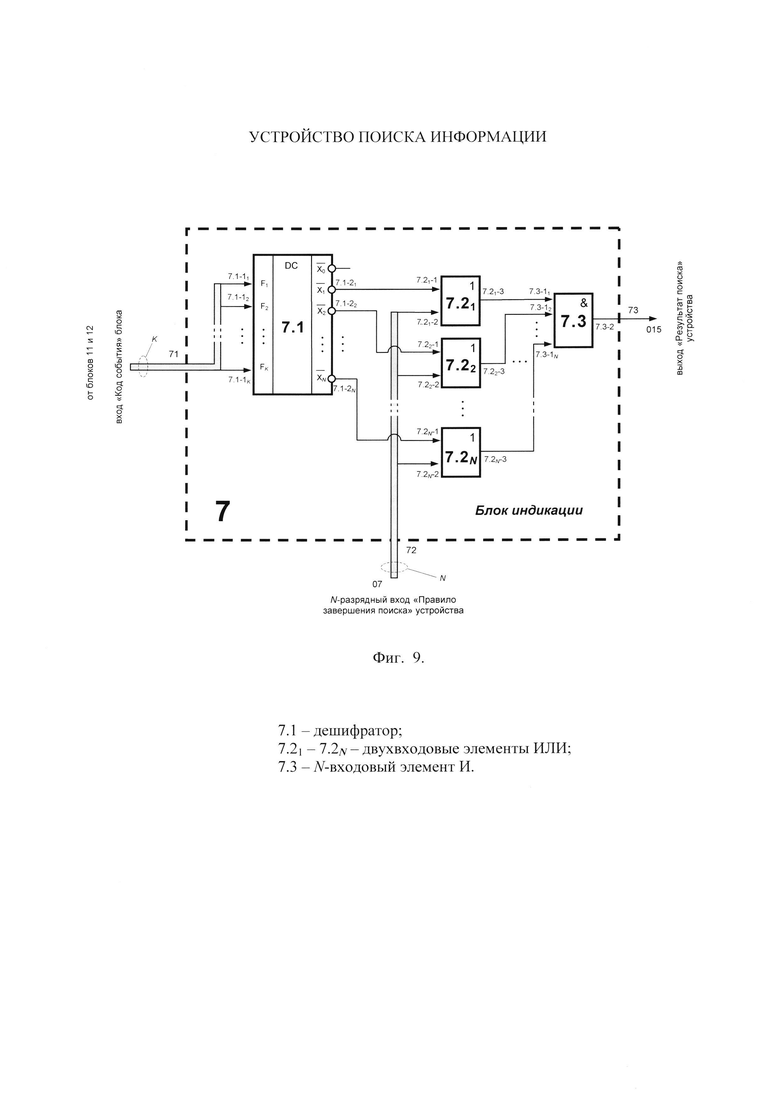

на фиг. 9 - структурная схема блока индикации;

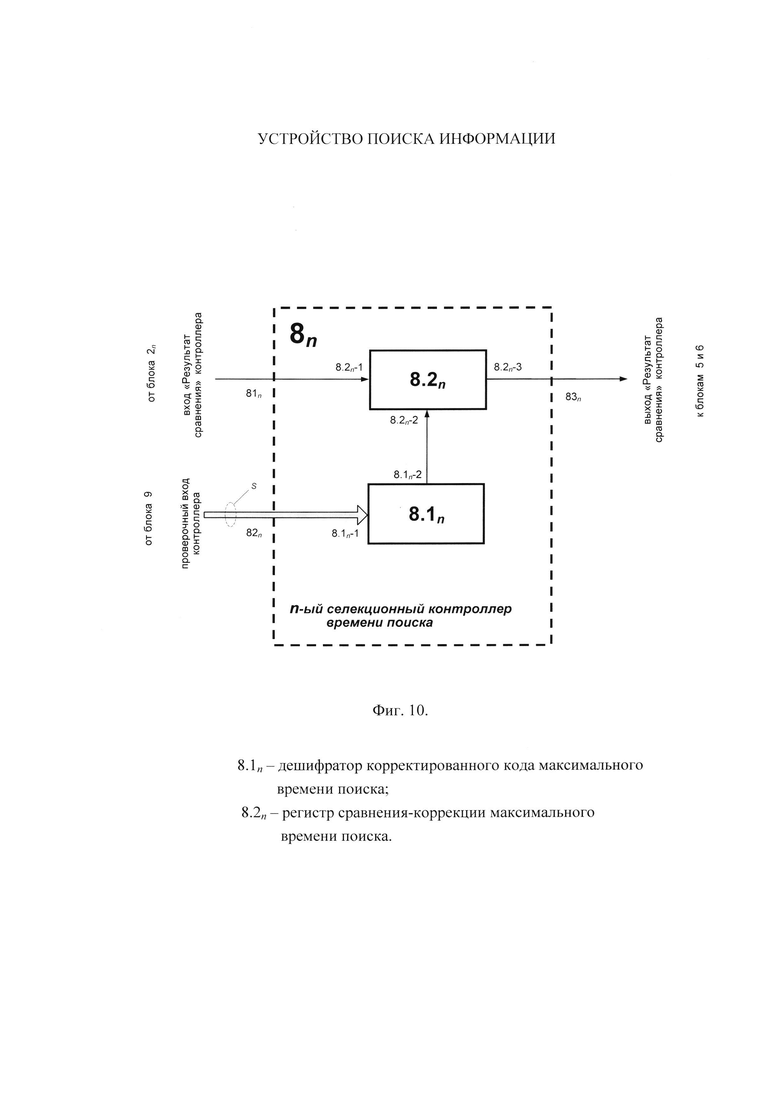

на фиг. 10 - структурная схема n-го ( ) селекционного контроллера времени поиска;

) селекционного контроллера времени поиска;

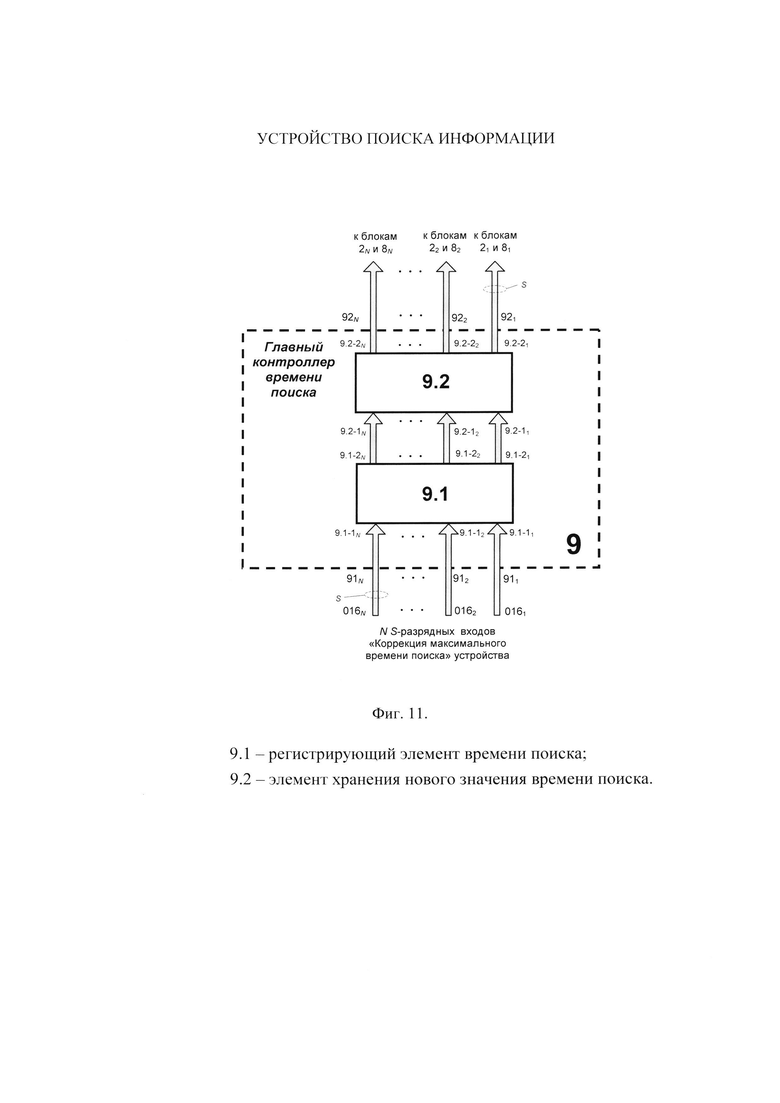

на фиг. 11 - структурная схема главного контроллера времени поиска;

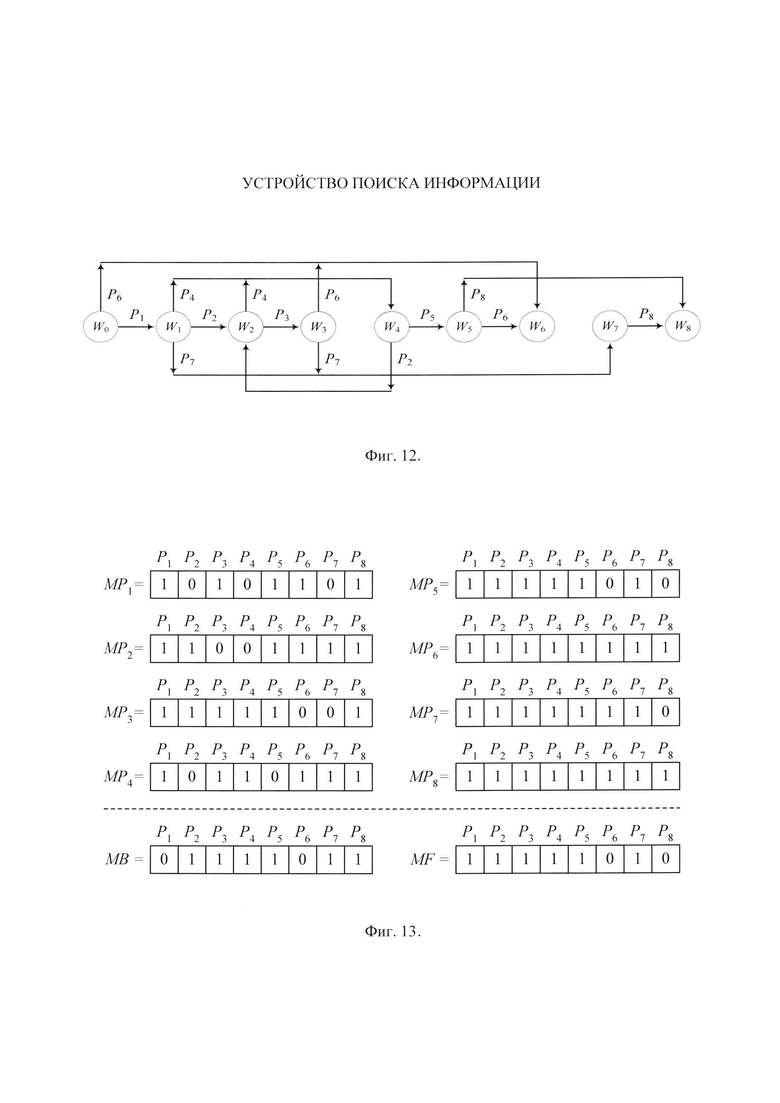

на фиг. 12 - пример сценария поиска;

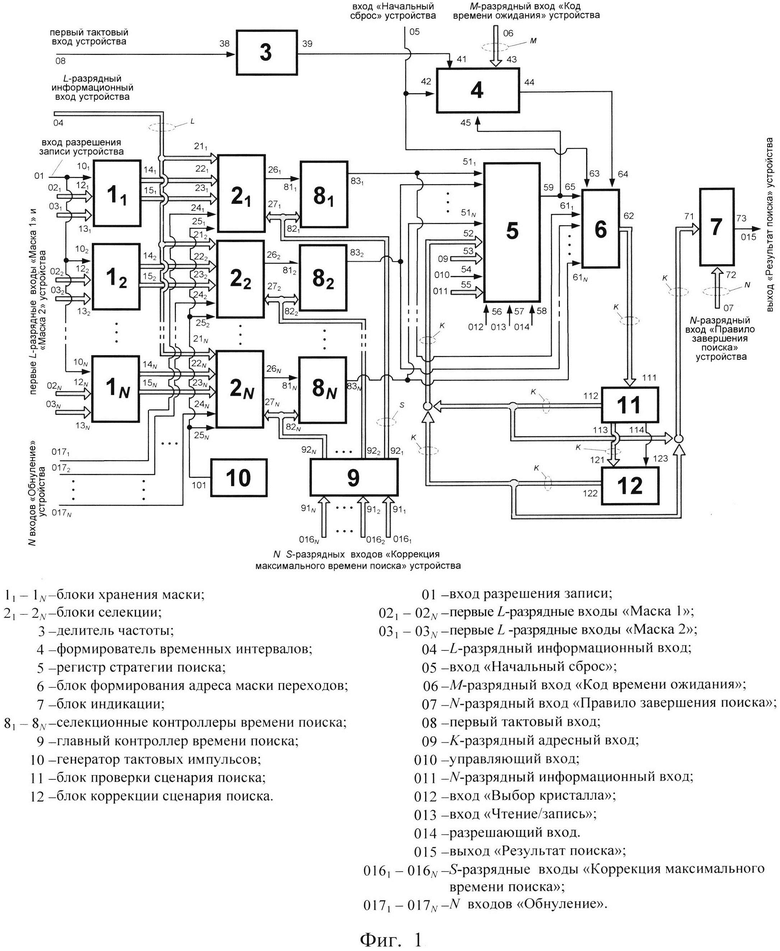

на фиг. 13 - пример заполнения масок переходов, маски начала сценария и маски окончания сценария.

Устройство (см. фиг. 1) состоит из N, где N≥2, блоков хранения маски 11-1N, N блоков селекции 21-2N, делителя частоты 3, формирователя временных интервалов 4, регистра стратегии поиска 5, блока формирования адреса маски переходов 6, блока индикации 7, N селекционных контроллеров времени поиска 81-8N, главного контроллера времени поиска 9, генератора тактовых импульсов 10, блока проверки сценария поиска 11 и блока коррекции сценария поиска 12.

Элементы соединены между собой следующим образом (см. фиг. 1). Тактовый вход 38 делителя частоты 3 является первым тактовым входом 08 устройства, а выход 39 делителя частоты 3 соединен с тактовым входом 41 формирователя временных интервалов 4. Входы разрешения записи 101-10N N блоков хранения маски 11-1N объединены и являются входом разрешения записи 01 устройства. L-разрядные информационные входы 211-21N, где L≥2, N блоков селекции 21-2N объединены и являются L-разрядным информационным входом 04 устройства. Первые L-разрядные входы «Маска 1» 12n и «Маска 2» 13n n-го блока хранения маски 1n, где n=1, 2, …, N, являются n-ми первыми L-разрядными входами соответственно «Маска 1» 02n и «Маска 2» 03n устройства. Вторые L-разрядные выходы «Маска 1» 14n и «Маска 2» 15n n-го блока хранения маски 1n подключены к соответствующим вторым L-разрядным входам «Маска 1» 22n и «Маска 2» 23n n-го блока селекции 2n. Вход «Начальный сброс» 42 формирователя временных интервалов 4 соединен с входом «Начальный сброс» 63 блока формирования адреса маски переходов 6 и является входом «Начальный сброс» 05 устройства. При этом, М-разрядный вход «Код времени ожидания» 43 формирователя временных интервалов 4, где М≥2 - разрядность кода времени ожидания, является М-разрядным входом «Код времени ожидания» 06 устройства, а выход 44 формирователя временных интервалов 4 соединен с входом «Сброс» 64 блока формирования адреса маски переходов 6. Сигнальный выход 59 регистра стратегии поиска 5 соединен с сигнальными входами 45 и 65 формирователя временных интервалов 4 и блока формирования адреса маски переходов 6 соответственно. K-разрядный, где К=(log2 N)+1, адресный вход 53, управляющий вход 54, N-разрядный информационный вход 55 и разрешающий вход 58 регистра стратегии поиска 5 являются соответственно K-разрядным адресным входом 09, управляющим входом 010, N-разрядным информационным входом 011 и разрешающим входом 014 устройства. Входы «Выбор кристалла» 56 и «Чтение/запись» 57 регистра стратегии поиска 5 являются соответственно входами «Выбор кристалла» 012 и «Чтение/запись» 013 устройства. N-разрядный вход «Правило завершения поиска» 72 и выход «Результат поиска» 73 блока индикации 7 являются соответственно N-разрядным входом «Правило завершения поиска» 07 и выходом «Результат поиска» 015 устройства. Выходы «Результат сравнения» 261-26N блоков селекции 21-2N соединены с соответствующими входами «Результат сравнения» 811-81N соответствующих селекционных контроллеров времени поиска 81-8N, выходы «Результат сравнения» 831-83N которых соединены с соответствующими входами «Результат сравнения» 511-51N регистра стратегии поиска 5 и с соответствующими входами «Результат сравнения» 611-61N блока формирования адреса маски переходов 6. Выход 101 генератора тактовых импульсов 10 подключен к тактовым входам 251-25N каждого из N блоков селекции 21-2N, входы «Обнуление» 241-24N которых являются соответствующими входами «Обнуление» 0171-017N устройства. Причем S-разрядный, где S≥2 - разрядность корректирующего кода времени поиска, корректирующий вход 27n n-ого блока селекции 2n соединен с S-разрядным проверочным входом 82n n-ого селекционного контроллера времени поиска 8n и подключен к n-ому S-разрядному выходу 92n главного контроллера времени поиска 9, N S-разрядных входов 911-91N которого являются соответствующими N S-разрядными входами «Коррекция максимального времени поиска» 016 устройства. При этом K-разрядный выход «Код события» 62 блока формирования адреса маски переходов 6 соединен с K-разрядным входом 111 блока проверки сценария поиска 11, K-разрядный корректировочный выход 113 которого подключен к K-разрядному корректировочному входу 121 блока коррекции сценария поиска 12, контрольный вход 123 которого соединен с контрольным выходом 114 блока проверки сценария поиска 11, K-разрядный прямой выход 112 которого соединен с K-разрядным прямым выходом 122 блока коррекции сценария поиска 12 и подключен к K-разрядным входам «Код события» 52 и 71 регистра стратегии поиска 5 и блока индикации 7 соответственно.

Число «N, (N≥2)» (блоков, разрядов, входов, выходов и т.п.) определяется в соответствии с возможным количеством типов БДИ (они определяют общее количество масок переходов, характеризующих состав сценариев поиска) и, как правило, составляет от 2 (двух) до 500 (пятисот).

Число «K, (где K=(log2 N)+1)» характеризует разрядность кода адреса маски переходов, адреса, по которому в оперативном запоминающем устройстве хранится маска переходов, определяющая тип ожидаемых согласно сценария поиска БДИ. Иными словами, это количество двоичных разрядов, достаточное для адресации N масок переходов и маски начала сценария поиска, как правило, составляет от 2 (двух) до 20 (двадцати).

Число «М, (М≥2)» характеризует разрядность кода времени ожидания - кода допустимого интервала времени, в течение которого ожидается очередной БДИ, заданный сценарием поиска и, как правило, составляет от 2 (двух) до 10 (десяти).

Число «L, (L≥2)» характеризует максимально возможное количество разрядов в БДИ, используемых в сценарии поиска и составляет от 2 (двух) до 10 (десяти).

Число «S, (S≥2)» характеризует разрядность корректирующего кода времени поиска, разрядность кода, обуславливающего изначальное или подвергшееся коррекции (новое) значение максимального времени поиска для каждого конкретного сценария (поискового запроса) и, как правило, составляет от 2 (двух) до 10 (десяти).

Блок проверки сценария поиска 11, изображенный на фиг. 2, предназначен для предварительного анализа (селекции) данных об истинных значениях кода типа БДИ и принятия решения о математической природе этих данных (данные однозначны или неоднозначны (недостоверны, неполны) и нуждаются в верификации), а также для регистрации данных, характеризующих тип ожидаемых БДИ и преобразования этих данных из параллельного кода в последовательный.

Блок проверки сценария поиска 11 (фиг. 2) состоит из селектора кода типа БДИ 11.1 и преобразователя кода типа БДИ 11.2, K-разрядный выход которого является K-разрядным корректировочным выходом 113 блока проверки сценария поиска 11, выход передачи TxD преобразователя кода типа БДИ 11.2 является контрольным выходом 114 блока проверки сценария поиска 11, разрешающий выход DSR преобразователя кода типа БДИ 11.2 соединен с инверсным разрешающим входом  селектора кода типа БДИ 11.1, K-разрядный выход которого является K-разрядным прямым выходом 112 блока проверки сценария поиска 11. Запрещающий вход DST преобразователя кода типа БДИ 11.2 подключен к запрещающему выходу МТ селектора кода типа БДИ 11.1, K-разрядный вход которого соединен с K-разрядным входом преобразователя кода типа БДИ 11.2 и является K-разрядным входом 111 блока проверки сценария поиска 11.

селектора кода типа БДИ 11.1, K-разрядный выход которого является K-разрядным прямым выходом 112 блока проверки сценария поиска 11. Запрещающий вход DST преобразователя кода типа БДИ 11.2 подключен к запрещающему выходу МТ селектора кода типа БДИ 11.1, K-разрядный вход которого соединен с K-разрядным входом преобразователя кода типа БДИ 11.2 и является K-разрядным входом 111 блока проверки сценария поиска 11.

Селектор кода типа БДИ 11.1 блока проверки сценария поиска 11 предназначен для осуществления процедуры предварительного анализа (селекции) данных об истинных значениях кода типа БДИ и принятия решения о математической природе этих данных - данные, характеризующие тип ожидаемых БДИ идентифицированы (определены) однозначно или неоднозначно (недостоверно, неполно) и нуждаются в верификации. Селектор кода типа БДИ 11.1 может быть технически реализован в виде серийно выпускаемого селектора на КМДП-структурах с одним инверсным разрешающим входом и одним запрещающим выходом, на базе интегральной микросхемы серии 564 (например, SEL К564КП2), как показано в литературе [Мальцев П.П., Долидзе Н.С. и др. Цифровые интегральные микросхемы: справочник. - М.: Радио и связь, 1994. С. 28-33].

Преобразователь кода типа БДИ 11.2 блока проверки сценария поиска 11 предназначен для регистрации данных, характеризующих тип ожидаемых БДИ и преобразования этих данных из параллельного кода в последовательный. Преобразователь кода типа БДИ 11.2 может быть технически реализован в виде универсального программируемого синхронно-асинхронного приемопередатчика на базе интегральной микросхемы PCI КР580ИК51, описанной в [Гришин Г.Г., Мошков А.А., Ольшанский О.В. и др. Микропроцессоры: Справочное пособие для разработчиков судовой РЭА. 2-е изд. - Л.: Судостроение, 1988. С. 66-74, рис. 3.14].

Блок коррекции сценария поиска 12, изображенный на фиг. 3, предназначен для преобразования идентифицируемых недостоверно (неполно, противоречиво) значений кода типа БДИ, к виду, пригодному для однозначного принятия достоверного решения о типе конкретных ожидаемых БДИ, записи и хранения значений кода, содержащего верифицированные результаты анализа типа ожидаемых БДИ, а также для преобразования этих данных из последовательного кода в параллельный.

Блок коррекции сценария поиска 12 (фиг. 3) состоит из программируемого вычислителя 12.1 и запоминающего элемента 12.2. При этом K-разрядный вход I программируемого вычислителя 12.1 является K-разрядным корректировочным входом 121 блока коррекции сценария поиска 12. Вход OE1 разрешения выходов А программируемого вычислителя 12.1 является контрольным входом 123 блока коррекции сценария поиска 12, К выходов А (А1-AK) программируемого вычислителя 12.1 соединены с соответствующими K входами 12.2-11-12.2-1K запоминающего элемента 12.2, K-разрядный выход которого является K-разрядным прямым выходом 122 блока коррекции сценария поиска 12.

Программируемый вычислитель 12.1 блока коррекции сценария поиска 12 предназначен для осуществления процедуры преобразования идентифицируемых недостоверно (неполно, противоречиво) значений кода, к виду, пригодному для однозначного принятия достоверного решения о типе конкретных ожидаемых БДИ. Программируемый вычислитель 12.1 представляет собой серийно выпускаемую микропроцессорную секцию (МПС или MPS - Micro-Processoring Section) типа MPS К1804ВС1, подробно описанную в [Гришин Г.Г., Мошков А.А., Ольшанский О.В. и др. Микропроцессоры: Справочное пособие для разработчиков судовой РЭА. 2-е изд. - Л.: Судостроение, 1988. С. 243-281, рис. 7.1 и 7.2].

Запоминающий элемент 12.2 блока коррекции сценария поиска 12 предназначен для записи и хранения значений кода, содержащего верифицированные результаты анализа типа ожидаемых БДИ, а также для преобразования этих данных из последовательного кода в параллельный. Запоминающий элемент 12.2 может быть технически реализован на базе серийно выпускаемого программируемого запоминающего устройства с К входами и K-разрядным выходом, в соответствии с описанием, представленным в работе [Гусев В.В., Лебедев О.Н., Сидоров A.M. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С. 198-200, рис. 6.11].

Блоки хранения маски 11-1N, входящие в общую структурную схему, идентичны и предназначены для хранения битовых масок, используемых для идентификации элементов входящего потока данных. Принцип работы и структура блоков хранения маски известны, описаны в прототипе (см. Патент РФ №2553093 «Устройство поиска информации» МПК G06F 9/46, опубликованное 10.06.2015 г., Бюл. №16, фиг. 5), структурная схема проиллюстрирована, на примере n-го ( ) блока хранения маски, на фиг. 4.

) блока хранения маски, на фиг. 4.

Блоки селекции 21-2N, входящие в общую структурную схему, идентичны и предназначены для контроля и идентификации соответствующих элементов входящего потока данных, формирования результата поиска, контроля оставшегося времени поиска, а также выработки управляющих сигналов по истечении установленного изначального или вновь вводимого в динамике управления времени поиска для каждого поискового запроса. Структура блоков селекции (БС) и их алгоритм работы известны, подробно описаны в прототипе (см. Патент РФ №2553093 «Устройство поиска информации» МПК G06F 9/46, опубликованное 10.06.2015 г., Бюл. №16, фиг. 4), структурная схема изображена, на примере n-го ( ) БС, на фиг. 5.

) БС, на фиг. 5.

Делитель частоты 3, входящий в общую структурную схему, предназначен для увеличения периода следования поступающей на его вход последовательности импульсов. Схема реализации делителя частоты известна и описана в прототипе (см. Патент РФ №2553093 «Устройство поиска информации» МПК G06F 9/46, опубликованное 10.06.2015 г., Бюл. №16). В частности, делитель частоты 3 может быть построен на базе счетчика, как описано в [Мальцев П.П., Долидзе Н.С. и др. Цифровые интегральные микросхемы: справочник. - М.: Радио и связь, 1994, с. 62-74]. При этом входом делителя будет счетный вход счетчика, а выходом делителя - один из выходов счетчика.

Формирователь временных интервалов 4, входящий в общую структурную схему, предназначен для контроля интервала времени между элементами входящего потока данных и формирования сигнала по его истечении. Структура и принцип действия формирователя временных интервалов известны, детально описаны в прототипе (см. Патент РФ №2553093 «Устройство поиска информации» МПК G06F 9/46, опубликованное 10.06.2015 г., Бюл. №16, фиг. 6), схема изображена на фиг. 6.

Регистр стратегии поиска 5, входящий в общую структурную схему, предназначен для проверки соответствия порядка следования идентифицированных элементов входящего потока данных заданным правилам и формирования сигнала при поступлении элемента, ожидаемого в соответствии с правилами. Состав элементов и принцип работы регистра стратегии поиска известны, подробно описаны в прототипе (см. Патент РФ №2553093 «Устройство поиска информации» МПК G06F 9/46, опубликованное 10.06.2015 г., Бюл. №16, фиг. 7), структурная схема регистра изображена на фиг. 7.

Блок формирования адреса маски переходов 6, входящий в общую структурную схему, предназначен для формирования и хранения кода, соответствующего маске, определяющей следующий элемент, который должен быть идентифицирован во входящем потоке данных. Принцип работы, состав и взаимосвязь элементов блока формирования адреса маски переходов известны, детально описаны в прототипе (см. Патент РФ №2553093 «Устройство поиска информации» МПК G06F 9/46, опубликованное 10.06.2015 г., Бюл. №16, фиг. 8), структурная схема изображена на фиг. 8.

Блок индикации 7, входящий в общую структурную схему, предназначен для обнаружения признаков, свидетельствующих о завершении заданной правилами последовательности элементов входящего потока данных и формирования соответствующего сигнала. Структура и порядок работы блока индикации известны, описаны в прототипе (см. Патент РФ №2553093 «Устройство поиска информации» МПК G06F 9/46, опубликованное 10.06.2015 г., Бюл. №16, фиг. 9), структурная схема изображена на фиг. 9.

Селекционные контроллеры времени поиска 81-8N, входящие в общую структурную схему, идентичны и предназначены для дешифровки, дополнительного сравнения и контроля нового, вводимого в динамике управления процессом реализации поисковых запросов, S-разрядного кода, обуславливающего новое значение (границы) максимального времени поиска для каждого конкретного поискового запроса. Структура селекционных контроллеров времени поиска (СКВП) и алгоритм их работы известны, подробно описаны в прототипе (см. Патент РФ №2553093 «Устройство поиска информации» МПК G06F 9/46, опубликованное 10.06.2015 г., Бюл. №16, фиг. 2), структурная схема изображена, на примере n-го ( ) СКВП, на фиг. 10.

) СКВП, на фиг. 10.

Главный контроллер времени поиска 9 предназначен для динамической коррекции значений (границ) максимального времени поиска для каждого поискового запроса из любого сочетания N масок переходов (сценариев поиска). Принцип работы, состав, назначение и взаимосвязь элементов главного контроллера времени поиска известны, детально описаны в прототипе (см. Патент РФ №2553093 «Устройство поиска информации» МПК G06F 9/46, опубликованное 10.06.2015 г., Бюл. №16, фиг. 3), структурная схема изображена на фиг. 11.

Генератор тактовых импульсов 10, входящий в общую структурную схему, предназначен для выработки синхронизирующей последовательности импульсов. Техническая реализация генератора тактовых импульсов 10 возможна на базе серийно выпускаемого генератора тактовых импульсов, описанного в работе [Шило В.Л. Популярные цифровые микросхемы. Справочник. - М.: Радио и связь, 1987. С. 50-53].

Устройство поиска информации работает следующим образом.

Известно [1-6], что с точки зрения верификации кода типа БДИ, существует возможность распознавания (определения) данных, характеризующих этот код, заданных как количественно, так и качественно (недостоверно, неполно, противоречиво). Эта возможность реализуется с использованием нейросетевых вычислительных методов и алгоритмов, позволяющих путем последовательных нейросетевых преобразований, осуществить переход от недостоверно (недостаточно, неполно) распознанных (определенных) данных, характеризующих код типа БДИ к виду данных, пригодному для однозначного принятия достоверного решения о значениях элементов этого кода, в рамках конкретного сценария поиска.

При этом код, характеризующий тип (типы) ожидаемых БДИ - конкретный сценарий поиска и определяющий соответствующие маски переходов, может быть верифицирован на основе математических методов принятия решений в слабоструктурированных задачах - нейросетевых вычислительных методов и алгоритмов, которые достаточно просто могут быть аппаратно реализуемы.

Нейросетевые вычислительные методы и алгоритмы работают на основе экспертных оценок, а для решения задачи объединения мнений экспертов, знания которых используются, например, для верификации кода типа БДИ, используется один из типовых вычислительных алгоритмов теории нейронных сетей - нейросетевой экстраполирующий вычислительный алгоритм, или, так называемая, экстраполирующая нейронная сеть (ЭНС), являющаяся разновидностью известных вычислительных моделей ассоциативной памяти [1-6].

Вычислительный нейросетевой алгоритм (экстраполирующая нейронная сеть) такого класса состоит из двух слоев вычислителей (нейронов) - входного слоя Ua и выходного слоя Ub. Входной слой Ua состоит из Квх нейронов, обладающих набором прямых и обратных связей с Квых нейронами выходного слоя Ub, причем количество входных и выходных образов К соответствует разрядности кода адреса маски переходов (определяющей тип ожидаемых, согласно сценария поиска, БДИ) и равно (K=Kвх=Kвых=(log2 N)+1) и зависит от количества двоичных разрядов, достаточных для адресации N масок переходов и маски начала сценария поиска, от количества экспертов и соответствующего количества входов устройств аппаратной реализации нейросетевого алгоритма. В нашем случае К может принимать значения от 2 (двух) до 20 (двадцати), соответствующие количеству входов микропроцессорной секции MPS К1804 ВС1, на базе которой построен программируемый вычислитель 12.1 блока коррекции сценария поиска 12.

В ЭНС используется так называемая когнитивная карта, полностью задаваемая матрицей связей и характеризующая причинно-следственные отношения текущих кодов типа БДИ, влияющих на получения однозначных (достоверных) результатов конкретного поиска. Когнитивная карта формулируется экспертами, принцип формирования когнитивных карт подробно описан в работах [2, 4]. При этом K ветвей алгоритма отвечают за преобразование мнений экспертов о недостоверно (неполно) распознанном (определенном) коде типа БДИ к виду, пригодному для однозначного распознавания этих кода.

На вход вычислительного нейросетевого алгоритма (ЭНС) поступает входной образ - данные, характеризующие значения кода типа БДИ и распознанные (определенные) как количественно, так и качественно (недостоверно, неполно, противоречиво). Определяется, какие из данных, характеризующих код типа БДИ в данный момент времени распознаны количественно, а какие данные идентифицированы неопределенно (недостоверно, неточно). В целях верификации значений кода типа БДИ, необходимо математически корректно, используя ЭНС, преобразовать распознанные недостоверно (неполно) данные.

Этапы функционирования вычислительного нейросетевого алгоритма (ЭНС) подробно, алгоритмически и аналитически описаны в [2].

На выходе вычислительного нейросетевого алгоритма (ЭНС) имеем выходной образ - данные, которые полностью (достоверно) характеризуют интегрированное мнение экспертов о принадлежности значений кода типа БДИ к пространству достоверных, верифицированных значений кода.

Рассмотренный в [1, 3, 5] и детально описанный в [2] вычислительный нейросетевой алгоритм позволяет устранить неопределенность (недостоверность, неполноту) данных, характеризующих тип ожидаемых БДИ, позволяет однозначно распознать (верифицировать) истинный код, определяемый конкретным сценарием поиска и соответствующими масками переходов в текущий момент времени, а в конечном итоге, повысить достоверность определения типа ожидаемых блоков двоичной информации, и, как следствие, повысить достоверность выполнения поисковых запросов в условиях, присущих реальной динамике процесса поиска и оперативной идентификации информации в сетях передачи данных с коммутацией пакетов и в информационно-справочных (поисковых) системах - в условиях недостаточности (неполноты и противоречивости) данных об истинных значениях параметров сценария поиска.

С учетом этого, осуществляется достоверное распознавание значений кода типа БДИ и, в соответствии с верифицированными значениями кода, реализация сценария поиска (реализация поисковых запросов абонентов) в заявленном устройстве.

Техническая реализация принципа повышения достоверности распознавания значений кода типа БДИ в заявленном устройстве осуществлена путем введения предварительного анализа (выявления) неоднозначно (недостоверно, неполно) идентифицируемых значений кода типа БДИ, а также верификации этих значений с использованием нейроматематических методов к виду, позволяющему однозначно (достоверно, полно, непротиворечиво) идентифицировать и трактовать значения этого кода, характеризующего тип конкретных ожидаемых БДИ (в заявленном устройстве реализованы соответственно в рамках блока проверки сценария поиска 11 и блока коррекции сценария поиска 12).

При этом, как и в прототипе, в заявленном устройстве реализован синтаксический подход к распознаванию образов [7], основанный на идентификации отдельных элементов входящего потока данных - БДИ, путем параллельного анализа значений признаков идентификации и контроля порядка их следования на предмет соответствия заданным правилам. В качестве признаков идентификации, используются значения битов в соответствующих позициях БДИ. Правила следования БДИ задаются формальной грамматикой - сценарием поиска. Для пояснения параллельного анализа значений признаков идентификации и контроля порядка их следования необходимо рассмотреть правила задания сценария поиска. Сценарий поиска SC может быть представлен следующей схемой:

,

,

где:

Р={Pn},  - множество типов БДИ, входящих в состав сценария;

- множество типов БДИ, входящих в состав сценария;

MP={MPn},  - множество масок переходов;

- множество масок переходов;

MB - маска начала сценария поиска;

MF - маска окончания сценария поиска;

Т - время ожидания очередного БДИ.

Идентификация типа БДИ в устройстве осуществляется путем сравнения значений идентификационных битов БДИ с их эталонными значениями. Под идентификационными битами понимаются биты БДИ, значения которых позволяют идентифицировать тип БДИ. Для каждого типа БДИ множество идентификационных битов может быть индивидуальным. В связи с этим каждому типу БДИ ставится в соответствие две битовые маски:

где:

M1n - первая битовая маска БДИ n-го типа;

M2n - вторая битовая маска БДИ n-го тип.

Битовые маски содержат L разрядов, где L - максимально возможное количество разрядов в БДИ, используемых в сценарии поиска. Первая битовая маска предназначена для указания позиций идентификационных битов БДИ. Значения логической единицы в разрядах первой битовой маски соответствуют позициям идентификационных битов. Во всех остальных разрядах битовой маски устанавливаются значения логического нуля. Вторая битовая маска предназначена для задания эталонных значений, которым должны соответствовать значения идентификационных битов. При этом разряды второй битовой маски, не являющиеся идентификационными, могут иметь произвольные значения, так как не влияют на процесс идентификации БДИ.

Множество масок переходов используется для задания порядка следования БДИ в рамках сценария. Множество содержит N масок переходов, каждая из которых содержит N двоичных разрядов. Таким образом каждому типу БДИ соответствует своя маска переходов. При этом, n-ая маска переходов MPn содержит информацию о типах БДИ, которые согласно сценария поиска ожидаются после наблюдения БДИ n-го типа. Указанная информация задается путем установки значения логического нуля в разрядах маски переходов, порядковые номера которых соответствуют типам ожидаемых БДИ. Во всех остальных разрядах маски переходов устанавливаются значения логической единицы.

Маска начала сценария поиска предназначена для указания типов БДИ, которые ожидаются первыми в сценарии поиска - начальных БДИ. Маска MB содержит N двоичных разрядов. В разрядах маски начала сценария поиска, номера которых соответствуют начальным типам БДИ, устанавливаются значения логического нуля. Во всех остальных разрядах маски начала сценария поиска устанавливаются значения логической единицы.

Маска окончания сценария поиска предназначена для указания типов БДИ, наблюдение которых свидетельствует о завершении сценария поиска - конечных БДИ. Маска MF содержит N двоичных разрядов. В разрядах маски окончания сценария поиска, номера которых соответствуют конечным типам БДИ, устанавливаются значения логического нуля. Во всех остальных разрядах маски окончания сценария поиска устанавливаются значения логической единицы.

В отличие от времени поиска, время ожидания очередного БДИ Т задает максимально допустимый интервал времени в течение которого ожидается очередной БДИ, заданного сценарием поиска типа. В том случае, если в течение заданного интервала времени ожидаемый тип БДИ не будет обнаружен, сценарий поиска прерывается, и осуществляется переход к ожиданию начальных БДИ. Время ожидания очередного БДИ задается в виде М-разрядного кода. При этом наименьшему времени ожидания соответствует наибольший код, являющийся дополнением до максимального числа, представимого в М-разрядном коде.

С учетом этого, в заявленном устройстве осуществляется управляемое обслуживание поисковых запросов и реализация потребностей абонентов в достоверной идентификации элементов входящего потока данных.

В целом, работу устройства поиска информации можно рассматривать как процесс перехода данного устройства из состояния в состояние. Множество состояний W={Wn},  , устройства соответствует множеству типов БДИ, входящих в состав сценария. При обнаружении очередного, заданного сценарием типа БДИ, устройство переходит в состояние, номер которого соответствует типу обнаруженного БДИ. Находясь в одном из состояний устройство ожидает появления БДИ, типы которых определяются маской переходов, номер которой соответствует номеру текущего состояния устройства.

, устройства соответствует множеству типов БДИ, входящих в состав сценария. При обнаружении очередного, заданного сценарием типа БДИ, устройство переходит в состояние, номер которого соответствует типу обнаруженного БДИ. Находясь в одном из состояний устройство ожидает появления БДИ, типы которых определяются маской переходов, номер которой соответствует номеру текущего состояния устройства.

На фиг. 12 приведен пример сценария поиска, включающий N=8 типов БДИ. Соответствующее приведенному сценарию поиска заполнение масок переходов, маски начала сценария и маски окончания сценария приведено на фиг. 13.

Инициализация устройства включает в себя проведение следующих операций:

начальный сброс устройства;

установка первой и второй битовых масок;

установка маски начала сценария и масок переходов;

установка маски окончания сценария поиска;

установка времени ожидания очередного БДИ;

установка начального максимального времени поиска.

Начальный сброс устройства осуществляется следующим образом. На разрешающем входе 014 устройства устанавливают значение логической единицы, которая поступает на соответствующий вход 58 регистра стратегии поиска 5. Логическая единица на разрешающем входе 58 регистра стратегии поиска 5, поступая на третьи входы 5.31-3-5.3N-3 всех трехвходовых элементов ИЛИ-НЕ 5.31-5.3N (см. фиг. 7), обеспечивает наличие логического нуля на их выходах 5.31-4- 5.3N-4 вне зависимости от логических значений, установленных на первых 5.31-1-5.3N-1 и вторых 5.31-2-5.3N-2 входах. В связи с этим на сигнальном выходе 59 регистра стратегии поиска 5 будет установлено значение логического нуля. Логический ноль с сигнального выхода 59 регистра стратегии поиска 5 поступает на соответствующий вход 45 формирователя временных интервалов 4 и далее -на первый информационный вход 4.2-1 (вход J) JK-триггера 4.2. На входе «Начальный сброс" 05 устройства устанавливают значение логической единицы, которая поступает на входы 42 и 63 формирователя временных интервалов 4 и блока формирования адреса маски переходов 6 соответственно. Значение логической единицы с входа «Начальный сброс» 42 формирователя временных интервалов 4 (см. фиг. 6) через первый двухвходовый элемент ИЛИ 4.1 поступает на второй информационный вход 4.2-2 (вход К) JK-триггера 4.2, а через второй двухвходовый элемент ИЛИ 4.6 - на вход сброса (вход R) счетчика 4.7. Логическая единица на входе 4.2-2 (входе К) JK-триггера 4.2 при наличии логического нуля на его входе 4.2-1 (входе J) приводит к установке логического нуля на выходе 4.2-3 JK-триггера 4.2, который, поступая на второй вход 4.3-2 двухвходового элемента И 4.3, приводит к установке значения логического нуля на его выходе 4.3-3 вне зависимости от логических значений на его первом входе 4.3-1. Логическая единица на входе сброса R счетчика 4.7 обеспечивает установку логического нуля на его выходе переполнения Р. Значение логического нуля с выхода переполнения Р счетчика 4.7 поступает на второй вход 4.5-2 второго двухвходового элемента И 4.5, что приводит к безусловной установке на его выходе 4.5-3, а соответственно и на выходе «Сброс» 44 формирователя временных интервалов 4, значения логического нуля. Логическая единица с входа «Начальный сброс» 63 блока формирования адреса маски переходов 6 (см. фиг. 8) через двухвходовый элемент ИЛИ 6.3 поступает на вход сброса 6.4-3 (входа R) регистра 6.4, что приводит к установке логического нуля на его выходах 6.4-4 (Q1-QK), а соответственно и на всех разрядах K-разрядного выхода «Код события» 62 блока формирования адреса маски переходов 6, на всех разрядах K-разрядных прямого 112 и корректировочного 113 выходов блока проверки сценария поиска 11 и на всех разрядах K-разрядного прямого выхода 122 блока коррекции сценария поиска 12. По завершении операции начального сброса на входе «Начальный сброс» 05 устройства устанавливают значение логического нуля, что приводит к установке значения логического нуля на втором информационном входе 4.2-2 (входе К) JK-триггера 4.2 и на входе сброса R счетчика 4.7 формирователя временных интервалов 4.

Установка первой и второй битовых масок, обеспечивающих идентификацию каждого из N типов БДИ, осуществляется в соответствующие блоки хранения маски 11-1N. Для этого на первых L-разрядных входах «Маска 1» 021-02N устройства и на соответствующих первых L-разрядных входах «Маска 1» 121-12N каждого из N блоков хранения маски 11-1N устанавливают соответствующие первые битовые маски, а на первых L-разрядных входах «Маска 2» 031-03N устройства и на соответствующих первых L-разрядных входах «Маска 2» 131-13N каждого из N блоков хранения маски 11-1N устанавливают соответствующие вторые битовые маски. На входе разрешения записи 01 устройства и на соответствующих входах разрешения записи 101-10N каждого из N блоков хранения маски 11-1N устанавливают значение логической единицы, которая поступает на входы инициализации (входы С) первых и вторых регистров 1.1 и 1.2 каждого из N блоков хранения маски (см. фиг. 4) и обеспечивает запись первых и вторых битовых масок в соответствующие регистры. По окончании операции записи на входе разрешения записи 01 устройства и на соответствующих входах разрешения записи 101-10N каждого из N блоков хранения маски 11-1N устанавливают значение логического нуля.

Установка маски начала сценария поиска и масок переходов осуществляется в оперативное запоминающее устройство 5.2 регистра стратегии поиска 5. При этом маска начала сценария поиска MB должна быть записана в оперативное запоминающее устройство по нулевому адресу, а n-ая маска перехода MPn,  , должна быть записана по адресу, соответствующему ее порядковому номеру, то есть адресу, значение которого равно n. Для этого на управляющем входе 010 устройства и, соответственно, на управляющем входе 54 регистра стратегии поиска 5 устанавливают значение логической единицы, которая, поступая на управляющий вход 5.1-3 (вход SE) селектора-мультиплексора 5.1 (см. фиг. 7), обеспечивает коммутацию второй группы информационных входов 5.1-2 (В1-BK) селектора-мультиплексора 5.1 на его выходы 5.1-4 (Q1-QK), где К=(log2 N)+1 - количество двоичных разрядов, достаточное для адресации N масок переходов и маски начала сценария поиска. На K-разрядном адресном входе 09 устройства и, соответственно, на K-разрядном адресном входе 53 регистра стратегии поиска 5 устанавливают K-разрядный адрес, по которому в оперативное запоминающее устройство 5.2 должна быть записана маска начала сценария поиска. С выходов 5.1-4 (Q1-QK) селектора-мультиплексора 5.1 К-разрядный адрес поступает на адресные входы 5.2-2 (A1-AK) оперативного запоминающего устройства 5.2. На N-разрядном информационном входе 011 устройства и, соответственно на N-разрядном информационном входе 55 регистра стратегии поиска 5 устанавливают маску начала сценария поиска, которая поступает на информационные входы 5.2-3 (D1-DN) оперативного запоминающего устройства 5.2. Запись осуществляется путем установки логического нуля на входах «Выбор кристалла» 012 и «Чтение/запись» 013 устройства, с которых логический ноль через входы «Выбор кристалла» 56 и «Чтение/запись» 57 регистра стратегии поиска 5 поступает на соответствующие входы 5.2-1 (

, должна быть записана по адресу, соответствующему ее порядковому номеру, то есть адресу, значение которого равно n. Для этого на управляющем входе 010 устройства и, соответственно, на управляющем входе 54 регистра стратегии поиска 5 устанавливают значение логической единицы, которая, поступая на управляющий вход 5.1-3 (вход SE) селектора-мультиплексора 5.1 (см. фиг. 7), обеспечивает коммутацию второй группы информационных входов 5.1-2 (В1-BK) селектора-мультиплексора 5.1 на его выходы 5.1-4 (Q1-QK), где К=(log2 N)+1 - количество двоичных разрядов, достаточное для адресации N масок переходов и маски начала сценария поиска. На K-разрядном адресном входе 09 устройства и, соответственно, на K-разрядном адресном входе 53 регистра стратегии поиска 5 устанавливают K-разрядный адрес, по которому в оперативное запоминающее устройство 5.2 должна быть записана маска начала сценария поиска. С выходов 5.1-4 (Q1-QK) селектора-мультиплексора 5.1 К-разрядный адрес поступает на адресные входы 5.2-2 (A1-AK) оперативного запоминающего устройства 5.2. На N-разрядном информационном входе 011 устройства и, соответственно на N-разрядном информационном входе 55 регистра стратегии поиска 5 устанавливают маску начала сценария поиска, которая поступает на информационные входы 5.2-3 (D1-DN) оперативного запоминающего устройства 5.2. Запись осуществляется путем установки логического нуля на входах «Выбор кристалла» 012 и «Чтение/запись» 013 устройства, с которых логический ноль через входы «Выбор кристалла» 56 и «Чтение/запись» 57 регистра стратегии поиска 5 поступает на соответствующие входы 5.2-1 ( ) и 5.2-4 (

) и 5.2-4 ( ) оперативного запоминающего устройства 5.2. По окончании записи маски на входе «Выбор кристалла» 012 устанавливают значение логической единицы. Затем на K-разрядном адресном входе 09 устройства устанавливают K-разрядный адрес, по которому в оперативное запоминающее устройство 5.2 должна быть записана первая маска переходов МР1 (значение адреса равно 1), а на N-разрядном информационном входе 011 устройства устанавливают маску переходов МР1, после чего путем установки значения логического нуля на входе «Выбор кристалла» 012 инициируют операцию записи в оперативное запоминающее устройство 5.2. Аналогичным образом в оперативное запоминающее устройство записывают все N масок переходов. По окончании записи масок переходов в оперативное запоминающее устройство 5.2 на входе «Чтение/запись» 013 устанавливают значение логической единицы, а на управляющем входе 010 устройства устанавливают значение логического нуля, что обеспечивает коммутацию первой группы информационных входов 5.1-1 (A1-AK) селектора-мультиплексора 5.1 на его выходы 5.1-4 (Q1-QK).

) оперативного запоминающего устройства 5.2. По окончании записи маски на входе «Выбор кристалла» 012 устанавливают значение логической единицы. Затем на K-разрядном адресном входе 09 устройства устанавливают K-разрядный адрес, по которому в оперативное запоминающее устройство 5.2 должна быть записана первая маска переходов МР1 (значение адреса равно 1), а на N-разрядном информационном входе 011 устройства устанавливают маску переходов МР1, после чего путем установки значения логического нуля на входе «Выбор кристалла» 012 инициируют операцию записи в оперативное запоминающее устройство 5.2. Аналогичным образом в оперативное запоминающее устройство записывают все N масок переходов. По окончании записи масок переходов в оперативное запоминающее устройство 5.2 на входе «Чтение/запись» 013 устанавливают значение логической единицы, а на управляющем входе 010 устройства устанавливают значение логического нуля, что обеспечивает коммутацию первой группы информационных входов 5.1-1 (A1-AK) селектора-мультиплексора 5.1 на его выходы 5.1-4 (Q1-QK).

Установка маски окончания сценария поиска MF заключается в установке на разрядах N-разрядного входа «Правило завершения поиска» 07 устройства и, следовательно, на разрядах N-разрядного входа «Правило завершения поиска» 72 блока индикации 7 (см. фиг. 9) соответствующих логических значений, соответствующих значениям битов маски окончания сценария поиска.

Установка времени ожидания очередного БДИ заключается в установке на разрядах М-разрядного входа «Код времени ожидания» 06 устройства и, следовательно, на разрядах М-разрядного входа «Код времени ожидания» 43 формирователя временных интервалов 4 (см. фиг. 6), логических значений, соответствующих значениям разрядов кода времени ожидания.

Установка начального максимального времени поиска заключается в установке на разрядах каждого из N S-разрядных входов «Коррекция максимального времени поиска» 0161-016N устройства (см. фиг. 11) через S-разрядные входы 211-27N блоков селекции 21-2N на S-разрядные входы 2.71-1-2.7N-1 корректирующих регистров 2.71-2.7N логических значений кода, задающего начальное максимальное время поиска для каждого n-го ( ) поискового запроса - набора конкретных типов БДИ (определяющего соответствующие маски переходов и характеризующего конкретный сценарий поиска).

) поискового запроса - набора конкретных типов БДИ (определяющего соответствующие маски переходов и характеризующего конкретный сценарий поиска).

После выполнения указанных операций устройство готово к работе.

В начальный период, когда подлежащие анализу БДИ не поступают на вход устройства, на вход 38 делителя частоты 3 через первый тактовый вход 08 устройства от внешнего генератора поступают тактовые импульсы. С выхода 39 делителя частоты 3 тактовые импульсы поступают на второй тактовый вход 41 формирователя временных интервалов 4. В результате проведенной операции начального сброса устройства на всех информационных выходах 6.4-4 (Q1-QK) регистра 6.4, а соответственно и на всех разрядах K-разрядного выхода «Код события» 62 блока формирования маски переходов 6 и, соответственно, на всех разрядах K-разрядных прямого 112 и корректировочного 113 выходов блока проверки сценария поиска 11 и на всех разрядах K-разрядного прямого выхода 122 блока коррекции сценария поиска 12, установлено значение логического нуля. На управляющем входе 54 регистра стратегии поиска 5 установлено значение логического нуля, что обеспечивает коммутацию значений логического нуля с разрядов K-разрядного входа «Код события» 52 регистра стратегии поиска 5 на соответствующие адресные входы 5.2-2 (A1-AK) оперативного запоминающего устройства 5.2. Таким образом, на адресном входе оперативного запоминающего устройства установлен нулевой адрес, указывающий на маску начала сценария поиска.

Значения логического нуля с разрядов K-разрядного выхода «Код события» 62 блока формирования адреса маски переходов 6 поступают на соответствующие разряды K-разрядного входа 111 блока проверки сценария поиска 11. При этом код, содержащий во всех разрядах значения логического нуля, поступает на K-разрядный вход селектора кода типа БДИ 11.1 и на K-разрядный вход (D1-DK) преобразователя кода типа БДИ 11.2 (см. фиг. 2), что обеспечивает транзитное преобразование (перезапись) значений кода в селекторе кода типа БДИ 11.1 ив преобразователе кода типа БДИ 11.2 и установку значений логического нуля на всех разрядах K-разрядного выхода селектора кода типа БДИ 11.1 и на соответствующих разрядах K-разрядного прямого выхода 112 блока проверки сценария поиска 11, а также на всех разрядах K-разрядного выхода Y (Y1-YK) преобразователя кода типа БДИ 11.2 и на соответствующих разрядах K-разрядного корректировочного выхода 113 блока проверки сценария поиска 11.

Поступление значений логического нуля с разрядов K-разрядного корректировочного выхода 113 блока проверки сценария поиска 11 на K-разрядный корректировочный входа 121 блока коррекции сценария поиска 12 и на соответствующие разряды K-разрядного входа I (I1-IK) программируемого вычислителя 12.1 происходят по соответствующей разрешительной (отпирающей) команде, поступающей с выхода передачи TxD преобразователя кода типа БДИ 11.2 через контрольный выход 114 блока проверки сценария поиска 11 на контрольный вход 123 блока коррекции сценария поиска 12 и на вход разрешения выходов А (ОЕ1) программируемого вычислителя 12.1 (см. фиг. 3), что обеспечивает установление значений логического нуля на всех К (A1-AK) выходах 12.1-11-12.1-1K программируемого вычислителя 12.1 и, как следствие, после записи в ячейки памяти, установление значений логического нуля на всех разрядах K-разрядного выхода запоминающего элемента 12.2 и на соответствующих разрядах K-разрядного прямого выхода 122 блока коррекции сценария поиска 12.

Значения логического нуля с разрядов K-разрядных прямых выходов 112 и 122 блока проверки сценария поиска 11 и блока коррекции сценария поиска 12 соответственно, поступают на соответствующие разряды входа «Код события» 71 блока индикации 7 и далее - на входы 7.1-11-7.1-1K (F1-FK) дешифратора 7.1 (см. фиг. 9). При наличии значения логического нуля на всех входах 7.1-11-7.1-1K (F1-FK) дешифратора 7.1, на всех его инверсных выходах 7.1-21-7.1-2N ( ) будет установлено значение логической единицы. Значения логической единицы с инверсных выходов 7.1-21-7.1-2N (

) будет установлено значение логической единицы. Значения логической единицы с инверсных выходов 7.1-21-7.1-2N ( ) дешифратора 7.1 поступает на первые входы 7.21-1-7.2N-1 соответствующих двухвходовых элементов ИЛИ 7.21-7.2N. В результате на выходах 7.21-3-7.2N-3 всех двухвходовых элементов ИЛИ 7.21-7.2N устанавливается значение логической единицы вне зависимости от логических значений на их вторых входах. Это приводит к установке значения логической единицы на выходе 7.3-2 N-входового элемента И 7.3, а соответственно и на выходе «Результат поиска» 015 устройства. Логические значения на выходе «Результат поиска» 015 устройства имеют следующее значение: логический ноль на указанном выходе означает, что во входящем потоке БДИ обнаружен заданный сценарий поиска, а логическая единица - отсутствие заданного сценария поиска. На входе «Чтение/запись» 57 регистра стратегии поиска 5 установлено значение логической единицы, что обеспечивает перевод оперативного запоминающего устройства 5.2 в режим чтения информации. При этом на входе «Выбор кристалла» 56 регистра стратегии поиска 5 также установлено значение логической единицы. На разрешающем входе 014 устройства и, соответственно на разрешающем входе 58 регистра стратегии поиска 5 установлено значение логической единицы, что обеспечивает установку на сигнальном выходе 59 регистра стратегии поиска 5 значения логического нуля. При этом на выходе 4.2-3 JK-триггера 4.2 формирователя временных интервалов 4 (см. фиг. 6), на его первом 4.2-1 (вход J) и втором 4.2-2 (вход К) информационных входах установлено значение логического нуля.

) дешифратора 7.1 поступает на первые входы 7.21-1-7.2N-1 соответствующих двухвходовых элементов ИЛИ 7.21-7.2N. В результате на выходах 7.21-3-7.2N-3 всех двухвходовых элементов ИЛИ 7.21-7.2N устанавливается значение логической единицы вне зависимости от логических значений на их вторых входах. Это приводит к установке значения логической единицы на выходе 7.3-2 N-входового элемента И 7.3, а соответственно и на выходе «Результат поиска» 015 устройства. Логические значения на выходе «Результат поиска» 015 устройства имеют следующее значение: логический ноль на указанном выходе означает, что во входящем потоке БДИ обнаружен заданный сценарий поиска, а логическая единица - отсутствие заданного сценария поиска. На входе «Чтение/запись» 57 регистра стратегии поиска 5 установлено значение логической единицы, что обеспечивает перевод оперативного запоминающего устройства 5.2 в режим чтения информации. При этом на входе «Выбор кристалла» 56 регистра стратегии поиска 5 также установлено значение логической единицы. На разрешающем входе 014 устройства и, соответственно на разрешающем входе 58 регистра стратегии поиска 5 установлено значение логической единицы, что обеспечивает установку на сигнальном выходе 59 регистра стратегии поиска 5 значения логического нуля. При этом на выходе 4.2-3 JK-триггера 4.2 формирователя временных интервалов 4 (см. фиг. 6), на его первом 4.2-1 (вход J) и втором 4.2-2 (вход К) информационных входах установлено значение логического нуля.

При поступлении БДИ, подлежащего анализу, на L-разрядном информационном входе 04 устройства устанавливают логические значения, соответствующие значениям двоичных разрядов БДИ. Момент времени, соответствующий установке БДИ на L-разрядном информационном входе 04 устройства, обозначим как Т1. С L-разрядного информационного входа 04 устройства БДИ поступает на L-разрядные информационные входы 211-21N блоков селекции 21-2N. Каждый блок селекции осуществляет идентификацию БДИ соответствующего типа. Тип БДИ определяется первой и второй битовыми масками, поступающими соответственно на вторые L-разрядные входы «Маска 1» 221-22N и вторые L-разрядные входы «Маска 2» 231-23N блоков селекции 21-2N. В компараторах 2.3 каждого блока селекции 21-2N (см. фиг. 4) происходит сравнение значений идентификационных битов поступившего БДИ со значениями соответствующих битов второй битовой маски. Выделение идентификационных битов осуществляется в первой и второй группах двухвходовых элементов И 2.11-2.1L, 2.21-2.2L каждого блока селекции на основании соответствующей первой битовой маски. В случае равенства сравниваемых значений на выходе равенства «А=В» 2.3-3 компаратора 2.3 установится значение логической единицы, в противном случае - значение логического нуля. Логическое значение, соответствующее результату сравнения, с выхода «А=В» 2.3-3 компаратора 2.3 в случае, когда задано только начальное максимальное время поиска и внешнее динамическое управление временем поиска отсутствует (нет сигналов на разрядах каждого из N S-разрядных входов «Коррекция максимального времени поиска» 0161-016N устройства), инвертируется инвертором 2.4 и поступает на выход «Результат сравнения» 26 блока селекции 2.

Иными словами, если в ходе анализа поступающих БДИ отсутствует внешнее динамическое управление временем поиска для всех N поисковых запросов, на S-разрядных корректирующих входах 271-27Nблоков селекции 21-2N, а значит и на S-разрядных входах 2.71-1-2.7N-1 корректирующих регистров 2.71-2.7N, кодовые сигналы отсутствуют. В этом случае корректирующие регистры 2.11-2.1N блоков селекции 21-2N (см. фиг. 4) идентифицируют начальные коды времени поиска как некорректируемые и транслируют (перезаписывают) их каждый через свои S выходов (2.71-21-2.71-2S)-(2.7N-21-2.7N-2S) на соответствующие S информационных входов (D1-DS) соответствующих счетчиков 2.51-2.5N блоков селекции 21-2N.

Если в ходе идентификации элементов входящего потока данных инициировано внешнее динамическое управление временем поиска для любого n-го ( ) поискового запроса - набора конкретных типов БДИ, с внешнего устройства в S-разрядном коде (либо с помощью человека-оператора, либо с помощью специального управляющего устройства), через N S-разрядных входов «Коррекция максимального времени поиска» 0161-016N устройства на N S-разрядных входов 911-91N главного контроллера времени поиска 9 (см. фиг. 3) поступают новые, дополнительно вводимые в динамике управления поиском, значения максимального времени поиска для конкретных поисковых запросов абонентов информационно-справочной (поисковой) системы.

) поискового запроса - набора конкретных типов БДИ, с внешнего устройства в S-разрядном коде (либо с помощью человека-оператора, либо с помощью специального управляющего устройства), через N S-разрядных входов «Коррекция максимального времени поиска» 0161-016N устройства на N S-разрядных входов 911-91N главного контроллера времени поиска 9 (см. фиг. 3) поступают новые, дополнительно вводимые в динамике управления поиском, значения максимального времени поиска для конкретных поисковых запросов абонентов информационно-справочной (поисковой) системы.

Дополнительно вводимые в динамике управления поиском, значения максимального времени поиска для конкретных поисковых запросов абонентов, в S-разрядном коде поступает через N S-разрядных входов 911-91N главного контроллера времени поиска 9 (см. фиг. 11) на N S-разрядных входов 9.1-11-9.1-1N регистрирующего элемента времени поиска 9.1 для контроля и регистрации. С N S-разрядных выходов 9.1-21-9.1-2N регистрирующего элемента времени поиска 9.1 новые значения максимального времени поиска поступают на соответствующие N S-разрядных входов 9.2-11-9.2-1N элемента хранения нового значения времени поиска 9.2, который записывает и хранит в S-разрядном коде эти значения до момента введения очередного управляющего воздействия, а также со своих N S-разрядных выходов 9.2-21-9.2-2N, через соответствующие N S-разрядных выходов 921-92N главного контроллера времени поиска 9, передает эти новые значения максимального времени поиска на корректирующие входы 211-21N соответствующих блоков селекции 21-2N и на проверочные входы 821-82N соответствующих селекционных контроллеров времени поиска 81-8N.

При этом на S-разрядных корректирующих входах 271-21N блоков селекции 21-2N, а значит и на S-разрядных входах 2.71-1-2.7N-1 корректирующих регистров 2.11-2.1N, присутствуют S-разрядные кодовые сигналы. Корректирующие регистры 2.71-2.7N блоков селекции 21-2N (см. фиг. 5) регистрируют изначальный код (записанный при подготовке устройства к работе, т.е. начальное максимальное время поиска) и предварительно сравнивают его с вновь вводимым в динамике управления S-разрядным кодом, который поступает через корректирующие входы 271-27N блоков селекции 21-2N на S-разрядные входы 2.71-1-2.7N-1 корректирующих регистров 2.71-2.7N.

Коррекция (формирование по итогам предварительного сравнения) на S выходах 2.7n-21-2.7n-2S например, корректирующего регистра 2.7n блока селекции 2n кода, характеризующего предварительное решение о значении максимального времени поиска для каждого конкретного n-ого запроса осуществляется следующим образом (см. фиг. 5). Если на S-разрядном входе 2.7n-1 корректирующего регистра 2.7n есть S-разрядный сигнал, обуславливающий новое, вводимое в динамике управления максимальное время поиска, этот сигнал идентифицируется как приоритетный, и именно он с S выходов 2.7n-21-2.7n-2S корректирующего регистра 2.7n поступает на соответствующие S информационных входов (D1-DS) счетчика 2.5n n-го ( ) блока селекции 2n. Если на S-разрядном входе 2.7n-1 корректирующего регистра 2.7n нет S-разрядного сигнала, обуславливающего новое, вводимое в динамике управления максимальное время поиска, то приоритетными признаются ранее записанные значения кода, задающего начальное максимальное время поиска.

) блока селекции 2n. Если на S-разрядном входе 2.7n-1 корректирующего регистра 2.7n нет S-разрядного сигнала, обуславливающего новое, вводимое в динамике управления максимальное время поиска, то приоритетными признаются ранее записанные значения кода, задающего начальное максимальное время поиска.

Таким образом, с S выходов 2.7n-21-2.7n-2S корректирующего регистра 2.7n поступает на соответствующие S информационных входов (D1-DS) счетчика 2.5n n-го ( ) блока селекции 2n либо изначально введенное, либо новое, вводимое в динамике управления процессом идентификации элементов входящего потока данных, значение кода, задающие максимальное время поиска. Тем самым обеспечивается инициализация счетчиков 2.51-2.5N блоков селекции 21-2N. Причем наименьшему времени поиска соответствует наибольший код, являющийся дополнением до максимального числа, представимого в S-разрядном коде.

) блока селекции 2n либо изначально введенное, либо новое, вводимое в динамике управления процессом идентификации элементов входящего потока данных, значение кода, задающие максимальное время поиска. Тем самым обеспечивается инициализация счетчиков 2.51-2.5N блоков селекции 21-2N. Причем наименьшему времени поиска соответствует наибольший код, являющийся дополнением до максимального числа, представимого в S-разрядном коде.

В начальный период, когда подлежащие анализу БДИ не поступают на вход устройства, логическое значение, соответствующее результатам сравнения, на выходе «А=В» 2.3n-3 компаратора 2.3n отсутствует. Трехвходовые элементы И 2.61-2.6N всех блоков селекции закрыты, тактовые импульсы от генератора тактовых импульсов 10 через трехвходовые элементы И 2.61-2.6N на счетные входы Z счетчиков 2.51-2.5N блоков селекции 21-2N не поступают. На выходах «Результат сравнения» 261-26N блоков селекции 21-2N сигнал отсутствует.

Если логические значения, соответствующие результатам сравнения, с выходов «А=В» 2.31-3-2.3N-3 компараторов 2.31-2.3N блоков селекции 21-2N поступают, на выходах 261-26N этих блоков через инверторы 2.41-2.4N предварительно установятся сигналы низкого уровня. На счетные входы Z счетчиков 2.51-2.5N блоков селекции 21-2N, поступают импульсы с выхода 101 генератора тактовых импульсов 10 по цепи: тактовые входы 251-25N блоков селекции 21-2N, открытые трехвходовые элементы И 2.61-2.6N блоков селекции 21-2N. Счетчики 2.51-2.5N каждого блока селекции выполняют функцию таймеров, которые контролируют истечение допустимого времени (изначального или введенного в рамках управления) поиска путем суммирования поступающих на их счетный вход Z тактовых импульсов и формируют сигнал переполнения на инверсных выходах  счетчиков 2.51-2.5N через установленный интервал времени, определяемый кодами начального заполнения счетчиков и частотой тактовых импульсов.

счетчиков 2.51-2.5N через установленный интервал времени, определяемый кодами начального заполнения счетчиков и частотой тактовых импульсов.

Сигналы с выходов «Результат сравнения» 261-26N блоков селекции 21-2N поступают через входы «Результат сравнения» 811-81N селекционных контроллеров времени поиска 81-8N (см. фиг. 10) на сигнальные входы 8.21-1-8.2N-1 регистров сравнения-коррекции максимального времени поиска 8.21-8.2N, на проверочные входы 8.21-2-8.2N-2 которых поступают в двоичном коде с проверочных выходов 8.11-2-8.1N-2 дешифраторов корректированного кода максимального времени поиска 8.11-8.1N сигналы, характеризующие новое, вводимое в процессе управления, значение (границы) максимального времени поиска для конкретного запроса. При этом дешифраторы корректированного кода максимального времени поиска 8.11-8.1N преобразуют S-разрядный код, обуславливающий новые, вводимые в процессе управления, значения (границы) максимального времени поиска в двоичный код и передают этот код для проверки истинности на регистры сравнения-коррекции максимального времени поиска 8.21-8.2N.

Регистры сравнения-коррекции максимального времени поиска 8.21-8.2N осуществляют дополнительную проверку (сравнение) выполнения требований по своевременности в соответствии с изначальным и вновь вводимым максимальным времени поиска и, выступая в качестве ретранслирующих узлов, формируют на своих выходах 8.21-3-8.2N-3 и на выходах «Результат сравнения» 831-83N селекционных контроллеров времени поиска 81-8N последовательность сигналов, описывающих логические значения, соответствующие результатам сравнения.

Таким образом, на выходах «Результат сравнения» 831-83N селекционных контроллеров времени поиска 81-8N имеем логические значения, соответствующие результатам сравнения и полученные с учетом динамической коррекции максимального времени поиска.

После удовлетворения потребности в поиске информации n-ый поисковый запрос снимается, на выходе «А=В» 2.3n-3 компаратора 2.3n сигнал отсутствует, происходит сброс счетчика 2.5n соответствующего блока селекции 2n по n-ому входу «Обнуление» 017n устройства и входу «Обнуление» 24n соответствующего блока селекции 2n.

В случае, если один или несколько поисковых запросов достигли максимального времени поиска или максимальное время поиска уменьшилось в результате динамической коррекции (управления), происходит переполнение счетчиков 2.51-2.5N соответствующих блоков селекции 21-2N, формирование на их инверсных выходах переполнения  , а, следовательно и на выходах «Результат сравнения» 261-26N соответствующих блоков селекции 21-2N сигнала переполнения, инициирующего блокирование выхода 2.4n-2 инвертора 2.4n и разовое поступление с данного инверсного выхода логических значений, соответствующих результатам сравнения на данный, конкретный момент времени, без возможности продолжения поиска, что соответствует процедуре динамического управления поиском - переносу поисковых запросов заново в очередь на места, соответствующие их приоритетам.

, а, следовательно и на выходах «Результат сравнения» 261-26N соответствующих блоков селекции 21-2N сигнала переполнения, инициирующего блокирование выхода 2.4n-2 инвертора 2.4n и разовое поступление с данного инверсного выхода логических значений, соответствующих результатам сравнения на данный, конкретный момент времени, без возможности продолжения поиска, что соответствует процедуре динамического управления поиском - переносу поисковых запросов заново в очередь на места, соответствующие их приоритетам.

При этом запираются соответствующие трехвходовые элементы И 2.61-2.6N (фиг. 5), запрещая поступление тактовых импульсов на счетные входы Z соответствующих счетчиков 2.51-2.5N блоков селекции 21-2N.

Логические значения, соответствующие результатам сравнения и полученные с учетом динамической коррекции максимального времени поиска с выходов «Результат сравнения» 831-83N селекционных контроллеров времени поиска 81-8N поступают на соответствующие входы «Результат сравнения» 511-51N регистра стратегии поиска 5 и соответствующие входы «Результат сравнения» 611-61N блока формирования адреса маски переходов 6.

При поступлении БДИ, тип которого соответствует одному из типов БДИ, предусмотренных в сценарии поиска, на выходе «Результат сравнения» 26n, например, блока селекции 2n и на соответствующем выходе «Результат сравнения» 83n селекционного контроллера времени поиска 8n, где обнаружено совпадение значений идентификационных битов поступившего БДИ с соответствующими значениями второй битовой маски, будет установлено значение логического нуля, а на выходах всех остальных блоков селекции и, как следствие, селекционных контроллеров времени поиска - значение логической единицы. При поступлении БДИ, не предусмотренного сценарием поиска, на выходах «Результат сравнения» всех блоков селекции и, как следствие, выходах «Результат сравнения» селекционных контроллеров времени поиска будет установлено значение логической единицы.