ПЕРЕКРЕСТНАЯ ССЫЛКА НА РОДСТВЕННЫЕ ЗАЯВКИ

[0001] Настоящая заявка испрашивает приоритет предварительной заявки США 61/484,575, поданной 10 мая 2011, которая включена в настоящий документ посредством ссылки в полном объеме.

ОБЛАСТЬ ТЕХНИКИ

[0002] Настоящее изобретение в целом относится к безопасной обработке данных в устройстве, таком как компьютер или удаленная станция.

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

[0003] Устройство может использовать операционную систему, которая может иметь открытое исходное ядро и/или высоко-доступное низкоуровневое программное обеспечение. К сожалению, защищенные реализации в ядре могут быть изменены с целью извлечения защищенного контента, такого как мультимедийный контент, защищенный с помощью DRM (управление цифровыми правами).

[0004] Существует, следовательно, потребность в эффективном методе для безопасной обработки данных.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

[0005] Один из аспектов настоящего изобретения может относиться к процессору, реализованному аппаратными средствами, для обработки данных из буферной памяти. Процессор включает в себя блок защиты. Блок защиты сконфигурирован для разрешения записи выходных данных, обработанных на основе входных данных из по меньшей мере одной защищенной ячейки, ассоциированной с защищенным диапазоном адресов буферной памяти, в одну или более защищенных ячеек, ассоциированных с защищенным диапазоном адресов. Блок защиты дополнительно сконфигурирован, чтобы блокировать запись выходных данных, обработанных на основе входных данных из по меньшей мере одной защищенной ячейки, ассоциированной с защищенным диапазоном адресов, в одну или более незащищенных ячеек, ассоциированных с незащищенным диапазоном адресов буферной памяти.

[0006] В более подробных аспектах изобретения блок защиты может быть дополнительно сконфигурирован, чтобы разрешать запись выходных данных, обработанных на основе входных данных из по меньшей мере одной незащищенной ячейки, ассоциированной с незащищенным диапазоном адресов, в одну или более незащищенных ячеек, ассоциированных с незащищенным диапазоном адресов. Адреса для защищенного диапазона адресов могут содержать виртуальные адреса. Защищенный диапазон адресов может содержать страницу буферной памяти. Виртуальные адреса могут быть отображены на физические адреса в буферной памяти посредством таблицы страниц. Кроме того, адреса для защищенного диапазона адресов могут содержать физические адреса.

[0007] В других более подробных аспектах изобретения входные данные могут быть основаны на данных, извлеченных из защищенного контента из защищенного источника. Выходные данные могут предназначаться для считывания из буферной памяти посредством аппаратных средств отображения для отображения.

[0008] Другой аспект настоящего изобретения может состоять в устройстве для обработки данных из буферной памяти, содержащем: средство для обеспечения возможности записи выходных данных, обработанных на основе входных данных из по меньшей мере одной защищенной ячейки, ассоциированной с защищенным диапазоном адресов буферной памяти, в одну или более защищенных ячеек, ассоциированных с защищенным диапазоном адресов; и средство для блокирования записи выходных данных, обработанных на основе входных данных из по меньшей мере одной защищенной ячейки, ассоциированной с защищенным диапазоном адресов, в одну или более незащищенных ячеек, ассоциированных с незащищенным диапазоном адресов буферной памяти.

[0009] Другой аспект изобретения может относиться к компьютерному программному продукту, содержащему машиночитаемый носитель, содержащий код для побуждения компьютера разрешать запись выходных данных, обработанных на основе входных данных из по меньшей мере одной защищенной ячейки, ассоциированной с защищенным диапазоном адресов буферной памяти, в одну или более защищенных ячеек, ассоциированных с защищенным диапазоном адресов, и код для побуждения компьютера блокировать запись выходных данных, обработанных на основе входных данных из по меньшей мере одной защищенной ячейки, ассоциированной с защищенным диапазоном адресов, в одну или более незащищенных ячеек, ассоциированных с незащищенным диапазоном адресов буферной памяти.

[0010] Другой аспект настоящего изобретения может состоять в способе обработки данных из буферной памяти. Способ может включать в себя разрешение процессору, реализованному в аппаратных средствах, записывать выходные данные, обработанные на основе входных данных из по меньшей мере одной защищенной ячейки, ассоциированной с защищенным диапазоном адресов буферной памяти, в одну или более защищенных ячеек, ассоциированных с защищенным диапазоном адресов. Способ дополнительно может включать в себя блокирование процессора от записи выходных данных, обработанных на основе входных данных из по меньшей мере одной защищенной ячейки, ассоциированной с защищенным диапазоном адресов, в одну или более незащищенных ячеек, ассоциированных с незащищенным диапазоном адресов буферной памяти.

[0011] Другой аспект настоящего изобретения может состоять в устройстве, содержащем буферную память и процессор. Буферная память имеет множество адресуемых ячеек, содержащих защищенные ячейки, ассоциированные с защищенным диапазоном адресов, и незащищенные ячейки, ассоциированные с незащищенным диапазоном адресов. Процессор реализован в аппаратных средствах для обработки данных из защищенных ячеек и из незащищенных ячеек. Процессор сконфигурирован, чтобы разрешать запись выходных данных, обработанных на основе входных данных из по меньшей мере одной из защищенных ячеек, ассоциированных с защищенным диапазоном адресов, в одну или более защищенных ячеек, ассоциированных с защищенным диапазоном адресов. Процессор также сконфигурирован, чтобы блокировать запись выходных данных, обработанных на основе входных данных из по меньшей мере одной из защищенных ячеек, ассоциированных с защищенным диапазоном адресов, в одну или более незащищенных ячеек, ассоциированных с незащищенным диапазоном адресов.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

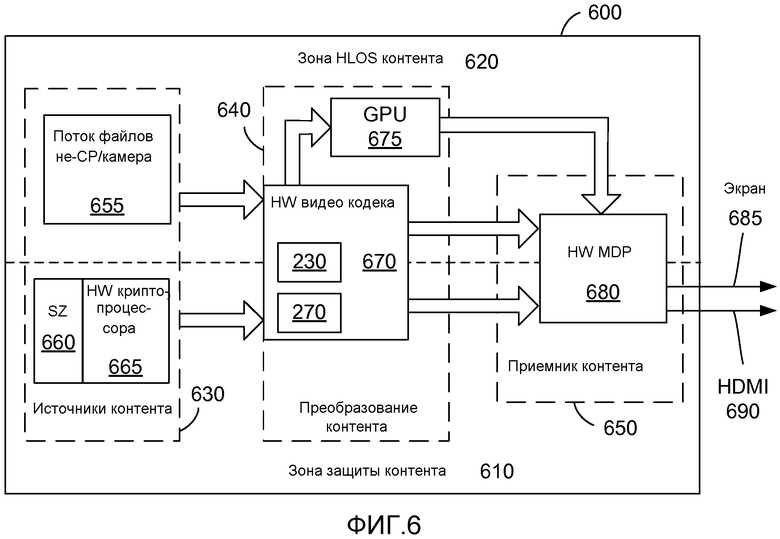

[0012] Фиг. 1 - блок-схема последовательности операций способа обработки данных из буферной памяти, имеющей множество адресуемых ячеек, содержащих ячейки, ассоциированные с защищенным диапазоном адресов, и ячейки, ассоциированные с незащищенным диапазоном адресов, в соответствии с настоящим изобретением.

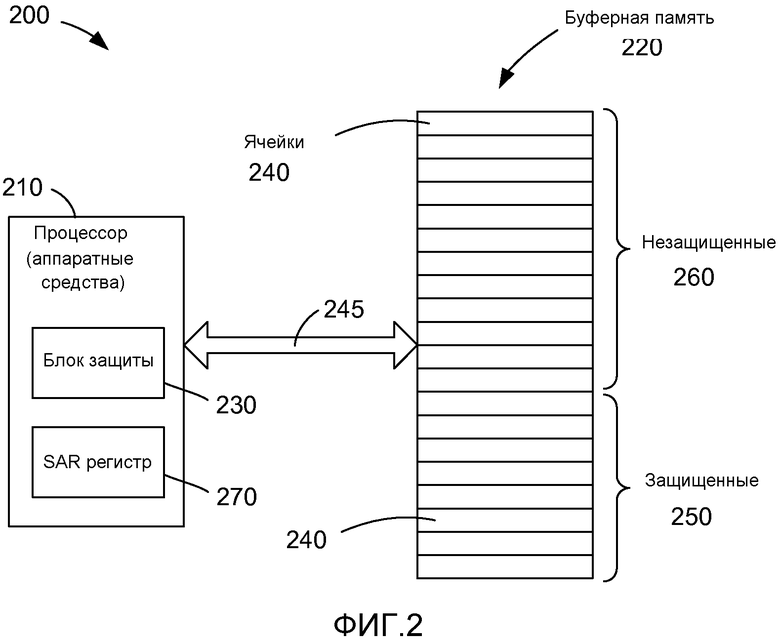

[0013] Фиг. 2 - блок-схема устройства, включающего в себя буферную память и процессор, имеющий блок защиты, в соответствии с настоящим изобретением.

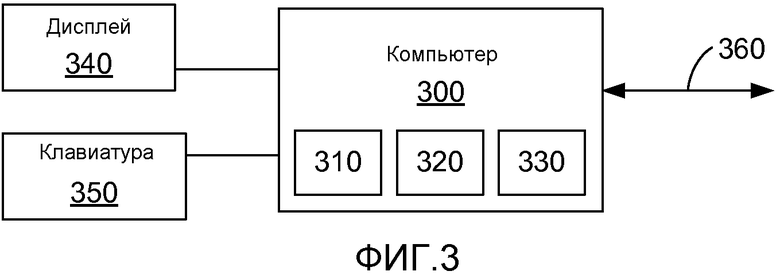

[0014] Фиг. 3 - блок-схема компьютера, включающего в себя процессор и память.

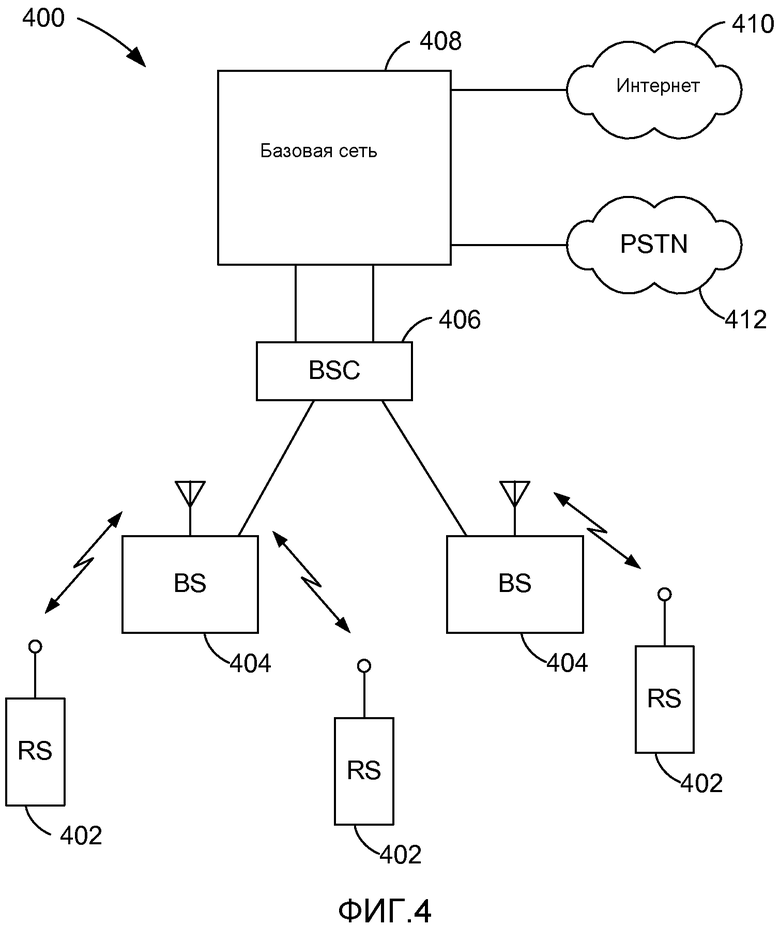

[0015] Фиг. 4 - блок-схема примера системы беспроводной связи.

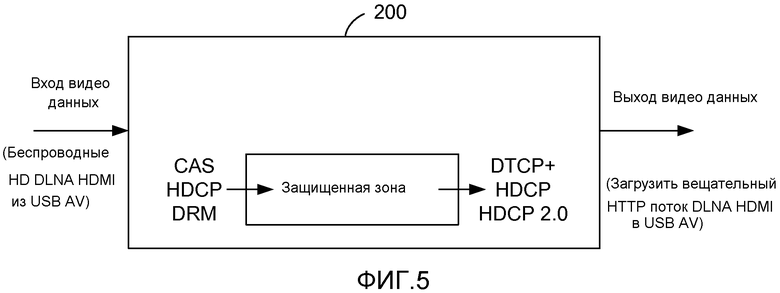

[0016] Фиг. 5 - блок-схема потока данных через устройство, имеющее защищенную зону.

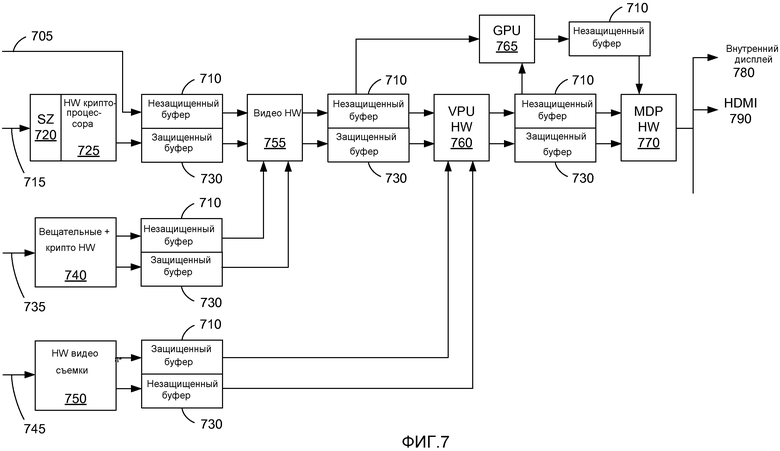

[0017] Фиг. 6 - блок-схема потока(ов) данных через устройство, имеющее защищенную зону.

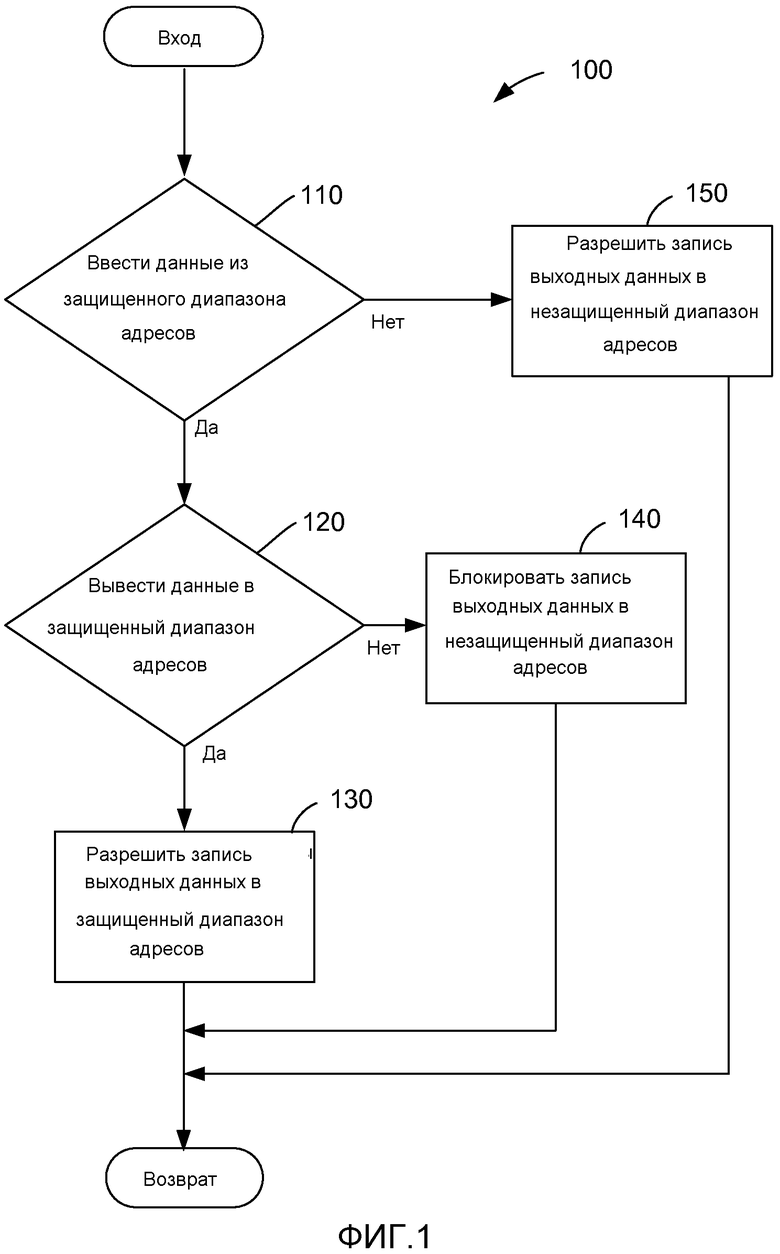

[0018] Фиг. 7 - блок-схема потоков данных через аппаратные средства, имеющие защищенные буферы.

ПОДРОБНОЕ ОПИСАНИЕ

[0019] Слово "примерный" используется здесь для обозначения “служащий в качестве примера, отдельного случая или иллюстрации". Любой вариант осуществления, описанный здесь как "примерный", не обязательно должен быть истолкован как предпочтительный или преимущественный над другими вариантами осуществления.

[0020] Со ссылкой на фиг. 1 и 2, аспект настоящего изобретения может относиться к процессору 210, реализованному в аппаратных средствах, для обработки данных из буферной памяти 220. Процессор 210 включает в себя блок 230 защиты. Процессор 210 считывает предварительно обработанные данные из ячеек 240 памяти в буферной памяти 220 через шину 245 данных. После дальнейшей обработки процессор 210 записывает обработанные данные обратно в ячейки памяти в буферной памяти 220. Данные, сохраненные в буферной памяти 220, могут быть извлечены из защищенного контента, такого как мультимедийный контент, защищенный с использованием DRM, и тому подобное. Предпочтительно поддерживать такие данные защищенными, когда они обрабатывается и "текут" через буферную память 220. Соответственно, данные, извлеченные из защищенного контента, хранятся в ячейке(ах) 240, ассоциированной(ых) с защищенным диапазоном 250 адресов буферной памяти 220. Блок 230 защиты обеспечивает аппаратную защиту потоков данных через буферную память 220, в некоторых вариантах осуществления, не требуя отслеживания потоков данных и ассоциированных сессий и привилегий для сессий.

[0021] В соответствии с правилами безопасности, показанными на фиг. 1, блок 230 защиты сконфигурирован, чтобы разрешать запись выходных данных в одну или более защищенных ячеек 240, ассоциированных с защищенным диапазоном адресов 250, когда выходные данные были обработаны на основе входных данных из по меньшей мере одной защищенной ячейки 240, ассоциированной с защищенным диапазоном 250 адресов буферной памяти 220. Блок 230 защиты дополнительно сконфигурирован, чтобы блокировать запись выходных данных в одну или более незащищенных ячеек 240, ассоциированных с незащищенным диапазоном 260 адресов буферной памяти 220, когда выходные данные были обработаны на основе входных данных из по меньшей мере одной защищенной ячейки 240, ассоциированной с защищенным диапазоном 250 адресов.

[0022] В более конкретных аспектах изобретения блок 230 защиты может быть дополнительно сконфигурирован, чтобы разрешать запись выходных данных, обработанных на основе входных данных из по меньшей мере одной незащищенной ячейки, ассоциированной с незащищенным диапазоном 260 адресов, в одну или несколько незащищенных ячеек, ассоциированных с незащищенным диапазоном 260 адресов. Таким образом, незащищенный контент может обрабатываться без ущерба для безопасности безопасно хранимого защищенного контента.

[0023] Адреса для защищенного диапазона 250 адресов могут содержать виртуальные адреса. Альтернативно, адреса для защищенного диапазона адресов могут включать в себя физические адреса. В защищенной схемы памяти физические адреса ячеек 240 памяти 240 буферной памяти 220 могут быть отображены на виртуальные адреса, например, таблицу страниц, чтобы позволить совместное использование физической памяти различными процессами и/или сессиями при помощи соответствующих независимых виртуальных адресных пространств. Как правило, физические адреса отображаются как 4-килобайтные страницы, хотя другие размеры страниц могут быть использованы. Таким образом, защищенный диапазон 250 адресов защищенной буферной памяти 730 (показано на фиг. 7) может содержать страницу ячеек памяти. В одном варианте осуществления процессор 210 реализует правила безопасности по фиг. 1, требуя записи выходных данных в ту же страницу, что и входные данные. В таком варианте осуществления процессор 210 блокирует запись выходных данных на другую страницу. Если защищенный диапазон 250 адресов содержит множество страниц, то страницы могут быть или могут не быть смежными в буферной памяти 220.

[0024] Ячейки 240 памяти могут быть сгруппированы в другие конфигурации, включая блоки, сегменты, порции и тому подобное. Защищенный диапазон 250 адресов буферной памяти 220 может включать такие блоки, сегменты, порции и т.д.

[0025] Хранилище данных, такое как регистр 270 защищенного диапазона адресов (SAR), может хранить защищенный диапазон 250 адресов. Регистр 270 может находиться в безопасно защищенной зоне, чтобы предотвратить изменение или взлом вредоносным программным обеспечением. Когда входные данные считываются, регистр 270 защищенного диапазона адресов может быть проверен блоком 230 защиты, чтобы определить, являются ли входные данные данными из защищенных ячеек. Аналогичным образом, когда выходные данные должны быть записаны, регистр 270 защищенного диапазона адресов может быть проверен устройством 230 защиты для определения того, должны ли выходные данные быть записаны в защищенную ячейку.

[0026] Другой аспект настоящего изобретения может состоять в устройстве 200 для обработки данных из буферной памяти 220, содержащем: средство (230) для разрешения записи выходных данных, обработанных на основе входных данных из по меньшей мере одной защищенной ячейки 240, ассоциированной с защищенным диапазоном 250 адресов буферной памяти 220, в одну или более защищенных ячеек 240, ассоциированных с защищенным диапазоном 250 адресов, и средство (230) для блокирования записи выходных данных, обработанных на основе входных данных из по меньшей мере одной защищенной ячейки, ассоциированной с защищенным диапазоном 250 адресов, в одну или более незащищенных ячеек, ассоциированных с незащищенным диапазоном 260 адресов буферной памяти 220.

[0027] Другой аспект изобретения может относиться к компьютерному программному продукту, содержащему машиночитаемый носитель 320 (фиг. 3), содержащий код для побуждения компьютера 300 разрешать запись выходных данных, обработанных на основе входных данных из по меньшей мере одной защищенной ячейки 240, ассоциированной с защищенным диапазоном 250 адресов буферной памяти 220, в одну или более защищенных ячеек, ассоциированных с защищенным диапазоном 250 адресов; и код для побуждения компьютера блокировать запись выходных данных, обработанных на основе входных данных из по меньшей мере одной защищенной ячейки, ассоциированной с защищенным диапазоном 250 адресов, в одну или более незащищенных ячеек, ассоциированных с незащищенным диапазоном 260 адресов буферной памяти 220.

[0028] Другой аспект изобретения может относиться к способу 100 для обработки данных из буферной памяти 220. Способ 100 может включать в себя разрешение процессору 210, реализованному в аппаратных средствах, записывать выходные данные, обработанные на основе входных данных из по меньшей мере одной защищенной ячейки 240, ассоциированной с защищенным диапазоном адресов 250 буферной памяти 220 (этап 110), в одну или более защищенных ячеек, ассоциированных с защищенным диапазоном 250 адресов (этапы 120 и 130). Способ 100 дополнительно может включать в себя блокирование процессора 210 от записи выходных данных, обработанных на основе входных данных из по меньшей мере одной защищенной ячейки, ассоциированной с защищенным диапазоном 250 адресов, в одну или более незащищенных ячеек, ассоциированных с незащищенным диапазоном 260 адресов буферной памяти 220 (этап 140). Способ 100 может дополнительно включать разрешение процессору 210 записывать выходные данные, обработанные на основе входных данных из по меньшей мере одной незащищенной ячейки, ассоциированной с незащищенным диапазоном 260 адресов, в одну или более незащищенных ячейках, ассоциированных с незащищенным диапазоном 260 адресов (этап 150).

[0029] Другой аспект настоящего изобретения может состоять в устройстве 200, содержащем буферную память 220 и процессор 210. Буферная память 220 имеет множество адресуемых ячеек 240, содержащих защищенные ячейки, ассоциированные с защищенным диапазоном 250 адресов, и незащищенные ячейки, ассоциированные с незащищенным диапазоном 260 адресов. Процессор 210 реализован в аппаратных средствах для обработки данных из защищенных ячеек и из незащищенных ячеек. Процессор 210 сконфигурирован для разрешения записи выходных данных, обработанных на основе входных данных из по меньшей мере одной из защищенных ячеек, ассоциированных с защищенным диапазоном 250 адресов, в одну или более защищенных ячеек, ассоциированных с защищенным диапазоном 250 адресов. Процессор 210 также сконфигурирован, чтобы блокировать запись выходных данных, обработанных на основе входных данных из по меньшей мере одной из защищенных ячеек, ассоциированных с защищенным диапазоном 250 адресов, в одну или более незащищенных ячеек, ассоциированных с незащищенным диапазоном 260 адресов.

[0030] Устройство 200 может быть удаленной станцией, включающий в себя компьютер 300, который включает в себя процессор 310, такой как процессор 210, запоминающий носитель 320, такой как память 220 и дисководы, дисплей 340, устройство ввода, такое как клавиатура 350, микрофон, динамик(и), камера и тому подобное. Станция может включать в себя интерфейс, например, антенну и/или модем и/или приемопередатчик для использования с беспроводным соединением 360. В некоторых вариантах осуществления станция может дополнительно содержать безопасный модуль 330. Безопасный модуль 330 может использоваться в некоторых вариантах осуществления для реализации блока 230 защиты и/или SAR регистра 270 отдельно от процессора 310. В других вариантах осуществления безопасный модуль 330 может реализовывать другие функции безопасности и/или защиты записи. В некоторых вариантах осуществления безопасный модуль 330 может быть опущен. В одном иллюстративном варианте осуществления, где блок 230 защиты 230 и SAR регистр 270 реализованы в процессоре 310, безопасный модуль 330 опускается. Кроме того, станция также может включать в себя USB, Ethernet и/или подобные интерфейсы.

[0031] Со ссылкой на фиг. 5, контент, такой как видеоданные, может быть введен в устройство 200 из различных источников, таких как загрузка, передача, HTTP поток, DLNA (Digital Living Network Alliance - набор стандартов, позволяющий совместимым устройствам передавать и принимать по домашней сети медиа-контент), HDMI (High-Definition Multimedia Interface - интерфейс для мультимедиа высокой четкости), USB AV (Universal Serial Bus Audio/Visual - Универсальная последовательная шина аудио/видео) и тому подобное. Защищенный контент (CAS (Conditional Access System - Система условного доступа), HDCP (High-bandwidth Digital Content Protection - Защита широкополосного цифрового контента), DRM (Digital Rights Management - Управление цифровыми правами) и т.д.) направляется в защищенную зону, реализованную устройством. Высокоуровневая операционная система (или ядро) не может получить прямой доступ к защищенной зоне. Устройство предоставляет обработанные выходные данные (слова) в адресуемые ячейки 240 памяти, ассоциированные с или находящиеся в защищенном диапазоне 250 адресов, в соответствии с правилами безопасности (фиг. 1). Выходные данные могут быть защищенным контентом (DTCP+ (Digital Transmission. Content Protection Plus - Цифровая передача. Защита контента плюс), HDCP, HDCP 2.0 и т.д.), направляемым непосредственно на устройство 340 отображения. Выходные видеоданные могут соответствовать беспроводному HD (High-Definition - Высокой четкости), DLNA, HDMI-выходу, USB AV и тому подобному.

[0032] Защищенная зона может быть ассоциирована с набором блоков обработки для реализации одной или более функций. Множество блоков обработки может включать в себя видеодекодер, процессор мобильных данных и тому подобное.

[0033] Со ссылкой на фиг. 6, устройство 600, которое может, например, содержать реализацию устройства 200 и/или компьютер 300, может иметь зону 610 защиты контента и зону 620 контента высокоуровневой операционной системы (HLOS). В некоторых вариантах осуществления зона 610 защиты может содержать реализацию защищенной зоны, обсужденной выше. Устройство может иметь источники 630 контента, преобразователи 640 контента и приемник(и) 650 контента. Источники контента могут быть потоками 655 файлов незащищенного контента и защищенным контентом, ассоциированным с безопасной зоной (SZ) 660 (безопасной средой исполнения) и аппаратными средствами (HW) 665 криптопроцессора. Защищенный контент может быть, например, мультимедийным контентом, защищенным с использованием DRM. Данные из защищенных источников контента остаются в пределах зоны 610 защиты контента, и данные из незащищенных источников контента остаются в пределах зоны 620 HLOS контента. Преобразование контента может быть выполнено аппаратными средствами 670 видеокодека и графическим процессором (GPU) 675. GPU может работать только с незащищенным контентом, в то время как аппаратные средства видеокодека могут работать с защищенным контентом и незащищенным контентом. Аппаратные средства видеокодека могут включать в себя блок 230 защиты и SAR регистр 270 для обеспечения того, чтобы дешифрованные и/или декодированные данные записывались только в адресуемые ячейки 240 памяти в соответствии с правилами безопасности, показанными на фиг. 1. Приемник 650 контента может включать в себя аппаратные средства 680 мобильной платформы отображения (MDP) для вывода мультимедийного контента на экран 685 или 340 устройства или в HDMI канал 690 и т.д.

[0034] Со ссылкой на фиг. 7, поток данных через буферную память 220 из множества источников 630 контента к множеству приемников 650 контента показан по отношению к множеству преобразователей 640 контента. Незащищенный буфер 710 соответствует ячейкам 240 памяти, ассоциированным с незащищенным диапазоном 260 адресов буферной памяти, а защищенный буфер 730 соответствует ячейкам 240 памяти, ассоциированным с защищенным диапазоном 250 адресов буферной памяти. Чтобы показать поток данных через буферную память, незащищенные и защищенные буферы 710 и 730 показаны в нескольких экземплярах между элементами аппаратных средств (HW). Однако несколько защищенных и незащищенных буферов могут быть единым адресным пространством буферной памяти 220, которая соединена с элементами аппаратных средств, например, посредством шины 245. В качестве примеров источников контента свободный контент из незащищенного источника 705 может быть помещен в ячейки памяти незащищенного буфера 710, ассоциированного с незащищенным диапазоном 260 адресов, в то время как высококачественный контент из защищенного источника 715 может быть введен в безопасную зону 720 (безопасную среду исполнения) и аппаратные средства 725 криптопроцессора, а затем выводится в ячейки памяти защищенного буфера 730, ассоциированного с защищенным диапазоном 250 адресов. Вещательный контент 735 может быть принят, дешифрован в случае необходимости и помещен в незащищенный буфер 710 или в защищенный буфер 730 при помощи аппаратных средств 740 вещания+шифрования, в зависимости от того, зашифрован ли входящий вещательный сигнал. Аналогично, сигналы 745 видео, захваченные аппаратными средствами 750 видеосъемки, могут быть помещены в незащищенный буфер 710 или в защищенный буфер 730, в зависимости от того, является ли входной сигнал видеозащищенным. Например, если HDCP включен на вход HDMI, то контент может обрабатываться как защищенный. Кроме того, если сигнал Macrovision®/CGMS-A (система управления генерацией копирования - аналоговая) обнаружен на аналоговом входе, то контент может обрабатываться как защищенный. Для цифрового (TTL) входа контент может обрабатываться как защищенный по умолчанию. В качестве примера преобразования контента видеоаппаратные средства 755 могут работать с данными из незащищенного буфера 710 и/или защищенного буфера 730 и помещать выходные данные в незащищенный буфер 710 или в защищенный буфер 730, в соответствии с правилами безопасности на фиг. 1. Аналогичным образом, аппаратные средства 760 видеопроцессора (VPU) могут работать с данными из незащищенного буфера 710 и/или защищенного буфера 730 и помещать выходные данные в незащищенный буфер 710 или в защищенный буфер 730, в соответствии с правилами безопасности на фиг. 1. Графический процессор (GPU) 765 может работать только с данными из незащищенного буфера 710 и может помещать выходные данные только в незащищенный буфер 710. В качестве примеров приемников контента MDP аппаратные средства 770 могут считывать и работать с данными из незащищенного буфера 710 и/или защищенного буфера 730 и выводить данные в форме мультимедийного контента на экран 780 устройства или в HDMI канал 790 и т.д.

[0035] Множество сессий и/или потоков контента могут существовать одновременно. Каждая сессия или поток могут быть ассоциированы с общим защищенным диапазоном 250 адресов или своим собственным защищенным диапазоном 250 адресов или страницей ячеек памяти. Например, первый защищенный диапазон адресов или страница для первой сессии или потока не может рассматриваться как защищенный диапазон адресов для второй сессии или потока. Аппаратные средства процессора могут блокировать запись выходных данных, ассоциированных с второй сессией или потоком, в первый защищенный диапазон адресов или страницу, потому что первый защищенный диапазон адресов или страница могут рассматриваться как незащищенная ячейка памяти по отношению к второй сессии. Однако если реализован общий защищенный диапазон адресов 250, то защита данных может быть упрощена в некоторых вариантах осуществления, потому что разные диапазоны адресов могут индивидуально не отслеживаться по отношению к различным сессиям или потокам, а вместо этого один диапазон адресов может применяться ко всему или некоторому охраняемому контенту. В некоторых вариантах осуществления сессии или потоки могут быть ассоциированы с различными процессорами. Каждый из этих процессоров может быть ассоциирован со своим собственным защищенным диапазоном адресов и/или буферной памятью в некоторых вариантах осуществления. В других вариантах осуществления два или более процессоров могут совместно использовать буферную память или защищенный диапазон адресов этой буферной памяти.

[0036] Варианты осуществления, описанные выше, могут обеспечивать аппаратную защиту потоков данных через буферную память 220 без того, чтобы отслеживать потоки данных и ассоциированные сессии и привилегии для сессий. Таким образом, защищенный контент и незащищенный контент из различных источников может быть обработан аппаратными средствами преобразования контента без необходимости отслеживания привилегий ассоциированных сессий при записи обработанных или преобразованных данных в буферную память. Когда правила безопасности на фиг. 1 реализованы в аппаратных средствах, вредоносное программное обеспечение не может перенаправить защищенный контент в незащищенную ячейку памяти, так как аппаратные средства блокируют такое вредоносное перенаправление.

[0037] Со ссылкой на фиг. 4, беспроводная удаленная станция (RS) 402 (такая как устройство 200) может осуществлять связь с одной или более базовых станций (BS) 404 системы 400 беспроводной связи. Система 400 беспроводной связи может дополнительно включать в себя один или более контроллеров базовых станций (BSC) 406 и базовую сеть 408. Базовая сеть может быть подключена к Интернету 410 и/или коммутируемой телефонной сети общего пользования (PSTN) 412 через соответствующие транзитные линии. Типичная беспроводная удаленная станция может включать в себя мобильную станцию, такую как портативный телефон или портативный компьютер. Система 400 беспроводной связи может использовать любой из множества методов множественного доступа, таких как множественный доступ с кодовым разделением (CDMA), множественный доступ с временным разделением (TDMA), множественный доступ с частотным разделением (FDMA), множественный доступ с пространственным разделением (SDMA), множественный доступ с поляризационным разделением (PDMA) или другие методы модуляции, известные в данной области.

[0038] Специалистам в данной области техники будет понятно, что информация и сигналы могут быть представлены с использованием любых из множества различных технологий и методов. Например, данные, инструкции, команды, информация, сигналы, биты, символы и элементарные сигналы, которые могут упоминаться на всем протяжении вышеприведенного описания, могут быть представлены напряжениями, токами, электромагнитными волнами, магнитными полями или частицами, оптическими полями или частицами или любой их комбинацией.

[0039] Специалистам в данной области будет понятно, что различные иллюстративные логические блоки, модули, схемы и этапы алгоритма, описанные в связи с раскрытыми вариантами осуществления, могут быть реализованы в виде электронных аппаратных средств, компьютерного программного обеспечения или их комбинации. Чтобы ясно проиллюстрировать эту взаимозаменяемость аппаратных средств и программного обеспечения, различные иллюстративные компоненты, блоки, модули, схемы и этапы были описаны выше в общем в терминах их функциональных возможностей. Реализованы ли такие функциональные возможности как аппаратные средства или программное обеспечение, зависит от конкретного применения и конструктивных ограничений, наложенных на всю систему. Специалисты в данной области техники смогут реализовать описанные функциональные возможности различными способами для каждого конкретного применения, но такие решения по реализации не должны интерпретироваться как вызывающие отклонение от объема настоящего изобретения.

[0040] Различные иллюстративные логические блоки, модули и схемы, описанные в связи с раскрытыми вариантами осуществления, могут быть реализованы или выполнены с помощью процессора общего назначения, цифрового сигнального процессора (DSP), специализированной интегральной схемы (ASIC), программируемой пользователем вентильной матрицы (FPGA) или другого программируемого логического устройства, дискретного логического элемента или транзисторной логики, дискретных компонентов аппаратных средств или любой их комбинации, разработанной для выполнения описанных здесь функций. Процессор общего назначения может быть микропроцессором, но в альтернативном варианте процессор может быть любым обычным процессором, контроллером, микроконтроллером или конечным автоматом. Процессор также может быть реализован в виде комбинации вычислительных устройств, например комбинации DSP и микропроцессора, множества микропроцессоров, одного или более микропроцессоров в соединении с DSP-ядром или любой другой такой конфигурации.

[0041] Этапы способа или алгоритма, описанные в связи с раскрытыми вариантами осуществления, могут быть воплощены непосредственно в аппаратных средствах, в программном модуле, выполняемом процессором, или в комбинации того и другого. Модуль программного обеспечения может находиться в памяти RAM, флэш-памяти, памяти ROM, памяти EPROM, памяти EEPROM, регистрах, жестком диске, съемном диске, компакт-диске или любой другой форме носителя данных, известного в данной области. Примерный запоминающий носитель соединен с процессором так, что процессор может считывать информацию и записывать информацию на запоминающий носитель. В качестве альтернативы, запоминающий носитель может быть неотъемлемой частью процессора. Процессор и запоминающий носитель могут находиться в ASIC. ASIC может постоянно находиться в пользовательском терминале. В альтернативном варианте процессор и запоминающий носитель могут постоянно размещаться как дискретные компоненты в пользовательском терминале.

[0042] В одном или более примерных вариантах осуществления описанные функции могут быть реализованы в аппаратных средствах, программном обеспечении, программно-аппаратных средствах или любой их комбинации. При реализации в программном виде компьютерного программного продукта, функции могут быть сохранены или переданы как одна или более инструкций или код на машиночитаемом носителе. Машиночитаемый носитель включает в себя как компьютерные запоминающие носители, так и среду связи, включая любой носитель, который способствует передаче компьютерной программы из одного места в другое. Запоминающие носители могут быть любыми доступными носителями, к которым может обращаться компьютер. В качестве примера, но не ограничения, такие машиночитаемые носители могут содержать RAM, ROM, EEPROM, CD-ROM или другой накопитель на оптических дисках, накопитель на магнитных дисках или другие магнитные запоминающие устройства или любой другой носитель, который может использоваться для переноса или хранения желаемого программного кода в форме инструкций или структур данных и к которому можно получить доступ с помощью компьютера. Кроме того, любое подключение корректно называть машиночитаемым носителем. Например, если программное обеспечение передается с веб-сайта, сервера или другого удаленного источника с использованием коаксиального кабеля, оптоволоконного кабеля, витой пары, цифровой абонентской линии (DSL) или беспроводных технологий, таких как инфракрасная, радиочастотная и микроволновая, то коаксиальный кабель, волоконно-оптический кабель, витая пара, DSL или беспроводные технологии, такие как инфракрасная, радиочастотная и микроволновая, включаются в определение носителя. Магнитный диск и оптический диск, как используется здесь, включают в себя компакт-диск (CD), лазерный диск, оптический диск, цифровой универсальный диск (DVD), гибкий диск и диск Blu-ray, где магнитные диски (disks) обычно воспроизводят данные магнитным способом, в то время как оптические диски (discs) воспроизводят данные оптически с помощью лазеров. Комбинации вышеперечисленного также должны быть включены в объем машиночитаемых носителей. Машиночитаемый носитель может быть не временным (постоянным, нетранзитивным), так что он не включает временный (транзитивный) распространяющийся сигнал.

Предыдущее описание раскрытых вариантов осуществления предоставлено, чтобы дать возможность любому специалисту в данной области техники изготовить или использовать настоящее изобретение. Различные модификации этих вариантов осуществления будут очевидны специалистам в данной области техники, а общие принципы, определенные здесь, могут быть применены к другим вариантам осуществления без отступления от сущности или объема изобретения. Таким образом, настоящее изобретение не предназначено быть ограниченным вариантами осуществления, показанными здесь, но должно соответствовать самому широкому объему, совместимому с принципами и новыми признаками, раскрытыми в данном документе.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ МОДИФИКАЦИИ РАЗРЕШЕНИЙ НА ДОСТУП К ПАМЯТИ В ЗАЩИЩЕННОЙ ПРОЦЕССОРНОЙ СРЕДЕ | 2014 |

|

RU2602793C2 |

| МАТРИЧНО-ВЕКТОРНЫЙ УМНОЖИТЕЛЬ С НАБОРОМ РЕГИСТРОВ ДЛЯ ХРАНЕНИЯ ВЕКТОРОВ, СОДЕРЖАЩИМ МНОГОПОРТОВУЮ ПАМЯТЬ | 2019 |

|

RU2795887C2 |

| ОТЛОЖЕННАЯ ОЧИСТКА БУФЕРОВ БЫСТРОГО ПРЕОБРАЗОВАНИЯ АДРЕСОВ | 2004 |

|

RU2361267C2 |

| СИСТЕМА И СПОСОБ ДЛЯ ЗАЩИТЫ ОТ НЕДОВЕРЕННОГО КОДА РЕЖИМА УПРАВЛЕНИЯ С СИСТЕМОЙ С ПОМОЩЬЮ ПЕРЕАДРЕСАЦИИ ПРЕРЫВАНИЯ РЕЖИМА УПРАВЛЕНИЯ СИСТЕМОЙ И СОЗДАНИЯ КОНТЕЙНЕРА ВИРТУАЛЬНОЙ МАШИНЫ | 2003 |

|

RU2313126C2 |

| БОЛЕЕ БЫСТРЫЙ ДОСТУП ЗАПОМИНАЮЩЕГО УСТРОЙСТВА ВИРТУАЛЬНОЙ МАШИНЫ, РЕЗЕРВИРУЕМОГО ВИРТУАЛЬНЫМ ЗАПОМИНАЮЩИМ УСТРОЙСТВОМ ВЫЧИСЛИТЕЛЬНОГО ХОСТ-УСТРОЙСТВА | 2019 |

|

RU2780969C1 |

| ОТОБРАЖЕНИЕ ДОСТОВЕРНОСТИ ИЗ ВЫСОКОНАДЕЖНОЙ СРЕДЫ НА НЕЗАЩИЩЕННУЮ СРЕДУ | 2004 |

|

RU2390836C2 |

| ФИЛЬТРАЦИЯ СОБЫТИЙ ДЛЯ ПРИЛОЖЕНИЙ БЕЗОПАСНОСТИ ВИРТУАЛЬНЫХ МАШИН | 2017 |

|

RU2723668C1 |

| УПРАВЛЕНИЕ УДАЛЕНИЕМ В СИСТЕМАХ ПАМЯТИ | 2014 |

|

RU2638006C2 |

| Процессор мультиобработки данных | 1975 |

|

SU590745A1 |

| РЕАЛИЗАЦИЯ УПРАВЛЕНИЯ ДОСТУПОМ К ПАМЯТИ С ИСПОЛЬЗОВАНИЕМ ОПТИМИЗАЦИЙ | 2004 |

|

RU2364932C2 |

Изобретение относится к вычислительной технике. Технический результат заключается в безопасной обработке данных. Процессор для обработки потока данных из множества источников мультимедийного контента для устройства отображения содержит блок защиты, который определяет, основаны ли выходные данные, подлежащие записи из видеокодека в буферную память, на входных данных из по меньшей мере одной защищенной ячейки, ассоциированной с защищенным диапазоном адресов буферной памяти, и в ответ на определение: i) разрешает запись выходных данных в одну или более защищенных ячеек буферной памяти, причем защищенные ячейки ассоциированы с защищенным диапазоном адресов буферной памяти; и ii) блокирует запись выходных данных в одну или более незащищенных ячеек буферной памяти, причем незащищенные ячейки ассоциированы с незащищенным диапазоном адресов буферной памяти. 5 н. и 29 з.п. ф-лы, 7 ил.

1. Процессор, реализованный в аппаратных средствах, для обработки потока данных из множества источников мультимедийного контента для устройства отображения, причем процессор функционирует между видеокодеком для передачи данных мультимедийного контента для отображения и буферной памятью, причем процессор содержит:

блок защиты, выполненный с возможностью:

определять, основаны ли выходные данные, подлежащие записи из видеокодека в буферную память, на входных данных из по меньшей мере одной защищенной ячейки, ассоциированной с защищенным диапазоном адресов буферной памяти, и

в ответ на определение, что выходные данные, подлежащие записи в буферную память, основаны на входных данных из по меньшей мере одной защищенной ячейки, ассоциированной с защищенным диапазоном адресов буферной памяти:

i) разрешать запись выходных данных в одну или более защищенных ячеек буферной памяти, причем защищенные ячейки ассоциированы с защищенным диапазоном адресов буферной памяти; и

ii) блокировать запись выходных данных в одну или более незащищенных ячеек буферной памяти, причем незащищенные ячейки ассоциированы с незащищенным диапазоном адресов буферной памяти.

2. Процессор по п. 1, в котором блок защиты дополнительно выполнен с возможностью разрешать запись выходных данных, обработанных на основе входных данных из по меньшей мере одной незащищенной ячейки, ассоциированной с незащищенным диапазоном адресов, в одну или более незащищенных ячеек, ассоциированных с незащищенным диапазоном адресов.

3. Процессор по п. 1, в котором адреса для защищенного диапазона адресов содержат виртуальные адреса.

4. Процессор по п. 3, в котором защищенный диапазон адресов содержит страницу буферной памяти.

5. Процессор по п. 4, в котором виртуальные адреса отображены на физические адреса в буферной памяти посредством таблицы страниц.

6. Процессор по п. 1, в котором адреса для защищенного диапазона адресов содержат физические адреса.

7. Процессор по п. 1, в котором входные данные основаны на данных, извлеченных из защищенного контента из защищенного источника.

8. Процессор по п. 1, в котором выходные данные предназначены для считывания из буферной памяти посредством аппаратных средств отображения.

9. Устройство для обработки потока данных из множества источников мультимедийного контента для устройства отображения, причем устройство функционирует между видеокодеком для передачи данных мультимедийного контента для отображения и буферной памятью, при этом устройство содержит:

средство для определения, основаны ли выходные данные, подлежащие записи из видеокодека в буферную память, на входных данных из по меньшей мере одной защищенной ячейки, ассоциированной с защищенным диапазоном адресов буферной памяти; и средство, в ответ на определение, что выходные данные, подлежащие записи в буферную память, основаны на входных данных из по меньшей мере одной защищенной ячейки, ассоциированной с защищенным диапазоном адресов буферной памяти, для:

i) разрешения записи выходных данных в одну или более защищенных ячеек буферной памяти, причем защищенные ячейки ассоциированы с защищенным диапазоном адресов буферной памяти; и

ii) блокирования записи выходных данных в одну или более незащищенных ячеек буферной памяти, причем незащищенные ячейки ассоциированы с незащищенным диапазоном адресов буферной памяти.

10. Устройство по п. 9, дополнительно содержащее средство для разрешения записи выходных данных, обработанных на основе входных данных из по меньшей мере одной незащищенной ячейки, ассоциированной с незащищенным диапазоном адресов, в одну или более незащищенных ячеек, ассоциированных с незащищенным диапазоном адресов.

11. Устройство по п. 9, в котором адреса для защищенного диапазона адресов содержат виртуальные адреса.

12. Устройство по п. 11, в котором защищенный диапазон адресов содержит страницу буферной памяти.

13. Устройство по п. 12, в котором виртуальные адреса отображаются на физические адреса в буферной памяти посредством таблицы страниц.

14. Устройство по п. 9, в котором адреса для защищенного диапазона адресов содержат физические адреса.

15. Устройство по п. 9, в котором входные данные основаны на данных, извлеченных из защищенного контента из защищенного источника.

16. Устройство по п. 9, в котором выходные данные предназначены для считывания из буферной памяти посредством аппаратных средств отображения.

17. Машиночитаемый носитель, на котором сохранен компьютерный программный продукт, причем компьютерный программный продукт содержит:

код для предписания компьютеру определять, основаны ли выходные данные, подлежащие записи из видеокодека в буферную память, на входных данных из по меньшей мере одной защищенной ячейки, ассоциированной с защищенным диапазоном адресов буферной памяти, и

код для предписания компьютеру, в ответ на определение, что выходные данные, подлежащие записи в буферную память, основаны на входных данных из по меньшей мере одной защищенной ячейки, ассоциированной с защищенным диапазоном адресов буферной памяти:

i) разрешать запись выходных данных в одну или более защищенных ячеек буферной памяти, причем защищенные ячейки ассоциированы с защищенным диапазоном адресов буферной памяти; и

ii) блокировать запись выходных данных в одну или более незащищенных ячеек буферной памяти, причем незащищенные ячейки ассоциированы с незащищенным диапазоном адресов буферной памяти.

18. Машиночитаемый носитель по п. 17, дополнительно содержащий:

код для предписания компьютеру разрешать запись выходных данных, обработанных на основе входных данных из по меньшей мере одной незащищенной ячейки, ассоциированной с незащищенным диапазоном адресов, в одну или более незащищенных ячеек, ассоциированных с незащищенным диапазоном адресов.

19. Машиночитаемый носитель по п. 17, в котором адреса для защищенного диапазона адресов содержат виртуальные адреса.

20. Машиночитаемый носитель по п. 19, в котором защищенный диапазон адресов содержит страницу буферной памяти.

21. Машиночитаемый носитель по п. 20, в котором виртуальные адреса отображаются на физические адреса в буферной памяти посредством таблицы страниц.

22. Машиночитаемый носитель по п. 17, в котором адреса для защищенного диапазона адресов содержат физические адреса.

23. Машиночитаемый носитель по п. 17, в котором входные данные основаны на данных, извлеченных из защищенного контента из защищенного источника.

24. Машиночитаемый носитель по п. 17, в котором выходные данные предназначены для считывания из буферной памяти для отображения.

25. Способ обработки потока данных из множества источников мультимедийного контента посредством видеокодека и ассоциированной буферной памяти, причем способ содержит этапы, на которых:

определяют, основаны ли выходные данные, подлежащие записи из видеокодека в буферную память, на входных данных из по меньшей мере одной защищенной ячейки, ассоциированной с защищенным диапазоном адресов буферной памяти, и

в ответ на определение, что выходные данные, подлежащие записи в буферную память, основаны на входных данных из по меньшей мере одной защищенной ячейки, ассоциированной с защищенным диапазоном адресов буферной памяти:

i) разрешают видеокодеку, реализованному в аппаратных средствах, записывать выходные данные в одну или более защищенных ячеек буферной памяти, причем защищенные ячейки ассоциированы с защищенным диапазоном адресов; и

ii) блокируют видеокодек от записи выходных данных в одну или более незащищенных ячеек буферной памяти, причем незащищенные ячейки ассоциированы с незащищенным диапазоном адресов буферной памяти.

26. Способ по п. 25, дополнительно содержащий разрешение видеокодеку записывать выходные данные, обработанные на основе входных данных из по меньшей мере одной незащищенной ячейки, ассоциированной с незащищенным диапазоном адресов, в одну или более незащищенных ячеек, ассоциированных с незащищенным диапазоном адресов.

27. Способ по п. 25, в котором адреса для защищенного диапазона адресов содержат виртуальные адреса.

28. Способ по п. 27, в котором защищенный диапазон адресов содержит страницу буферной памяти.

29. Способ по п. 28, в котором виртуальные адреса отображаются на физические адреса в буферной памяти посредством таблицы страниц.

30. Способ по п. 25, в котором адреса для защищенного диапазона адресов содержат физические адреса.

31. Способ по п. 25, в котором входные данные основаны на данных, извлеченных из защищенного контента из защищенного источника.

32. Способ по п. 25, в котором выходные данные предназначены для считывания из буферной памяти для отображения.

33. Устройство для обработки потока данных из множества источников мультимедийного контента посредством видеокодека и ассоциированной буферной памяти, содержащее:

буферную память, имеющую множество адресуемых ячеек, содержащую:

защищенные ячейки, ассоциированные с защищенным диапазоном адресов, и

незащищенные ячейки, ассоциированные с незащищенным диапазоном адресов, и

процессор, реализованный в аппаратных средствах, для обработки данных из защищенных ячеек и из незащищенных ячеек, причем процессор выполнен с возможностью:

определения, основаны ли выходные данные, подлежащие записи из видеокодека в буферную память, на входных данных из по меньшей мере одной защищенной ячейки, ассоциированной с защищенным диапазоном адресов буферной памяти; и

в ответ на определение, что выходные данные, подлежащие записи в буферную память, основаны на входных данных из по меньшей мере одной защищенной ячейки, ассоциированной с защищенным диапазоном адресов буферной памяти:

i) разрешения записи выходных данных в одну или более защищенных ячеек, ассоциированных с защищенным диапазоном адресов, и

ii) блокирования записи выходных данных в одну или более из незащищенных ячеек, ассоциированных с незащищенным диапазоном адресов.

34. Устройство по п. 33, в котором процессор дополнительно выполнен с возможностью разрешения записи выходных данных, обработанных на основе входных данных из по меньшей мере одной из незащищенных ячеек, ассоциированных с незащищенным диапазоном адресов, в одну или более незащищенных ячеек, ассоциированных с незащищенным диапазоном адресов.

| US 4184201 А, 15.01.1980 | |||

| Станок для изготовления деревянных ниточных катушек из цилиндрических, снабженных осевым отверстием, заготовок | 1923 |

|

SU2008A1 |

| Колосоуборка | 1923 |

|

SU2009A1 |

| Устройство для регистрации информации | 1984 |

|

SU1256056A1 |

| СИСТЕМА ВРЕМЕННОГО ЗАПОМИНАНИЯ ИНФОРМАЦИИ | 1991 |

|

RU2138845C1 |

Авторы

Даты

2016-01-20—Публикация

2012-05-10—Подача