Область техники, к которой относится изобретение

Настоящее изобретение относится, к области обработки информации и более конкретно в области обеспечения безопасности в системах обработки информации.

Уровень техники

Многие системы обработки информации сохраняют, передают и используют конфиденциальную информацию. Поэтому были разработаны способы обеспечения безопасного обращения и хранения конфиденциальной информации. Эти способы содержат разнообразные подходы к созданию и поддержанию безопасных, защищенных или изолированных контейнера, секции или среды в системе обработки информации.

Краткое описание чертежей

Настоящее изобретение иллюстрируется примерами и без ограничений на прилагаемых чертежах.

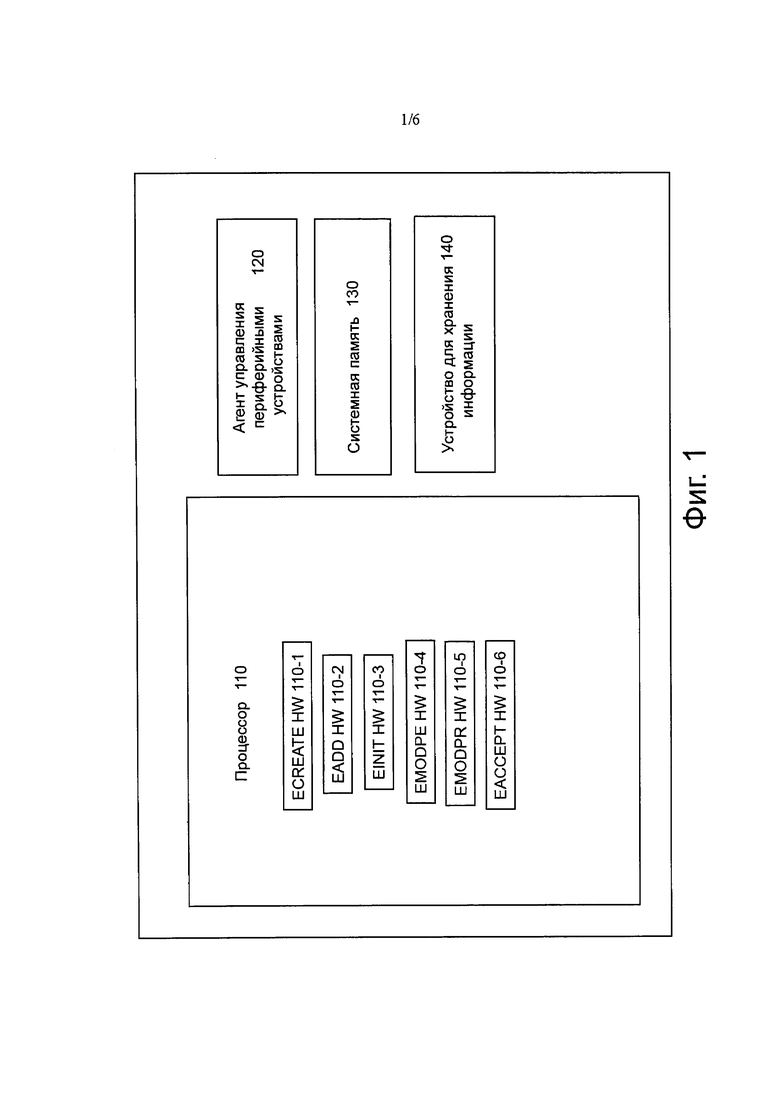

Фиг. 1. иллюстрирует систему для модификации разрешений на доступ к памяти в защищенной процессорной среде согласно одному из вариантов настоящего изобретения.

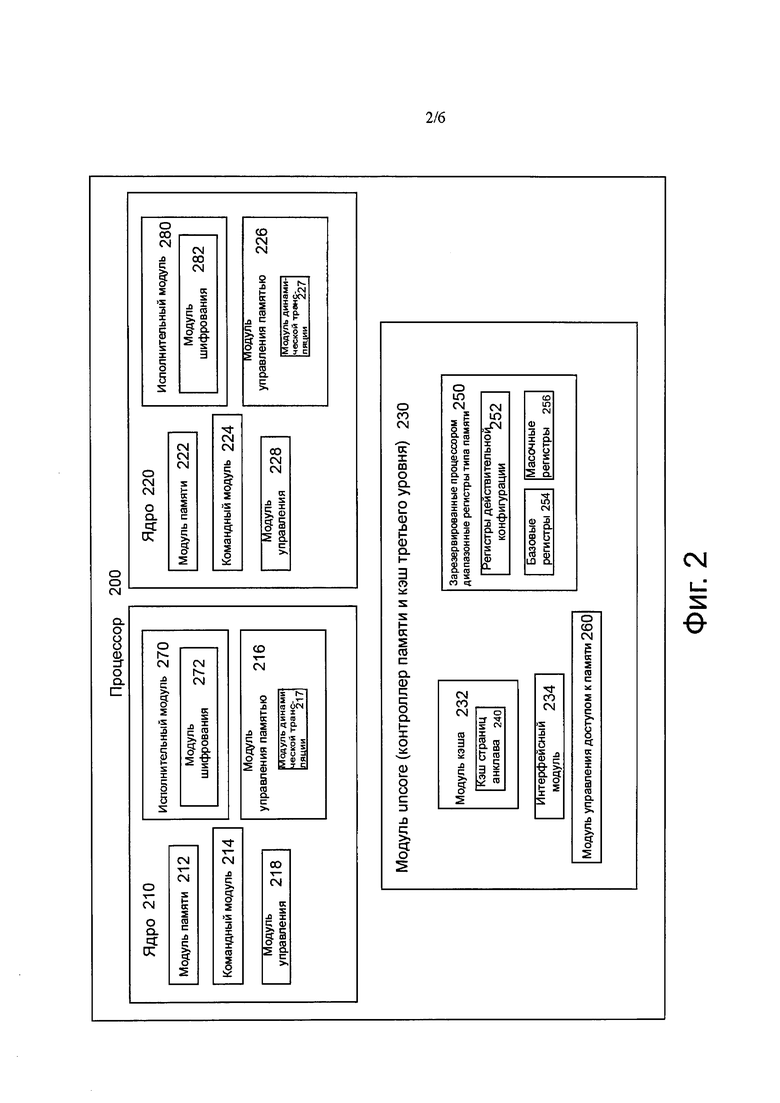

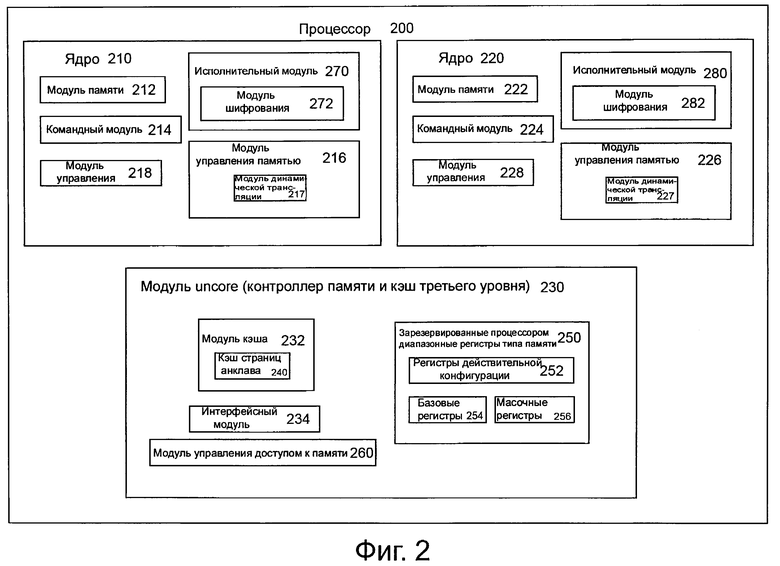

Фиг. 2 иллюстрирует процессор для модификации разрешений на доступ к памяти в защищенной процессорной среде согласно одному из вариантов настоящего изобретения.

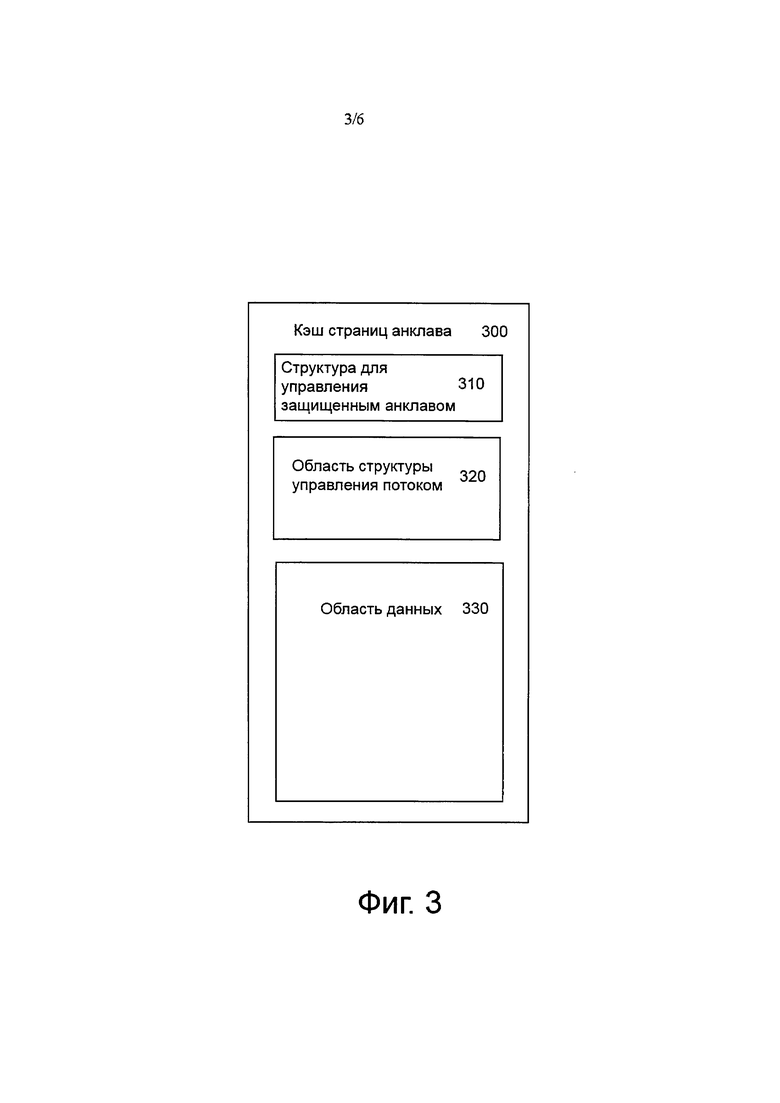

Фиг. 3 иллюстрирует кэш страниц анклава согласно одному из вариантов настоящего изобретения.

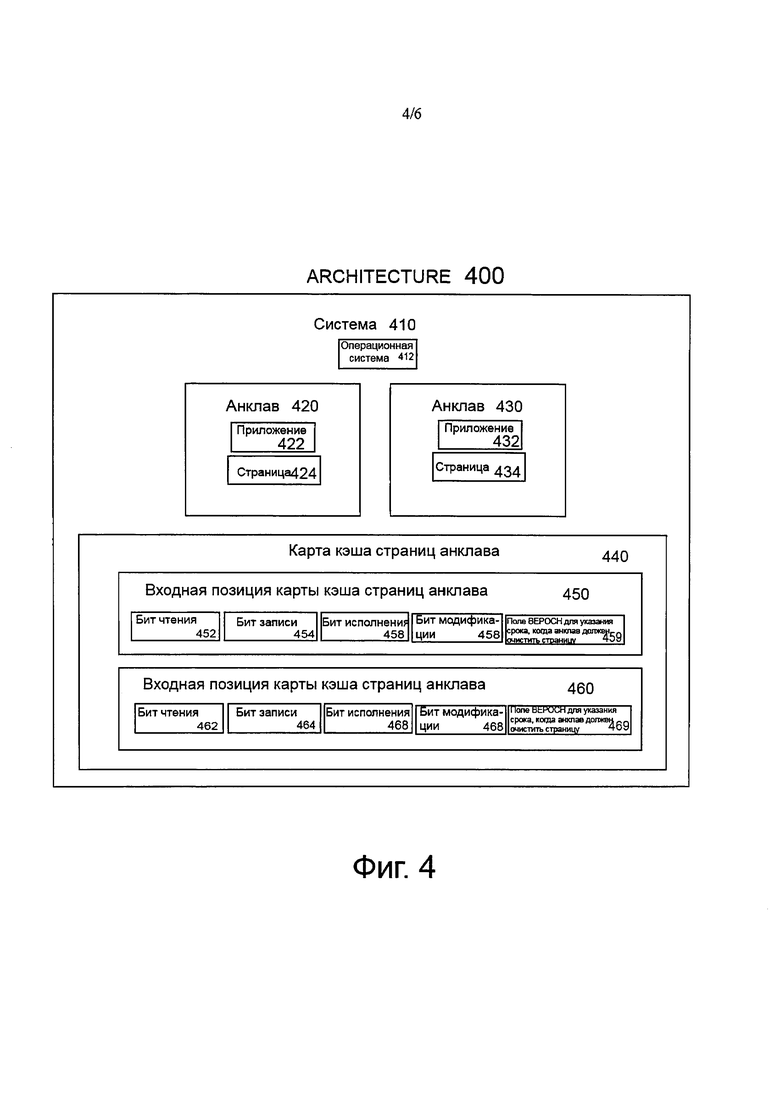

Фиг. 4 иллюстрирует архитектуру системы, содержащей защищенные процессорные среды согласно одному из вариантов настоящего изобретения.

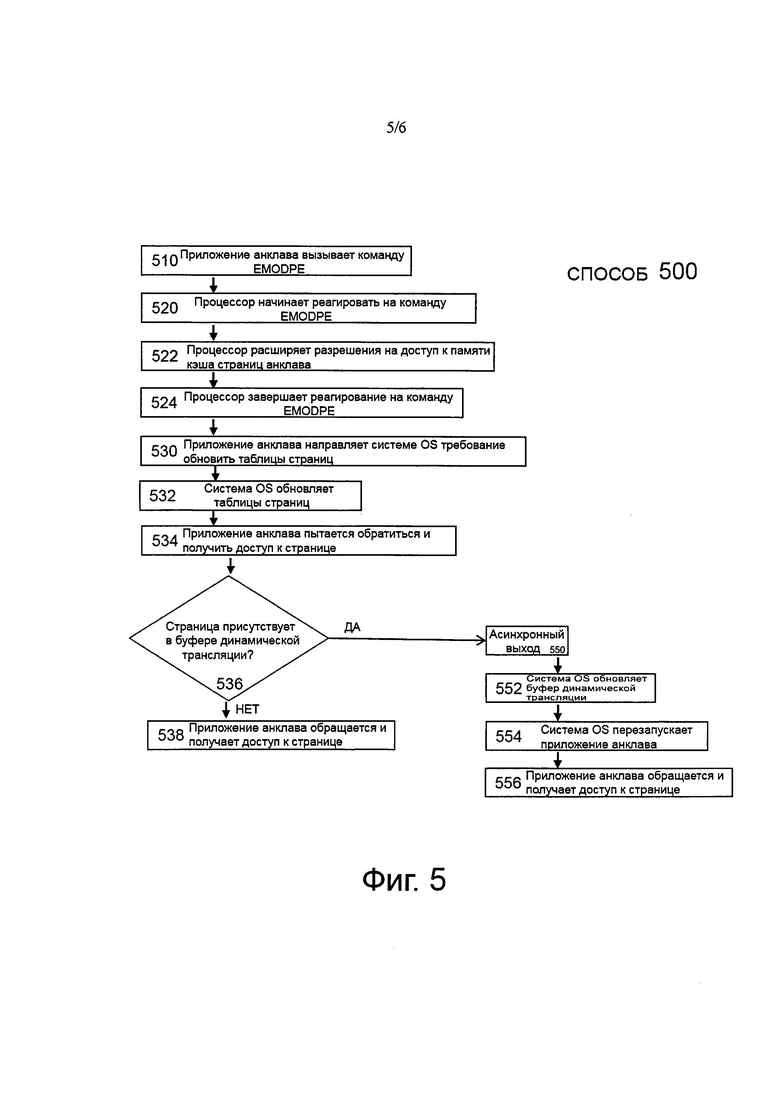

Фиг. 5 иллюстрирует способ расширения разрешений на доступ к памяти в защищенной процессорной среде согласно одному из вариантов настоящего изобретения.

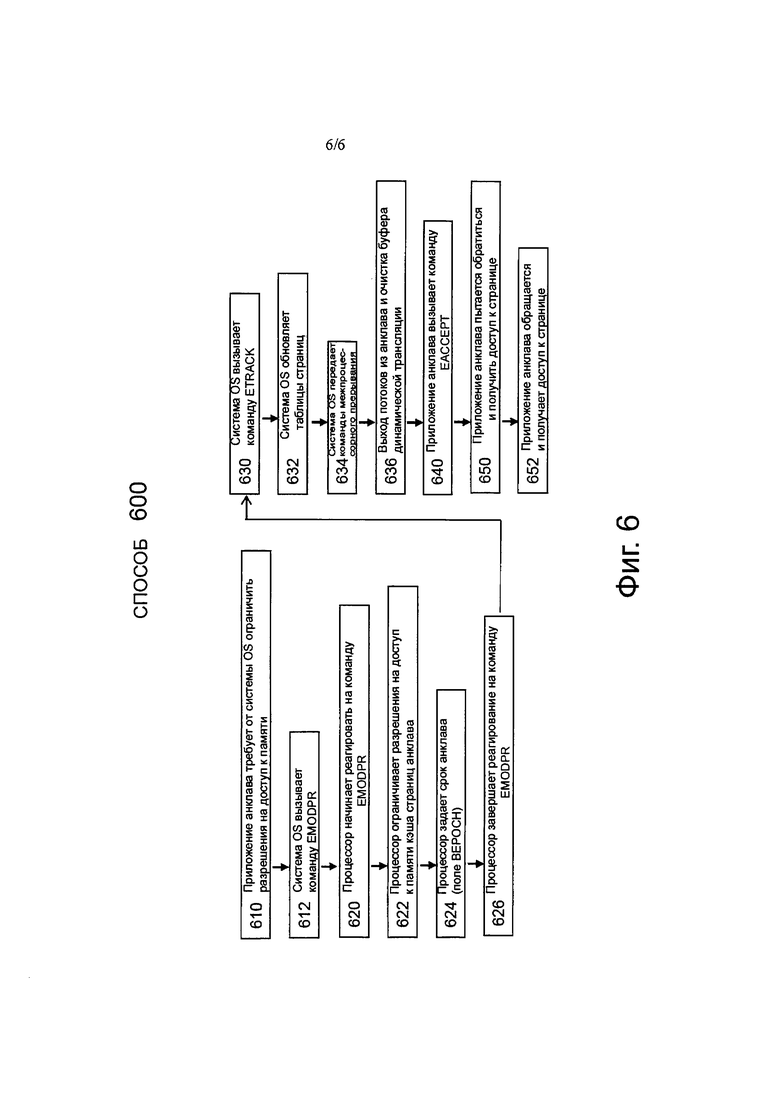

Фиг. 6 иллюстрирует способ ограничения разрешений на доступ к памяти в защищенной процессорной среде согласно одному из вариантов настоящего изобретения.

Подробное описание

Здесь описаны варианты изобретения, направленного на модификацию разрешений на доступ к памяти в защищенной процессорной среде. В этом описании могут быть приведены многочисленные конкретные подробности, такие как конфигурации компонентов и систем, с целью достижения более глубокого понимания настоящего изобретения. Однако специалисту в рассматриваемой области должно быть понятно, что настоящее изобретение может быть практически реализовано и без таких конкретных подробностей. Кроме того, некоторые хорошо известные структуры, способы и другие признаки не показаны подробно, чтобы избежать ненужного загромождения и затемнения описания настоящего изобретения.

В последующем описании ссылки на «один вариант», «какой-либо вариант», «пример варианта», «различные варианты» и т.д. указывают, что среда согласно настоящему изобретению может содержать конкретные признаки, структуры или характеристики, но при этом более одного варианта могут иметь и не каждый вариант обязательно обязан иметь эти конкретные признаки, структуры или характеристики. Более того, некоторые варианты могут иметь некоторые признаки, все признаки или ни одного признака, описанного для других вариантов.

При использовании в Формуле изобретения, если не указано иначе, применение порядковых прилагательных «первый», «второй», «третий» и т.п. для описания элемента означает только, что речь идет о конкретном случае элемента или разных случаях подобных элементов, и не имеет целью указать, что описываемые таким способом элементы должны быть в какой-то конкретной последовательности, будь то во времени, в пространстве, по рангу или каким-либо иным образом.

Кроме того, термины «бит», «флаг», «поле», «входная позиция», «индикатор» и т.д. могут быть использованы для описания позиций хранения данных в регистре, таблице, базе данных или другой структуре данных, реализованной аппаратно или программно, но не означают ограничения вариантов настоящего изобретения каким-либо конкретным типом позиций хранения данных, либо числом битов или каких-либо других элементов в какой-либо конкретной позиции хранения данных. Термин «очистка» (“clear”) может быть использован для указания записи или внесения другим способом нулевой логической величины в позицию памяти, а термин «задание» (“set”) может быть использован для указания, записи или внесения другим способом величины логической единицы, всех единиц или какой-либо другой заданной величины в позицию памяти; однако эти термины не означают ограничения вариантов настоящего изобретения какой-либо конкретной логической конвенцией, поскольку в рамках вариантов настоящего изобретения может быть использована любая логическая конвенция.

Как указано в разделе о предпосылках для создания изобретения, были разработаны разнообразные подходы к созданию и поддержанию безопасных, защищенных или изолированных контейнера, секции или среды в системе обработки информации. Один такой подход использует защищенные анклавы, как описано в одновременно рассматриваемой Заявке на выдачу патента США под названием «Способ и устройство для защищенного выполнения приложений» (“Method and Apparatus to Provide Secure Application Execution”), Serial No. 13/527,547, поданной 19 июня 2012 г., где приведена информация относительно по меньшей мере одного варианта безопасных, защищенных или изолированных контейнера, секции или среды. Однако эта ссылка не имеет целью ограничить каким-либо образом объем вариантов настоящего изобретения, так что могут быть использованы и другие варианты, остающиеся в пределах смысла и объема настоящего изобретения. Поэтому любые случаи каких-либо безопасных, защищенных или изолированных контейнера, секции или среды, используемые в вариантах настоящего изобретения, могут здесь именоваться защищенным анклавом или просто анклавом.

Варианты настоящего изобретения предлагают динамическую модификацию разрешений на доступ к анклаву памяти без того, чтобы сделать память недоступной для приложений, работающих в анклаве, в процессе модификации. Модели использования анклава могут содержать работу программного обеспечения внутри анклава с применением ограничений для разрешений на доступ к памяти с целью оптимизировать характеристики полупостоянных (только для чтения) структур данных, с ожиданиями, что считыватели смогут обращаться к структуре данных во время процесса модификации разрешений на доступ к памяти. Варианты настоящего изобретения могут удовлетворить такие ожидания при некоторых условиях, не требуя при этом увеличения снижающих производительность издержек по выходу из анклава для модификации разрешений. Например, критичный сегмент кода может копировать динамическую страницу («кучу») в новую позицию во время операции «сбора мусора», когда процессы записи на эту страницу должны сделать паузу, но варианты настоящего изобретения позволяют считывателям безопасно продолжать доступ.

Фиг. 1 иллюстрирует систему 100, т.е. систему обработки информации, осуществляющую модификацию разрешений на доступ к памяти в защищенной процессорной среде согласно одному из вариантов настоящего изобретения. Система 100 может представлять собой систему обработки информации любого типа, такую как сервер, настольный компьютер, портативный компьютер, приставка, ручное устройство, типа планшетного компьютера или смартфона, или встроенная система управления. Система 100 содержит процессор 110, агент 120 управления периферийными устройствами, системную память 130 и устройство 140 для хранения информации. Системы, реализующие настоящее изобретение, могут содержать любое число компонентов каждого из перечисленных типов, а также любые другие компоненты или иные элементы, такие как периферийные устройства и устройства ввода/вывода. Любые или все такие компоненты или другие элементы в рассматриваемом варианте или в любом варианте системы могут быть соединены, связаны или иначе осуществлять связь одни с другими через произвольное число шин, двухпунктовых или других проводных или беспроводных интерфейсов или соединений, если специально не указано иное. Любые компоненты или другие части системы 100, показаны ли они на Фиг. 1 или нет, могут быть интегрированы или другим способом выполнены на одном кристалле (система-на-кристалле или SOC), на одной подложке или в одном корпусе.

Агент 120 управления периферийными устройствами может представлять собой любой компонент, такой как компонент чипсета, который содержит периферийные устройства, устройства ввода/вывода, либо другие компоненты или устройства или через который эти компоненты или устройства могут быть соединены или связаны с процессором 110. Системная память 130 может представлять собой динамическое запоминающее устройство с произвольной выборкой или носитель какого-либо другого типа, читаемый процессором 110. Устройство 140 для хранения информации может содержать постоянную или энергонезависимую память или. запоминающее устройство любого типа, такого как флэш-память и/или накопитель на твердотельном, магнитном или оптическом диске.

Процессор 110 может представлять собой один или несколько процессоров, интегрированных на одной общей подложке или смонтированных в одном общем корпусе, так что каждый из этих процессоров может содержать несколько потоков и/или несколько исполнительных ядер в любом сочетании. Каждый процессор, представленный в качестве или в составе процессора 110, может представлять собой процессор любого типа, включая микропроцессоры общего назначения, такие как процессоры семейства Intel® Core® Processor Family, семейства Intel® Atom® Processor Family или какого-либо другого семейства процессоров от компании Intel® Corporation, или другой процессор производства, какой-либо другой компании, или процессор специального назначения или микроконтроллер.

Процессор 110 может работать в соответствии с архитектурой набора команд, содержащей первую команду для создания защищенного анклава, вторую команду для добавления контента в анклав, третью команду для инициализации анклава, четвертую команду для расширения разрешений на доступ к памяти, пятую команду для ограничения разрешений на доступ к памяти и шестую команду для удостоверений ограничения разрешения. Хотя варианты настоящего изобретения могут быть практически реализованы с использованием процессора, имеющего любую архитектуру набора команд, и никак не ограничиваются архитектурой семейства процессоров от компании, эти команды могут представлять собой часть набора расширений существующей архитектуры для защиты программного обеспечения, и могут именоваться здесь как команда ECREATE, команда EADD, команда EINIT, команда EMODPE, команда EMODPR и команда ЕАССЕРТ, соответственно. Поддержка для этих команд может быть реализована в процессоре с использованием любого сочетания схем и/или логики, встроенной в аппаратуру процессора, микрокода, встроенного программного обеспечения и/или других структур, организованных, как будет описано ниже, или согласно какому-либо другому подходу, и показана на Фиг. 1 в виде аппаратного модуля ECREATE 110-1, аппаратного модуля EADD 110-2, аппаратного модуля ЕГМТ 110-3, аппаратного модуля EMODPE 110-4, EMODPR аппаратного модуля 110-5 и аппаратного модуля ЕАССЕРТ 110-6.

На Фиг. 2 показан процессор, вариант которого может служить процессором 110 в системе 100. Процессор 200 может содержать ядро 210, ядро 220 и модуль uncore (контроллер памяти и кэш третьего уровня) 230. Ядро 210 может содержать модуль 212 памяти, командный модуль 214, исполнительный модуль 270, модуль 216 управления памятью (MMU) и модуль 218 управления. Ядро 220 может содержать модуль 222 памяти, командный модуль 224, исполнительный модуль 280, модуль MMU 226 и модуль 228 управления. Модуль uncore 230 может содержать модуль 232 кэша, интерфейсный модуль 234, зарезервированные процессором диапазонные регистры 250 типа памяти и модуль 260 управления доступом к памяти. Процессор 200 может также содержать также какие-либо другие схемы, структуры или логику, не показанные на Фиг. 2. Функциональные возможности аппаратного модуля ECREATE 110-1, аппаратного модуля EADD 110-2, аппаратного модуля EINIT 110-3, аппаратного модуля EMODPE 110-4, аппаратного модуля EMODPR 110-5 и аппаратного модуля ЕАССЕРТ 110-6, как указано выше и дополнительно объясняется ниже, могут быть сосредоточены в или распределены между какими-либо маркированными и поименованными модулями или где-либо еще в процессоре 200.

Модули 212 и 222 памяти могут содержать какое-либо сочетание запоминающих устройств любого типа, пригодных для каких-либо целей в ядрах 210 и 220, соответственно; например, они могут содержать какое-либо количество читаемых, записываемых и/или читаемых/записываемых регистров, буферов и/или кэшей, реализованных с использованием какой-либо технологии памяти или хранения данных, для сохранения информации о возможностях, информации о конфигурации, информации управления, информации состояния, информации о производительности, команд, данных и/или другой информации, используемой во время работы ядер 210 и 220 соответственно, равно как и схемы для доступа к таким устройствам памяти и хранения данных.

Командные модули 214 и 224 могут содержать какие-либо схемы, логику, структуры и/или другую аппаратуру для выборки, приема, декодирования, интерпретации или планирования команд, таких как команды EMODPE, EMODPR и ЕАССЕРТ, для выполнения ядрами 210 и 220, соответственно. В рамках настоящего изобретения может быть использован любой формат команд; например, команда может содержать код операции и один или несколько операндов, причем код операции может быть декодирован для разложения на одну или несколько микрокоманд или микроопераций для выполнения посредством исполнительными модулями 270 или 280, соответственно. Команды, такие как перечисленные выше, могут быть «лепестками» одного кода операции, такого как код привилегированной операции защищенного анклава (например, ENCLS) или код непривилегированной операции защищенного анклава (например, ENCLU), где команды «лепестки» специфицированы величиной в регистре процессора (например, ЕАХ). Операнды или другие параметры могут быть ассоциированы с командой неявно, прямо, косвенно или в соответствии с каким-либо другим подходом.

Исполнительные модули 270 и 280 могут содержать любые схемы, логику, структуры и/или другую аппаратуру, такую как арифметические модули, логические модули, модули для операций с плавающей запятой, модули сдвига, и т.п., для обработки данных и выполнения команд, таких как команды EMODPE, EMODPR и ЕАССЕРТ, микрокоманды и/или микрооперации. Исполнительные модули 270 и 280 могут содержать модули 272 и 282, соответственно, шифрования, которые могут представлять собой какие-либо схемы, логику, структуры и/или другую аппаратуру для выполнения одного или нескольких алгоритмов шифрования и соответствующих алгоритмов дешифровки с использованием схем, логики, структур и/или другой аппаратуры, специализированной для шифрования/дешифровки или совместно используемой в исполнительных модулях 270 и 280 или где-либо еще в процессоре 200 для выполнения других функций.

Модули MMU 216 и 226 могут содержать любые схемы, логику, структуры и/или другую аппаратуру для управления пространством памяти ядер 210 и 220 соответственно. Логика управления памятью поддерживает использование виртуальной памяти для предоставления программному обеспечению, включая «гостевое» программное обеспечение, работающему в виртуальной памяти (VM), адресного пространства для хранения кода и данных и доступа к ним, так что это предоставляемое адресное пространство больше адресного пространства физической памяти в системе, например, системной памяти 130. Пространство виртуальной памяти ядер 210 и 220 может быть ограничено только числом адресных битов, доступных для программного обеспечения, работающего в процессоре, тогда как пространство физической памяти этих ядер 210 и 220 дополнительно ограничено размером системной памяти 130. Модули MMU 216 и 226 поддерживают схему управления памятью, такую как разбиение на страницы, для подкачки кода исполняемого программного обеспечения и данных в системную память и из нее по мере необходимости. Как часть такой схемы программное обеспечение может обращаться и получать доступ в пространство виртуальной памяти процессора с нетранслированными адресами, которые процессор транслирует и превращает в транслированные адреса, какие процессор может использовать для доступа в физическое адресное пространство этого процессора.

Соответственно, модули MMU 216 и 226 могут каждый содержать каждый буферы динамической трансляции (translation lookaside buffers (TLB)) 217 и 227, соответственно, для сохранения трансляций виртуальных, логических, линейных или иных нетранслированных адресов в физические или другие транслированные адреса в соответствии с известным способом управления памятью, таким как разбиение на страницы. Для осуществления таких трансляций адресов модули MMU 216 и 226 могут справляться с одной или несколькими структурами данных, хранящимися в процессоре 200, системной памяти 130 или другом, не показанном на Фиг. 1, месте хранения данных в системе 100 и/или в сочетании этих мест. Эти структуры данных могут содержать директории страниц и таблицы страниц в соответствии с архитектурой процессоров семейства Pentium® Processor Family.

Модули 218 и 228 управления могут содержать какой-либо микрокод, встроенные программы, схемы, логику, структуры и/или другую аппаратуру для управления работой модулей и других элементов ядер 210 и 220 соответственно, и передают данные в пределах этих ядер 210 и 220, в эти ядра и из них. По командам этих модулей 218 и 228 управления ядра 210 и 220 и процессор 200 в целом могут осуществлять или участвовать в осуществлении вариантов способа согласно настоящему изобретению, таких как варианты способа, рассмотренные ниже, например, путем инициирования выполнения ядрами 210 и 220 команд, таких как команды EMODPE, EMODPR и ЕАССЕРТ, принимаемые командными модулями 214 и 224, и микрокоманд или микроопераций, полученных из команд, принятых командными модулями 214 и 224.

Модуль 232 кэша может содержать любое число массивов кэша и контроллеров кэша на одном или нескольких уровней кэш-памяти в иерархии памяти в системе 100 обработки информации, реализованных в виде статического запоминающего устройства с произвольной выборкой или с применением другой технологии памяти. Модуль 232 кэша может быть совместно использован любым числом ядер и/или логических процессоров в процессоре 200 согласно какому-либо подходу к кэшированию в системах обработки информации. Модуль 232 кэша может также содержать один или несколько массивов памяти для использования в качестве кэша 240 страниц анклава (enclave page cache (ЕРС)), как это будет дополнительно описано ниже.

Интерфейсный модуль 234 может представлять собой какую-либо схему, логику, структуру и/или другую аппаратуру, такую как модуль линий связи, модуль шин или модуль передачи сообщений, позволяющие процессору 200 осуществлять связь с другими компонентами в системе, такой как система 100, посредством шин какого-либо типа, двухпунктовых или других соединений непосредственно или через какой-либо другой компонент, такой как мост, концентратор или чипсет. Интерфейсный модуль 234 может содержать один или несколько встроенных контроллеров памяти для связи с системной памятью, такой как системная память 130, или может осуществлять связь с системной памятью через один или несколько контроллеров памяти, находящихся вне процессора 200.

Зарезервированные процессором диапазонные регистры 250 типа памяти (processor reserved memory range registers (PRMRR)) могут представлять собой одну или несколько позиций для хранения команд и данных в модулях 212 и 222 памяти, где-либо еще в процессоре 200 и/или копий в модуле uncore 230. Регистры PRMRR 250 могут быть использованы, например, встроенными программами конфигурации, такими как базовая система ввода/вывода (BIOS), для резервирования одного или нескольких физически непрерывных диапазонов памяти, именуемых зарезервированной процессором памятью (processor reserved memory (PRM)). Модуль 260 управления доступом к памяти может представлять собой какие-либо схемы, логику, структуры и/или другую аппаратуру в любом месте в процессоре 200, которые могут управлять доступом к памяти PRM, так что кэш ЕРС 240 может быть создан в пространстве системной памяти, определенном как память PRM.

В одном из вариантов память PRM имеет размер, равный целой степени двух, например, 32 Мбайт, 64 Мбайт или 128 Мбайт, и совмещена с адресами памяти, кратными этому размеру. Группа регистров PRMRR 250 может содержать один или несколько только читаемых регистров PRMMR 252 действительной конфигурации, для указания действительных размеров, с которыми может быть конфигурирована память PRM, один или несколько базовых регистров PRMMR 254 и масочных регистров PRMMR 256 для определения одного или нескольких базовых адресов и диапазонов памяти PRM.

Кэш ЕРС 240 представляет собой защищенную область памяти, в которой программное обеспечение может быть защищено от атак какой-нибудь вредоносной программы, работающей на привилегированном уровне. Могут быть созданы один или несколько защищенных анклавов, так что каждый анклав может содержать одну или несколько страниц или других областей кэша ЕРС 240, в которых сохраняют код, данные или другую информацию таким образом, что доступ к ним может иметь только программное обеспечение, работающее внутри анклава, исключительно согласно вариантам настоящего изобретения. Например, защищенный анклав может быть использован программой приложения, так что только эта программа приложения, работающая внутри анклава, может получить доступ к контенту этого анклава, исключительно согласно вариантам настоящего изобретения. Исключительно согласно вариантам настоящего изобретения, ни другое программное обеспечение, ни даже операционная система или монитор виртуальной машины не могут считывать незашифрованный контент этого анклава, модифицировать контент этого анклава или каким-то иным способом «взламывать» контент этого анклава, когда этот контент загружен в кэш ЕРС (предполагается, что анклав является производственным анклавом в отличие, например, от отладочного анклава). Однако доступ к анклаву может получить программное обеспечение, исполняемое изнутри анклава на любом процессоре в системе 100. Эта защита обеспечивается модулем 260 управления доступом к памяти, работающим в соответствии с архитектурой защищенных анклавов.

На Фиг. 2 кэш ЕРС 240 показан в составе модуля 232 кэша, где он может быть усеченной частью совместно используемого кэша, либо выделенной областью памяти. В рамках процессора 200 или на одном кристалле с процессором кэш ЕРС 240 может быть реализован в виде статического запоминающего устройства с произвольной выборкой, встроенного динамического запоминающего устройства с произвольной выборкой или с применением какой-либо другой технологии памяти. Кэш ЕРС 240 может быть также или дополнительно реализован вне процессора 200, например, в защищенной области системной памяти 130. Для защиты контента защищенных анклавов, когда они хранятся не на кристалле, могут быть использованы модули 272 и/или 282 шифрования, чтобы зашифровывать контент перед тем, как передать его за пределы кристалла и расшифровывать контент, переданный назад в кэш ЕРС 240 на кристалле. Для защиты контента от воспроизведения и других атак могут быть также использованы другие механизмы защиты.

На Фиг. 3 показан кэш ЕРС 300, один из вариантов которого может быть использован в качестве кэша ЕРС 240 на Фиг. 2. На Фиг. 3 кэш ЕРС 300 содержит структуру 310 управления защищенным анклавом (secure enclave control structure (SECS)), область 320 структуры управления потоком (thread control structure (TCS)) и область 330 данных. Хотя на Фиг. 3 показано, что кэш ЕРС 300 разделен на три раздельные области, этот кэш ЕРС 300 может быть разбит на любое число блоков, областей или страниц, каждая из которых может быть использована для контента любого типа. В одном из вариантов кэш ЕРС 300 разделен на страницы по 4 килобайт размером и совмещен в системной памяти 130 с адресами, кратными 4 кбайт, структура SECS 310 может быть какой-либо одной из таких страниц по 4 кбайт в кэше ЕРС 300, область TCS 320 может занимать любое число смежных или несмежных страниц по 4 кбайт, и область 330 данных также может занимать любое число смежных или несмежных страниц по 4 кбайт. Более того, хотя на Фиг. 3 показаны одна структура SECS, одна область TCS и одна область данных, соответствующие одному защищенному анклаву, кэш ЕРС может содержать любое число структур SECS и любое число областей TCS и областей данных при условии, что каждый анклав имеет одну и только одну структуру SECS, каждая действительная область TCS и каждая действительная область данных (например, страница) принадлежит одному и только одному анклаву и что все страницы структур SECS, областей TCS и данных встроены в кэш ЕРС (или могут быть постранично переданы из этого кэша и возвращены назад в кэш ЕРС).

Структура SECS может быть создана посредством выполнения команды ECREATE для хранения метаданных, которые будет использовать аппаратура, и быть доступной только для аппаратуры (т.е. не может быть прочитана, записана или каким-либо иным образом доступна для программного обеспечения, независимо от того, работает ли это программное обеспечение внутри или вне анклава) для формирования, поддержки и защиты анклава. С одним защищенным анклавом могут быть ассоциированы одна или несколько областей TCS. Область TCS содержит метаданные, используемые аппаратурой для сохранения и восстановления информации, специфичной для потоков, при входе в анклав и выходе из него.

Атрибуты безопасности для каждой страницы сохранены в микроархитектурной структуре данных, именуемой карта кэша страниц анклава (enclave page cache map (EPCM)) и используемой модулем 260 управления доступом к памяти для приведения в действие мер зашиты, создаваемых архитектурой защищенных анклавов. Карта ЕРСМ сохраняет только одну входную позицию для каждой страницы в кэше ЕРС. Каждая входная позиция содержит идентификатор (например, поле 64 бит) структуры SECS (т.е. анклава), которой принадлежит страница. К этим идентификаторам могут обращаться команды работы с защищенным анклавом (например, адрес структуры SECS может быть сохранен в регистре, таком как RCX, адрес микроархитектурной структуры данных, содержащей адрес структуры SECS, может быть сохранен в регистре, таком как RBX, и т.п.), чтобы аппаратура могла прочитать структуру SECS для выполнения соответствующей команды.

Каждая входная позиция карты ЕРСМ может также содержать некоторое число битов или полей для определения разрешений на доступ и/или других атрибутов соответствующей страницы. Бит чтения (R-бит) может быть задан для указания, что страницу можно читать изнутри анклава. Бит записи (W-бит) может быть задан для указания, что страницу можно записывать изнутри анклава. Бит исполнения (Х-бит) может быть задан для указания, что страницу можно выполнять изнутри анклава. Бит модификации (М-бит) может быть задан для указания, что разрешение на доступ к памяти или другой атрибут страницы были модифицированы. Поле срока блокирования (blocked-epoch field (ВЕРОСН)) может быть задано для указания срока, когда анклав должен очистить страницу, подлежащую удалению (переносу) из кэша ЕРС.

Фиг. 4 иллюстрирует архитектуру 400, представляющую собой архитектуру системы, содержащей защищенные процессорные среды согласно одному из вариантов настоящего изобретения. В одном из вариантов система 410 содержит анклав 420 и анклав 430, каждый из которых может быть создан посредством вызова и исполнения команды ECREATE. Каждое из приложений 422 и 432 может представлять собой прикладное программное, обеспечение или какой-либо поток, задачу, процесс или другой случай команд, кода или программного обеспечения, загруженных в анклавы 420 и 430, соответственно; каждое из приложений 422 и 432 может быть загружено в анклав посредством вызова и исполнения одной или нескольких команд EADD. Анклавы 420 и 430 могут быть инициализированы посредством вызова и исполнения команды EINIT. Приложения 422 и 432 вошли в анклавы посредством, например, вызова команды EENTER. Поэтому приложения 422 и 432 можно рассматривать как находящиеся в анклавах 420 и 430, соответственно, либо выполняемые или работающие в этих анклавах. Хотя на Фиг. 4 показаны только по одному приложению на каждый анклав, единственное приложение может работать в нескольких (больше одного) анклавах и/или больше одного приложения могут работать в одном анклаве.

Система 410 содержит также несколько операционных систем (каждая обозначена OS), мониторов виртуальных машин (каждый обозначен VMM) или другое управляющее работой системы или привилегированное программное обеспечение, так что каждая из этих программ может работать на одном или нескольких процессорах в системе 410, внутри или вне анклава. Для удобства каждое такое привилегированное программное обеспечение, будь то операционная система (OS), обозначено в настоящем описании как OS 412. Система OS 412 (или какой-либо поток, задача, процесс или другой случай системы OS 412) может работать на уровне привилегий процессора (например, кольцо-0 (ring-0) или режим супервизора), который является более привилегированном, чем уровень привилегий процессора (например, кольцо-3 (ring-3) или режим пользователя), на котором работают приложения 422 и 432.

На Фиг. 4 показана также карта ЕРСМ 440 для сохранения атрибутов безопасности страниц кэша ЕРС из состава анклавов 420 и 430 и две репрезентативные входные позиции 450 и 460 этой карты ЕРСМ 440. Входная позиция 450 содержит бит 452 чтения, бит 454 записи и бит 456 исполнения для определения разрешений на доступ к памяти репрезентативной страницы 424 кэша ЕРС из состава анклава 420 с целью чтения, записи и исполнения этой страницы. Входная позиция 450 содержит также бит 458 модификации для указания состояния модификации разрешений для страницы 424 кэша ЕРС и поле ВЕРОСН 459 для указания срока, когда анклав должен очистить страницу 424, подлежащую удалению из кэша ЕРС 300. Входная позиция 460 содержит бит 462 чтения, бит 464 записи и бит 466 исполнения для определения разрешений на доступ к памяти репрезентативной страницы 434 кэша ЕРС из состава анклава 430 с целью чтения, записи и исполнения этой страницы. Входная позиция 460 содержит также бит 468 модификации для указания состояния модификации разрешений для страницы 434 кэша ЕРС и поле ВЕРОСН 469. для указания срока, когда анклав должен очистить страницу 434, подлежащую удалению из кэша ЕРС 300.

Варианты настоящего изобретения позволяют приложению в анклаве, такому как приложение 422 или 432 использовать команду расширения разрешений на доступ к памяти (например, команду EMODPE) с целью расширения (т.е., чтобы сделать доступ более легким и/или разрешить доступ при большем числе условий) разрешений на доступ к памяти (например, к страницам) в составе анклава или к памяти, выделенной для этого анклава, так что такие расширенные разрешения на доступ к памяти немедленно становятся доступными (действительными) для приложений, работающих в анклаве. В одном из вариантов команда расширения разрешений на доступ к памяти может быть частью («лепестком») непривилегированной команды защищенного анклава (например, ENCLU), так что она может быть вызвана приложением, работающим в анклаве на уровне привилегий процессора (например, кольцо-3 (ring-3)), который является менее привилегированным, чем уровень привилегий процессора (например, кольцо-0 (ring-0)), на котором работает система OS вне анклава. Работа процессора в ответ на команду расширения разрешений на доступ к памяти согласно одному из вариантов настоящего изобретения дополнительно описана ниже при рассмотрении способа 500, показанного на Фиг. 5.

Варианты настоящего изобретения позволяют также приложению в анклаве, такому как приложение 422 или 432 использовать команду ограничения разрешений на доступ к памяти (например, команду EMODPR) с целью ограничения (т.е., чтобы сделать доступ менее легким и/или разрешить доступ при меньшем числе условий) разрешений на доступ к памяти (например, к страницам) в составе анклава или к памяти, выделенной для этого анклава, путем направления системного вызова программному обеспечению системы, такому как система OS 412, для выполнения этой команды EMODPR. В одном из вариантов команда ограничения разрешений на доступ к памяти может быть частью («лепестком») привилегированной команды защищенного анклава (например, ENCLS), так что она может быть вызвана системой OS, монитором VMM или другим системным программным обеспечением, работающим вне анклава на уровне привилегий процессора (например, кольцо-0 (ring-0)), который является более привилегированным, чем уровень привилегий процессора (например, кольцо-3 (ring-3)), на котором работают приложения внутри анклава, но не может быть вызвана приложением непосредственно. Ограниченные разрешения на доступ к памяти становятся действующими сразу же после выполнения команды EMODPR, так что от приложения, сделавшего указанный системный вызов, никакие другие действия не требуются; однако приложение может удостовериться, что ограниченные разрешения на доступ к памяти стали действующими, путем вызова команды ЕАССЕРТ, которая может быть частью («лепестком») команды ENCLU. Работа процессора в ответ на команду ограничения разрешений на доступ к памяти согласно одному из вариантов настоящего изобретения дополнительно описана ниже при рассмотрении способа 600, показанного на Фиг. 6.

Фиг. 5 и 6 иллюстрируют способы 500 и 600 для расширения и ограничения, соответственно, разрешений на доступ к памяти в защищенной процессорной среде согласно одному из вариантов настоящего изобретения. Хотя варианты способов согласно настоящему изобретению не ограничиваются в этом отношении, могут быть сделаны ссылки на элементы, изображенные на Фиг. 1, 2, 3 и 4, с целью помочь описанию вариантов способов, показанных на Фиг. 5 и 6. Кроме того, способы 500 и 600 могут быть описаны и проиллюстрированы, для удобства, с использованием конкретных имен команд, таких как EMODPE, EMODPR и ЕАССЕРТ; однако варианты настоящего изобретения этими конкретно названными командами не ограничиваются.

В блоке 510 способа 500 приложение, такое как приложение 422, работающее в анклаве, таком как анклав 420, на уровне привилегий режима пользователя, вызывает команду EMODPE, чтобы расширить разрешения на доступ к странице, такой как страница 424 в кэше ЕРС 240. Эти разрешения на доступ могут содержать доступ для чтения, доступ для записи, доступ для исполнения и/или какой-либо иной индикатор разрешения, указывающий, каким может быть доступ к рассматриваемой странице. Например, приложение может вызвать команду EMODPE, чтобы изменить атрибуты страницы, обозначенной как «только для чтения», и сделать ее «доступной для чтения-записи». С командой EMODPE могут быть ассоциированы первый операнд для идентификации страницы, например, с использованием линейного или другого адреса, и второй операнд для идентификации новых разрешений. В качестве альтернативы, идентификация страницы и/или новых разрешений или изменений существующих разрешений могут быть указаны каким-либо другим способом.

В блоке 520 процессор, например, процессор 200 начинает реагировать на команду EMODPE. Отклик на эту команду может осуществляться полностью аппаратурой процессора, такой как командный модуль 214 и исполнительный модуль 270, под управлением микрокода или другой управляющей логики из состава модуля управления, такого как модуль 218 управления, без привлечения какой-либо другой команды посредством приложения 422 или другого программного обеспечения. В одном из вариантов процессор выполняет команду EMODPE, только когда эта команда вызвана из режима пользователя.

В блоке 522, в ответ на команду EMODPE процессор изменяет разрешения на доступ к памяти кэша ЕРС для страницы 424, как это указано командой EMODPE. Например, процессор изменяет контент (например, с 0 на 1) одного или нескольких битов разрешения или других индикаторов во входной позиции карты ЕРСМ, соответствующей рассматриваемой странице, таких как R-бит 452, W-бит 454 и/или Х-бит 456 во входной позиции 450 карты ЕРСМ. Более того, процессор изменяет разрешения на доступ к странице таким образом, что новые разрешения сразу же становятся действующими, т.е. без задания или изменения М-бита 458. Поэтому выполнение команды EMODPE отличается от выполнения команды модификации разрешения на доступ к памяти, такой как команда EMOD, в ответ на которую процессор задает М-бит 458, так что страница не может быть доступна до тех пор, пока приложение 422 или другое программное обеспечение не очистит М-бит 458 посредством вызова команды ЕАССЕРТ. Выполнение команды EMODPE также отличается от выполнения команды EMODPR ограничения разрешений на доступ памяти, поскольку поле ВЕРОСН 459 не задают в ответ на команду EMODPE так, как это было бы сделано в ответ на команду EMODPR, что будет описано ниже.

В блоке 524 отклик процессора на команду EMODPE и/или выполнение этой команды завершается, так что процессор откликнулся на команду EMODPE или выполнил эту команду, не сделав при этом рассматриваемую страницу недоступной для приложения 422.

В блоке 530 приложение 422 в анклаве 420 направляет системе OS 412 (или другому привилегированному программному обеспечению, такому как монитор VMM) требование обновить разрешения на доступ к странице 424 для согласования с новыми разрешениями, примененными в блоке 522, например, посредством направления системного вызова для системы OS 412 (или другого привилегированного программного обеспечения, такого как монитор VMM) с целью изменения разрешений для страницы 424 в директории страниц, таблице страниц или другой структуре, через которую осуществляется доступ к странице 424. Отметим, что приложение 422 может продолжать обращаться и получать доступ к странице 424 в соответствии со старыми (более ограничивающими) разрешениями пока система OS 412 (или другое привилегированное программное обеспечение, такое как монитор VMM) не обновит разрешения в таблицах страниц. В блоке 532 система OS 412 (или другое привилегированное программное обеспечение, такое как монитор VMM), работающее вне анклава 420 в режиме супервизора, обновляет разрешения на доступ к странице 424 в таблицах страниц.

В блоке 534 приложение 422 в анклаве 420 предпринимает попытку доступа к странице 424 в соответствии с новыми разрешениями. В блоке 536, если нетранслированный (например, линейный) адрес, по которому приложение 422 пытается обратиться к странице 424, записан в буфере TLB 217, способ 500 переходит к блоку 550. В этом блоке 536, если нетранслированный (например, линейный) адрес, по которому приложение 422 пытается обратиться к странице 424, не записан в буфере TLB 217, способ 500 переходит к блоку 538. В блоке 538 приложение 422 в анклаве 420 успешно обращается и получает доступ к странице 424 в соответствии с новыми разрешениями, не вызывая асинхронного выхода из анклава 420.

В блоке 550 попытка обратиться к странице 424 вызывает асинхронный выход (asynchronous exit (АЕХ)) из анклава 420. В блоке 552 система OS 412 (или другое привилегированное программное обеспечение, такое как монитор VMM), работающая вне анклава 420 в режиме супервизора, обновляет или удаляет соответствующую входную позицию в буфере TLB 217. В блоке 554 система OS 412 (или другое привилегированное программное обеспечение, такое как монитор VMM) перезапускает приложение 422 в анклаве 420. В блоке 556 приложение 422 в анклаве 420 успешно обращается и получает доступ к странице 424 в соответствии с новыми разрешениями.

Согласно способу 600, в блоке 610 приложение, такое как приложение 432, работающее в анклаве, таком как анклав 430, на уровне привилегий режима пользователя, направляет системный вызов в систему OS (или другому привилегированному программному обеспечению, такому как монитор VMM), такую как система OS 412, с целью потребовать от системы OS (или другого привилегированного программного обеспечения, такого как монитор VMM) ограничить разрешения на доступ к памяти, в соответствии-с которыми может быть осуществлен доступ к странице, такой как страница 434, в кэше ЕРС 240. Эти разрешения на доступ могут содержать доступ для чтения, доступ для записи, доступ для исполнения и/или какой-либо иной индикатор разрешения, указывающий, каким может быть доступ к рассматриваемой странице. Например, приложение может направить системный вызов, чтобы изменить атрибуты страницы, обозначенной как «для чтения-записи», и сделать ее доступной «только для чтения».

В блоке 612, в ответ на системный вызов из блока 610, система OS 412 (или другое привилегированное программное обеспечение, такое как монитор VMM), работающая вне анклава 430 в режиме супервизора, вызывает команду EMODPR, чтобы ограничить разрешения на доступ к памяти, в соответствии с которыми может быть осуществлен доступ к странице, такой как страница 434, в кэше ЕРС 240. С командой EMODPR могут быть ассоциированы первый операнд для идентификации страницы, например, с использованием линейного или другого адреса, и второй операнд для идентификации новых разрешений. В качестве альтернативы, идентификация страницы и/или новых разрешений или изменений существующих разрешений могут быть указаны каким-либо другим способом

В блоке 620 процессор, например, процессор 200 начинает реагировать на команду EMODPR. Отклик на эту команду может осуществляться полностью аппаратурой процессора, такой как командный модуль 214 и исполнительный модуль 270, под управлением микрокода или другой управляющей логики из состава модуля управления, такого как модуль 218 управления, без привлечения какой-либо другой команды посредством приложения 432 или другого программного обеспечения. В одном из вариантов процессор выполняет команду EMODPR, только когда эта команда вызвана из режима супервизора.

В блоке 622, в ответ на команду EMODPR процессор изменяет разрешения на доступ к памяти кэша ЕРС для страницы 434, как это указано командой EMODPR. Например, процессор изменяет контент (например, с 0 на 1) одного или нескольких битов разрешения или других индикаторов во входной позиции карты ЕРСМ, соответствующей рассматриваемой странице, таких как R-бит 462, W-бит 464 и/или Х-бит 466 во входной позиции 460 карты ЕРСМ. Более того, процессор изменяет разрешения на доступ к странице таким образом, что новые разрешения сразу же становятся действующими, т.е. без задания или изменения М-бита 468. Поэтому выполнение команды EMODPR отличается от выполнения команды модификации разрешения на доступ к памяти, такой как команда EMOD, в ответ на которую процессор задает М-бит 468, так что страница не может быть доступна до тех пор, пока приложение 432 или другое программное обеспечение не очистит М-бит 468 посредством вызова команды ЕАССЕРТ.

В блоке 624, в ответ на команду EMODPR, процессор задает поле ВЕРОСН 469 для идентификации текущего слова анклава с целью тем самым, как будет описано ниже, отслеживания и удаления входных позиций буфера TLB, утративших силу из-за ограничения разрешений на доступ к памяти. Поэтому приложение 432 может безопасно работать в критичном разделе кода после того, как входные позиции буфера TLB, относящиеся к текущему сроку анклава, были удалены.

В блоке 626 отклик процессора на команду EMODPR и/или выполнение этой команды завершается, так что процессор откликнулся на команду EMODPR или выполнил эту команду, не сделав при этом рассматриваемую страницу недоступной для приложения 432.

В блоке 630 система OS 412 (или другое привилегированное программное обеспечение, такое как монитор VMM) отслеживает потоки анклава, для которых входные позиции буфера TLB утратили силу из-за ограничения разрешений на доступ к памяти, например, посредством вызова команды ETRACK.

В блоке 632 система OS 412 (или другое привилегированное программное обеспечение, такое как монитор VMM) обновляет разрешения на доступ к странице 434 для согласования с новыми разрешениями, примененными в блоке 622, например, посредством изменения разрешений для страницы 434 в директории страниц, таблице страниц или другой структуре, через которую осуществляется доступ к странице 434. Отметим, что приложение 432 может продолжать обращаться и получать доступ к странице 424 в соответствии с новыми (более ограничивающими) разрешениями, примененными в блоке 622 прежде, чем система OS 412 (или другое привилегированное программное обеспечение, такое как монитор VMM) обновит разрешения в таблицах страниц.

В блоке 634 система OS 412 (или другое привилегированное программное обеспечение, такое как монитор VMM) передает команды межпроцессорного прерывания (inter-processor-interrupt (IPI)) для запуска выхода потоков из анклава (т.е. все потоки, использующие страницу 434, покидают анклав 430) и очистку («выключение») буфера TLB. В блоке 636 все такие потоки покинули анклав 430, например, посредством вызова команды EEXIT, очистка буфера TLB приводит к удалению входных позиций буфера TLB, утративших силу из-за ограничения разрешений на доступ к памяти.

В блоке 640 приложение 432 в анклаве 430 удостоверяется, что ограничения разрешений на доступ к памяти были осуществлены, посредством, например, вызова команды ЕАССЕРТ. Отметим, однако, что действия, выполняемые в блоке 640, включая использование команды ЕАССЕРТ, не требуется, чтобы приложение 432 могло обращаться и получать доступ к странице 434 в соответствии с новыми разрешениями. Кроме того, такое удостоверение будет успешным только в том случае, когда все относящиеся к делу потоки покинули анклав, например, в блоке 636.

В блоке 650 приложение 432 в анклаве 430 предпринимает попытку доступа к странице 434 в соответствии с новыми разрешениями. В блоке 652 приложение 432 в анклаве 430 успешно обращается и получает доступ к странице 434 в соответствии с новыми разрешениями, не вызывая асинхронного выхода из анклава 430.

Отметим, что в период времени между обновлением карты ЕРСМ, чтобы отразить новые разрешения на доступ к памяти, (например, блок 522 способа 500 или блок 622 способа 600) и обновлением таблиц страниц, чтобы отразить эти новые разрешения, (например, блок 532 способа 500 или блок 632 способа 600) страница доступна для потока в анклаве, но доступ к этой странице (например, странице 424 или странице 434) ограничен в соответствии с более ограничительными из разрешений, указанных в карте ЕРСМ, и разрешений, указанных в таблице страниц. Поэтому, согласно способу 500, иллюстрирующему команду для расширения разрешений на доступ к памяти, доступ к странице со стороны потока, работающего в анклаве, в этот период времени осуществляется в соответствии со старыми разрешениями, а согласно способу 600, иллюстрирующему команду для ограничения таких разрешений, доступ к странице со стороны потока, работающего в анклаве, в этот период времени осуществляется в соответствии, с новыми разрешениями.

В различных вариантах настоящего изобретения способы, иллюстрируемые на Фиг. 5 и 6, могут осуществляться в другом порядке, так что показанные на этих чертежах блоки могут быть объединены или опущены, а дополнительные блоки добавлены, либо все это в виде сочетания переупорядоченных, объединенных, исключенных или дополнительных блоков. Более того, варианты способов согласно настоящему изобретению не ограничиваются способами 500 и 600 или их вариациями. Многие другие способы (равно как и устройства, системы и другие варианты), не описанные здесь, возможны в рамках объема настоящего изобретения.

Варианты или фрагменты вариантов согласно настоящему изобретению, как описано выше, могут быть записаны на машиночитаемом носителе любого типа. Например, все или часть операций способов 500 и 600 могут быть реализованы в виде команд загружаемого программного обеспечения или встроенного программного обеспечения, записанных на носителе, читаемом посредством процессора 110, и выполняемых процессором 110, вследствие чего процессор 110 осуществляет вариант настоящего изобретения. Кроме того, аспекты настоящего изобретения могут быть выражены в виде данных, записанных на машиночитаемом носителе, где эти данные представляют проектную или иную информацию, используемую при изготовлении всего процессора 110 или его части.

Таким образом, были рассмотрены варианты настоящего изобретения для модификации разрешений на доступ к памяти в защищенной процессорной среде. Хотя некоторые варианты были описаны и показаны на прилагаемых чертежах, следует понимать, что такие варианты являются всего лишь иллюстрациями и не ограничивают широкого изобретения, и что настоящее изобретение не ограничивается конкретными конструкциями и структурами, показанными и описанными здесь, поскольку рядовые специалисты в рассматриваемой области могут найти разнообразные другие модификации после изучения настоящего описания. В такой области техники, как эта, где происходит быстрое развитие, и дальнейшие достижения не так легко предвидеть, рассмотренные варианты могут быть легко модифицированы в целом и в отдельных деталях, насколько это позволят технологические достижения, без отклонения от принципов настоящего изобретения или от объема прилагаемой Формулы изобретения.

Изобретение относится к вычислительной технике. Технический результат заключается в оптимизации модификации разрешений на доступ к защищенному анклаву памяти. Процессор содержит командный модуль для приема первой команды для расширения разрешений на доступ к памяти для страницы в защищенном анклаве и для вызова, посредством приложения изнутри защищенного анклава, операционной системы вне защищенного анклава с целью вызова второй команды для ограничения разрешений на доступ к памяти для страницы; исполнительный модуль для выполнения первой команды и второй команды, в котором выполнение первой команды и второй команды содержит изменение разрешений на доступ к памяти в элементе таблицы отображения кэша страниц анклава, без задания бита модификации в элементе таблицы отображения кэша страниц анклава, в котором выполнение второй команды содержит запись значения срока, когда анклав должен очистить страницу, подлежащую удалению из кэша страницы анклава, в элементе таблицы отображения кэша страниц анклава, и в котором указанная страница сразу же становится доступна изнутри защищенного анклава в соответствии с измененными разрешениями; при этом операционная система предназначена для отслеживания потоков анклава, для запуска выходов потоков анклава и очистки буфера динамической трансляции. 3 н. и 7 з.п. ф-лы, 6 ил.

1. Процессор, содержащий:

командный модуль для приема первой команды и второй команды, при этом первая команда предназначена для расширения разрешений на доступ к памяти для страницы в защищенном анклаве, и вторая команда предназначена для вызова, посредством приложения изнутри защищенного анклава, операционной системы вне защищенного анклава с целью вызова второй команды для ограничения разрешений на доступ к памяти для страницы; и

исполнительный модуль для выполнения первой команды и второй команды, в котором выполнение первой команды и второй команды содержит изменение по меньшей мере одного из чтения, записи и исполнения разрешений на доступ к памяти в элементе таблицы отображения кэша страниц анклава без задания бита модификации в элементе таблицы отображения кэша страниц анклава, в котором выполнение второй команды содержит запись значения срока, когда анклав должен очистить страницу, подлежащую удалению из кэша страницы анклава, в элементе таблицы отображения кэша страниц анклава, и в котором указанная страница сразу же становится доступна изнутри защищенного анклава в соответствии с измененными разрешениями на доступ к памяти; и

буфер динамической трансляции, при этом операционная система предназначена для отслеживания потоков анклава, для которых входные позиции буфера динамической трансляции утратили силу из-за измененных разрешений на доступ к памяти и передачи команд межпроцессорного прерывания для запуска выходов потоков анклава и очистки буфера динамической трансляции.

2. Процессор по п. 1, отличающийся тем, что первая команда может быть выполнена изнутри защищенного анклава.

3. Процессор по п. 2, отличающийся тем, что первая команда может быть выполнена только изнутри защищенного анклава.

4. Процессор по п. 1, отличающийся тем, что первая команда может быть выполнена только в режиме супервизора.

5. Способ динамической модификации разрешений на доступ к защищенной изолированной области памяти, содержащий:

выдачу первой команды процессору для расширения разрешения на доступ к памяти для страницы в защищенном анклаве; и

выполнение, посредством процессора, первой команды, в котором выполнение первой команды содержит изменение по меньше мере одного из чтения, записи и исполнения разрешений на доступ к памяти в элементе таблицы отображения кэша страниц анклава без задания бита модификации в элементе таблицы отображения кэша страниц анклава, и в котором указанная страница сразу же становится доступна изнутри защищенного анклава в соответствии с измененными разрешениями на доступ к памяти;

вызов, посредством приложения изнутри защищенного анклава, операционной системы вне защищенного анклава с целью вызова второй команды для ограничения по меньшей мере одного разрешения на доступ к памяти для страницы;

выдачу второй команды процессору для ограничения по меньшей мере одного разрешения на доступ к памяти для страницы;

выполнение, посредством процессора, второй команды, в котором выполнение второй команды содержит изменение по меньше мере одного из чтения, записи и исполнения разрешений на доступ к памяти в элементе таблицы отображения кэша страниц анклава и запись значения срока, когда анклав должен очистить страницу, подлежащую удалению из кэша страницы анклава, в элементе таблицы отображения кэша страниц анклава, и в котором указанная страница сразу же становится доступна изнутри защищенного анклава в соответствии с измененными разрешениями на доступ к памяти; и

отслеживание, посредством операционной системы, потоков анклава, для которых входные позиции буфера динамической трансляции утратили силу из-за измененных разрешений на доступ к памяти и

передачу, посредством операционной системы, команд межпроцессорного прерывания для запуска выходов потоков анклава и очистки буфера динамической трансляции.

6. Способ по п. 5, дополнительно содержащий:

обращение и получение доступа посредством приложения изнутри защищенного анклава к странице согласно новому разрешению на доступ к памяти, и

обновление, посредством операционной системы извне защищенного анклава, таблиц страниц, чтобы отразить новые разрешения на доступ к памяти.

7. Способ по п. 5, дополнительно содержащий:

попытку со стороны приложения изнутри защищенного анклава получить доступ к рассматриваемой странице после выполнения первой команды;

определение, посредством процессора, что отображение для рассматриваемой страницы существует в буфере динамической трансляции; и

инициирование, посредством процессора, сбоя страницы и асинхронного выхода из защищенного анклава.

8. Способ по п. 7, дополнительно содержащий:

обработку, посредством операционной системы извне защищенного анклава, сбоя страницы; и

перезапуск, посредством операционной системы, приложения в защищенном анклаве.

9. Способ по п. 5, дополнительно содержащий удостоверение, посредством приложения изнутри защищенного анклава, что новые разрешения на доступ к памяти были заданы.

10. Система динамической модификации разрешений на доступ к защищенной изолированной области памяти, содержащая:

память;

процессор, имеющий

командный модуль для приема первой команды и второй команды, при этом первая команда предназначена для расширения разрешений на доступ к памяти для страницы в защищенном анклаве и вторая команда предназначена для вызова, посредством приложения изнутри защищенного анклава, операционной системы вне защищенного анклава с целью вызова второй команды для ограничения разрешений на доступ к памяти для страницы; и

исполнительный модуль для выполнения первой команды и второй команды, в котором выполнение первой команды и второй команды содержит изменение по меньшей мере одного из чтения, записи и исполнения разрешений на доступ к памяти в элементе таблицы отображения кэша страниц анклава без задания бита модификации в элементе таблицы отображения кэша страниц анклава, в котором выполнение второй команды содержит запись значения срока значения срока, когда анклав должен очистить страницу, подлежащую удалению из кэша страницы анклава, в элементе таблицы отображения кэша страниц анклава, и в котором указанная страница сразу же становится доступна изнутри защищенного анклава в соответствии с измененными разрешениями на доступ к памяти; и

буфер динамической трансляции, при этом операционная система предназначена для отслеживания потоков анклава, для которых входные позиции буфера динамической трансляции утратили силу из-за измененных разрешений на доступ к памяти и передачи команд межпроцессорного прерывания для запуска выходов потоков анклава и очистки буфера динамической трансляции.

| Изложница с суживающимся книзу сечением и с вертикально перемещающимся днищем | 1924 |

|

SU2012A1 |

| Способ приготовления лака | 1924 |

|

SU2011A1 |

| Изложница с суживающимся книзу сечением и с вертикально перемещающимся днищем | 1924 |

|

SU2012A1 |

| Станок для изготовления деревянных ниточных катушек из цилиндрических, снабженных осевым отверстием, заготовок | 1923 |

|

SU2008A1 |

| Изложница с суживающимся книзу сечением и с вертикально перемещающимся днищем | 1924 |

|

SU2012A1 |

| УПРАВЛЕНИЕ ПАМЯТЬЮ ДЛЯ ВЫСОКОСКОРОСТНОГО УПРАВЛЕНИЯ ДОСТУПОМ К СРЕДЕ | 2007 |

|

RU2491737C2 |

Авторы

Даты

2016-11-20—Публикация

2014-11-27—Подача