Изобретение относится к области вычислительной техники, в частности к коммуникационным сетевым устройствам.

Известен сетевой адаптер, использующий специальный подход VELO. Данный подход в первую очередь ориентирован на соединения сетевого адаптера с процессором с помощью шины HyperTransport или PCIe (Heiner Litz, Holger Froning, Mondrian Nussle, Ulrich Bruning, "VELO: A Novel Communication Engine for Ultra-low Latency Message Transfers'7/3 7th INTERNATIONAL CONFERENCE ON PARALLEL PROCESSING (ICPP-08), September 08-12, 2008, Portland, Oregon, USA; Holger Froning, Mondrian Nussle, Heiner Litz, Christian Leber and Ulrich Briining, "On Achieving High Message Rates" // 13th IEEE/ACM International Symposium on Cluster, Cloud and Grid Computing (CCGrid), May 13-16, 2013, Delft, The Netherlands). Для передачи сообщений используется механизм VELO, в котором размер и получатель сообщения кодируются в адресе пакета формата HyperTransport или PCIe. Это позволяет уменьшить размер передаваемых данных. С другой стороны, процессор инициирует передачу данных размером, равным ровно размеру пакета. Если размер пакета не кратен 64 и в короткий промежуток времени посылается только одно сообщение данного размера, то механизм Write Combining в процессоре не срабатывает, и по шине PCIe идут пакеты размером 8 байтов, что происходит очень неэффективно из-за особенностей организации шине PCIe, которая оптимизирована для передачи пакетов размером, кратным 64.

Известен модуль передачи данных между процессором и сетевым адаптером в сети InfmiBand (US 20130103777 (A1), опубл. 25.04.2013, МПК G06F 15/167). Согласно изобретению модуль передачи данных между процессором и сетевым адаптером в сети использует очередь на кольцевом буфере. При этом необходима отдельная передача указателя на конец очереди после записи сообщения для уведомления процессора о факте поступления сообщения, что снижает общую скорость передачи данных. Кроме того, в охранном документе не указывается размер PCIe пакетов, что позволяет предположить, что используются пакеты PCIe неоптимального размера.

Задачей изобретения является создание высокоскоростного сетевого адаптера для обмена сообщениями с процессором вычислительного узла по шине PCIe.

Техническим результатом является увеличение реальной пропускной способности и уменьшение задержки при обмене сообщениями размером от 56 до 248 байтов по шине PCIe между сетевым адаптером и процессором вычислительного узла.

Технический результат достигается тем, что сетевой адаптер включает основную ПЛИС, разъем PCIe, разъемы QSFP+, синтезатор частот, кварцевый резонатор и микроконтроллер, предназначенный для конфигурирования синтезатора частот, постоянное запоминающее устройство, предназначенное для конфигурирования основной ПЛИС после включения питания сетевого адаптера, и вспомогательную ПЛИС, предназначенную для управления таким конфигурированием, кварцевый генератор, предназначенный для формирования для вспомогательной ПЛИС тактовой частоты, разъем питания для видеокарт, к которому подключены преобразователи напряжения. При этом ПЛИС включает маршрутизатор, первые и вторые входные каналы которого соединены соответственно с выходными каналами инжекторов, предназначенных для приема PCIe-пакетов от процессора и формирования из них сообщений, и выходными каналами приемопередатчиков, предназначенных для обмена сообщениями с такими же сетевыми адаптерами других вычислительных узлов; первый и второй выходные каналы маршрутизатора соединены с входными каналами эжекторов, предназначенных для приема сообщений и формирования из них PCIe-пакетов, и входными каналами приемопередатчиков, при этом к шине PCIe через встроенные трансиверы основной ПЛИС и мультиплексоры и демультиплексоры подключены выходные каналы эжекторов и входные каналы инжекторов соответственно, а также входной и выходной канал модуля управления, предназначенный для управления и мониторинга компонентами устройства, реализованного в основной ПЛИС, а к разъемам QSFP+ через встроенные трансиверы основной ПЛИС подключены входные и выходные каналы приемопередатчиков. При этом инжектор включает приемник PCIe-пакетов от процессора, буфер инжекции, представляющий собой кольцевой буфер, и генератор сообщений, причем входом приемника PCIe-пакетов является входной канал инжектора, а выходом генератора сообщений является выходной канал инжектора, вход буфера инжекции соединен с выходом приемника PCIe-пакетов, а выход буфера инжекции соединен с входом генератора сообщений. Эжектор включает приемник сообщений от маршрутизатора, генератор заголовка PCIe-пакета, генератор тела PCIe-пакета, генератор PCIe-пакетов, причем входом приемника сообщения является вход эжектора, вход генератора заголовка PCIe-пакета соединен с выходом приемника сообщений, входы генератора тела PCIe-пакета соединены с выходами генератора заголовка PCIe-пакета и приемника сообщения, входы генератора PCIe-пакетов соединены с выходами генератора заголовка PCIe-пакета и генератора тела PCIe-пакета, отличающийся тем, что буфер инжекции дополнительно предназначен для учета заполнения ячеек кольцевого буфера, а генератор сообщений дополнительно предназначен для извлечения заголовка сообщения из начала ячейки буфера инжекции, в которой располагается начало сообщения, и удаления добавленных процессором произвольных данных, а генератор заголовка PCIe-пакета предназначен для вычисления бита четности, вычисления размера PCIe-пакета, кратного 64, и адреса PCI-пакета, составляющего в сумме с размером PCI-пакета величину, кратную 256, а генератор тела PCIe-пакета предназначен для размещения полезных данных в начало тела PCIe-пакета, заголовка сообщения в конец тела PCIe-пакета и помещения между ними не более 63 байтов неиспользуемых данных.

При этом возможно, что преобразователи напряжения подключены к напряжению питания на шине PCIe.

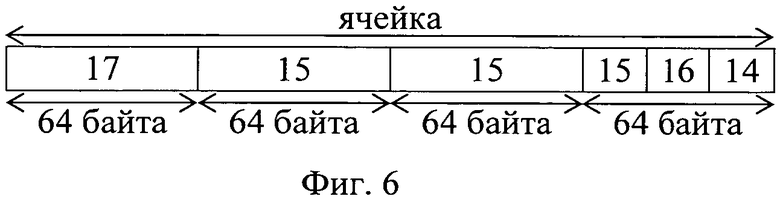

На фиг. 1 показана схема сетевого адаптера.

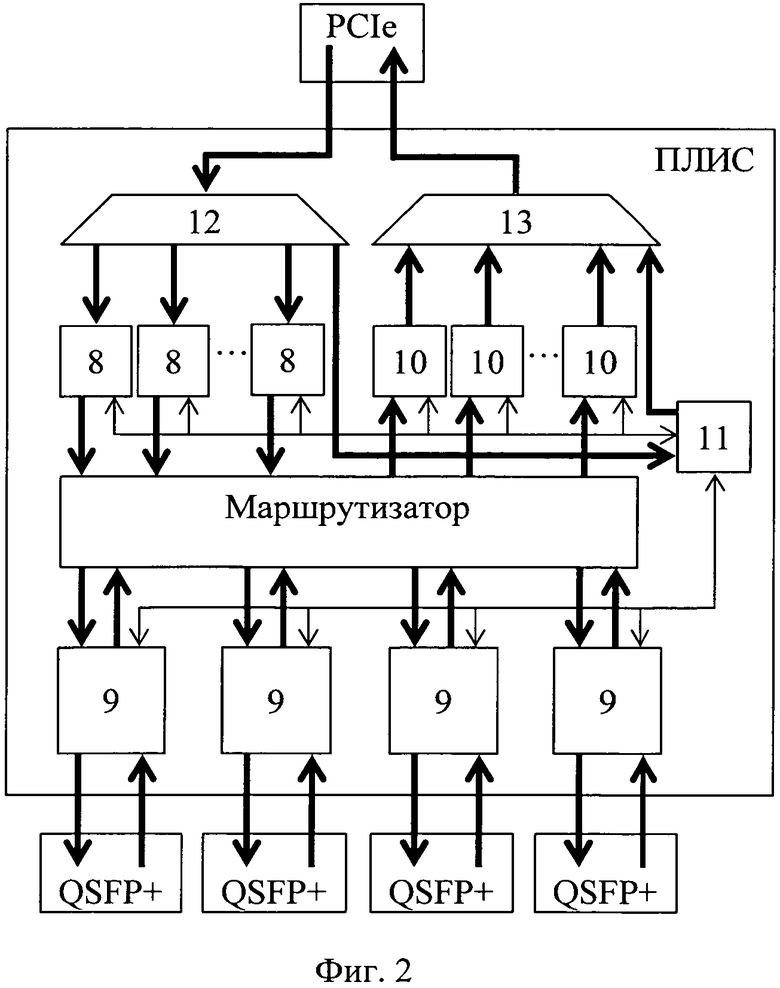

На фиг. 2 показана схема основной ПЛИС.

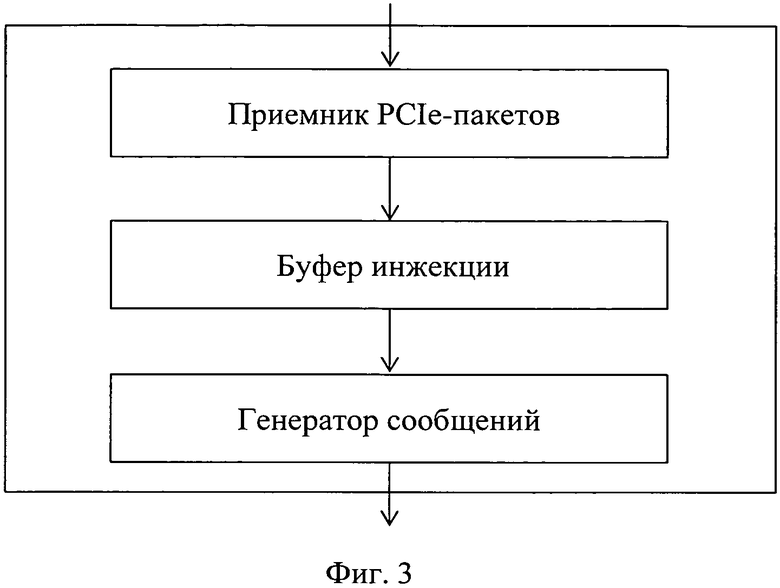

На фиг. 3 показана схема инжектора.

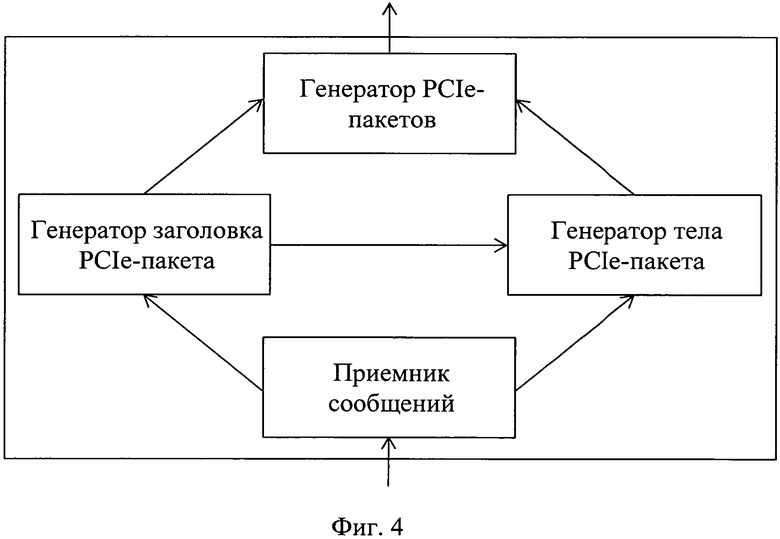

На фиг. 4 показана схема эжектора.

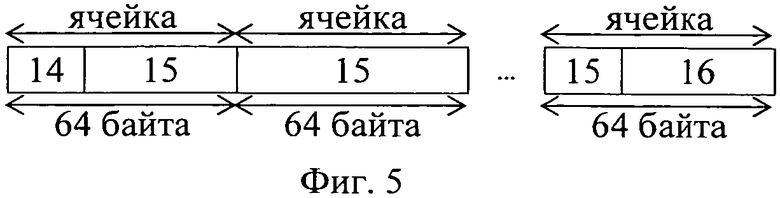

На фиг. 5 показан формат сообщения в буфере инжекции.

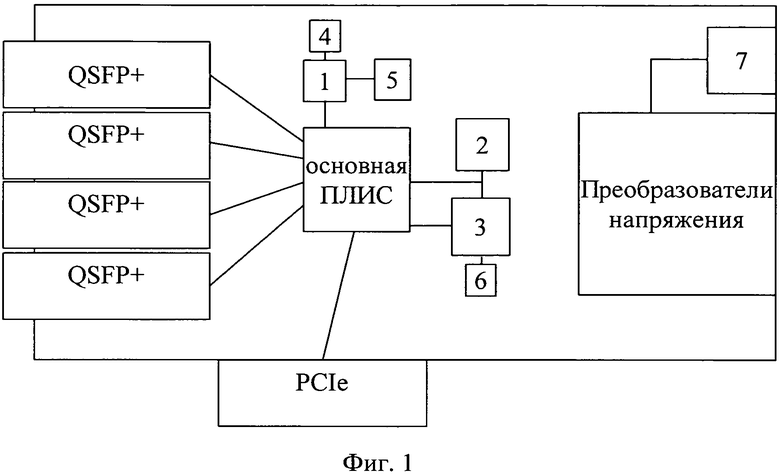

На фиг. 6 показан формат сообщения в кольцевом буфере в системной оперативной памяти.

Основным элементом сетевого адаптера является смонтированная на печатной плате основная ПЛИС со встроенными трансиверами (на чертеже не показаны). Восемь таких трансиверов используются для подключения к шине PCIe, посредством которой сетевой адаптер взаимодействует с процессором вычислительного узла. Передача данных между основной ПЛИС и разъемом PCIe осуществляется по дифференциальным полосковым линиям с волновым сопротивлением 100 Ом по стандарту LVDS.

На печатной плате размещены четыре разъема QSFP+, предназначенные для обмена данными с такими же сетевыми адаптерами, установленными в других вычислительных узлах, через активные оптические кабели. Каждый разъем QSFP+ подключен к четырем встроенным трансиверам основной ПЛИС по дифференциальным полосковым линиям с волновым сопротивлением 100 Ом по стандарту LVDS.

К основной ПЛИС посредством дифференциальных полосковых линий с волновым сопротивлением 100 Ом по стандарту LVDS подключены синтезатор частот 1, генерирующий опорные частоты, используемые основной ПЛИС для тактирования трансиверов, и постоянные запоминающие устройства NAND Flash 2, количество которых может варьироваться. Постоянные запоминающие устройства NAND Flash 2 подключены к основной ПЛИС посредством параллельной шины шириной 32 бита и предназначены для ее конфигурирования после включения питания сетевого адаптера. К постоянным запоминающим устройствам NAND Flash и основной ПЛИС по параллельной шине также подключена вспомогательная ПЛИС 3, предназначенная для управления таким конфигурированием.

Синтезатор частот 1 соединен с кварцевым резонатором 4, предназначенным для генерации опорной частоты сигнала, и микроконтроллером 5, предназначенным для его конфигурирования, посредством шины I2C.

К вспомогательной ПЛИС подключен кварцевый генератор 50 МГц 6, предназначенный для формирования для нее тактовой частоты.

Питание сетевого адаптера осуществляется от внешнего источника питания 12 В через разъем питания для видеокарт 7 или от напряжения питания 12 В на шине PCIe. К разъему питания для видеокарт 7 или к напряжению питания на шине PCIe соответственно подключены преобразователи напряжения, которые формируют необходимые для питания компонентов сетевого адаптера уровни напряжения: 0,9 В; 1,05 В; 1,5 В; 1,8 В; 2,5 В; 3,0 В; 3,3 В. От преобразователей напряжения питание подается к компонентам сетевого адаптера по печатным проводникам.

Основная ПЛИС включает маршрутизатор, первый и второй входные каналы которого соединены соответственно с выходными каналами одного или более инжекторов 8 и выходными каналами приемопередатчиков 9. Первый и второй выходные каналы маршрутизатора соединены с входными каналами одного или более эжекторов 10 и входными каналами приемопередатчиков 9. Таким образом, между маршрутизатором и приемопередатчиками 9 организован двунаправленный поток сообщений.

Приемопередатчики 9 предназначены для обмена сообщениями с такими же сетевыми адаптерами других вычислительных узлов. Инжекторы 8 предназначены для формирования сообщений и передачи их от процессора к сетевому адаптеру, а эжекторы 10 предназначены для формирования PCIe-пакетов и передачи их от сетевого адаптера к процессору.

Модуль управления 11 предназначен для управления и мониторинга компонентов основной ПЛИС посредством выделенных каналов управления (на фиг. 2 показаны тонкими стрелками).

Входные каналы инжекторов 8 и входной канал модуля управления 11 подсоединены к шине PCIe через демультиплексоры 12 и встроенные трансиверы основной ПЛИС. Выходные каналы эжекторов 10 и выходной канал модуля управления 11 подсоединены к шине PCIe через мультиплексоры 13 и встроенные трансиверы основной ПЛИС.

Инжектор 8 включает буфер инжекции, предназначенный для временного хранения данных и представляющий собой кольцевой буфер с размером ячейки 64 байта, который размещен во внутренней памяти основной ПЛИС. Вход буфера инжекции соединен с выходом приемника PCIe-пакетов, а его выход соединен с входом генератора сообщений, который предназначен для формирования сообщений с удалением добавленных процессором вычислительного узла неиспользуемых данных. Входом приемника PCIe-пакетов является входной канал инжектора 8, а выходом генератора сообщений является выходной канал инжектора.

В системной оперативной памяти организованы кольцевые буферы с размером ячейки 256 байтов, предназначенные для использования эжекторами 10 - по одному кольцевому буферу на каждый эжектор.

Эжектор 10 включает генератор тела PCIe-пакета, предназначенный для формирования тела PCIe-пакета посредством объединения полезных данных, неиспользуемых данных и заголовка сообщения с помещенным в него битом четности. Бит четности обозначает четность номера прохода по кольцевому буферу в системной оперативной памяти и служит для уведомления процессора о факте поступления сообщения. Первый вход генератора тела PCIe-пакета соединен с первым выходом приемника сообщений, предназначенного для приема сообщений из маршрутизатора, второй вход соединен с первым выходом генератора заголовка PCIe-пакета, а его выход соединен с первым входом генератора PCIe-пакетов, предназначенного для формирования PCIe-пакета из заголовка PCIe-пакета и тела PCIe-пакета. Второй выход генератора заголовка PCIe-пакета соединен со вторым входом генератора PCIe-пакетов, а его вход соединен с приемником сообщений. Входом приемника сообщений является входной канал эжектора 10, а выходом генератора PCIe-пакетов является выходной канал эжектора.

Генератор заголовка PCIe-пакета предназначен для вычисления бита четности и формирования заголовка PCIe-пакета на основе вычисляемых им размера и адреса PCIe-пакета.

Сетевой адаптер работает следующим образом. При включении питания сетевого адаптера основная ПЛИС конфигурируется под управлением вспомогательной ПЛИС при помощи постоянных запоминающих устройств NAND Flash 2. Во время загрузки BIOS вычислительного узла задает адреса, по которым процессор вычислительного узла обращается к управляющему модулю 11 и инжектору 9 для осуществления записи данных в буфер инжекции. При загрузке операционная система вычислительного узла выделяет в системной оперативной памяти один сегмент для всех кольцевых буферов, предназначенных для использования эжекторами, и сообщает начальный адрес и размер такого сегмента системной оперативной памяти модулю управления 11. Модуль управления 11 по адресу и размеру сегмента вычисляет адрес начала каждого кольцевого буфера в системной оперативной памяти и его размер и передает эти данные в генератор заголовка PCIe-пакета.

В приемник PCIe-пакетов через демультиплексор попадают PCIe-пакеты, сформированные процессором следующим образом. Если размер полезных данных составлял не более 56 байтов, сформирован один PCIe-пакет размером 64 байта, в теле которого сначала расположен заголовок сообщения, затем - полезные данные, и в конце - неиспользуемые данные, дополняющие тело PCIe-пакета до 64 байтов. Если размер полезных данных составлял более 56 байтов, но не более 248 байтов, то для них сформировано несколько PCIe-пакетов размером по 64 байта каждый. Причем в теле первого PCIe-пакета расположены сначала заголовок сообщения, а затем полезные данные. В теле последнего PCIe-пакета расположены сначала полезные данные, затем - неиспользуемые данные, дополняющие его до 64 байтов. Тела остальных PCIe-пакетов включают полезные данные.

Приемник PCIe-пакетов выделяет тело и адрес PCIe-пакета. Если адрес PCIe-пакета соответствует данному инжектору, то тело PCIe-пакета записывается в буфер инжекции.

В процессе записи данных в ячейки буфер инжекции ведет учет заполнения каждой из ячеек, помечая в какую из них записываются данные.

Генератор сообщений последовательно анализирует заполненность ячеек кольцевого буфера инжектора. Когда он обнаруживает, что ячейка кольцевого буфера инжектора, содержащая начало сообщения, полностью заполнена, то он извлекает из ее начала заголовок сообщения 14. Из заголовка сообщения генератор сообщений выделяет размер сообщения, вычисляет необходимое для формирования сообщения количество заполненных ячеек и ожидает заполнения всех этих ячеек. Формат заполнения сообщением ячеек буфера инжекции представлен на фиг. 5.

Когда все необходимые ячейки буфера инжекции заполнятся, генератор сообщений извлекает из них полезные данные 15 и формирует сообщение из заголовка сообщения и полезных данных. Таким образом, из сообщения, сформированного процессором, исключаются неиспользуемые данные 16. Затем сообщение передается в маршрутизатор.

Ведение учета заполнения ячеек кольцевого буфера инжектора позволяет инжектору быть толерантным к нарушению порядка приходящих PCIe-пакетов и не ожидать никаких дополнительных PCIe-пакетов, кроме PCIe-пакетов с полезными данными и заголовком.

Маршрутизатор определяет номер выходного канала по заголовку входящего сообщения. В зависимости от того, в какой выходной канал маршрутизатором было направлено сообщение, оно попадает в эжектор и затем в процессор, или в приемопередатчик 9 и далее в сетевой адаптер другого вычислительного узла.

Приемник сообщений принимает сообщения от маршрутизатора и направляет их в генератор тела PCIe-пакета. Заголовки сообщений приемник сообщений направляет в генератор заголовка PCIe-пакета.

Генератор заголовка PCIe-пакета управляет доступом к кольцевому буферу в системной оперативной памяти. Кольцевой буфер разбит на ячейки по 256 байтов. Каждая ячейка предназначена для одного сообщения. Формат ячейки представлен на фиг. 6.

Получив заголовок сообщения, генератор заголовка PCIe-пакета определяет свободную ячейку в кольцевом буфере в системной оперативной памяти, вычисляет ее адрес и бит четности. По размеру сообщения генератор заголовка PCIe-пакета вычисляет адрес и размер PCIe-пакета. Если размер полезных данных 15 не более 56 байтов, то адрес PCIe-пакета равен адресу ячейки плюс 192 байта, а размер PCIe-пакета - 64 байта. Если размер полезных данных более 56 байтов, но не более 120 байтов, то адрес PCIe-пакета равен адресу ячейки плюс 128 байтов, а размер PCIe-пакета - 128 байтов. Если размер полезных данных более 120 байтов, но не более 184 байтов, то адрес PCIe-пакета равен адресу ячейки плюс 64 байта, а размер PCIe-пакета - 192 байта. Если размер полезных данных более 184 байтов, но не более 248 байтов, то адрес PCIe-пакета равен адресу ячейки, а размер PCIe-пакета - 256 байтов. Таким образом, если размер сообщения не более 184 байтов, то левая часть ячейки 17 остается незаполненной. По адресу и размеру PCIe-пакета генератор заголовка PCIe-пакета формирует заголовок PCIe-пакета и отправляет его в генератор PCIe-пакетов. Размер PCIe-пакета и бит четности генератор заголовка PCIe-пакета отправляет в генератор тела PCIe-пакета.

Генератор тела PCIe-пакетов, получив размер PCIe-пакета, сообщение и бит четности, формирует тело PCIe-пакета следующим образом: в начало тела PCIe-пакета помещает полезные данные 15 сообщения, а в конец - заголовок 14 сообщения, предварительно добавив в него бит четности. Оставшийся промежуток между полезными данными и заголовком сообщения он заполняет неиспользуемыми данными 16. Сформированное таким образом тело PCIe-пакета генератор тела PCIe-пакета отправляет генератору PCIe-пакета.

Генератор PCIe-пакета, получив заголовок PCIe-пакета и тело PCIe-пакета, формирует PCIe-пакет и отправляет его в процессор вычислительного узла.

Таким образом, на каждое сообщение эжектор 10 формирует один PCIe-пакет размером 64-256 байтов в зависимости от размера сообщения, причем размер PCIe-пакета всегда кратен 64. Он включает полезные данные, неиспользуемые данные и заголовок сообщения, содержащий бит четности. При этом заголовок сообщения помещается в конце ячейки кольцевого буфера в системной оперативной памяти. Благодаря этому заголовок сообщения, во-первых, всегда располагается в известном месте ячейки, и, во-вторых, приходит процессору гарантированно позднее, чем полезные данные. Чтобы определить факт прихода сообщения, процессору достаточно прочитать конец ячейки кольцевого буфера, где располагается заголовок сообщения, и проверить значение бита четности.

Технический результат достигается благодаря минимизации количества передаваемых PCIe-пакетов для одного сообщения и использования всей пропускной способности шины PCIe. Это осуществляется, во-первых, за счет отсутствия дополнительных PCIe-пакетов для уведомления процессора о факте поступления сообщения, а во-вторых, за счет того, что передаются PCIe-пакеты оптимального размера, а именно кратного 64 и находящегося в диапазоне 64-256 байтов.

Помещение заголовка сообщения, содержащего бит четности, в конец PCIe-пакета при передаче его от сетевого адаптера в процессор позволяет процессору обнаружить приход сообщения в системную оперативную память сразу после прихода PCIe-пакета.

Дополнение PCIe-пакета, передаваемого от сетевого адаптера к процессору, соответствующим наименьшим количеством неиспользуемых данных так, чтобы его размер стал кратен 64, и удаление неиспользуемых данных из PCIe-пакета, следующего в обратном направлении, позволяет задействовать максимально возможную пропускную способность шины PCIe, поскольку пакеты такого размера по ней передаются более эффективно, чем пакеты другого размера. При этом передается наименьшее возможное количество PCIe-пакетов на одно сообщение. При передаче из сетевого адаптера в процессор используется ровно один PCIe-пакет на сообщение, а при передаче из процессора в сетевой адаптер используются только самые большие по размеру PCIe-пакеты - 64 байта, PCIe-пакеты размером больше 64 байтов процессор послать не может.

| название | год | авторы | номер документа |

|---|---|---|---|

| МУЛЬТИСЕРВИСНЫЙ ТЕЛЕКОММУНИКАЦИОННЫЙ КОМПЛЕКС | 2023 |

|

RU2833335C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ОБЕСПЕЧЕНИЯ ПОТОКОВ НА ОСНОВЕ ИДЕНТИФИКАТОРА ЧЕРЕЗ ШИНУ PCI EXPRESS | 2010 |

|

RU2509348C2 |

| УСОВЕРШЕНСТВОВАНИЕ ИНТЕРФЕЙСА PCI EXPRESS | 2013 |

|

RU2645288C2 |

| СПОСОБ ЗАЩИТЫ ВЫЧИСЛИТЕЛЬНЫХ СЕТЕЙ | 2018 |

|

RU2680038C1 |

| СПОСОБ ИЗОЛЯЦИИ ПАКЕТОВ ДАННЫХ, ПЕРЕДАВАЕМЫХ ПО СЕТЯМ ОБЩЕГО ПОЛЬЗОВАНИЯ В ФОРМАТЕ ПРОТОКОЛОВ СЕМЕЙСТВА TCP/IP, С ПОМОЩЬЮ КОМБИНАЦИИ СПОСОБОВ МАСКИРОВАНИЯ, ШИФРОВАНИЯ И КОНТРОЛЯ ПОЛУЧАЕМЫХ ДАННЫХ | 2021 |

|

RU2762157C1 |

| СИСТЕМА УПРАВЛЕНИЯ СВЯЗЬЮ, КОММУТАЦИОННЫЙ УЗЕЛ И СПОСОБ УПРАВЛЕНИЯ СВЯЗЬЮ | 2012 |

|

RU2584449C2 |

| СПОСОБ ЗАЩИТЫ ВЫЧИСЛИТЕЛЬНЫХ СЕТЕЙ | 2018 |

|

RU2690749C1 |

| МУЛЬТИСЕРВИСНЫЙ МАРШРУТИЗАТОР | 2019 |

|

RU2710980C1 |

| Способ обеспечения идентичности балансировки для двунаправленного потока данных сетевой сессии | 2022 |

|

RU2786629C1 |

| СПОСОБ ЗАЩИТЫ ВЫЧИСЛИТЕЛЬНЫХ СЕТЕЙ | 2018 |

|

RU2686023C1 |

Изобретение относится к коммуникационным сетевым устройствам. Техническим результатом является увеличение реальной пропускной способности и уменьшение задержки при обмене сообщениями размером от 56 до 248 байтов по шине PCIe между сетевым адаптером и процессором вычислительного узла. Сетевой адаптер включает ПЛИС, разъемы PCIe и QSFP+. ПЛИС включает инжекторы, предназначенные для приема PCIe-пакетов от процессора и формирования из них сообщений, эжекторы, предназначенные для приема сообщений и формирования из них PCIe-пакетов, маршрутизатор и приемопередатчики. Инжектор записывает поступающие PCIe-пакеты в кольцевой буфер, где ведется учет заполнения ячеек. Когда ячейка, содержащая заголовок сообщения и начало полезных данных, и все остальные ячейки, необходимые для формирования сообщения, полностью заполнены, инжектор извлекает из этих ячеек заголовок сообщения и полезные данные и формирует сообщение. Эжектор на каждое полученное сообщение формирует один PCIe-пакет размером 64-256 байтов в зависимости от размера сообщения, размер PCIe-пакета кратен 64. Он включает полезные данные, неиспользуемые данные и заголовок сообщения, содержащий бит четности. Заголовок сообщения всегда располагается в известном месте и приходит процессору гарантированно позднее, чем полезные данные. 1 з.п. ф-лы, 6 ил.

1. Сетевой адаптер, включающий основную ПЛИС, разъем PCIe, разъемы QSFP+, синтезатор частот, кварцевый резонатор и микроконтроллер, предназначенный для конфигурирования синтезатора частот, постоянное запоминающее устройство, предназначенное для конфигурирования основной ПЛИС после включения питания сетевого адаптера, и вспомогательную ПЛИС, предназначенную для управления таким конфигурированием, кварцевый генератор, предназначенный для формирования для вспомогательной ПЛИС тактовой частоты, разъем питания для видеокарт, к которому подключены преобразователи напряжения; при этом основная ПЛИС включает маршрутизатор, первые и вторые входные каналы которого соединены соответственно с выходными каналами инжекторов, предназначенных для приема PCIe-пакетов от процессора и формирования из них сообщений, и выходными каналами приемопередатчиков, предназначенных для обмена сообщениями с такими же сетевыми адаптерами других вычислительных узлов; где первый и второй выходные каналы маршрутизатора соединены с входными каналами эжекторов, предназначенных для приема сообщений и формирования из них PCIe-пакетов, и входными каналами приемопередатчиков, при этом к шине PCIe через встроенные трансиверы основной ПЛИС и мультиплексоры и демультиплексоры подключены выходные каналы эжекторов и входные каналы инжекторов соответственно, а также входной и выходной канал модуля управления, предназначенный для управления и мониторинга компонентов основной ПЛИС, а к разъемам QSFP+ через встроенные трансиверы основной ПЛИС подключены входные и выходные каналы приемопередатчиков; при этом инжектор включает приемник PCIe-пакетов от процессора, буфер инжекции, представляющий собой кольцевой буфер, и генератор сообщений, причем входом приемника PCIe-пакетов является входной канал инжектора, а выходом генератора сообщений является выходной канал инжектора, вход буфера инжекции соединен с выходом приемника PCIe-пакетов, а выход буфера инжекции соединен с входом генератора сообщений; а эжектор включает приемник сообщений от маршрутизатора, генератор заголовка PCIe-пакета, генератор тела PCIe-пакета, генератор PCIe-пакетов, причем входом приемника сообщений является вход эжектора, вход генератора заголовка PCIe-пакета соединен с выходом приемника сообщений, входы генератора тела PCIe-пакета соединены с выходами генератора заголовка PCIe-пакета и приемника сообщений, входы генератора PCIe-пакетов соединены с выходами генератора заголовка PCIe-пакета и генератора тела PCIe-пакета, отличающийся тем, что буфер инжекции дополнительно предназначен для учета заполнения ячеек кольцевого буфера, а генератор сообщений дополнительно предназначен для извлечения заголовка сообщения из начала ячейки буфера инжекции, в которой располагается начало сообщения, и удаления добавленных процессором неиспользуемых данных, а генератор заголовка PCIe-пакета предназначен для вычисления бита четности, вычисления размера PCIe-пакета, кратного 64, и адреса PCI-пакета, составляющего в сумме с размером PCI-пакета величину, кратную 256, а генератор тела PCIe-пакета предназначен для размещения полезных данных в начало тела PCIe-пакета, размещения заголовка сообщения в конец тела PCIe-пакета и помещения между ними не более 63 байтов неиспользуемых данных.

2. Сетевой адаптер по п. 1, отличающийся тем, что преобразователи напряжения подключены к напряжению питания на шине PCIe.

| Многоступенчатая активно-реактивная турбина | 1924 |

|

SU2013A1 |

| US 5983305 A, 09.11.1999 | |||

| US 7269153 B1, 11.09.2007 | |||

| Предохранительное устройство от выдергивания путевых костылей | 1938 |

|

SU54476A1 |

| Сплав на медной основе | 1947 |

|

SU73576A1 |

Авторы

Даты

2016-02-10—Публикация

2014-10-15—Подача