Область техники, к которой относится изобретение

Данное изобретение относится к области взаимных соединений и, в частности, к обеспечению потоков на основе идентификатора через шину PCI Express.

Уровень техники

Компьютерные системы включают в себя множество компонентов и элементов. Часто компоненты соединены через шину или взаимное соединение. Ранее устройства ввода-вывода (I/O) соединяли вместе через обычную архитектуру моноканальной параллельной шины, называемую межсоединением периферийных компонентов (PCI). Совсем недавно стали использовать новое поколение I/O шины, называемой PCI Express (PCIe), для обеспечения более быстрого взаимного соединения между устройствами, использующими последовательный протокол передачи данных на физическом уровне.

Архитектура PCIE включает в себя многоуровневый протокол, предназначенный для передачи данных между устройствами. Например, уровень малой передачи данных на физическом уровне и уровень транзакции формируют стек протокола PCIE.

Канал передачи данных PCIe построен вокруг специализированных однонаправленных пар последовательных соединений из точки в точку, называемых дорожкой. Канал передачи данных между устройствами включает в себя некоторое количество дорожек, например одну, две, шестнадцать, тридцать две и так далее. Современная спецификация PCIE base spec 2.0 доступна по адресу<>.

Удобные правила упорядочения PCIe были сформулированы для обеспечения модели программирования производитель-потребитель. В соответствии с этой моделью считывание из определенного устройства требуется для проталкивания записей, которые были сгенерированы перед ними. Такая модель программирования обеспечивает то, что при считывании из места расположения X в запоминающем устройстве всегда получают самые последние данные, которые были записаны в данном местоположении в запоминающем устройстве.

Однако такие требования упорядочения приводят к тому, что один поток запроса (последовательность транзакций считывания или записи, которые имеют одно и то же запрашивающее устройство и одно и то же место назначения) мешают другим независимым потоком запросов. Такие взаимные помехи могут привести к образованию существенных узких мест, снижающих общие характеристики. Данная проблема особенно остро проявляется, если не отправленные запросы будут блокированы после отправленных запросов, поскольку запросы на считывание являются чувствительными к задержке.

Краткое описание чертежей

Настоящее изобретение представлено в качестве примера и не предназначено для ограничения чертежами, показанными на приложенных чертежах.

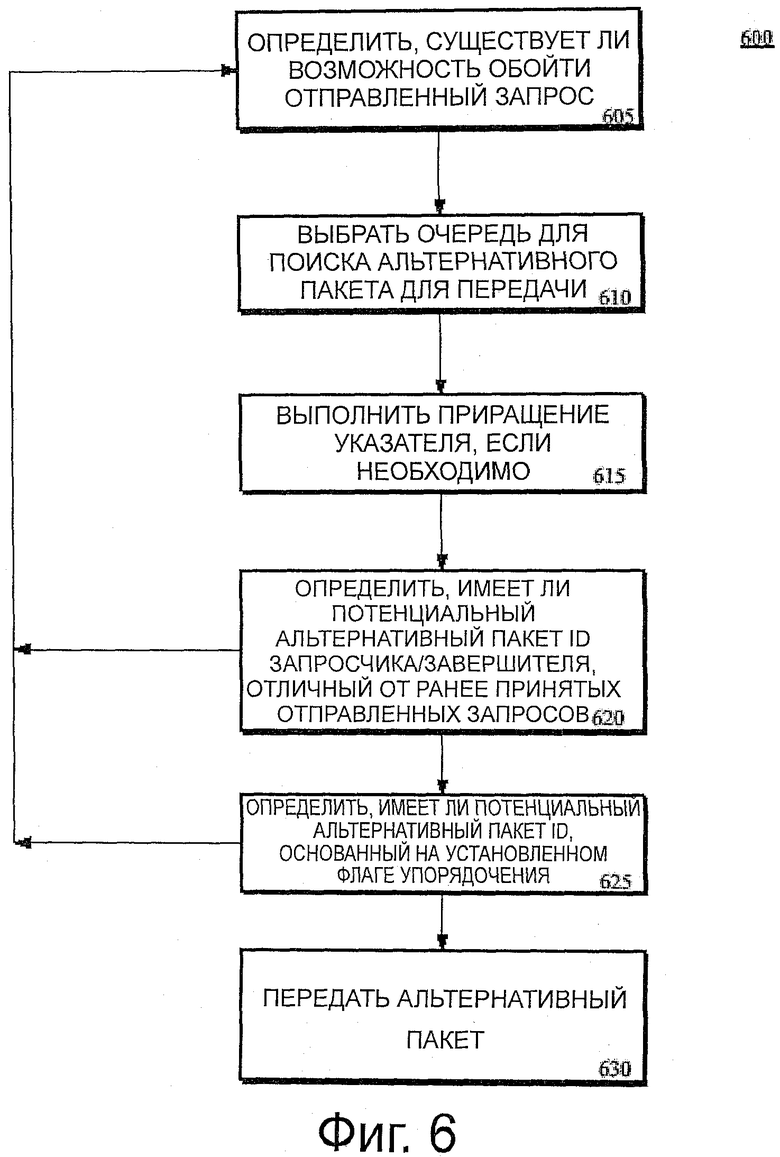

На фиг.1 показан вариант осуществления системы, включающей в себя последовательное двухточечное взаимное соединение для соединения устройств I/O в компьютерной системе.

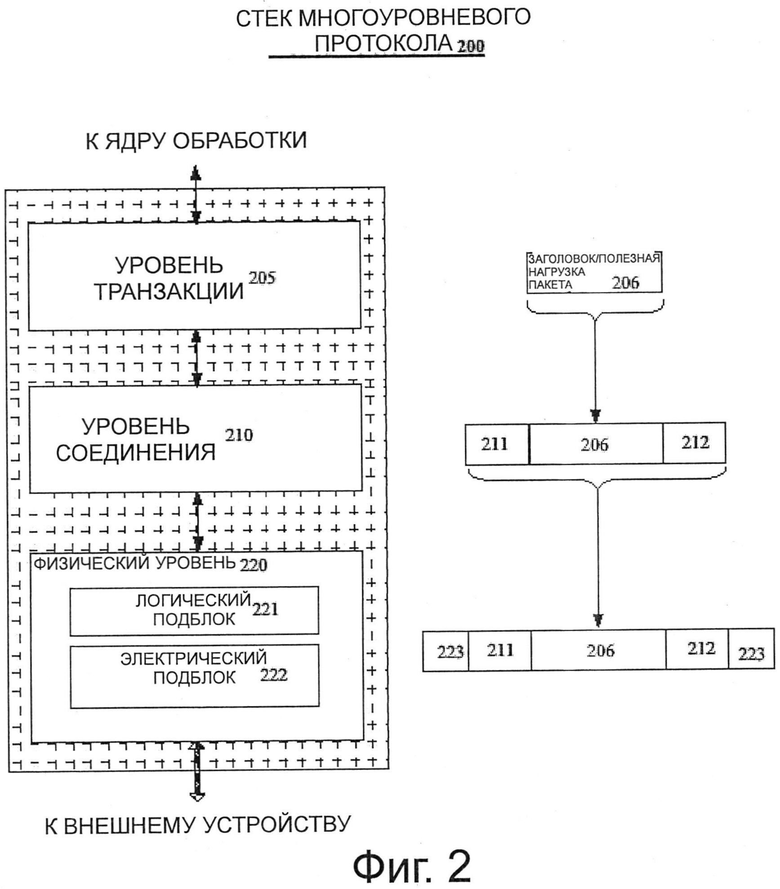

На фиг.2 показан вариант осуществления пакета многоуровневого протокола.

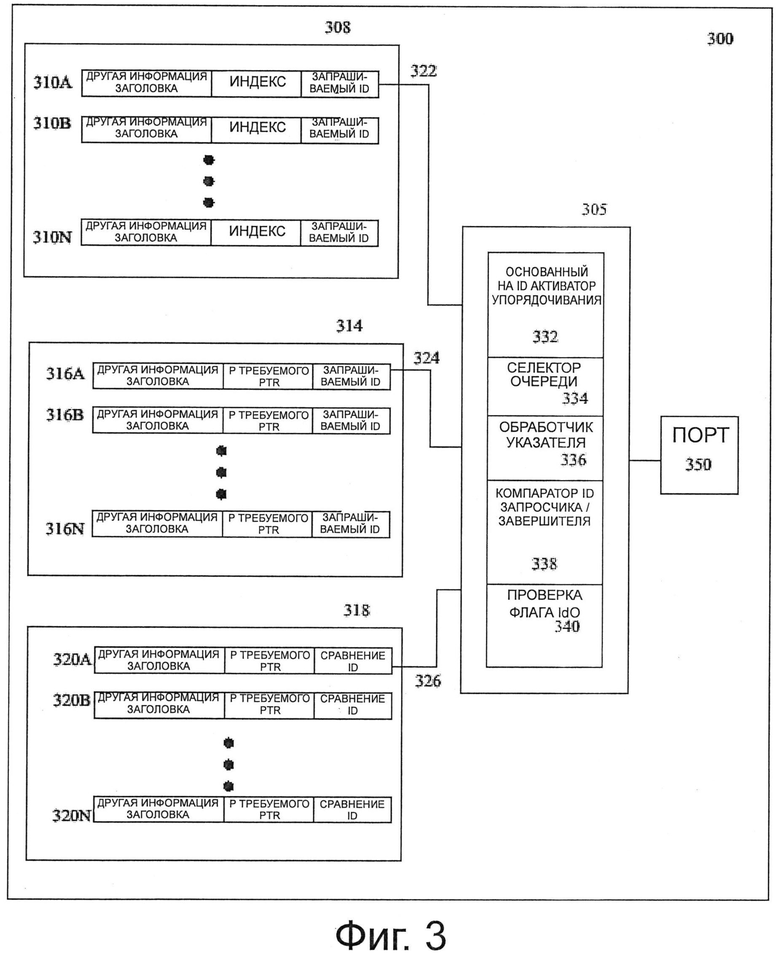

На фиг.3 показан вариант осуществления логики заказа запоминающего устройства.

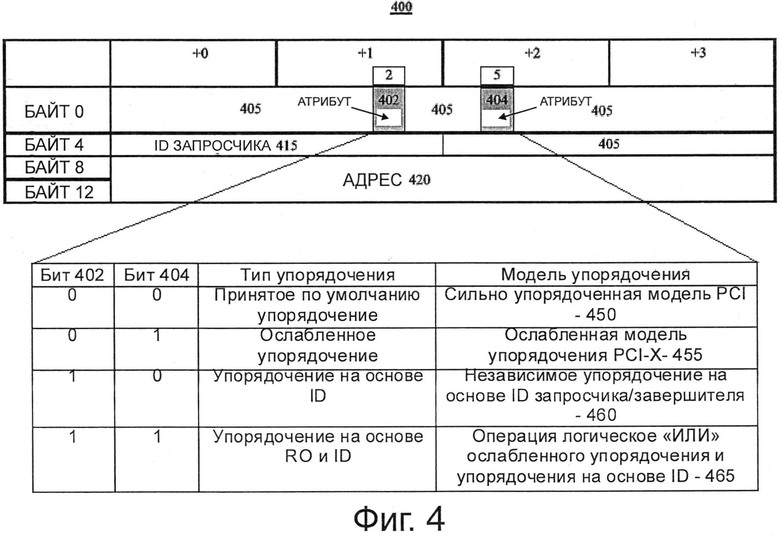

На фиг.4 показан вариант осуществления пакета, включая в себя флаг упорядочивания на основе ID.

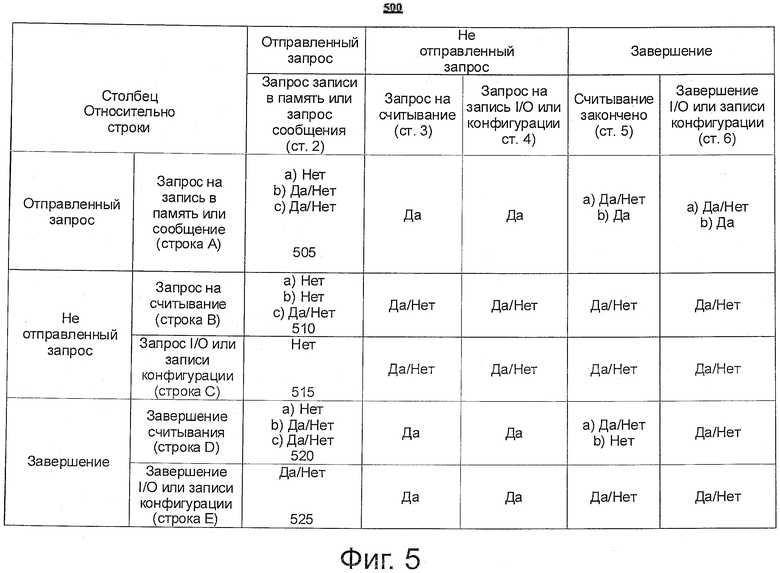

На фиг.5 показан вариант осуществления таблицы упорядочивания.

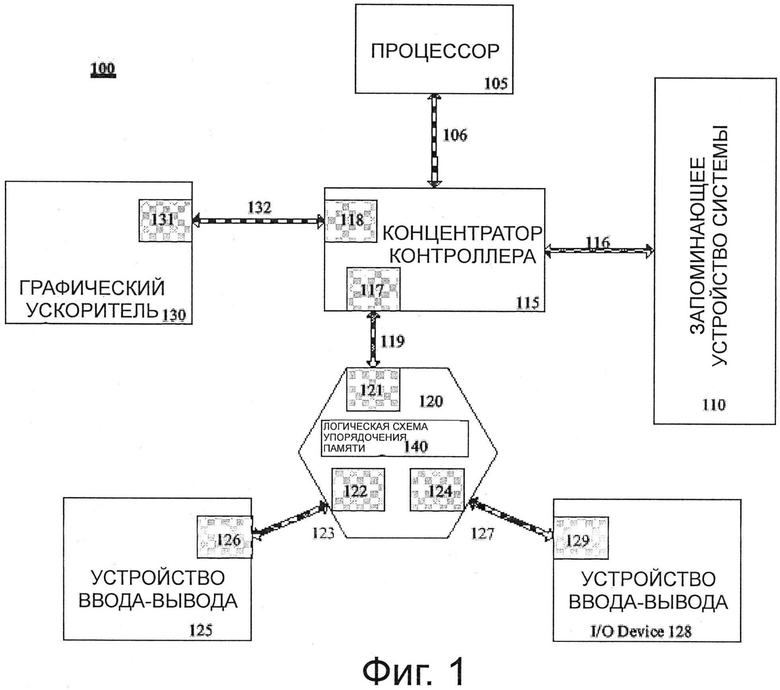

На фиг.6 показан вариант осуществления блок-схемы последовательности операций для обеспечения возможности потоков на основе ID устройства.

Подробное описание изобретения

В следующем описании различные конкретные детали представлены как примеры конкретных взаимных соединений, конкретных пакетов/сообщений, конкретных полей и мест расположения в пределах пакетов/сообщений, конкретных мест положения логических элементов/кэш и т.д. для обеспечения полного понимания настоящего изобретения. Однако для специалиста в данной области техники следует понимать, что эти конкретные детали не обязательно должны быть использованы на практике настоящего изобретения. В других случаях хорошо известные компоненты или способы, такие как логика/воплощение кэш, протоколы передачи сообщений по межсоединению периферийных компонентов экспресс (PCIe), поля/протоколы PCIe при транзакциях и другие основные воплощения PCIe, не были подробно описаны для того, чтобы обеспечить ясное понимание настоящего изобретения.

Способ и устройство, описанные здесь, предназначены для обеспечения потоков ID через PCIe. В частности, обход установленных в очереди запросов в переключателе описан со ссылкой на отправленный запрос, который был остановлен (кредит или другие события, такие как отсутствие страницы). Однако способы и устройство, обеспечивающие потоки на основе ID, не ограничиваются этим, поскольку они могут быть воплощены в или в ассоциации с любым устройством в виде интегральной микросхемы, таким как любое устройство ввода-вывода, или другим компьютерным компонентом, а также совместно с любым типом последовательного взаимного соединения из точки в точку.

Соединение/взаимное соединение "из точки-в-точку" на основе последовательного многоуровневого протокола

На фиг.1 представлен вариант осуществления системы, включающий в себя устройство, соединенное с концентратором контроллера через последовательное соединение. Система 100 включает в себя процессор 105 и запоминающее устройство ПО системы, соединенное с концентратором 115 контроллера. Процессор 105 включает в себя любой элемент обработки, такой как микропроцессор, главный процессор, встроенный процессор, сопроцессор или другой процессор. Процессор 105 соединен с концентратором 115 контроллера через системную шину (FSB) 106. В одном варианте осуществления FSB 106 представляет собой переданное взаимное соединение из точки в точку, как описано ниже.

Запоминающее устройство ПО системы включает в себя любое запоминающее устройство, такое как оперативное запоминающее устройство (RAM), энергонезависимое (NV) запоминающее устройство или другое запоминающее устройство, доступ к которому может осуществляться устройствами в системе 100. Запоминающее устройство ПО системы соединено с концентратором 115 контроллера через интерфейс 116 запоминающего устройства. Примеры интерфейса запоминающего устройства включают в себя интерфейс запоминающего устройства с двойной скоростью передачи данных (DDR), интерфейс запоминающего устройства с двумя каналами DDR и интерфейс запоминающего устройства с динамическим RAM (DRAM).

В одном варианте осуществления концентратор 115 контроллера представляет собой корневой концентратор или корневой контроллер в иерархии взаимного соединения для межсоединения периферийных компонентов экспресс (PCIe или PCIE). Примеры концентратора 115 контроллера включают в себя набор микросхем, концентратор контроллера запоминающего устройства (МСН), северный мост, концентратор контроллера взаимного соединения (ICH) южного моста и корневой контроллер/ концентратор. Часто термин "набор микросхем" относится к двум физически отдельным концентраторам контроллера, то есть к концентратору контроллера запоминающего устройства (МСН), соединенному с концентратором контроллера взаимного соединения (ICH).

Здесь концентратор 115 контроллера соединен с переключателем/мостом 120 через последовательное соединение 119. Модули 117 к 121 ввода-вывода, которые также можно называть интерфейсами/портами 117 и 121, включают в себя/воплощают стек многоуровневого протокола для обеспечения возможности обмена данными между концентратором 115 контроллера и переключателем 120. Модуль, такой как модули 117, 118, 121, 122, 124, 126, 129 и 131, могут быть воплощены в виде аппаратных средств, программных средств, встроенного программного обеспечения или любой их комбинации. Кроме того, границы модуля обычно изменяются, и функции воплощены вместе, а также по отдельности в разных вариантах осуществления. В одном варианте осуществления множество устройств могут быть соединены с переключателем 120.

Переключатель 120 направляет пакеты/сообщения из устройств 125 и 128 вверх по потоку, то есть вверх по иерархии в направлении корневого контроллера, в концентратор 115 контроллера и вниз по потоку, то есть вниз по иерархии от корневого контроллера, от процессора 105 или запоминающего устройства ПО системы в устройства 125 и 128. Устройства 125 и 128 включают в себя любое внутреннее или внешнее устройство или компонент, присоединяемые к электронной системе, такие как устройство I/O, контроллер сетевого интерфейса (NIC), добавочная карта, аудиопроцессор, сетевой процессор, привод жесткого диска, устройство накопитель, CD/DVD ROM, монитор, принтер, мышь, клавиатура, маршрутизатор, портативное устройство - накопитель, устройство типа Firewire, устройство универсальной последовательной шины (USB), сканер и другие устройства ввода-вывода. Переключатель 120 включает в себя логику 140 упорядочивания запоминающего устройства, как описано более подробно ниже, которая обеспечивает потоки на основе ID устройства.

Графический ускоритель 130 также соединен с концентратором /75 контроллера через последовательное соединение 132. В одном варианте осуществления графический ускоритель 130 соединен с МСН, который соединен с ICH. Переключатель 120 и, соответственно, устройства 125 и 128 I/O затем соединены с ICH. Модули 131 и 118 I/O также предназначены для воплощения стека многоуровневого протокола, для обмена данными между графическим ускорителем 130 и концентратором 115 контроллера.

На фиг.2 представлен вариант осуществления стека многоуровневого протокола. Стек 200 многоуровневого протокола включает в себя любой многоуровневый стек передачи данных, такой как стек быстрого взаимного соединения канала передачи (QPI), стек PCIe или другой стек протокола. В одном варианте осуществления стек 200 протокола представляет собой стек протокола PCIe, включающий в себя уровень 205 транзакции, уровень 210 соединения и физический уровень 220. Интерфейс, такой как интерфейсы 117, 118, 121, 122, 124, 126, 129 и 131 на фиг.1, может быть представлен как стек 200 протокола передачи данных. Представление в качестве стека протокола передачи данных также называется модулем или интерфейсом, воплощающим/включающим в себя стек протокола.

Уровень транзакции

В одном варианте осуществления уровень 205 транзакции предназначен для обеспечения интерфейса между ядром обработки устройства и архитектурой взаимного соединения, такой как уровень 210 передачи данных и физический уровень 220. В этом отношении основная ответственность уровня 205 транзакции представляет собой сборку и разборку пакетов (то есть пакетов уровня транзакции, или TLPs). PCIe воплощает разделенные транзакции, то есть транзакции с запросом и ответом, разделенными по времени, что обеспечивает возможность передачи по соединению другого трафика, в то время как целевое устройство собирает данные для ответа.

Кроме того, в PCIe используется управление потоком на основе кредита. В этой схеме устройство рекламирует исходное количество кредита для каждого из приемных буферов на уровне 205 транзакции. Внешнее устройство на противоположном конце соединения, такое как концентратор 115 контроллера по фиг.1, подсчитывает количество кредитов, употребленных каждым TLP. Транзакция может быть передана, если транзакция не превысит предел кредита. После приема ответа величина кредита будет восстановлена. Преимущество схемы кредита состоит в том, что скрытность возврата кредита не влияет на характеристики при условии, что не будет достигнут предел кредита.

В одном варианте осуществления четыре пространства адресов транзакций включают в себя пространство адресов конфигурации, пространство адресов запоминающего устройства, пространство адресов ввода-вывода и пространство адресов сообщения. Транзакции пространства запоминающего устройства включают в себя один или более запросов на считывание и запросов на запись для передачи данных в/из места расположения, отображенного в запоминающем устройстве. В одном варианте осуществления в транзакциях пространства запоминающего устройства могут использоваться два разных формата адреса, например формат короткого адреса, такой как 32-х битный адрес, или формат длинного адреса, такой, как 64-х битный адрес. Транзакции пространства конфигураций используются для доступа к пространству конфигураций устройств PCIe. Транзакции в пространстве конфигураций включают в себя считывание запросов и запись запросов. Транзакции пространства сообщения (или простые сообщения) определены для поддержки передачи данных в полосе пропускания между агентами PCIe.

Поэтому в одном варианте осуществления уровень 205 транзакции собирает заголовки/полезную нагрузку 206 пакетов. Формат для заголовков/полезной нагрузки пакетов может быть найден в спецификации PCIe, то есть в спецификации PCIe base spec 2.0, которая доступна по адресу<>.

Уровень соединения

Уровень 210 соединения, также называемый уровнем 210 канала передачи данных, действует как промежуточный каскад между уровнем 205 транзакции и физическим уровнем 220. В одном варианте осуществления ответственность уровня 210 канала передачи данных состоит в предоставлении надежного механизма для обмена пакетами уровня транзакций (TLP) между двумя компонентами соединения. Одна сторона уровня 210 канала передачи данных принимает TLP, собранные уровнем 205 транзакций, применяет идентификатор 211 последовательности пакета, то есть идентификационный номер или номер пакета, рассчитывает и применяет код детектирования ошибки, то есть CRC 212, и подает модифицированные TLP в физический уровень 220 для передачи через физический уровень во внешнее устройство.

Физический уровень

В одном варианте осуществления физический уровень 220 включает в себя логический подблок 227 и электрический подблок 222 для физической передачи пакета во внешнее устройство. Здесь логический подблок 227 отвечает за "цифровые" функции физического уровня 227. В этом отношении логический подблок включает в себя блок передачи, предназначенный для подготовки исходящей информации для передачи с помощью физического подблока 222, и блок приемника для идентификации и подготовки принятой информации перед подачей ее в уровень 270 соединения.

Физический блок 222 включает в себя передатчик и приемник. В передатчик подают из логического подблока 227 символы, которые передатчик преобразует в последовательную форму и передает во внешнее устройство. В приемник подают преобразованные в последовательные символы из внешнего устройства и преобразует принятые сигналы в поток битов. Поток битов является децентрализованным и его подают в логический подблок 227. В одном варианте осуществления используют код передачи 8b/10b, где передают/принимают десятибитные символы. Здесь специальные символы используют для формирования пакета с фреймами 223. Кроме того, в одном примере приемник также предоставляет тактовую частоту символов, восстановленную из входящего последовательного потока.

Как упомянуто выше, хотя уровень 205 транзакции, уровень 210 соединения и физический уровень 220 описаны со ссылкой на конкретный вариант осуществления стека протокола PCIe, многоуровневый стек протокола не ограничен этим. Фактически, любой многоуровневый протокол может быть включен/воплощен. Например, порт/интерфейс, который представлен как многоуровневый протокол, включает в себя: (1) первый уровень для сборки пакетов, то есть уровень транзакции; второй уровень для установления последовательности пакетов, то есть уровень соединения; и третий уровень для передачи пакетов, то есть физический уровень.

Далее на фиг.3 представлен вариант осуществления логической схемы упорядочения запоминающего устройства. Как показано, интеллектуальный переключатель 300 включает в себя логическую схему 305 упорядочения запоминающего устройства, очередь 308 отправленного запроса (включающую в себя отправленные запросы 310A-N) и указатель 322, очередь 314 неотправленного запроса (включающая в себя неотправленные запросы 316A-N) и указатель 324, очередь 318 завершения (включающая в себя завершения 320A-N) и указатель 326, и порт 350 (который может представлять собой восходящий или нисходящий порт).

Логическая схема 305 упорядочения запоминающего устройства воплощает способ, обеспечивающий потоки на основе ID устройства, например, как описано со ссылкой на фиг.6, и может включать в себя активатор 332 упорядочения на основе ID, селектор 334 очереди, обработчик 336 указателя, компаратор 338 ID запросчика/завершителя и блок 340 проверки флага IDO.

На фиг.4 представлен вариант осуществления пакета, включающего в себя флаг упорядочения на основе ID. Пакет относится к любому запросу, сообщению, доступу или другому группированию информации, предназначенной для передачи по шине/взаимному соединению. В представленном варианте осуществления пакет 400 включает в себя другие информационные поля 405. Примеры другой информации 405 включают в себя зарезервированные поля, поля форматирования, поля типа, поля атрибута, поля длины, PCIe специфичные поля и любые другие поля, специфичные для протокола. Кроме того, пакет 400 включает в себя ID 415 запросчика (байты 4 и 5), который может ссылаться на запрашивающий агент/устройство и представлять собой часть глобального ID/дескриптора транзакции или включает в себя глобальный ID/ID транзакции и поле 420 адреса для ссылки на адрес местоположения.

Биты 402 и 404 атрибута могут обеспечить возможность использования моделей 450, 455, 460 и 465 упорядочивания, как показано. Бит 402 атрибута, который может использовать зарезервированный в настоящее время бит 2 из байта 1, представляет ID на основе флага упорядочивания, который может быть установлен, как запросчик или завершитель, для обозначения того, что запрос или завершение является независимым от порядка и может обходить отправленные запросы.

На фиг.5 представлен вариант осуществления таблицы I упорядочивания. Таблица 500 аналогична Таблице 2-24 Спецификации PCIe, но является модифицированной для обеспечения возможности обхода ранее установленных в очередь, но остановленных, отправленных запросов записи в запоминающее устройство или сообщений (столбец 2) по независимому потоку запроса, в определенных случаях.

В соответствии с ячейкой 505 запрос на запись в запоминающее устройство или запрос сообщения: со сброшенным ослабленным битом 404 атрибута упорядочивания и сброшенным битом 402 упорядочения по ID не должен быть пропущен (а); с установленным, ослабленным битом 404 атрибута упорядочения и сброшенным битом 402 упорядочения по ID разрешено пропустить (b); и при сброшенном, ослабленном бите 404 атрибута упорядочения и установленном бите 402 упорядочения ID разрешено пропустить любой другой запрос записи в запоминающее устройство или сообщение, если ID 415 их запросчика являются разными (с).

В соответствии с ячейкой 510 запрос на считывание: со сброшенным, ослабленным битом 404 атрибута упорядочения и со сброшенным битом 402 упорядочения ID не должен быть пропущен (а); с установленным, ослабленным битом 404 атрибута упорядочения и со сброшенным битом 402 упорядочения ID не должен быть пропущен (b); и со сброшенным или установленным ослабленным битом 404 атрибута упорядочения и с установленным битом 402 упорядочения ID разрешено пропустить любой другой запрос на запись запоминающего устройства или сообщения, если ID 415 их запросчика являются разными (с).

В соответствии с ячейкой 515 I/O или запросы на запись конфигурации не могут пропустить запрос на запись в запоминающем устройстве или запрос сообщения. Это предотвращает сильное упорядочение записи, требуемое для поддержки модели использования производителя/потребителя.

В соответствии с ячейкой 520 завершение считывания: со сброшенным, ослабленным битом 404 атрибута упорядочения и со сброшенным битом 402 упорядочения ID не должно быть пропущено (а); с установленным, ослабленным битом 404 атрибута упорядочения и сброшенным битом 402 упорядочения ID разрешено пропустить (b); и со сброшенным, ослабленным битом 404 атрибута упорядочения и установленным битом 402 упорядочения ID разрешено пропустить любой запрос на запись в запоминающее устройство или сообщения, если ID его завершителя отличается от ID 415 запросчика записи в запоминающее устройство (с).

Наконец, в соответствии с ячейкой 525, I/O или завершения записи конфигурации разрешено блокировать или пропускать с помощью запроса записи в запоминающее устройство и сообщений. Такие транзакции фактически движутся в противоположном направлении и поэтому не имеют взаимосвязи упорядочивания.

Далее на фиг.6 показан вариант осуществления блок-схемы последовательности операций, обеспечивающий потоки на основе ID устройства. В потоке 605 активатор 332 упорядочения на основе ID определяет, существует ли возможность обхода отправленного запроса. В одном варианте осуществления активатор 332 переводит процесс в поток 610, если определяется, что оправленный запрос остановлен.

Селектор 334 очереди затем выбирает очередь для поиска альтернативного пакета, для передачи в потоке 610. В одном варианте осуществления селектор 334 выбирает очередь 308 отправленного запроса, очередь 314 неотправленного запроса или очередь 318 завершения, на основе которого очередь имеет большинство точек входа. В другом варианте осуществления селектор 334 всегда вначале выбирает очередь 314 неотправленного запроса для поиска альтернативного пакета. В потоке 615 обработчик 336 указателя может последовательно увеличивать один или более указателей 322, 324, 326, например, если предыдущий потенциальный альтернативный пакет не было разрешено пропустить (то есть не из независимого потока, при неустановленном бите 402 упорядочения ID).

Затем в потоке 620 компаратор 338 ID запросчика/завершителя определяет, отличается ли ID запросчика/завершителя потенциального альтернативного пакета от любого из ранее принятых отправленных запросов в очереди 308 отправленного запроса. В одном варианте осуществления компаратор 338 использует указатель отправленного запроса, сохраненный с каждым неотправленным запросом и завершением для определения, какие из отправленных запросов в очереди 308 отправленного запроса были приняты перед потенциальным альтернативным пакетом. Если определяют, что потенциальный альтернативный пакет представляет собой независимый поток из ранее принятых отправленных запросов, тогда обработка продолжается в потоке 625. В противном случае обработка возвращается к потоку 605.

В потоке 625 проверка 340 флага IDO проверяет, что бит 402 упорядочения ID установлен в потенциальном альтернативном пакете, и если это так, в потоке 630 альтернативный пакет передают через порт 350. В противном случае обработка возвращается в поток 605.

Варианты осуществления способов, программного обеспечения, встроенного программного обеспечения или кода, представленные выше, могут быть воплощены через инструкции или код, сохраненные на носителе информации, доступ к которому осуществляется устройством, или на считываемом устройством носителе информации, которые могут быть выполнены элементом обработки. Носитель информации, доступ/считывание которого осуществляет устройство, включает в себя любой механизм, который обеспечивает (то есть сохраняет и/или передает) информацию в форме, считываемой устройством, таким как компьютер или электронная система. Например, носитель информации, доступ к которому осуществляет устройство, включает в себя оперативное запоминающее устройство (RAM), такое как статическое RAM (SRAM) или динамическое RAM (DRAM); ROM; магнитный или оптический носитель информации; запоминающее устройство типа флэш; электрические, оптические, акустические или другие формы распространяющихся сигналов (например, несущих волн, инфракрасных сигналов, цифровых сигналов) и т.д.

Ссылка в данном описании на "один вариант осуществления" или "вариант осуществления" означает, что определенное свойство, структура или характеристика, описанная в связи с вариантом осуществления, включена, по меньшей мере, в один вариант осуществления настоящего изобретения. Таким образом, появляющиеся фразы "в одном варианте осуществления" или "в варианте осуществления" в различных местах в данном описании необязательно все относятся к одному и тому же варианту осуществления. Кроме того, конкретные особенности, структуры или характеристики могут быть скомбинированы любым соответствующим способом в одном или болеше вариантах осуществления.

В предыдущем описании подробное описание изобретения было представлено со ссылкой на конкретные примерные варианты выполнения. Однако следует понимать, что различные модификации и изменения могут быть выполнены в отношении него, без выхода за пределы широко понимаемых сущности и объема изобретения, как установлено в приложенной формуле изобретения. Описание и чертежи, соответственно, следует рассматривать в качестве иллюстрации, а не как ограничение. Кроме того, представленное выше использование варианта осуществления и другие примерные формулировки необязательно относятся к одному и тому же варианту осуществления или одному и тому же примеру, но могут относиться к разным и отличным вариантам осуществления, а также потенциально к одному и тому же варианту осуществления.

Изобретение относится к области взаимных соединений и, в частности, к обеспечению потоков на основе идентификатора через шину PCI Express. Технический результат - упорядочивание потоков запросов для минимизации очередей. Устройство для упорядочивания пакетов содержит логическую схему упорядочивания памяти для упорядочивания пакетов, подлежащих передаче через порт последовательного двухточечного взаимного соединения, при этом логическая схема упорядочивания памяти выполнена с возможностью выборочного обхода остановленного отправленного запроса и передачи через порт неотправленного запроса, принятого после остановленного отправленного запроса, если заголовок неотправленного запроса указывает, что неотправленный запрос является независимым от порядка, и если заголовок неотправленного запроса включает в себя идентификатор запросчика, отличный от идентификаторов запросчиков ранее принятых отправленных запросов; и выборочного обхода остановленного отправленного запроса и передачи через порт пакета завершения, принятого после остановленного отправленного запроса, если заголовок пакета завершения указывает, что остановленный отправленный запрос является независимым от порядка, и если заголовок пакета завершения включает в себя идентификатор завершителя, отличный от идентификаторов завершителей ранее принятых отправленных запросов. 3 н. и 11 з.п. ф-лы, 6 ил.

1. Устройство для упорядочивания пакетов, содержащее:

логическую схему упорядочивания памяти для упорядочивания пакетов, подлежащих передаче через порт последовательного двухточечного взаимного соединения, при этом логическая схема упорядочивания памяти выполнена с возможностью

выборочного обхода остановленного отправленного запроса и передачи через порт неотправленного запроса, принятого после остановленного отправленного запроса, если заголовок неотправленного запроса указывает, что неотправленный запрос является независимым от порядка, и если заголовок неотправленного запроса включает в себя идентификатор запросчика, отличный от идентификаторов запросчиков ранее принятых отправленных запросов; и

выборочного обхода остановленного отправленного запроса и передачи через порт пакета завершения, принятого после остановленного отправленного запроса, если заголовок пакета завершения указывает, что остановленный отправленный запрос является независимым от порядка, и если заголовок пакета завершения включает в себя идентификатор завершителя, отличный от идентификаторов завершителей ранее принятых отправленных запросов.

2. Устройство по п.1, в котором идентификатор содержит байты четыре и пять заголовка пакета.

3. Устройство по п.1, в котором последовательное двухточечное взаимное соединение представляет собой межсоединение периферийных компонентов экспресс (PCIE), при этом дополнительно содержит процессор, системную память и графический ускоритель, соединенные с возможностью передачи данных по межсоединению PCIE.

4. Устройство по п.1, в котором порт представляет собой порт, расположенный ниже по потоку.

5. Устройство для упорядочивания пакетов, содержащее:

порт для передачи пакетов по последовательной двухточечной линии связи;

первую очередь для хранения пакетов отправленных запросов, подлежащих передаче через порт;

вторую очередь для хранения пакетов неотправленных запросов, подлежащих передаче через порт; и

логическую схему для выборочного обхода остановленного отправленного запроса из первой очереди и передачи через порт неотправленного запроса из второй очереди, принятого после остановленного отправленного запроса, если заголовок неотправленного запроса указывает, что неотправленный запрос является независимым от порядка, и если заголовок неотправленного запроса включает в себя идентификатор запросчика, отличный от идентификаторов запросчиков ранее принятых отправленных запросов в первой очереди,

при этом устройство для упорядочивания пакетов дополнительно содержит:

третью очередь для хранения пакетов завершений, подлежащих передаче через порт, при этом логическая схема выполнена с возможностью выборочного обхода остановленного отправленного запроса из первой очереди и передачи через порт пакета завершения из третьей очереди, принятого после остановленного отправленного запроса, если заголовок пакета завершения указывает, что пакет завершения является независимым от порядка, и если заголовок пакета завершения включает в себя идентификатор завершителя, отличный от идентификаторов запросчиков ранее принятых отправленных запросов в первой очереди.

6. Устройство по п.5, в котором логическая схема выполнена с возможностью выборочного обхода остановленного отправленного запроса из первой очереди и передачи через порт отправленного запроса из первой очереди, который был принят после остановленного отправленного запроса, если заголовок отправленного запроса указывает, что запрос является независимым от порядка, и если заголовок отправленного запроса включает в себя идентификатор запросчика, отличный от идентификатора запросчика остановленного отправленного запроса.

7. Устройство по п.5, в котором порт представляет собой порт, расположенный выше по потоку.

8. Устройство по п.5, дополнительно содержащее процессор, системную память и графический ускоритель, соединенные с возможностью передачи данных с последовательной двухточечной линией связи.

9. Устройство по п.5, в котором вторая очередь выполнена с возможностью хранения отправленного указателя запросов, связанного с каждым неотправленным пакетом запроса, для указания, какие из отправленных запросов, содержащихся в первой очереди, были приняты ранее каждого неотправленного пакета запроса.

10. Устройство по п.5, в котором флаг атрибута содержит бит два байта один заголовка пакета.

11. Устройство для упорядочивания пакетов, содержащее:

устройство, включающее в себя модуль ввода-вывода (I/O), содержащий стек протокола, при этом стек протокола включает в себя физический уровень, уровень соединения и уровень транзакции, причем стек протокола выполнен с возможностью:

передачи пакета неотправленного запроса по последовательной двухточечной линии связи, при этом пакет неотправленного запроса включает в себя флаг, установленный для обозначения, что операция является независимой от порядка, при этом пакетам неотправленных запросов, содержащим указанный флаг, разрешено обходить отправленные запросы, если заголовок пакета неотправленного запроса включает в себя идентификатор запросчика, отличные от идентификаторов запросчиков ранее принятых отправленных запросов, и

передачи пакета завершения по последовательной двухточечной линии связи, при этом пакет завершения включает в себя флаг, установленный для обозначения, что операция является независимой от порядка, при этом пакетам завершения, содержащим указанный флаг, разрешено обходить отправленные запросы, если заголовок пакета завершения включает в себя идентификатор завершителя, отличный от идентификаторов запросчиков ранее принятых отправленных запросов.

12. Устройство по п.11, в котором флаг, установленный для обозначения, что операция является независимой от порядка, содержит бит два байта один заголовка пакета.

13. Устройство по п.11, в котором устройство выбрано из группы, состоящей из ускорителя, устройства ввода-вывода, концентратора контроллера, корневого контроллера, переключателя и процессора.

14. Устройство по п.11, в котором устройство соединено с возможностью обмена данных с системной памятью и множеством дополнительных устройств для формирования системы.

| Станок для изготовления деревянных ниточных катушек из цилиндрических, снабженных осевым отверстием, заготовок | 1923 |

|

SU2008A1 |

| US 7443869 B1, 28.10.2008 | |||

| Способ приготовления мыла | 1923 |

|

SU2004A1 |

| Станок для изготовления деревянных ниточных катушек из цилиндрических, снабженных осевым отверстием, заготовок | 1923 |

|

SU2008A1 |

| Колосоуборка | 1923 |

|

SU2009A1 |

| US 6993611 B2, 31.01.2006 | |||

| Станок для изготовления деревянных ниточных катушек из цилиндрических, снабженных осевым отверстием, заготовок | 1923 |

|

SU2008A1 |

| СПОСОБЫ И УСТРОЙСТВА ДЛЯ ОСУЩЕСТВЛЕНИЯ КАНАЛА СВЯЗИ ПЕРЕМЕННОЙ РАЗРЯДНОСТИ | 2004 |

|

RU2288542C2 |

Авторы

Даты

2014-03-10—Публикация

2010-03-10—Подача