Область техники, к которой относится изобретение

Настоящее изобретение относится к компьютерным системам, в частности (но не исключительно) к соединениям точка-точка.

Уровень техники

Достижения в области технологии полупроводниковых приборов и в проектировании логических устройств позволили увеличить объем логических устройств, которые могут быть размещены в одной интегральной схеме. Как следствие, произошло развитие конфигураций компьютерных систем от одной или более интегральных схем до систем с множеством ядер, множеством аппаратных потоков и множеством логических процессоров в одной индивидуальной интегральной схеме, равно как и других интерфейсов, интегрированных в таких процессорах. Процессор или интегральная схема обычно содержит один физический процессорный кристалл, где этот процессорный кристалл может содержать произвольное число ядер, аппаратных потоков, логических процессоров, интерфейсов, запоминающих устройств, контроллеров-концентраторов и т.п.

В результате возросших возможностей вместить больше процессорных мощностей в корпуса меньшего размера выросла популярность малогабаритных компьютерных устройств. Численность и сфера применения смартфонов, планшетов, ультратонких ноутбуков и других пользовательских устройств росли экспоненциально. Однако эти малогабаритные устройства зависят от серверов как для хранения данных, так и для осуществления сложной обработки данных, для которой не хватает возможностей, ограниченных форм-фактором малогабаритных устройств. Следовательно, потребности в создании рынка высокопроизводительных вычислений (т.е. в серверном пространстве) тоже выросли. Например, современный сервер обычно содержит не только один многоядерный процессор, но и несколько физических процессоров (также называемых несколькими сокетами) для увеличения вычислительной мощности. Но по мере роста процессорных мощностей вместе с числом устройств в компьютерной системе связь между сокетами и другими устройствами становится все более критичной.

На деле технология соединений между устройствами прошла путь развития от более традиционных многоотводных шин, осуществлявших преимущественно электрическую связь, до полностью развитой полнофункциональной архитектуры соединений, способствующей осуществлению высокоскоростной связи. К сожалению, по мере роста требований к процессорам будущего работать на все более высоких скоростях, соответствующие требования предъявляются и к возможностям существующих архитектур соединений.

Краткое описание чертежей

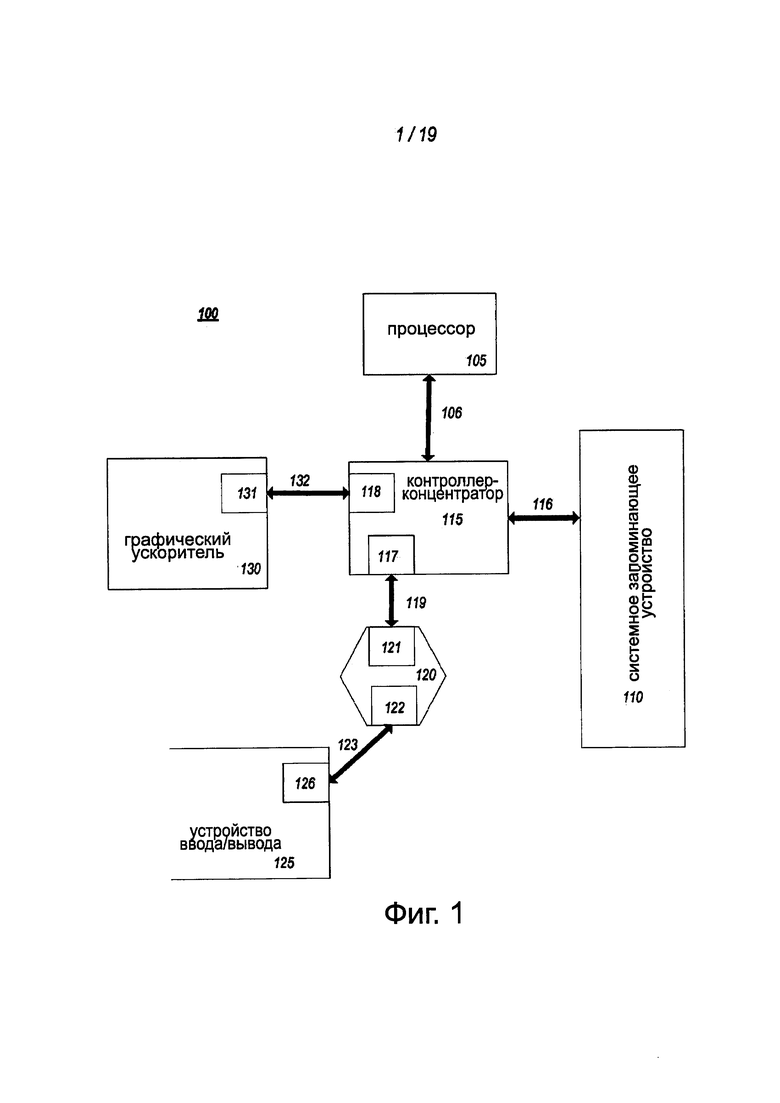

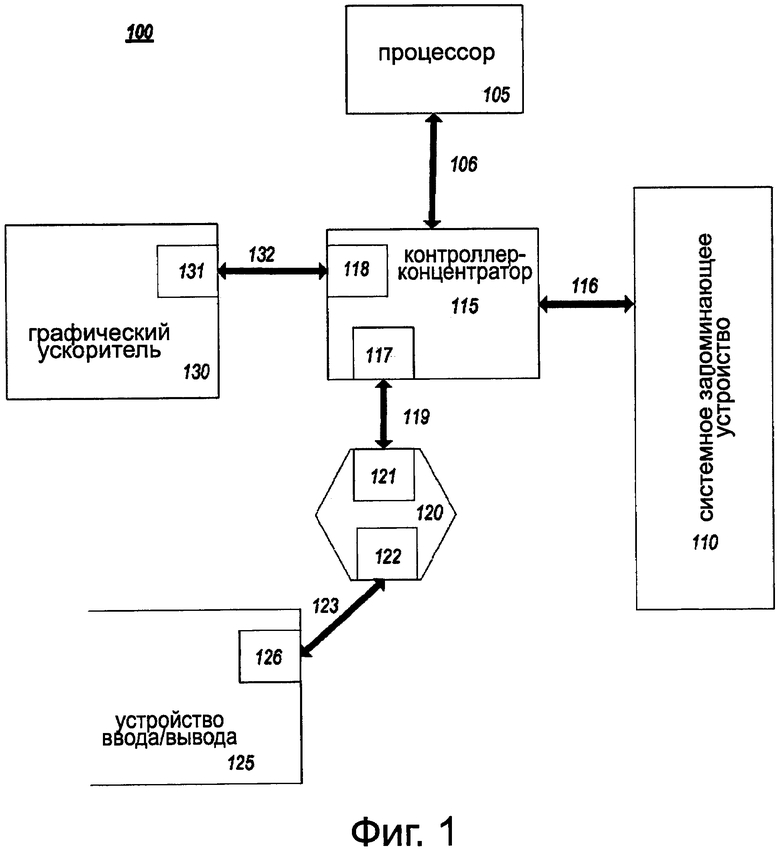

Фиг. 1 иллюстрирует вариант компьютерной системы, содержащей архитектуру соединений.

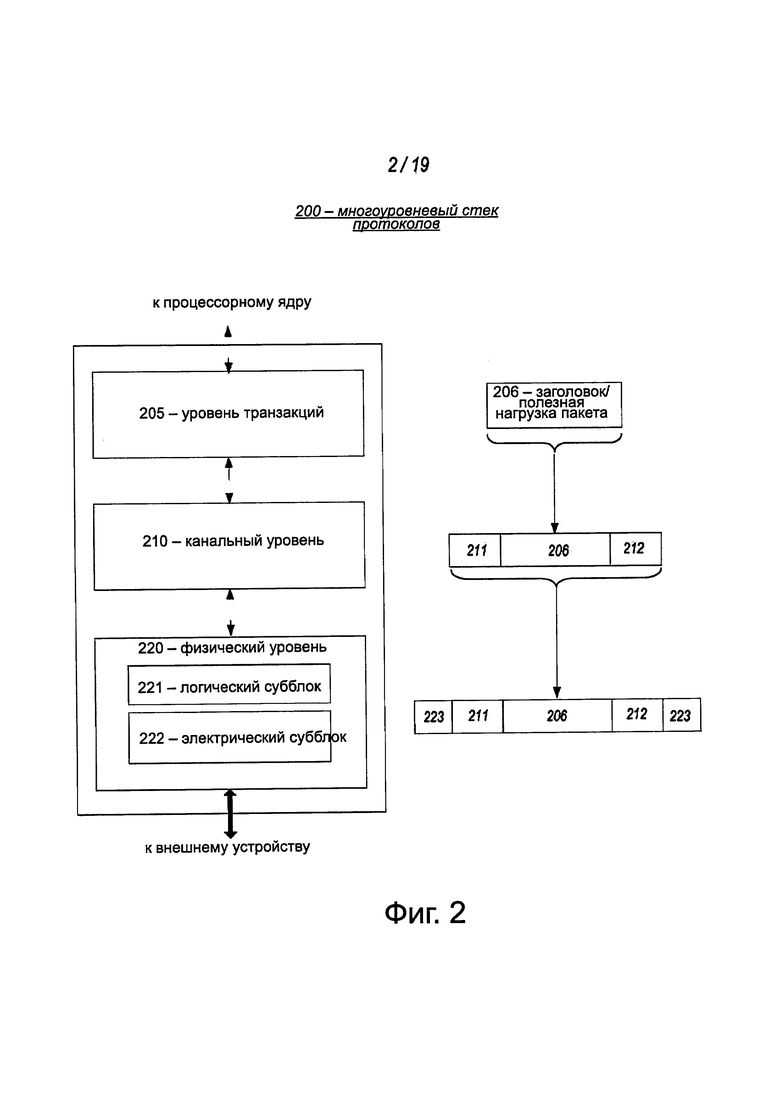

Фиг. 2 иллюстрирует вариант архитектуры соединений, содержащей многоуровневый стек.

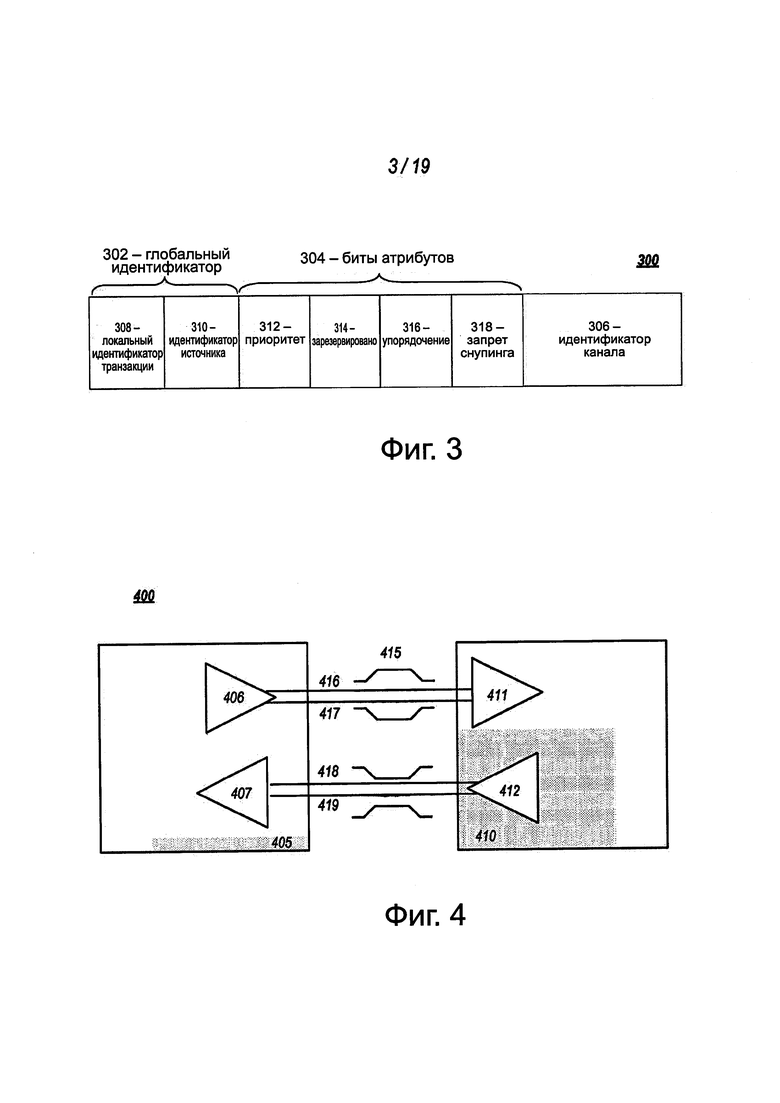

Фиг. 3 иллюстрирует вариант запроса или пакета, какие следует генерировать или принимать в архитектуре соединений.

Фиг. 4 иллюстрирует варианты пары из передатчика и приемника для архитектуры соединений.

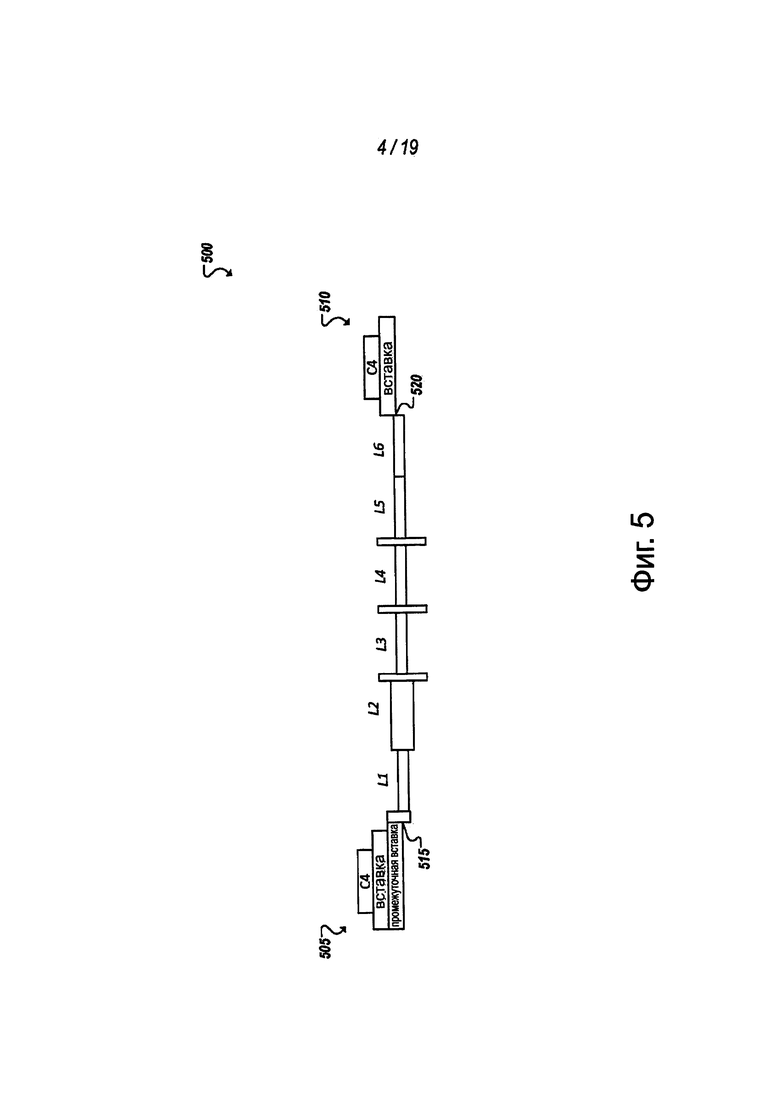

Фиг. 5 иллюстрирует вариант примера канала для соединения между двумя разъемами.

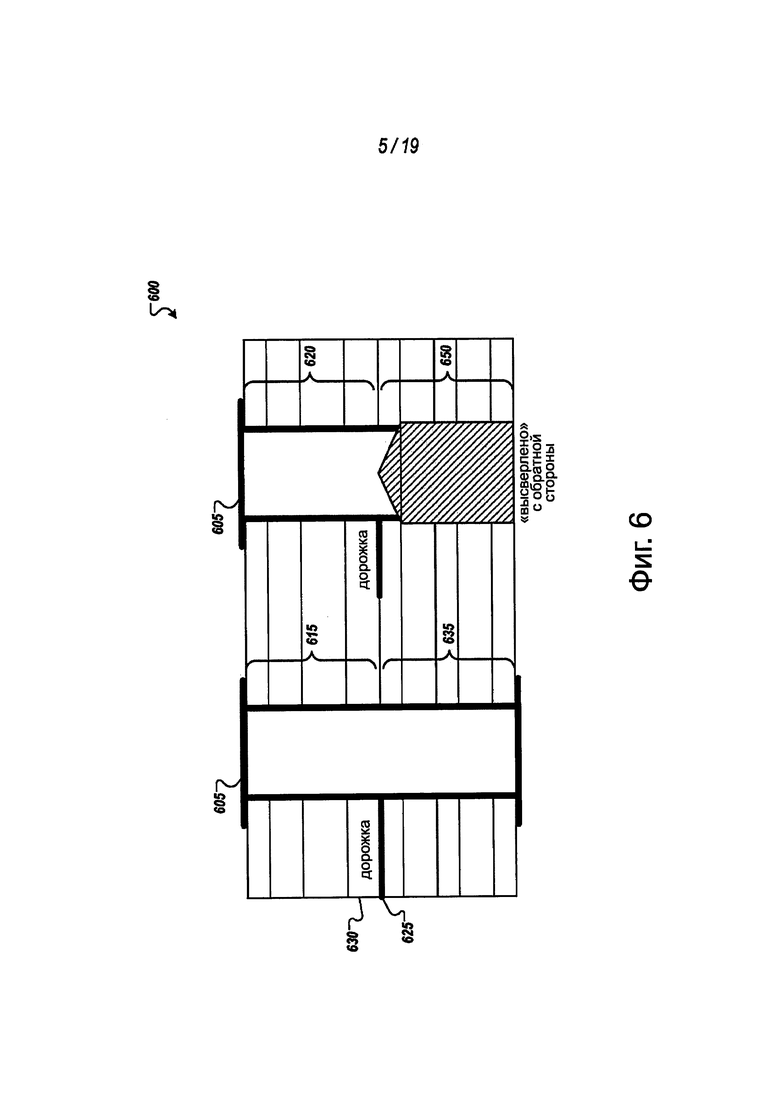

Фиг. 6 представляет упрощенную блок-схему соединительной структуры, имеющей сквозные соединения, в разрезе.

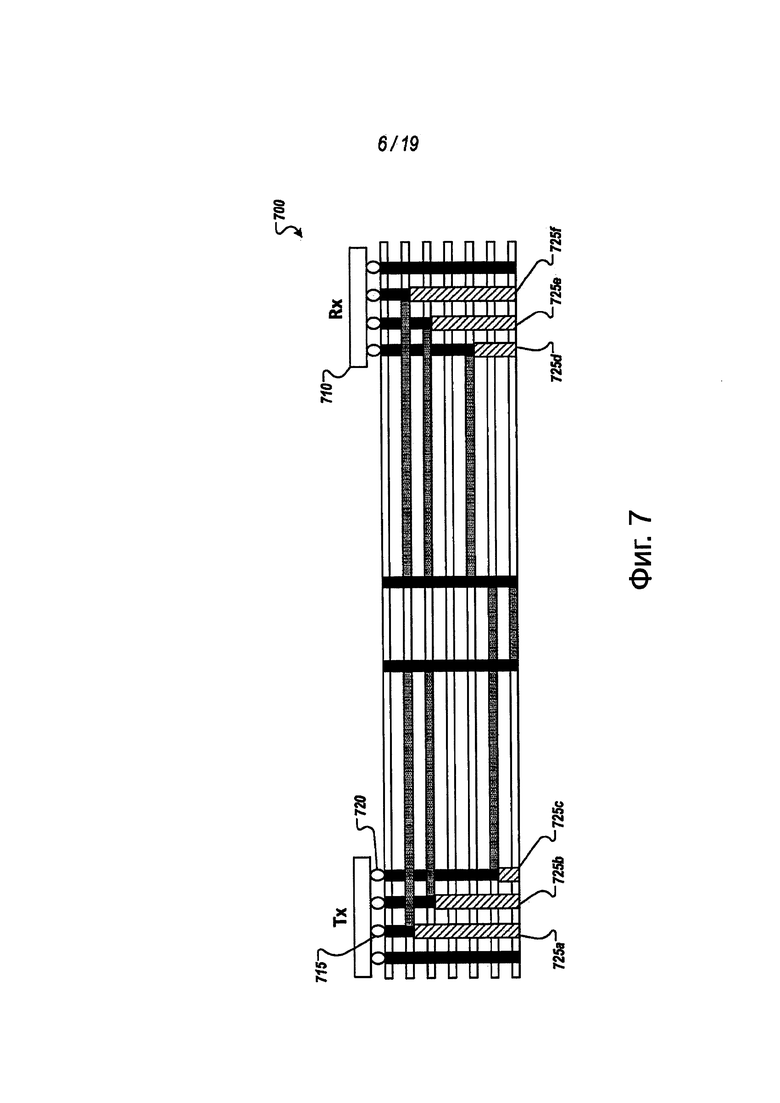

Фиг. 7 представляет соединение в разрезе с использованием «высверливания» столбиков сквозных соединений сзади.

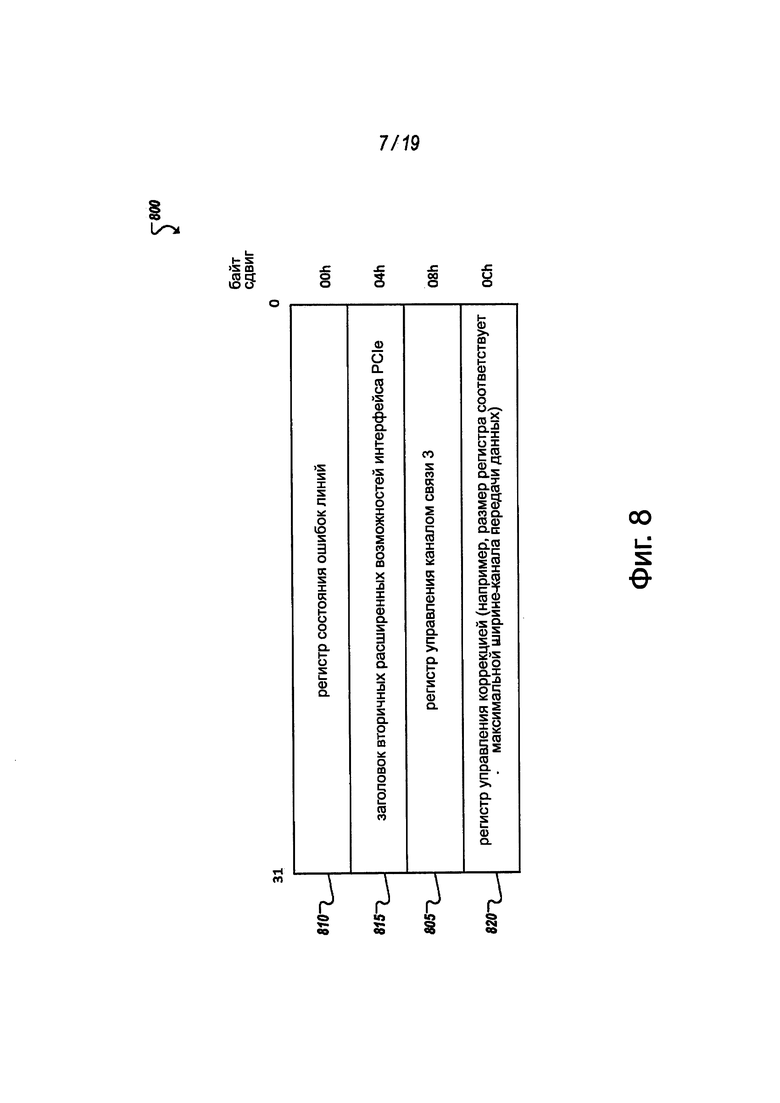

Фиг. 8 представляет блок-схему структуры возможностей, включая регистр состояния ошибки линии.

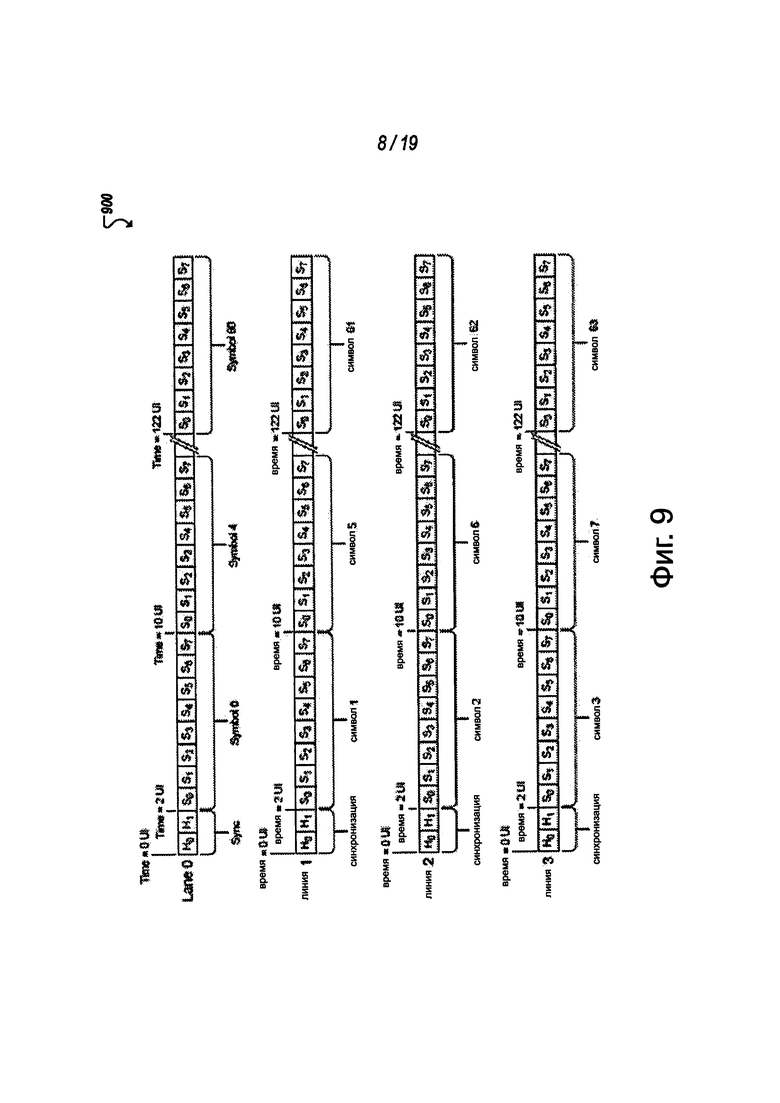

Фиг. 9 представляет упрощенную схему, иллюстрирующую потоки данных в много линейном соединении.

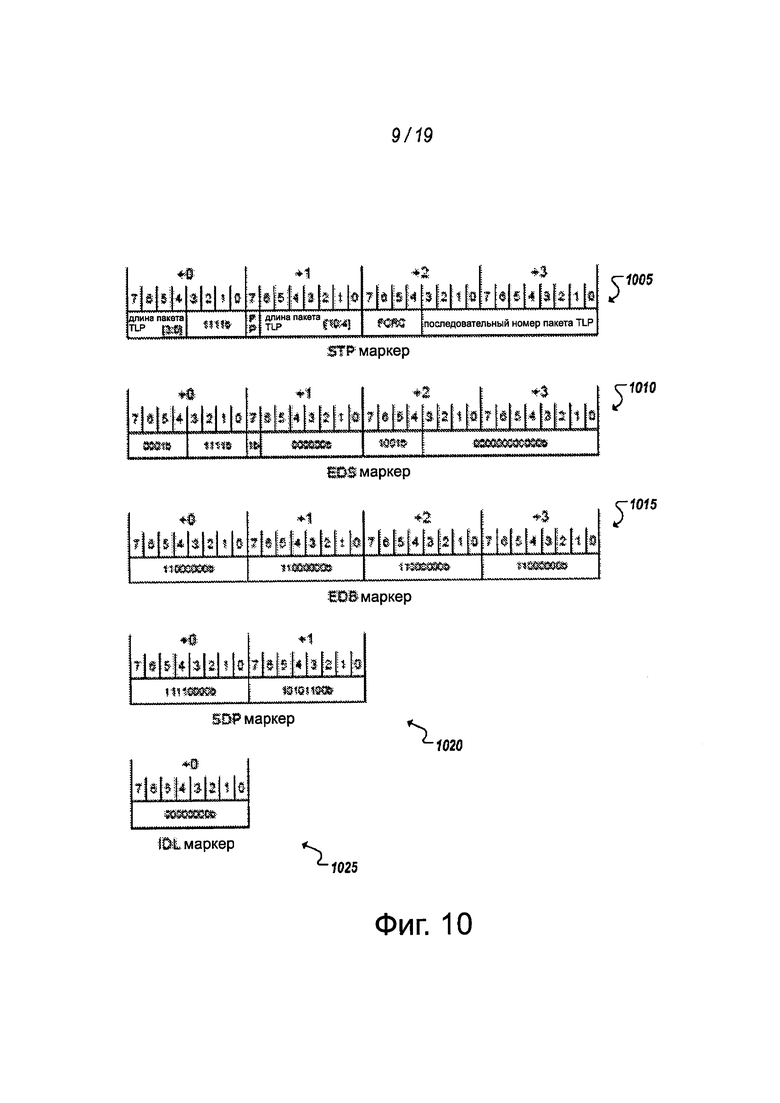

Фиг. 10 показывает представление примера символов кадрирующего маркера.

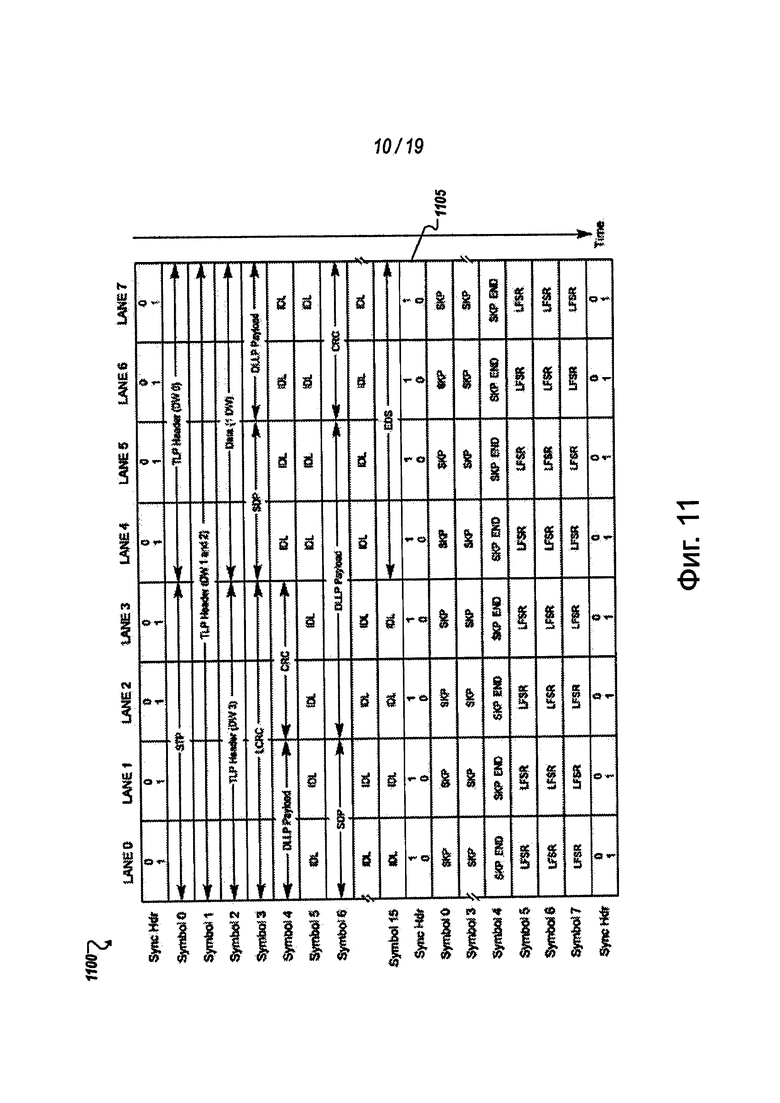

Фиг. 11 представляет упрощенную схему, иллюстрирующую потоки данных, включая пример упорядоченного множества пропуска (SKP).

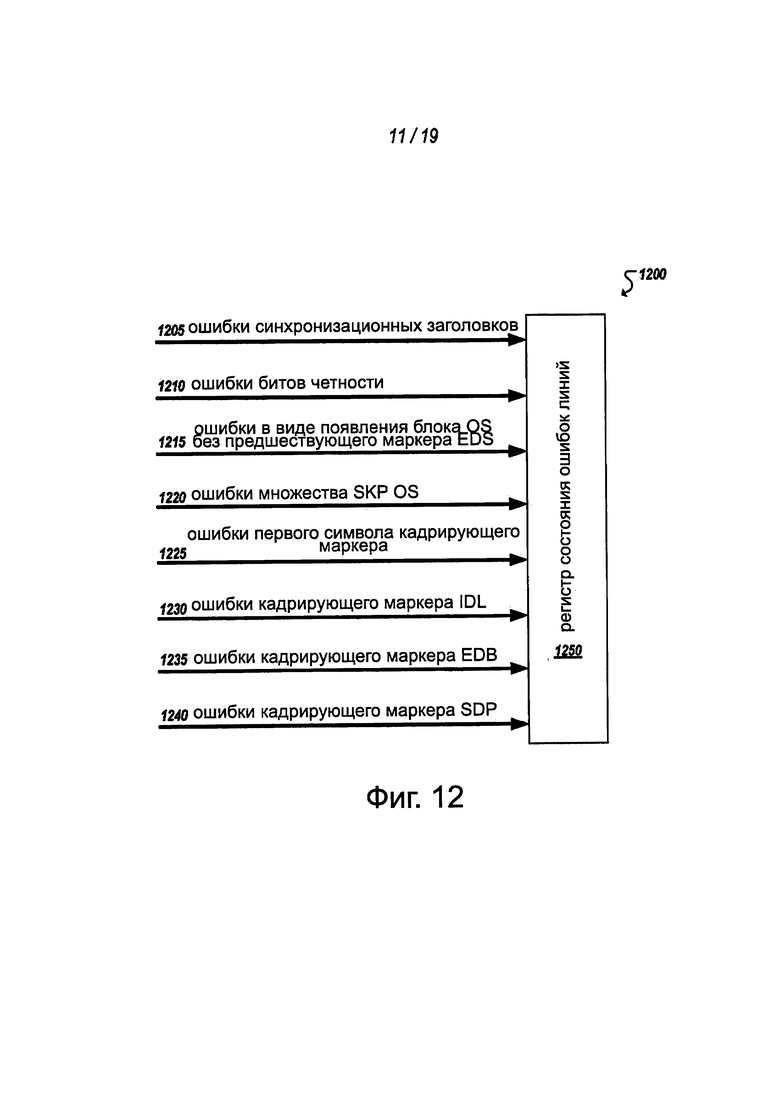

Фиг. 12 представляет упрощенную схему, иллюстрирующую ошибки линии, сообщение о которых может быть передано в регистр ошибок.

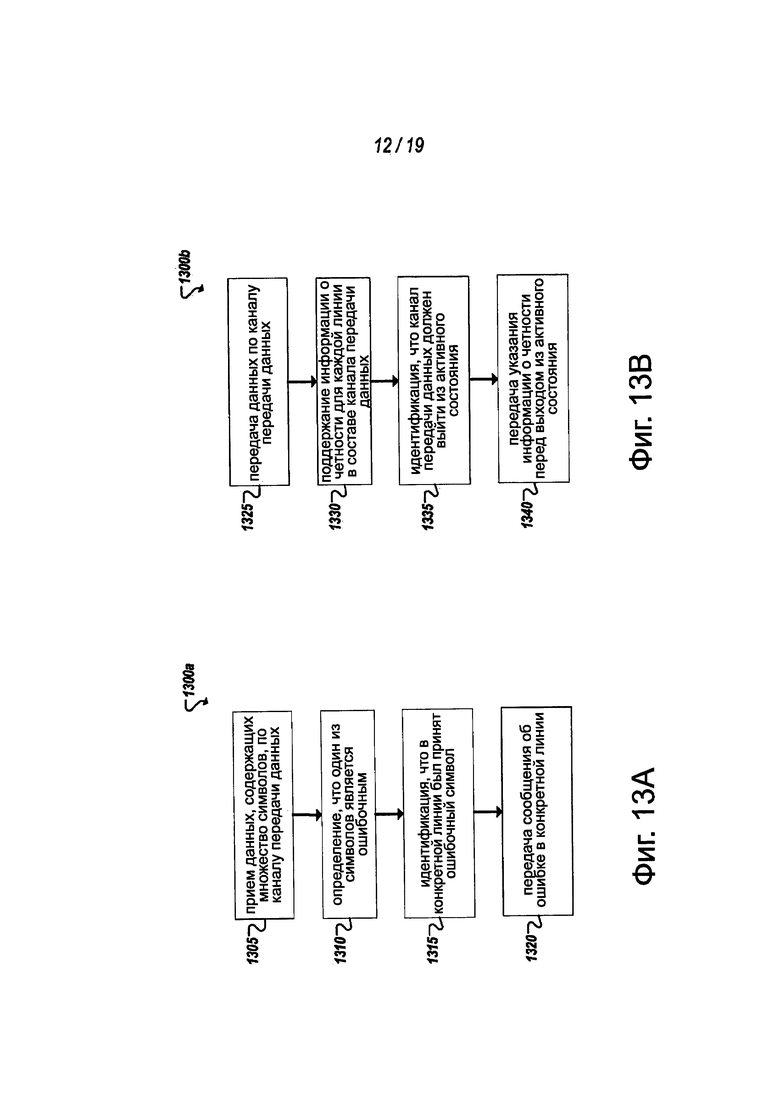

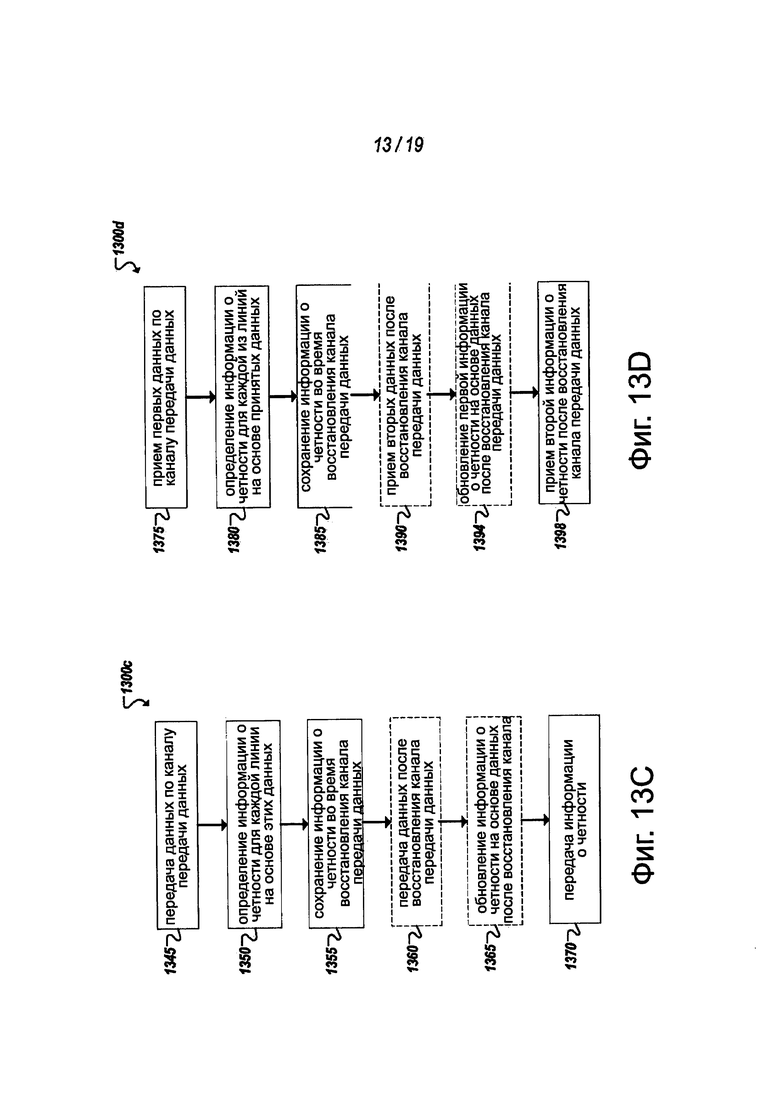

Фиг. 13A-13D представляют логические схемы, иллюстрирующие примеры передачи сообщений об ошибках линий канала связи.

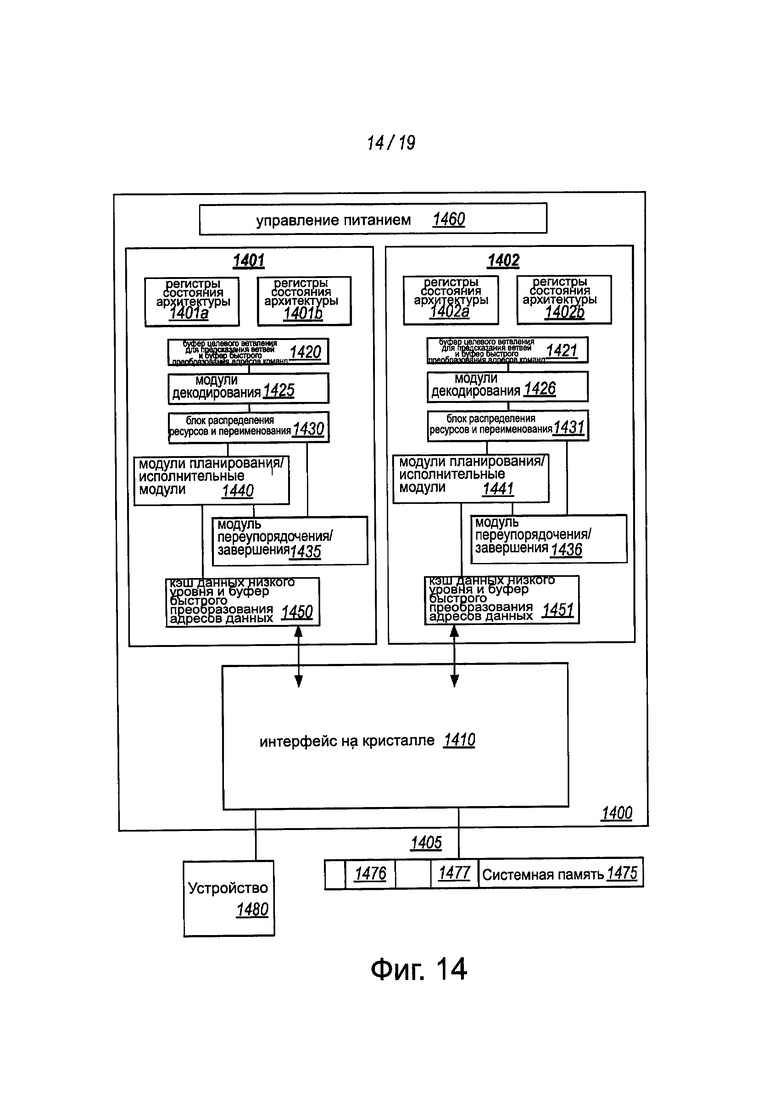

Фиг. 14 иллюстрирует вариант блок-схемы компьютерной системы, содержащей многоядерный процессор.

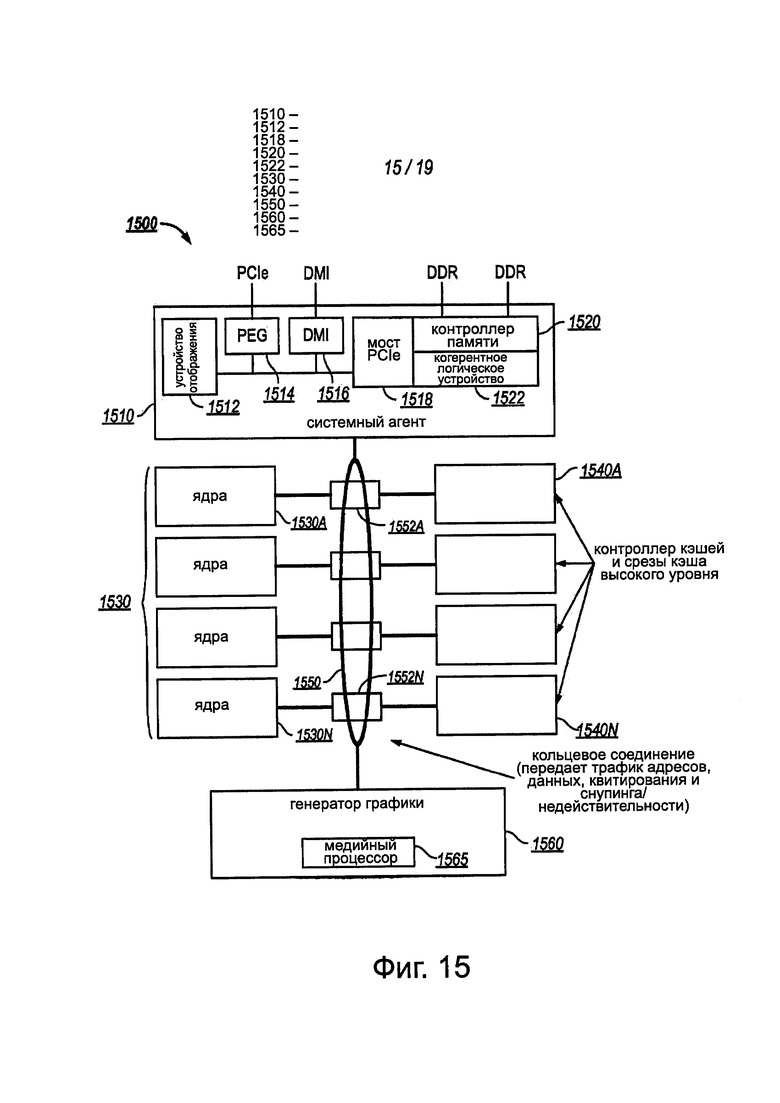

Фиг. 15 иллюстрирует другой вариант блок-схемы компьютерной системы, содержащей многоядерный процессор.

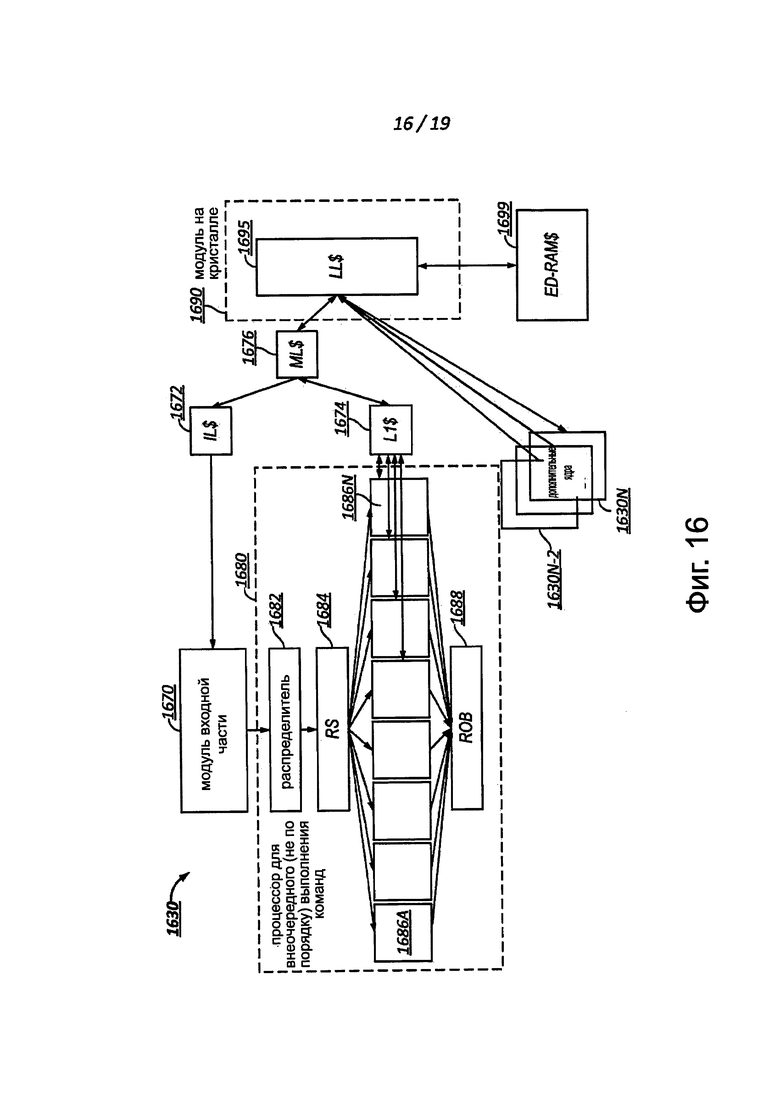

Фиг. 16 иллюстрирует вариант блок-схемы процессора.

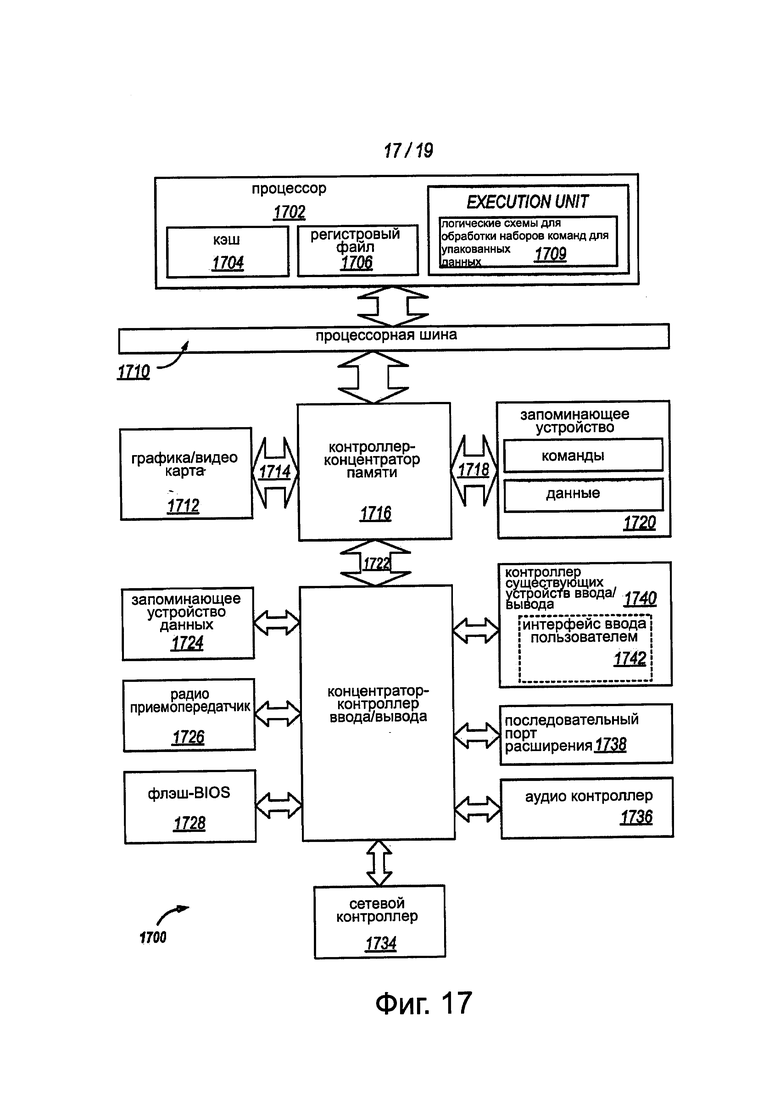

Фиг. 17 иллюстрирует другой вариант блок-схемы компьютерной системы, содержащей процессор.

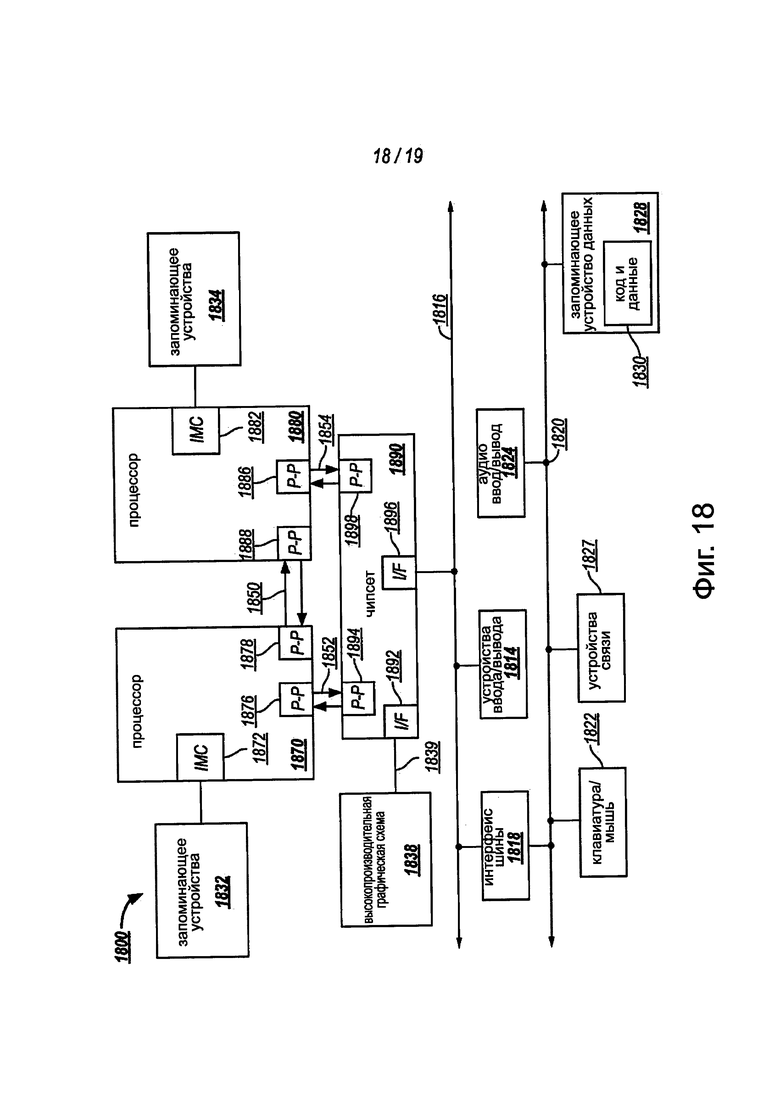

Фиг. 18 иллюстрирует вариант блок-схемы компьютерной системы, содержащей несколько процессоров.

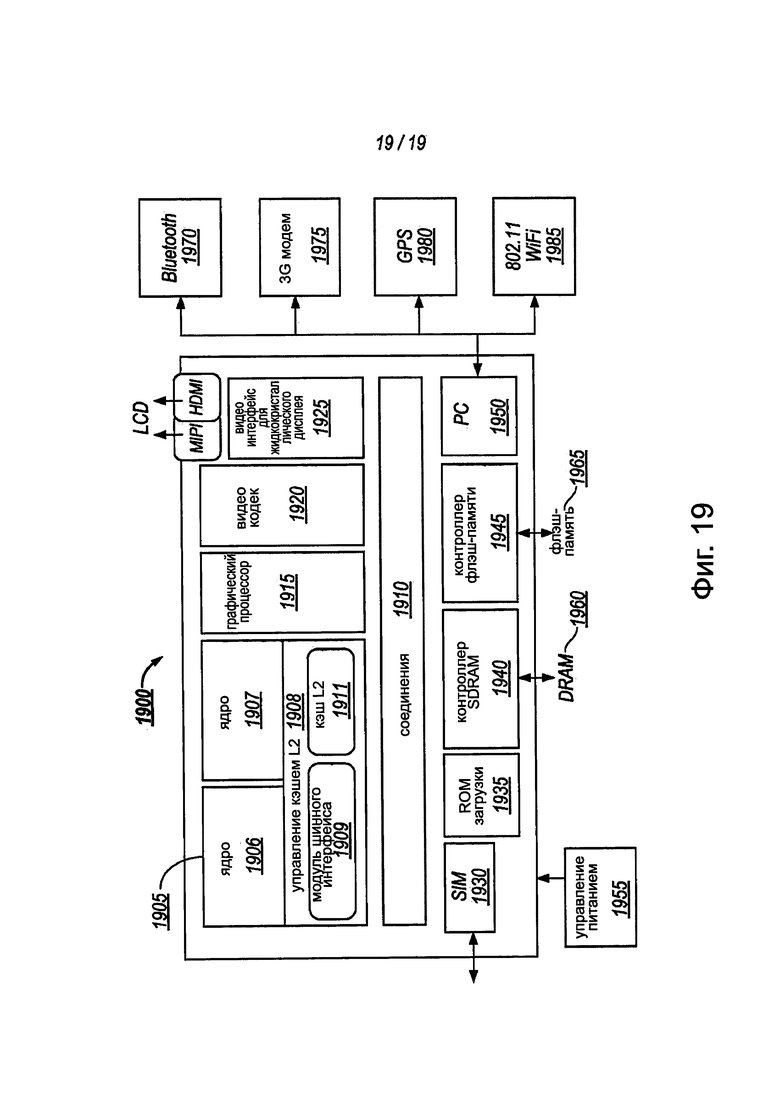

Фиг. 19 иллюстрирует пример системы, реализованной в виде системы на кристалле (SoC).

Подобные цифровые и иные позиционные обозначения на разных чертежах указывают подобные элементы.

Осуществление изобретения

В последующем описании приведены многочисленные конкретные детали, такие как примеры конкретных типов процессоров и конфигурации систем, конкретные структуры аппаратуры, конкретные архитектурные и микроархитектурные подробности, конкретные конфигурации регистров, конкретные типы команд, конкретные компоненты систем, конкретные размеры/высоты, конкретные ступени процессорных конвейеров и операций и т.п., с целью предоставления возможности полного понимания настоящего изобретения. Однако специалисту в рассматриваемой области должно быть понятно, что эти конкретные детали не обязательно использовать при практической реализации настоящего изобретения. В других случаях хорошо известные компоненты или способы, такие как конкретные и альтернативные процессорные архитектуры, конкретные логические схемы/коды для описываемых алгоритмов, конкретные коды встроенного программного обеспечения, конкретные соединительные операции, конкретные логические конфигурации, конкретные способы изготовления и материалы, конкретные варианты реализации компилятора, конкретные выражения алгоритмов в виде кода, конкретные способы/логические устройства для выключения питания/стробирования и другие конкретные подробности работы компьютерных систем здесь не были описаны подробно, чтобы избежать нежелательного загромождения и «затемнения» описания настоящего изобретения.

Хотя последующие варианты могут быть описаны с точки зрения энергосбережения и энергетической эффективности конкретных интегральных схем, таких как компьютерные платформы или микропроцессоры, другие варианты применимы к другим типам интегральных схем и логических устройств. Способы и принципы, аналогичные описываемым здесь вариантам, могут быть применены к другим типам схем или полупроводниковых приборов, которые также могут выиграть от лучшей энергетической эффективности и сбережения энергии. Например, описываемые варианты не ограничиваются настольными компьютерными системами или компьютерами типа Ultrabooks™. Они могут быть также использованы в других устройствах, таких как ручные устройства, планшеты, другие тонкие ноутбуки, системы на кристалле (system on а chip (SOC)) и встроенные приложения. В качестве некоторых примеров ручных устройств можно указать сотовые телефоны, устройства Интернет-протокола, цифровые фото и видеокамеры, персональные цифровые помощники (personal digital assistants (PDA)) и ручные персональные компьютеры. Встроенные приложения обычно содержат микроконтроллер, цифровой процессор сигнала (digital signal processor (DSP)), систему на кристалле, сетевые компьютеры (network computers (NetPC)), приставки, сетевые концентраторы, коммутаторы глобальной сети связи (wide area network (WAN)) или какие-либо другие системы, которые могут осуществлять функции и операции, рассматриваемые ниже. Более того, аппаратура, способы и системы, рассматриваемые здесь, не ограничиваются физическими компьютерными устройствами, а могут также относиться к программным оптимизациям с целью сбережения энергии и энергетической эффективности. Как станет легко понятно из приведенного ниже описания, варианты способов, аппаратуры и систем, описываемые здесь (будь то со ссылками на аппаратуру, встроенное программное обеспечение, загружаемое программное обеспечение или сочетания этих компонентов) являются жизненно важными для так называемой «зеленой технологии» будущего, сбалансированной с учетом соображений производительности.

По мере совершенствования компьютерных систем компоненты таких систем становятся все более сложными. В результате сложность архитектуры соединений для связи между компонентами также возрастает, чтобы удовлетворить требованиям к широкополосности связи для оптимальной работы компонентов. Более того, разные сегменты рынка требуют различных аспектов архитектуры соединений для удовлетворения разных потребностей рынка. Например, от серверов требуется высокая производительность, тогда мобильная экосистема иногда может пожертвовать общей производительностью в пользу энергосбережения. До сих пор единственным требованием к большинству систем соединений являлось достижение наивысшей возможной производительности при максимальном энергосбережении. Ниже обсуждаются некоторые системы соединений, которые потенциально должны были бы выиграть от некоторых аспектов настоящего изобретения, рассматриваемых здесь.

Одна из архитектур соединений содержит архитектуру соединений периферийных устройств Peripheral Component Interconnect (PCI) Express (PCIe). Основной целью архитектуры PCIe является обеспечение возможности для компонентов и устройств от разных поставщиков взаимодействовать в открытой архитектуре, охватывая несколько сегментов рынка: а именно Клиентов (Client) (настольных (Desktop) и мобильных (Mobile)), Серверов (Server) (обычных (Standard) и серверов предприятий (Enterprise)), а также встроенных (Embedded) устройств и устройств связи (Communication). Стандарт интерфейса PCI Express представляет собой стандарт высокопроизводительной системы соединений ввода/вывода общего назначения, созданный для самого широкого спектра компьютерных платформ и платформ связи будущего. Некоторые атрибуты интерфейса PCI, такие как модель использования, архитектура загрузки-хранения и программные интерфейсы, были сохранены во всех редакциях этого интерфейса, тогда как прежняя параллельная реализация шины была заменена в высокой степени масштабируемым полностью последовательным интерфейсом. Более новые версии интерфейса PCI Express используют достижения в области двухпунктовых соединений, технологии на основе коммутации и протокола передачи пакетов данных для достижения новых, более высоких уровней производительности и характеристик. Среди усовершенствованных характеристик интерфейса PCI Express можно указать управление питанием (Power Management), управление качеством обслуживания (Quality Of Service (QoS)), поддержку «горячего» подключения в рабочем состоянии (Hot-Plug) и «горячей» замены в рабочем состоянии (Hot-Swap) устройств, обеспечение целостности данных (Data Integrity) и обработку ошибок (Error Handling).

На Фиг. 1 представлен вариант архитектуры соединений, составленной из каналов связи точка-точка, соединяющих множество компонентов. Система 100 содержит процессор 105 и системное запоминающее устройство ПО, соединенные с контроллером-концентратором 115. Процессор 105 содержит какой-либо процессорный элемент, такой как микропроцессор, главный процессор, встроенный процессор, сопроцессор или какой-либо другой процессор. Процессор 105 соединен с контроллером-концентратором 115 посредством внешней шины (front-side bus (FSB)) 106. В одном из вариантов шина FSB 106 представляет собой последовательное двухпунктовое соединение, как описано ниже. В другом варианте канал 106 связи содержит последовательную дифференциальную архитектуру соединений, совместимую с другим стандартом соединений.

Системное запоминающее устройство 110 представляет собой запоминающее устройство какого-либо типа, такое как запоминающее устройство с произвольной выборкой (RAM), энергонезависимое запоминающее устройство (non-volatile (NV) memory) или какое-нибудь другое запоминающее устройство, доступное для других устройств в системе 100. Системное запоминающее устройство 110 связано с контроллером-концентратором 115 через интерфейс 116 памяти. Среди примеров таких интерфейсов памяти можно указать интерфейс памяти с удвоенной скоростью передачи данных (double-data rate (DDR)) двухканальный DDR-интерфейс памяти и интерфейс памяти для динамического (DRAM).

В одном из вариантов контроллер-концентратор 115 представляет собой корневой концентратор, корневой комплекс или корневой контроллер в иерархии соединений Peripheral Component Interconnect Express (PCIe или PCIE). К примерам таких контроллеров-концентраторов 115 относятся чипсет, контроллер-концентратор памяти (МСН), схема «Северный мост» (northbridge), контроллер-концентратор соединений (ICH), схема «Южный мост» (southbridge) и корневой контроллер/концентратор. Часто термин «чипсет» относится к двум физически раздельным контроллерам-концентраторам, т.е. к контроллеру-концентратору памяти (МСН), связанному с контроллером-концентратором соединений (ICH). Отметим, что современные системы часто содержат блок МСН, интегрированный с процессором 105, тогда как контроллер 115 предназначен для связи с устройствами ввода/вывода аналогично тому, как описано ниже. В некоторых вариантах корневым комплексом 115 в качестве опции поддерживается одноранговая маршрутизация.

Здесь контроллер-концентратор 115 соединен с коммутатором/мостом 120 посредством последовательного канала 119 связи. Модули 117 и 121 ввода/вывода, которые могут также называться интерфейсами/портами 117 и 121, содержат/реализуют многоуровневый стек протоколов для осуществления связи между контроллером-концентратором 115 и коммутатором 120. В одном из вариантов с коммутатором 120 могут быть соединены несколько устройств.

Коммутатор/мост 120 осуществляет маршрутизацию пакетов/сообщений от устройства 125 «вверх», т.е. вверх по иерархии по направлению к корневому комплексу, к контроллеру-концентратору 115 и «вниз», т.е. вниз по иерархии прочь от корневого контроллера, от процессора 105 или системного запоминающего устройства 110 к устройству 125. Коммутатор 120 в одном из вариантов называется логической сборкой из нескольких виртуальных мостовых устройств PCI-k-PCI/. Устройство 125 содержит какое-либо внутреннее устройство или компонент для соединения с электронной системой. Это устройство или компонент может представлять собой устройство ввода/вывода, контроллер сетевого интерфейса (Network Interface Controller (NIC)), расширительную плату, аудио процессор, сетевой процессор, накопитель на жестком диске, запоминающее устройство, накопитель CD/DVD ROM, монитор, принтер, мышь, клавиатуру, маршрутизатор, портативное запоминающее устройство, устройство с шиной сверхбыстрой передачи данных (Firewire), устройство с универсальной последовательной шиной (Universal Serial Bus (USB)), сканер или другое устройство ввода/вывода. Часто на жаргоне PCIe такое устройство называется конечной или крайней точкой. Хотя это не показано специально, устройство 125 может содержать мост для соединения PCIe с PCI/PCI-X с целью поддержки PCI-устройств, соответствующих прежним устаревшим или другим версиям. Устройства конечных точек в системах PCIe часто классифицируют как прежние, устаревшие конечные точки, конечные точки PCIe или интегральные конечные точки корневого комплекса.

С контроллером-концентратором 115 по последовательному каналу 132 связи соединен также графический ускоритель 130. В одном из вариантов графический ускоритель 130 соединен с блоком МСН, который связан с блоком ICH. Коммутатор 120 и соответственно устройство 125 ввода/вывода затем соединены с блоком ICH. Модули 131 и 118 ввода/вывода также реализуют многоуровневый стек протоколов для осуществления связи между графическим ускорителем 130 и контроллером-концентратором 115. Аналогично обсуждавшемуся выше блоку МСН графический контроллер или графический ускоритель 130 сам может быть интегрирован в процессор 105.

На Фиг. 2 показан вариант многоуровневого стека протоколов. Этот многоуровневый стек 200 протоколов может содержать какую-либо форму многоуровневого стека связи, такую как стек шины быстрого соединения (Quick Path Interconnect (QPI)), стек PCIe, стек высокопроизводительных компьютерных соединений следующего поколения или другой многоуровневый стек. Хотя приведенное непосредственно ниже со ссылками на Фиг. 1-4 обсуждение относится к стеку PCIe, те же самые принципы могут быть применены и к другим стекам соединений. В одном из вариантов стек 200 протоколов является PCIe-стеком протоколов, содержащим уровень 205 транзакций, канальный уровень 210 и физический уровень 220. Интерфейс, такой как интерфейсы 117, 118, 121, 122, 126 и 131, может быть представлен в виде стека 200 протоколов связи. Представление в виде стека протоколов связи может также называться модулем или интерфейсом, реализующим/содержащим стек протоколов.

Интерфейс PCI Express использует пакеты для передачи информации между компонентами. Пакеты формируются на уровне 205 транзакций (Transaction Layer) и на уровне 210 канала передачи данных или канальном уровне (Data Link Layer) для переноса информации от передающего компонента к приемному компоненту. Когда передаваемые пакеты проходят через другие уровни, происходит расширение этих пакетов за счет добавления дополнительной информации, необходимой для обработки пакетов на этих уровнях. На приемной стороне осуществляется обратный процесс и происходит преобразование пакетов от представления, которое они имели на физическом уровне 220 (Physical Layer) к представлению на канальном уровне 210 и, в конце концов (для пакетов уровня транзакций) к форме, в которой эти пакеты могут быть обработаны на уровне 205 транзакций в приемном устройстве.

Уровень транзакций

В одном из вариантов уровень 205 транзакций служит интерфейсом между процессорным ядром устройства и архитектурой соединений, такой как канальный уровень 210 и физический уровень 220. С этой точки зрения главной сферой ответственности уровня 205 транзакций является сборка и разборка пакетов (т.е. пакетов уровня транзакций (transaction layer packet) или TLP). Уровень 205 транзакций обычно осуществляет управление потоком на кредитной основе для пакетов TLP. Интерфейс PCIe осуществляет расщепленные транзакции, т.е. транзакции, для которых запрос и ответ разделены во времени, что позволяет каналу связи передавать другой трафик, пока целевое устройство собирает данные для ответа.

Кроме того, интерфейс PCIe использует управление потоком на кредитной основе. При использовании такой схемы устройство объявляет первоначальный объем кредита для каждого из приемных буферов на уровне 205 транзакций. Внешнее устройство на противоположном конце канала связи, такое как контроллер-концентратор 115, показанный на Фиг. 1, подсчитывает число кредитов, израсходованных каждым пакетом TLP. Любая транзакция может быть передана, только если она не превышает кредитный лимит. После приема ответа объем кредита восстанавливается. Преимущество такой кредитной схемы состоит в том, что задержка возврата кредита не влияет на производительность при условии, что кредитный лимит не достигнут.

В одном из вариантов совокупность четырех адресных пространств транзакций содержит адресное пространство конфигурации, адресное пространство памяти, адресное пространство ввода/вывода и адресное пространство сообщений. К транзакциям в пространстве памяти относятся один или несколько запросов считывания и запросов записи для передачи данных в/из позиций памяти. В одном из вариантов транзакции в пространстве памяти могут использовать два разных формата адресов, например, короткий адресный формат, такой как 32-битовые адреса, или длинный адресный формат, такой как 64-битовые адреса. Транзакции в пространстве конфигурации используются для доступа в пространство конфигурации PCIe-устройств. Транзакции в пространстве конфигурации содержат запросы считывания и запросы записи. Транзакции в пространстве сообщений (или просто сообщения) определены для поддержки передачи данных через сеть между PCIe-агентами.

Поэтому в одном из вариантов уровень 205 транзакций собирает заголовок/полезную нагрузку пакета 206. Формат для заголовков/полезной нагрузки пакетов, действующий на сегодня, можно найти в спецификациях интерфейса PCIe на веб-сайте спецификаций PCIe.

Фиг. 3 иллюстрирует один из вариантов дескриптора транзакции для интерфейса PCIe. В одном из вариантов дескриптор 300 транзакции представляет собой механизм для передачи информации о транзакции. В этом смысле дескриптор 300 транзакции поддерживает идентификацию транзакций в системе. Среди других потенциальных областей использования дескриптора можно указать отслеживание модификаций порядка транзакций по умолчанию и ассоциирование транзакций с каналами.

Дескриптор 300 транзакции содержит поле глобального идентификатора 302, поле 304 атрибутов и поле идентификатора 306 канала. В иллюстрируемом примере показано, что поле глобального идентификатора 302 содержит поле локального идентификатора 308 транзакции и поле идентификатора 310 источника. В одном из вариантов глобальный идентификатор 302 транзакции является уникальным для всех ожидающих выполнения запросов.

Согласно одному из вариантов поле локального идентификатора 308 транзакции представляет собой поле идентификатора, генерируемого запросившим агентом и являющегося уникальным для всех невыполненных запросов, которые нуждаются в выполнении, от этого запросившего агента. Более того, в этом примере идентификатор 310 источника однозначно идентифицирует запросившего агента в иерархии PCIe. Соответственно, вместе с идентификатором 310 источника поле локального идентификатора 308 транзакции обеспечивает глобальную идентификацию транзакции в иерархической области.

Поле 304 атрибутов определяет характеристики и взаимосвязи транзакции. С этой точки зрения поле 304 атрибутов потенциально используется для предоставления дополнительной информации, которая позволяет модифицировать обработку транзакций по умолчанию. В одном из вариантов поле 304 атрибутов содержит поле 312 приоритета, зарезервированное поле 314, поле 316 упорядочения и поле 318 запрета снупинга (несанкционированного вмешательства). Здесь субполе 312 приоритета может быть модифицировано инициатором, чтобы назначить приоритет транзакции. Зарезервированное поле 314 атрибута остается в резерве на будущее или для использования в целях, заданных поставщиком. С применением этого зарезервированного поля атрибутов могут быть реализованы возможные модели использования, применяющие атрибуты приоритета или безопасности.

В этом примере поле 316 атрибута упорядочения используется для передачи информации об опциях, которая несет тип упорядочения и которая может модифицировать правила упорядочения по умолчанию. Согласно одному из примеров реализации атрибут упорядочения, равный "0", обозначает, что следует применять правила упорядочения по умолчанию, тогда как атрибут упорядочения, равный "1", обозначает ослабленные правила упорядочения, где операции записи могут проходить по записям в одном и том же направлении, и завершения считывания могут проходить по записям в одном и том же направлении. Поле 318 атрибута снупинга используется для определения, производится ли снупинг транзакций. Как показано, поле идентификатора 306 канала обозначает канал, с которым ассоциирована транзакция.

Канальный уровень

Канальный уровень 210, также именуемый уровнем 210 канала передачи данных, служит промежуточным уровнем между уровнем 205 транзакций и физическим уровнем 220. В одном из вариантов ответственность уровня 210 канала передачи данных состоит в создании надежного механизма обмена пакетами уровня транзакций (Transaction Layer Packet (TLP)) между двумя компонентами канала связи. Одна сторона уровня 210 канала передачи данных принимает пакеты TLP, собранные уровнем 205 транзакций, присваивает идентификатор 211 последовательности пакетов, т.е. идентификационный номер или номер пакета, вычисляет и применяет код контроля ошибок, т.е. циклически избыточный контрольный код CRC 212, и передает модифицированные пакеты TLP на физический уровень 220 для передачи по физическим линиям связи внешнему устройству.

Физический уровень

В одном из вариантов физический уровень 220 содержит логический субблок 221 и электрический субблок 222 для физической передачи пакета внешнему устройству. Здесь логический субблок 221 отвечает за «цифровые» функции физического уровня 220. Для этого логический субблок содержит передающую секцию для подготовки исходящей информации к передаче посредством физического субблока 222 и приемную секцию для идентификации и подготовки принятой информации перед тем, как передать ее на канальный уровень 210.

Физический блок 222 содержит передатчик и приемник. Передатчик получает символы от логического субблока 221, преобразует эти символы в последовательную форму и передает внешнему устройству. Приемник получает преобразованные в последовательную форму символы от внешнего устройства и преобразует принятые сигналы в поток битов данных. Этот поток битов данных преобразуют из последовательной формы и передают логическому субблоку 221. В одном из вариантов используется код передачи 8b/10b, где передают/принимают 10-битовые символы. Здесь специальные символы используются для разбиения пакета на кадры 223. Кроме того, в одном из примеров приемник генерирует также тактовый сигнал символов, выделенный из входящего последовательного потока данных.

Как указано выше, хотя уровень 205 транзакций, канальный уровень 210 и физический уровень 220 обсуждаются здесь применительно к конкретному варианту стека протоколов PCIe, многоуровневый стек протоков этим не ограничивается. На деле, здесь может быть включен/реализован любой многоуровневый протокол. В качестве примера, порт/интерфейс, представленный в виде многоуровневого протокола, содержит: (1) первый уровень для сборки пакетов, т.е. уровень транзакций; второй уровень для выстраивания последовательности пакетов, т.е. канальный уровень; и третий уровень, для передачи пакетов, т.е. физический уровень. В качестве конкретного примера используется многоуровневый протокол общего стандартного интерфейса (common standard interface (CSI)).

Далее, на Фиг. 4 показаны последовательные двухпунктовые соединения согласно стандарту PCIe. Хотя здесь показан вариант последовательного двухпунктового канала согласно стандарту PCIe, само условие последовательного двухпунктового канала не является столь уж ограничивающим, поскольку оно охватывает любой передающий тракт, позволяющий передавать последовательные данные. В показанном варианте базовый канал связи интерфейса PCIe содержит две пары устройств для работы с низковольтными дифференциальными сигналами: пару передатчиков 406/411 и пару приемников 412/407. Соответственно, устройство 405 содержит передающую логическую схему 406 для передачи данных устройству 410 и приемную логическую схему 407 для приема данных от устройства 410. Другими словами, в канал связи интерфейса PCIe входят два передающих тракта, т.е. тракты 416и417, и два приемных тракта, т.е. тракты 418 и 419.

Передающим трактом называется любой тракт для передачи данных, такой как линия передачи, медный провод, оптическая линия передачи, канал радиосвязи, инфракрасная линия связи или другой тракт связи. Соединение между двумя устройствами, такими как устройство 405 и устройство 410, называется каналом связи, таким как канал 415 связи. Канал связи может поддерживать одну линию - где каждая линия представляет набор пар дифференциальных сигналов (одна пара для передачи и одна пара для приема). Для масштабирования полосы канал связи может агрегировать несколько линий, обозначенных xN, где N - какая-либо поддерживаемая ширина канала, такая как 1, 2, 4, 8, 12, 16, 32, 64 или шире.

Дифференциальная пара обозначает два передающих тракта, таких как проводники 416 и 417, для передачи дифференциальных сигналов. В качестве примера, когда проводник 416 переключается с низкого уровня напряжения на высокий уровень, т.е. происходит восходящий перепад уровней, проводник 417 переходит с высокого логического уровня на низкий логический уровень, т.е. имеет место нисходящий перепад уровней. Дифференциальные сигналы потенциально демонстрируют лучшие электрические характеристики, такие как лучшая целостность сигнала, т.е. меньше перекрестные связи, меньше положительные/отрицательные выбросы напряжения, меньше «звон» и т.д. Это позволяет лучше определить временное окно синхронизации и, тем самым, дает возможность использовать более высокие частоты передачи.

Высокоскоростной канал

Новой редакцией спецификаций ввода/вывода для интерфейса PCIe является стандарт PCIe редакция 4.0 (или PCIe 4.0). При скорости 16 ГТ/с (Гигатранзакций/с) (GT/s) интерфейс PCIe 4.0 имеет целью удвоить полосу соединения по сравнению со стандартом PCIe 3.0, сохраняя при этом совместимость с программными и механическими интерфейсами. Расширение рабочей полосы по сравнению с интерфейсами PCIe предшествующих поколений может обеспечить масштабирование производительности, согласованное с потребностями расширения полосы со стороны разнообразных вновь разрабатываемых приложений, и при этом нацелено на достижение небольшой стоимости, небольшой потребляемой мощности и минимальных возмущений на уровне платформы. Одним из основных факторов широкого применения архитектуры PCIe является ее чувствительность к возможностям массового производства и соответствующим материалам, таким как недорогие печатные платы, дешевые разъемы и т.д.

Скорость передачи данных 16 ГТ/с направлена на достижение оптимального компромисса между производительностью, технологичностью, стоимостью, мощностью и совместимостью. Для выработки рекомендаций о характеристиках для устройств и каналов связи, поддерживающих скорость передачи данных 16 ГТ/с для интерфейса PCIe 4.0, был проведен анализ реализуемости. Анализ PCI-SIG охватывал множество топологий. Например, анализ определил, что достижение скорости 16 ГТ/с при использовании медных проводников, что должно удвоить ширину полосы по сравнению с возможностями интерфейса PCIe 3.0, технически реализуемо при приблизительно таких же уровнях мощности, какие используют интерфейсы PCIe 3.0. Здесь соединения со скоростью передачи данных 16 ГТ/с потенциально могут быть изготовлены с применением типовой кремниевой технологии и развернуты с использованием существующих недорогих материалов и инфраструктуры при сохранении совместимости с архитектурами PCIe предшествующих поколений.

Системы с последовательным вводом/выводом и высокой скоростью передачи данных (например, 16 ГТ/с согласно стандарту PCIe 4.0) должны рассеивать значительную мощность и обладать повышенной сложностью схем, что потенциально ведет к увеличению используемой площади кремния (Si). Эти соображения в перспективе имеют потенциал ограничить интеграцию интерфейсов стандарта PCIe 4.0 (и других подобных высокоскоростных архитектур соединений) в центральные процессоры CPU и системы, использующие увеличенное число линий. В некоторых примерах реализаций, например, ограничения накладываются на длину соединений и число соединителей, используемых в высокоскоростной архитектуре, такой как PCIe 4.0. Например, такое ограничение определено на уровне спецификаций. В одном из примеров, длина соединительного канала связи ограничена одним (1) соединителем и двенадцатью (12) или меньшим числом дюймов.

Наложение ограничений на соединительные каналы связи может ограничить их применимость в некоторых системах. Например, в серверных соединительных приложениях соединения платформы могут достигать в длину двадцать (20) дюймов и более и иметь два соединителя. Если архитектура ограничивает соединительные каналы связи максимальной длиной 12 дюймов и наличием только одного соединителя, придется вводить отдельный кристалл ретранслятора или другое дополнительное устройство для соединения двух каналов по 12 дюймов и адаптации к расстояниям между устройствами, присущим серверной системе, это среди потенциально других примерах.

В некоторых вариантах реализации может быть организован соединительный канал связи, конфигурированный в соответствии со стандартом интерфейса PCIe 4.0 и другими соединениями, допускающий создание имеющего два соединителя канала длиной не меньше двадцати дюймов и при этом все еще поддерживающего скорости передачи данных 16 ГТ/с. Например, схема и соединение могут быть совместно оптимизированы таким образом, чтобы можно было исключить ретрансляторы и другие устройства из более длинных «пролетов» соединительных каналов. Это может помочь снизить производственные затраты, уменьшить задержку ввода/вывода и расширить область применения более широкополосных архитектур с повышенной скоростью на новые, дополнительные приложения. Например, кристалл ретранслятора может содержать передатчик, приемник, тактовый генератор (например, контур фазовой автоподстройки частоты (phase lock loop (PLL))), схему выделения тактового сигнала и ассоциированные функции. Такие компоненты могут использовать ценную площадь на плате. Кроме того, в соединении х16 PCIe 4.0 каждый ретранслятор может рассеивать дополнительную мощность и вносить дополнительные затраты при изготовлении системы, среди прочих потенциальных недостатков. Например, ретрансляторы могут также вносить дополнительную задержку ввода/вывода.

На Фиг. 5 показан пример конфигурации канала связи с двумя соединителями. Например, канал 500 может содержать несколько секций, таких как секции сокета (например, центрального процессора CPU), материнскую плату, расширительную плату, надстроечную плату среди других элементов, через которые может проходить канал связи для соединения двух устройств (например, 505, 510) в системе. Каждая секция канала может иметь свою длину, в этом примере длины секций равны L1=1ʺ, L2=10.5ʺ, L3=0.5ʺ, L4=4ʺ, L5=3ʺ и L6=lʺ, всего 20ʺ для полной длины канала 500. Этот канал связи может быть соединен с каждым из устройств 505, 510 с использованием соответствующего соединителя 515, 520 (в каждом корпусе).

При использовании традиционных способов конфигурация, такая как показана на Фиг. 5, может дать отрицательный запас по всему каналу связи. В одном из примеров может быть создан имеющий два соединителя канал связи длинной 20ʺ, поддерживающий скорость 16 ГТ/с передачи данных (например, 500), минимизирующий эффект столбиков сквозных соединений, минимизирующий эффект сокетов серверных процессоров (SPU), использующий усовершенствованные и обладающие небольшими потерями платы персональных компьютеров (personal computer board (РСВ)) и обеспечивающий увеличение усиления входного блока выполненного на кристалле приемника среди потенциально других признаков, для реализации положительного коэффициента усиления по длине канала связи.

Соединитель может содержать одно или более сквозных соединений, используемых для создания электрических соединений между слоями. Сквозные соединения могут быть использованы, например, для передачи сигналов или питания между слоями печатной платы или компонента. В высокоскоростных системах часть такого сквозного соединения остается поверх соединителя, кристалла или платы, так что эта часть не используется в двухпунктовом канале электрической связи, проходящем через это сквозное соединение. На Фиг. 6 показано упрощенное представление 600 одного или нескольких столбиковых сквозных соединений 605, 610. Сквозное соединение может создать электрические соединения между слоями печатной платы, например, с использованием технологии металлизированных сквозных отверстий (plated through hole (РТН)). Например, сквозные соединения могут электрически соединять штырьки соединителей с внутренними сигнальными слоями (например, дорожками). В примере, показанном на Фиг. 6, часть канала связи может быть реализована с использованием участка (например, 615, 620) металлизированного сквозного отверстия (РТН) для соединения одного отрезка канала связи с другим (например, дорожки (например, 625), проходящей в слое 630 рассматриваемого компонента к другому компоненту, другому сквозному соединению и т.п. по каналу связи). Остальная часть (например, 635) сквозного соединения может считаться столбиком. В высокоскоростных соединениях с использованием сквозных соединений столбик 635 в составе сквозного соединения может создавать резонансные эффекты (например, нули на резонансных частотах), что ведет к деградации сигнала в канале связи (например, в линии). Соответственно, в некоторых вариантах столбики в составе сквозных соединений могут быть «высверлены», как показано поз. 650, чтобы ослабить указанные эффекты. «Высверливание» столбиков в сквозных соединений может удалить столбиковую часть сквозного соединения, являющуюся источником указанных отрицательных электромагнитных эффектов. В некоторых случаях высверливание может быть реализовано уже после изготовления структуры, так что высверленное отверстие имеет больший диаметр по сравнению с первоначальным металлизированным сквозным отверстием (plated through hole (РТН)).

Столбики в сквозных соединениях в двух соединителях, используемых в канале связи длиной 20" со скоростью передачи данных 16 ГТ/с, могут быть удалены или минимизированы, например, посредством высверливания, создания U-образных сквозных соединений и применения других решений. В случае высверливания выбирают тип соединителя на основе того, какой из соединителей является хорошим кандидатом для высверливания. Например, некоторые соединители могут быть механически скомпрометированы и выйти из строя в случае высверливания этих соединителей. Другие типы соединителей, такие как соединители для поверхностного монтажа, могут быть более подходящими.

В дополнение к улучшению электрического качества соединителей посредством высверливания можно улучшить также электрическое качество процессорных (CPU) сокетов, что позволит реализовать каналы связи длиной 20ʺ со скоростью передачи данных 16 ГТ/с. Например, каждый штырек процессорного (CPU) сокета или другого устройства, соответствующий линии канала связи длиной 20ʺ со скоростью передачи данных 16 ГТ/с, соединенный и проходящий сквозь плату с использованием сквозного соединения, может быть высверлен. Длина столбика сокета в таких более длинных имеющих по два соединителя высокоскоростных каналах связи также может быть уменьшена посредством резервирования слоев, расположенных ближе к штырькам, для дорожек, используемых каналом связи. Это может позволить ограничить длину столбика сокета (в сквозном соединении) путем маршрутизации этих линий сквозь такие слои платы.

Процедура минимизации эффектов процессорного сокета CPU может содержать проектирование компоновки выходных штырьков и разрывов платы таким образом, чтобы линии каналов связи длиной 20ʺ со скоростью передачи данных 16 ГТ/с, имели заданный уровень приоритета в этой компоновке. Например, каналы связи могут быть маршрутизированы в слоях таким образом, чтобы сделать высверливание возможным для каждого штырька процессора CPU, соединенного с этим каналом связи длиной 20ʺ со скоростью передачи данных 16 ГТ/с. В качестве альтернативы (или в дополнение) маршрутизация может быть спроектирована таким образом, чтобы каналы связи длиной 20ʺ со скоростью передачи данных 16 ГТ/с использовали слои, позволяющие ограничить длину столбиков сокета.

На Фиг. 7 показано упрощенное представление разреза платы, через которую два устройства 705, 710 соединены с использованием пример канала связи, имеющего два соединителя (такого как канал связи длиной 20ʺ со скоростью передачи данных 16 ГТ/с). В этом примере раскладка штырьков устройств 705, 710 может быть спроектирована таким образом, чтобы можно было применить высверливание без блокирования других выходных каналов связи. Например, внутренние штырьки (например, 715) могут быть рассчитаны на выход в слоях поверх выходов выходных штырьков (например, 720), проложенных в нижних слоях платы. Далее, штырьки могут быть размещены таким образом, чтобы любой штырек, для которого столбик в сквозном соединении должен быть высверлен, (например, штырек для канала связи длиной 20ʺ со скоростью передачи данных 16 ГТ/с) не располагался рядом со сквозным соединением для цепей питания, поскольку высверливание (например, 725a-f) может вызвать риск перфорации плоскостей и профилей питания, что потенциально ведет к образованию, неэффективной сети распределения питания. Кроме того, среди других правил и примеров, штырьки заземления могут быть размещены на основе расположения отверстий, которые могут остаться в плоскостях заземления после высверливания.

В канал длиной 20ʺ с двумя соединителями могут быть введены дополнительные свойства, чтобы скорости передачи данных в канале соответствовали уровню 16 ГТ/с или превосходили его, но при этом коэффициент усиления по всему каналу связи оставался положительным. Например, может быть реализована печатная плата с небольшими потерями, например, такая плата, где дифференциальные вносимые потери дорожки не превышают 0.48 дБ/дюйм на частоте 4 ГГц.

В дополнение к ослаблению эффектов столбиков в соединителях и сокетах обладающего двумя соединителями канала длиной 12ʺ и создания такого канала с использованием печатной платы с небольшими потерями, скорости порядка 16 ГТ/с в канале длиной по меньшей мере 20ʺ могут быть, в некоторых случаях, реализованы путем дополнительного увеличения коэффициента усиления во входном блоке приемника и/или дополнительного «обострения» характеристики в работающем в непрерывном времени линейном корректоре (continuous time linear equalizer (CTLE)). В некоторых примерах входной блок приемника может содержать сочетание аналоговых схем в тракте сигнала данных, включая, например, корректор CTLE, схему автоматической регулировки усиления (AGC (automatic gain control)), корректор с решающей обратной связью (DFE (decision-feedback equalizer)) и/или схему выборки данных (именуемая также схемой выделения срезов данных), среди прочих потенциальных примеров. Например, в одном из вариантов реализации добавление всего приблизительно 6 дБ усиления (например, сверх базового уровня для стандарта PCIe 4.0) во входном блоке приемника и/или в корректоре CTLE может позволить реализовать канал связи длиной 20ʺ со скоростью передачи данных 16 ГТ/с. Реализация вполне скромного коэффициента усиления (например, приблизительно 6 дБ) может быть достигнута ценой лишь вполне умеренного увеличения мощности и сложности схемы, например, путем добавления только одного каскада усиления, среди других примеров. Кроме того, в некоторых системах коэффициент усиления в канале связи может быть настраиваемым или конфигурируемым другим способом. Например, канал связи может быть программируемо настроен для приложений, где используются скорости порядка 16 ГТ/с, и это дополнительное усиление может быть отключено для приложений, использующих меньшие скорости передачи данных, среди других примеров.

Надежность, работоспособность и удобство эксплуатации (Reliability, Availability, and Serviceability (RAS))

В некоторых вариантах архитектура соединений, такая как PCIe, может содержать средства для улучшения показателей надежности, работоспособности и удобства эксплуатации (Reliability, Availability, and Serviceability (RAS)) системы. Хотя этот принцип может быть применен для всех скоростей передачи данных, некоторые архитектуры могут применять специальные схемы кодирования при работе с повышенными скоростями передачи данных. Например, интерфейс PCIe 4.0 (равно как и интерфейс PCIe редакция 3.0) использует схему кодирования 128b/130b, например, для скоростей передачи данных, превосходящих 8 ГТ/с. В схеме 128b/130b информацию о четности для каждой линии передают посредство упорядоченного множества пропусков (SKP (или "skip") Ordered Set (SKP OS)) с целью идентификации, какие именно линии в канале связи могут оказаться не справившимися с выполнением упреждающего анализа и потому должны будут работать с уменьшенной шириной канала связи, если применимо, среди других примеров. Четность линий может быть эффективным инструментом для идентификации ошибок в конкретных линиях в канале связи, однако, в некоторых случаях, когда канал связи преимущественно находится в состоянии простоя (например, в канале связи передают только логические кадрирующие маркеры простоя (IDL)), возможна ситуация, когда способность обнаружения ошибок с использованием бита четности окажется подорванной, поскольку ошибки в кадрирующем маркере (например, IDL) могут привести к восстановлению канала связи, которое устраняет информацию о четности вплоть до этого момента. В механизмах обнаружения ошибок в традиционных архитектурах могут существовать «слепые пятна», которые могут вызвать недооценку ошибок. Например, архитектура соединений может не определить или вообще оказаться неспособной определить неисправные линии, связанные с обнаруженными ошибками кадрирующих маркеров, среди других недостатков.

В некоторых архитектурах может быть создан регистр для идентификации ошибок, обнаруженных или предполагаемых в канале связи, равно как, в некоторых случаях, конкретных линий, где произошли ошибки. Например, как показано на Фиг. 8, интерфейс PCIe может создать регистр 805 состояния ошибок линий (Lane Error Status (LES)) в связи со структурой возможностей, такой как структура вторичных расширенных возможностей интерфейса PCIe (Secondary PCIe Extended Capability). Такая структура 800 возможностей может содержать заголовок 810 вторичных расширенных возможностей интерфейса PCIe (Secondary PCIe Extended Capability Header), Регистр 815 управления каналом связи 3 (Link Control 3 Register) и регистр 820 управления коррекцией (Equalization Control Register) в дополнение к регистру 805 LES. В некоторых вариантах этот регистр LES может содержать 32-битовый вектор, где каждый бит соответствует, например, линии в канале связи (идентифицированной номером линии) и указывает, обнаружена ли в соответствующей линии ошибка. В стандарте PCIe определен ряд ошибок, которые могут привести к появлению сообщения о событии ошибки в регистре LES. Например, как описывается выше, четность данных может быть реализована посредством бита четности, входящего в множество SKP OS и указывающего, обнаружена ли положительная четность в полезной нагрузке всех блоков данных, переданных после скремблирования после последней последовательности SKP OS (или упорядоченной последовательности начала потока данных (Start of Data Stream (SDS) Ordered Set)), среди других примеров. Четность данных может быть вычислена для каждой линии независимо. Приемные и передающие устройства вычисляют четность данных одинаковым способом, и приемник сравнивает вычисленную им четность для каждой линии с четностью, вычисленной в передатчике (как это обозначено битом четности) с целью идентификации потенциальных ошибок. Например, если вычисленная и принятая величины не совпадают, может быть задан бит в регистре LES (например, соответствующий номеру линии, где обнаружено несовпадение).

Как обсуждается выше и иллюстрируется упрощенным представлением 900, показанным на Фиг. 9, данные можно передавать по двум или более линиям в составе канала передачи данных. Например, как показано в примере интерфейса PCIe, базовым объектом передачи данных может быть символ, такой как символ, реализованный в виде 8-битового знака данных. Полезная нагрузка блока данных представляет собой поток символов, определенный как поток данных, который может содержать кадрирующие маркеры, пакеты уровня транзакций (TLP), пакеты канального уровня передачи данных (DLLP) и т.п. Каждый символ потока данных может быть помещен в одну линию канала связи для передачи, так что этот поток символов оказывается распределен «полосками» по всем линиям канала передачи данных и занимает промежуток между границами блока. Далее, в некоторых случаях физических уровень может использовать блочный код по линиям. Каждый блок может содержать двухбитовый синхронизационный заголовок и полезную нагрузку. В стандарте PCIe определены два действующих вида кодирования синхронизационного заголовка: 10b и 01b, что определяет тип полезной нагрузки, которую содержит блок. Например, синхронизационный заголовок 10b может указывать на блок данных, а синхронизационный заголовок 01b может указывать на блок упорядоченного множества. В качестве примера, на Фиг. 9 показана передача потока данных по четырем линиям (Lane) 0, 1, 2 и 3. Все линии многолинейного канала связи передают блоки с одинаковым синхронизационным заголовком одновременно. Порядок передачи битов может начинаться с синхронизационного заголовка (представленного как "Н1Н0", помещенного в линию как "Н0-Н1"), за которым следует первый символ, представленный как "S7-S6-S5-S4-S3-S2-S1-S0", помещенный в линию, начиная с "S0" и заканчивая "S7".

Интерфейс PCIe предоставляет приемнику опцию сообщать регистрам LES об ошибках, соответствующих рассогласованным или недействительным синхронизационным заголовкам в потоке данных. Например, определение, что одна или несколько линий (например, во время первых двух элементов UI в потоке данных) содержит синхронизационный заголовок, имеющий недействительную величину, (например, 00b, 11b) может быть идентифицировано как ошибка в линии, о которой может быть сообщено в регистр LES, среди других примеров.

На Фиг. 10 показаны представления примеров кадрирующих маркеров 1005, 1010, 1015, 1020, 1025. Кадрирующий маркер (или «маркер» ("token")) может представлять собой объект инкапсуляции данных на физическом уровне, который задает или подразумевает число символов, ассоциированных с этим маркером, и тем самым идентифицирует положение следующего кадрирующего маркера. Кадрирующий маркер в потоке данных может располагаться в первом символе (символ 0) первой линии (например, Линии 0) первого блока данных в потоке данных. В одном из примеров интерфейс PCIe определяет пять кадрирующих маркеров и в том числе маркер 1005 начала пакета TLP (STP), маркер 1010 конца потока данных (EDS), маркер 1015 конечного дефекта (EDB), маркер 1020 начала пакета DLLP (SDP) и логический маркер 1025 простоя (IDL). Маркер 1005 STP может иметь длину четыре (4) символа, и за ним может следовать информация канального уровня передачи данных. Пример маркера 1010 EDS может иметь длину четыре (4) символа и может указывать, что следующий блок будет блоком упорядоченного множества. Маркер 1015 EDB также может иметь длину четыре (4) символа и может подтверждать, что пакет TLP был «плохим» (дефектным) и потому был исключен. Маркер EDB может всегда следовать за данными пакета TLP. Далее, маркер 1020 SDP может быть короче, два (2) символа в длину, и за ним может следовать информация пакета DLLP. Наконец, в этом примере маркер 1025 может представлять собой один символ и может быть передан, когда по каналу связи не передают пакеты TLP, DLLP или другие кадрирующие маркеры.

Фиг. 11 иллюстрирует представление 1100, показывающее пример данных, передаваемых по каналу связи х8, иллюстрируя признаки потока данных, определяемые в соответствии с конкретной архитектурой соединений, такой как архитектура PCIe. В этом примере данные могут содержать передачу упорядоченного множества SKP. Поток в этом примере может начаться с передачи синхронизационных заголовков HI НО=10b, указывающих на блок данных. Соответственно кадрирующий маркер STP может быть передан в качестве первого символа 0 в Линиях 0-3 для указания начала потока пакетов TLP. За данными пакетов TLP может следовать циклически избыточный контрольный код канала передачи данных (link cyclic redundancy check (LCRC)), а за ним может следовать заголовок SDP, указывающий, что далее должны быть переданы данные пакета DLLP (например, в Символах 3-4). В связи с этими данными пакета DLLP могут быть также переданы данные циклически избыточного контрольного кода (CRC).

В примере, показанном на Фиг. 11, логические маркеры простоя (IDL) передают, когда не происходит передача данных по каналу передачи данных в течение ряда элементов UI. Затем может быть передан маркер EDS для указания перехода к упорядоченному множеству данных в линиях. Например, другой синхронизационный заголовок (например, 1105) может быть передан в виде кода "01b" для указания, что следующие блоки данных будут блоками данных упорядоченного множества. В этом конкретном примере передаваемое упорядоченное множество представляет собой упорядоченное множество (OS) SKP. Как отмечено выше, в некоторых вариантах множество SKP OS может содержать бит четности, являющийся указанием состояния четности для каждой линии (например, Линии 0-7) канала передачи данных. Множество SKP OS может далее иметь заданную компоновку, идентифицируемую приемником. Например, в случае применения кодирования 128b/130b в интерфейсе PCIe, множество SKP OS может в базовом варианте содержать шестнадцать символов. Какой-либо порт может добавить или удалить группу из четырех символов SKP, так что множество SKP OS может иметь размер 8, 12, 16, 20 или 24 символа и т.п. Далее, в линии может быть передан символ SKPEND, как показано на Фиг. 11, для указания местонахождения конца множества SKP OS и положения синхронизационного заголовка следующего блока, который нужно передать по линиям, среди других примеров.

В некоторых примерах вариантов может быть создана логическая схема для обнаружения дополнительных ошибок линий в архитектуре соединений. Программное обеспечение в системе может контролировать регистр, такой как регистр LES, для отслеживания ошибок по принципу линия за линией в течение некоторого периода времени. Одна ошибка лини может еще не означать, что есть проблемы с ошибками. Однако если ошибки появляются со статистически значимой частотой в одной или нескольких конкретных линиях канала передачи данных, системное программное обеспечение может определить факт наличия потенциальной проблемы применительно к этим конкретным линиям. Далее в некоторых вариантах могут быть приняты корректирующие меры, чтобы избежать передачи по меньшей мере некоторых системных данных по линии, склонной к ошибкам, например, путем реконфигурирования канала передачи данных, генерации уведомления для более внимательной проверки канала передачи данных, среди других примеров. Некоторые ошибки может быть трудно обнаружить при проверке линия за линией. Хотя уже разработаны некоторые механизмы для обнаружения части ошибок в канале передачи данных и передачи сообщений об этих ошибках (например, на основе четности или неправильных синхронизационных заголовков), другие признаки архитектуры и правила могут быть привлечены для идентификации таких дополнительных правил, специфичных для каких-то линий. Об этих ошибках также может быть извещен регистр с целью учета вместе с отчетами о традиционных ошибках линий и построения более полной картины исправности индивидуальных линий в канале передачи данных, среди других примеров и соображений.

В первом примере, как и в примере интерфейса PCIe, описанном выше, если линия принимает блок упорядоченного множества с недействительным (несогласованным, неправильным или по другой причине неожиданным) маркером EDS, непосредственно предшествующим этому блоку, можно предполагать наличие ошибки в линии, где был обнаружен недействительный маркер EDS. Далее, об ошибке, относящейся к недействительному маркеру EDS в линии, может быть сообщено регистру ошибок, например, посредством установления соответствующего бита в регистре LES интерфейса PCIe.

В другом примере заданный формат для конкретного упорядоченного множества может быть использован для идентификации дополнительных ошибок линий. Например, множество SKP OS может содержать хорошо определенные символы SKP, пока не будут переданы символы SKPEND для идентификации конца упорядоченного множества. Если в конкретной линии будет обнаружен недействительный или неправильный символ SKP в пределах совокупности ожидаемых символов SKP из состава этого упорядоченного множества (и прежде символов SKPEND), идентификация этого ошибочного символа SKP может быть использована для запуска передачи сообщения об ошибке в указанной конкретной линии регистру ошибок, такому как регистр LES. Кроме того, заданные моменты времени поступления символов конкретного множества OS также могут быть использованы для идентификации того, что в какой-то линии был принят неожиданный символ. Например, продолжая пример упорядоченных множеств SKP, поскольку число символов в упорядоченном множестве SKP OS должно быть кратно четырем, отсутствие приема символа SKP_END на месте символа 8, 12, 16, 20 или 24 в одной или нескольких конкретных линиях канала передачи данных может привести к установлению соответствующего бита для этих конкретных линий в регистре ошибок, среди других потенциальных примеров.

В некоторых вариантах реализации могут возникать и могут быть обнаружены разнообразные ошибки кадрирования. Например, при обработке символов, которые, как ожидается, должны представлять собой кадрирующий маркер, прием символа или последовательности символов, которые не соответствуют определению кадрирующего маркера, может быть ошибкой кадрирования. Кроме того, некоторые кадрирующие маркеры могут быть заданы для следования после данных других типов, тогда неожиданный приход (или задержка прихода) конкретного кадрирующего маркера может быть ошибкой кадрирования. В качестве всего лишь одного из примеров, может быть задано, что маркер EDB должен быть принят сразу же после пакета TLP, а прием маркера EDB в любое другое время (отличное от момента сразу же после пакета TLP) может инициировать ошибку кадрирования, среди многих других примеров, такой как ошибки кадрирования, которые определены в спецификациях стандарта PCIe. Хотя ошибки кадрирования могут быть определены внутри системы, в некоторых вариантах ошибки кадрирования не определяют по принципу линия за линией или не отображают на конкретную линию канала передачи данных. Действительно, в некоторых случаях ошибка кадрирования может вызвать инициирование восстановления канала передачи данных, еще более затрудняя обнаружение ошибок линии, когда при восстановлении канала передачи данных происходит удаление результатов вычисления четности и отчетов (например, через бит четности, передаваемый во множестве SKP OS), среди других примеров.

В некоторых вариантах реализации логические схемы в составе логического физического уровня PHY (например, в приемнике) могут дополнительно идентифицировать неисправную линию на основе кадрирующего маркера. В первом примере могут быть заданы символы кадрирующего маркера (как это показано в примерах на Фиг. 10) и может быть идентифицирована ошибка в одном из символов, величина которого отличается от ожидаемой величины, равно как может быть определена линия, в которой идентифицирован ошибочный символ маркера. Например, может быть идентифицирован первый символ кадрирующего маркера, и если этот символ не совпадает с первым символом какого-либо одного из совокупности заданных кадрирующих маркеров для физического уровня (PHY), может быть передан сигнал ошибки. Эта ошибка может быть зарегистрирована, например, в регистре LES. В примере кадрирующих маркеров стандарта PCIe, если первый символ принятого кадрирующего маркера не совпадает с первым символом, заданным для какого-либо из маркеров IDL, SDP, STP, EDB или EDS в стандарте PCIe, может быть определено наличие ошибки в линии, где появился ошибочный первый символ кадрирующего маркера, и эта ошибка может быть зарегистрирована в регистре ошибок линии, соответствующего идентифицированной линии.

Второе, в другом примере, кадрирующие маркеры IDL, поскольку длина такого маркера составляет только один символ, могут быть заданы для передачи по всем линиям канала передачи данных, когда не происходит передача какого-либо пакета TLP, DLLP или другого кадрирующего маркера. Соответственно, когда первый маркер IDL появился в одной из линий канала передачи данных, имеющего четыре или более линий, можно ожидать, что такие маркеры IDL появятся также в Линиях с номерами n+1, n+2 и n+3 (здесь для первой Линии n (n modulo 4=0)). После передачи маркера IDL первый символ маркера STP или SDP может быть задан для передачи в Линию 0 во время следующего символа. Соответственно, с учетом этих ограничений на использование и ожидаемого применения маркеров IDL, если маркер IDL не повторяется, как ожидалось, или если первый маркер IDL появится в неправильной линии, может быть идентифицирована линия, где появился не повторяющийся маркер IDL или другой ошибочный символ, и также зарегистрирована в регистре ошибок, таком как регистр LES, как ошибка для конкретной линии.

Еще в одном примере может быть определена конкретная длина маркера EDB, такая как четыре символа в стандарте PCIe. Вследствие этого ошибка кадрирования может быть результатом идентификации первого символа EDB, а затем отсутствия идентификации дополнительных символов EDB в непосредственно следующих символах в пределах этой заданной длины. Например, в интерфейсе PCIe, если кадрирующий маркер EDB обнаружен в Линии n (n modulo 4=0), сразу же после пакета TLP, но не обнаружен в какой-либо из Линий n+1, n+2 или n+3, может быть передано сообщение об ошибке в регистр ошибок той линии (например, Линии n+1, n+2 или n+3), где не появился ожидаемый действительный символ EDB. Кроме того, может быть задано, что первый символ любого маркера EDB должен быть помещен сразу же после потока пакета TLP, а это означает, что предшествующий кадрирующий маркер, а именно маркер STP, был последним кадрирующим маркером, появившимся в канале передачи данных. Соответственно, ошибка в Линии n может быть идентифицирована и сообщена регистру ошибок, когда в этой Линии n появился первый символ маркера EDB, но самый последний предшествующий ему кадрирующий маркер отличался от маркера STP, среди других примеров.

Аналогично ошибке кадрирования маркера EDB ошибки кадрирования могут быть следствием отклонений длины, формата и позиции других кадрирующих маркеров. Например, в другом случае, где первый символ маркера SDP обнаружен в Линии n, в соответствии с правилами размещения действительных маркеров SDP (например, перед трафиком пакетов DLLP), но символ в Линии n+1 не совпадает с ожидаемым вторым символом маркера SDP, логическая схема физического уровня (PHY) может идентифицировать ошибку в Линии n+1 и зарегистрировать эту ошибку в регистре ошибок.

На Фиг. 12 представлена упрощенная блок-схема, иллюстрирующая расширенный способ обнаружения и регистрации ошибок линий (например, 1205, 1210, 1215, 1220, 1225, 1230, 1235, 1240) в примере регистра 1250 ошибок, таком как регистр LES интерфейса PCIe, соответствующий каналу передачи данных. Например, в дополнение к сообщениям об ошибках 1205 синхронизационных заголовках в линиях и ошибках 1210 битов четности, могут быть обнаружены и другие ошибки и в том числе ошибки упорядоченных множеств в линиях, таких как ошибка 1215 в виде появления блока OS без предшествующего маркера EDS и ошибка 1220 множества SKP OS (такая, как описано в примерах выше). Возможно также сообщения о других ошибках, включая, например, ошибки кадрирующих маркеров в линиях, такие как ошибки 1225 первого символа кадрирующего маркера, ошибки 1230 кадрирующего маркера IDL (например, относящиеся к правильному повторению маркера IDL после первоначального маркера IDL в Линии n), ошибки 1235 кадрирующего маркера EDB (например, включая ошибки размещения символов маркера EDB, как это описано, например, в предшествующем обсуждении) и ошибки 1240 кадрирующего маркера SDP (например, включая ошибку, обнаруженную во втором символе какого-либо маркера SDP), среди других потенциальных примеров использования правил, заданных для упорядоченных множеств, блоков данных и кадрирующих маркеров в архитектуре.

Как отмечено выше, в некоторых случаях ошибки или другие события, вызывающие принудительное восстановление канала передачи данных, могут отрицательно повлиять на работу механизмов обнаружения ошибок линий, таких как определение четности. Как отмечено выше, приемные и передающие устройства могут определять четность для потока данных или другого потока, а информация о четности, вычисленная передатчиком, может быть сообщена приемнику для сравнения этой принятой информации о четности с соответствующей информацией о четности (для линии), вычисленной приемником для того же самого потока данных. Информацию о четности можно передавать периодически. Например, может быть передано множество SKP OS, содержащее один или несколько битов четности в символах SKP OS, служащих индикацией четности, вычисленной передатчиком для каждой линии. В некоторых традиционных системах, однако, восстановления канала передачи данных или другие события могут привести к стиранию информации о четности и/или перезапуска процедуры определения четности прежде, чем ранее вычисленная информация о четности будет сообщена приемнику. Соответственно, в таких случаях информация об ошибках, обнаруженных для конкретной линии на основе информации о четности, также может быть утрачена, а сообщения об этих ошибках переданы не будут, что отрицательно влияет на точность передачи сообщений об ошибках для этой конкретной линии.

В одном из вариантов информация о четности может быть сохранена путем задания режима, в котором восстановлению канала передачи данных автоматически предшествует передача множества SKP OS или другого множества данных, содержащего данные сообщения информации о четности для каждой линии в канале передачи данных, подлежащем восстановлению. Например, протокол восстановления канала передачи данных может быть переопределен таким образом, чтобы передавать множество SKP OS (включая биты четности) в ответ на ошибку кадрирования или другое событие, запускающее процедуру восстановления канала передачи данных. Тем самым множество SKP OS может передавать информацию о четности, вычисленную передатчиком вплоть до момента, когда произошел запуск процедуры восстановления канала передачи данных, что позволяет приемнику идентифицировать потенциальные ошибки линии на основе информации о четности.

В одном из примеров, информация о четности может быть передана перед восстановлением путем передачи множества SKP OS перед тем, как канал передачи данных покинет активное (например, L0) состояние для входа в режим восстановления. Например, каждый передатчик может передать множество SKP OS (например, в соответствии с заданными интервалами, такими как максимальный интервал между передачами множеств SKP OS) и затем передать дополнительный блок данных с маркером EDS перед тем, как войти в режим восстановления. Это может обеспечить получение приемником информации о четности для предшествующих принятых им блоков данных, включая один или несколько блоков данных, которые могли вызвать ошибку кадрирования. После этого приемник может зарегистрировать ошибку в подходящем регистре LES, если сравнение битов четности укажет на присутствие ошибки.

В другом примере, вместо того, чтобы преждевременно «выгружать» информацию о четности перед восстановлением или другим событием (например, в попытке гарантировать, что информация о четности будет передана прежде, чем она окажется утраченной), информация о четности, такая как информация о четности для множества SKP OS, может быть расширена так, чтобы охватывать четность потоков данных, пока канал передачи данных остается активным (например, "LinkUp=1b" в интерфейсе PCIe). Далее, информация о четности может сохраняться постоянно для каждой линии канала передачи данных, таким образом, эта информация о четности сохраняется в течение всего события восстановления. Там, где традиционное восстановление канала передачи данных должно было бы вызвать утрату информации о четности для предшествующего блока данных (например, прерванного процедурой восстановления), постоянное сохранение информации о четности может позволить сохранить информацию о четности в течение всей процедуры восстановления и передать ее после завершения восстановления (например, в первом множестве SKP OS после восстановления). Кроме того, в некоторых случаях информация о четности для новых блоков данных, передаваемых после восстановления канала передачи данных, (и перед следующим множеством SKP OS) также может быть определена и в некоторых случаях добавлена к информации о четности, сохраненной перед восстановлением, после чего эта объединенная информация о четности может быть передана, например, в следующем множестве SKP OS, среди других примеров.

Следует понимать, что рассмотренные выше примеры не являются ограничивающими, а приведены только с целью иллюстрации некоторых принципов и признаков. Далее, некоторые системы могут содержать различные сочетания из двух или более рассмотренных выше признаков и компонентов. В качестве примера, система может содержать сочетания ряда функций обнаружения ошибок, описываемых выше, таких как рассмотренные выше функции обнаружения ошибок линий.

На Фиг. 13A-13D показаны примеры логических схем 1300a-d, иллюстрирующих примеры способов обнаружения ошибок в линиях канала передачи данных. Например, на Фиг. 13А, данные могут быть приняты 1305 по каналу передачи данных, содержащему несколько линий. Эти данные могут содержать символы, причем эти символы можно контролировать для определения 1310, являются ли один или несколько символов ошибочными символами. Ошибочный символ может быть символом кадрирующего маркера (например, EDB, EDS, STP, IDL, SDP и т.п.), упорядоченного множества (например, SKP OS и т.п.) или другой определенной последовательности, имеющим неправильную величину, следующим в неправильном или неожиданном порядке, передаваемым по неправильной или неожиданной линии, не принадлежащим конкретной заданной последовательности, среди других примеров. Может быть идентифицирована 1315 линия, по которой был передан ошибочный символ, и затем может быть передано 1320 сообщение об ошибке в идентифицированной линии, например, в регистр ошибок линии, на основе этого ошибочного символа, среди других примеров.

В схеме, показанной на Фиг. 13В, могут быть переданы 1325 данные по каналу передачи данных, содержащему несколько линий. Для каждой линии в составе этого канала передачи данных может сохраняться 1330 информация о четности. В ответ на идентификацию 1335, что канал передачи данных должен выйти из активного состояния, (например, в связи с восстановлением этого канала) может быть передана 1340 информация о четности перед выходом рассматриваемого канала передачи данных из активного состояния. В одном из примеров индикация информации о четности может быть включена в биты четности передаваемого получателю упорядоченного множества, такого как множество SKP согласно стандарту PCIe. Индикация информации о четности может быть использована (например, получателем конкретной информации) для сравнения этой информации о четности с информацией о четности, принятой этим получателем. Несовпадения в информации о четности могут быть идентифицированы как свидетельства ошибки в линии, соответствующей зафиксированному несовпадению информации о четности.

В примере, показанном на Фиг. 13С, данные могут быть переданы 1345 по линиям канала передачи данных, и может быть определена 1350 информация о четности для каждой из линий на основе данных, идентифицированных в этой линии. При этом возможны события восстановления канала передачи данных, а информация о четности может сохраняться 1355 во время такого восстановления. После восстановления может быть передано 1370 указание информации о четности, которая может быть основана на информации о четности, сохранявшейся во время восстановления канала передачи данных. В качестве опции по каналу передачи данных после восстановления могут быть переданы дополнительные данные, а информации о четности для каждой линии может быть определена на основе этих данных, переданных после восстановления. Информация о четности для каждой линии может быть обновлена 1365 на основе данных, переданных в этой линии до и после восстановления, а переданное 1370 сообщение с информацией о четности может служить индикатором такой объединенной информации о четности.

В соответствии с примером, показанным на Фиг. 13С, согласно схеме, показанном на Фиг. 13D, по каналу передачи данных могут быть приняты 1375 первые данные, и может быть определена 1380 первая информация о четности для каждой линии на основе данных, принимаемых по этим линиям. Эта информация о четности может быть сохранена 1385 в процессе восстановления канала передачи данных после приема первых данных. После восстановления канала передачи данных могут быть приняты 1398 вторые данные о четности, как это идентифицировано в битах четности принятого упорядоченного множества SKP. Эти вторые данные о четности можно сравнить с информацией о четности, сохраняемой в процессе (и за пределами) восстановления канала передачи данных. В некоторых случаях сохраненная информация о четности может быть обновлена 1394 для учета информации о четности, вычисленной для линий на основе вторых данных, принятых 1390 в этих линиях после восстановления канала передачи данных (например, согласно обновлению информации о четности в соответствующем передатчике на основе передач данных после восстановления), среди других примеров.

Следует отметить, что хотя значительная часть приведенных выше принципов и примеров описаны здесь в контексте стандарта интерфейса PCIe и конкретных редакций спецификаций этого интерфейса PCIe, принципы, технические решения и признаки, описываемые здесь, могут быть в равной степени применимы к другим протоколам и системам. Например, аналоговые ошибки линий могут быть обнаружены в других каналах передачи данных с использованием других протоколов на основе аналоговых символов, потоков данных и маркеров, равно как правил, заданных для использования, размещения и форматирования таких структур в составе данных, передаваемых по этим другим каналам. Кроме того, альтернативные механизмы и структуры (например, помимо регистра LES интерфейса PCIe или множества SKP OS) могут быть использованы для обнаружения ошибок и передачи сообщений функциональным устройствам в пределах системы. Более того, в системах могут быть применены сочетания приведенных выше решений, включая сочетания логических и физических усовершенствований в канале передачи данных и в соответствующих логических устройствах этого канала, как они описаны здесь, среди других примеров.

Отметим, что рассмотренные выше устройства, способы и системы могут быть реализованы в каком-либо электронном устройстве или системе, как отмечено ранее. В качестве конкретных иллюстраций рассмотренные ниже чертежи предлагают примеры систем, использующих настоящее изобретение. В ходе приведенного ниже более подробного описания указанных систем будут рассмотрены различные соединения, в том числе посредством повторных обращений к уже приведенному выше обсуждению. И, как легко понятно, описанные выше усовершенствования могут быть применены к любым из этих соединений, структур и архитектур.

На Фиг. 14 представлен вариант блок-схемы компьютерной системы, содержащей многоядерный процессор. Процессор 1400 представляет собой какой-либо процессор или процессорное устройство, такое как микропроцессор, встроенный процессор, цифровой процессор сигнала (digital signal processor (DSP)), сетевой процессор, ручной процессор, процессор приложений, сопроцессор, систему на кристалле (system on a chip (SOC)) или другое устройство для выполнения кода. Процессор 1400 в одном из вариантов содержит по меньшей мере два ядра - ядро 1401 и ядро 1402, которые могут быть асимметричными ядрами или симметричными ядрами (иллюстрируемый вариант). Однако процессор 1400 может содержать произвольное число процессорных элементов - симметричных или асимметричных.

В одном из вариантов термин «процессорный элемент» обозначает аппаратуру или логическое устройство для поддержки выполнения потоков программного обеспечения. К примерам аппаратных процессорных элементов относятся: потоковый модуль, потоковый слот, поток, процессорный модуль, контекст, контекстный модуль, логический процессор, аппаратный поток, ядро и/или какой-либо другой элемент, способный иметь и сохранять состояние процессора, такое как состояние выполнения или архитектурное состояние. Другими словами, процессорный элемент в одном из вариантов обозначает какую-либо аппаратуру, способную быть независимо ассоциированной с кодом, таким как программный поток, операционная система, приложение или другой код. Термин «физический процессор» (или процессорный сокет) обычно обозначает интегральную схему, которая потенциально содержит какое-либо число других процессорных элементов, таких как ядра или аппаратные потоки.

Термин «ядро» часто обозначает логическую схему, расположенную в составе интегральной схемы и способную сохранять независимое архитектурное состояние, где каждое независимо сохраняемое архитектурное состояние ассоциировано по меньшей мере с некоторыми выделенными исполнительными ресурсами. В отличие от ядер термин «аппаратный поток» обозначает какую-либо логическую схему, расположенную в составе интегральной схемы и способную сохранять независимое архитектурное состояние, где эти независимо сохраняемые архитектурные состояния совместно используют доступ к исполнительным ресурсам. Как можно видеть, когда какие-то ресурсы используются совместно, а другие ресурсы специально выделены для какого-то архитектурного состояния, происходит наложение линий между номенклатурой аппаратных потоков и ядер. Также часто операционная система видит ядро и аппаратный поток как индивидуальные логические процессоры, так что эта операционная система может индивидуально планировать операции для каждого логического процессора.

Физический процессор 1400, как показано на Фиг. 14, содержит два ядра - ядро 1401 и ядро 1402. Здесь ядра 1401 и 1402 считаются симметричными ядрами, т.е. ядрами с одинаковыми конфигурациями, функциональными модулями и/или логическими структурами. В другом варианте ядро 1401 представляет собой процессорное ядро для внеочередного (не по порядку) выполнения команд, а ядро 1402 представляет собой процессорное ядро с очередным (по порядку) выполнением команд. Однако для ядер 1401 и 1402 можно индивидуально выбирать какой-либо из типов ядер, таких как собственное, естественное ядро, программно управляемое ядро, ядро для выполнения собственной структуры системы команд (Instruction Set Architecture (ISA)), ядро для выполнения транслированной структуры системы команд (ISA), ядро совместного проектирования или другое известное ядро. В среде с гетерогенными ядрами (т.е. с асимметричными ядрами) некоторые формы трансляции, такие как двоичная трансляция, могут быть использованы для планирования или выполнения кода на одном или обоих ядрах. При этом функциональные модули, показанные в ядре 1401, более подробно описаны ниже, тогда как в представленном варианте модули, изображенные в ядре 1402, работают аналогичным образом.