Изобретение откосится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов в схемах приемопередатчиков мультиплексного канала передачи данных, драйверах кабельных модемов, буферах АЦП и ЦАП, активных фильтрах и т.п.

Известны схемы операционных усилителей (ОУ) с входными каскадами на основе двухтактных эмиттерных повторителей на комплементарных биполярных транзисторах, связанных с промежуточным каскадом, реализованным на основе двух токовых зеркал [1-10]. Более высокочастотными являются ОУ, в которых во входных каскадах используется каскодная схема [11-13].

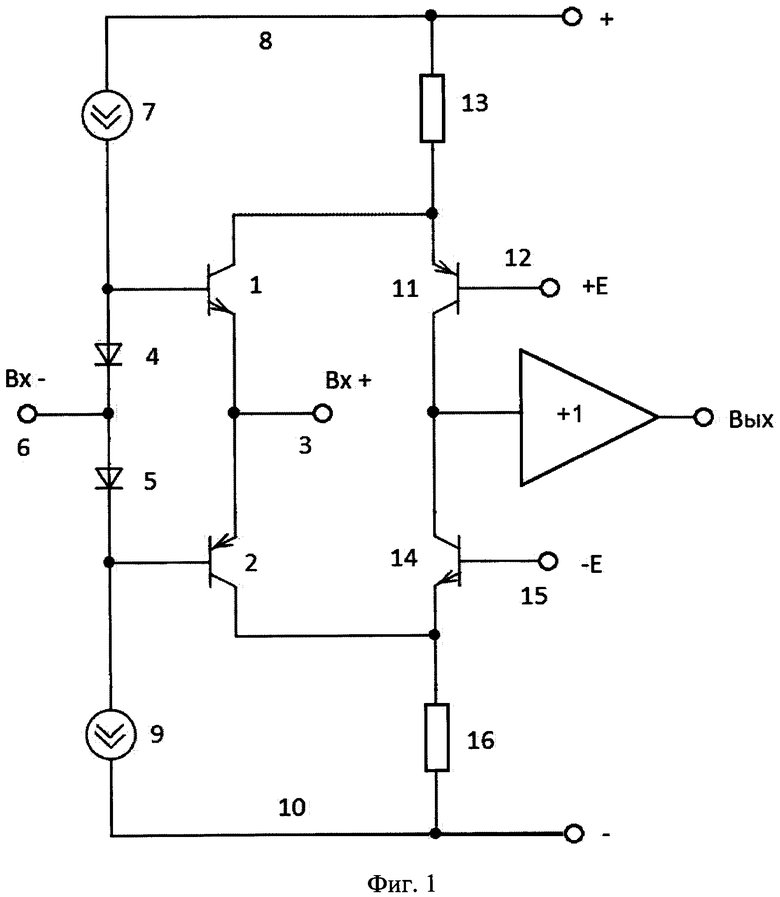

Прототипом (фиг. 1) заявляемого устройства является операционный усилитель, описанный в патент US 7479831, fig. 7 [11], содержащий первый 1 и второй 2 входные транзисторы, эмиттеры которых соединены с неинвертирующим входом 3 устройства, первый 4 и второй 5 последовательно соединенные прямосмещенные р-n переходы, включенные между базами первого 1 и второго 2 входных транзисторов, инвертирующий 6 вход устройства, первый 7 токостабилизирующий двухполюсник, включенный между базой первого 1 входного транзистора и первой 8 шиной источника питания, второй 9 токостабилизирующий двухполюсник, включенный между базой второго 2 входного транзистора и второй 10 шиной источника питания, первый 11 выходной транзистор, база которого соединена с первым 12 вспомогательным источником напряжения питания, а эмиттер соединен с коллектором первого 1 входного транзистора и через первый 13 токостабилизирующий резистор связан с первой 8 шиной источника питания, второй 14 выходной транзистор, база которого соединена со вторым 15 вспомогательным источником напряжения питания, а эмиттер соединен с коллектором второго 2 входного транзистора и через второй 16 токостабилизирующий резистор связан со второй 10 шиной источника питания, причем коллекторы первого 11 и второго 14 выходных транзисторов связаны с токовым выходом устройства.

Существенный недостаток известного ОУ состоит в том, что он характеризуется невысоким быстродействием при импульсных входных сигналах и низким значением ширины полосы пропускания сигнала. Это обусловлено повышенной склонностью этого ОУ к возбуждению, для препятствования чему необходимо существенно увеличивать емкость коррекции, что приводит к снижению быстродействия ОУ.

Основная задача предлагаемого изобретения состоит в создании операционного усилителя с улучшенными динамическими свойствами входного каскада, что обеспечивается созданием дополнительных каналов преобразования входного напряжения в выходной ток ОУ, повышающих при прочих равных условиях крутизну усиления входного каскада.

Технический результат - увеличение ширины полосы пропускания и повышение быстродействия при импульсных входных сигналах.

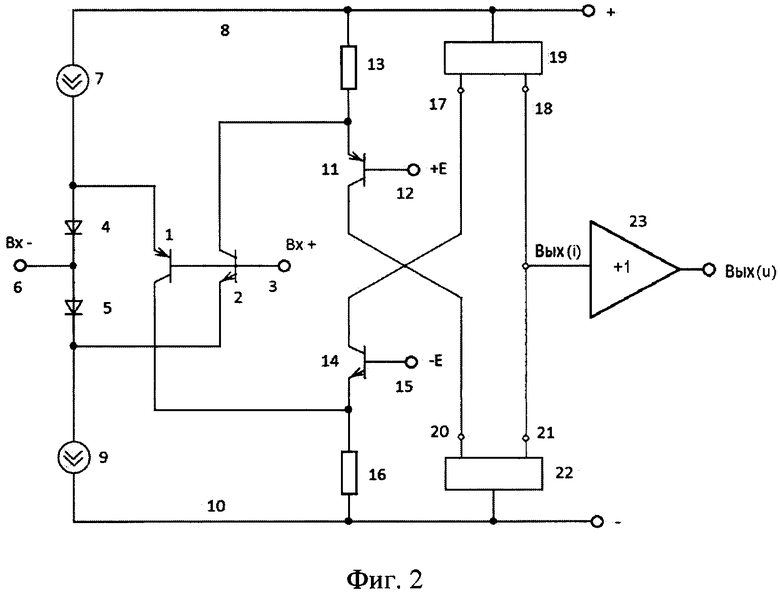

Поставленная задача достигается тем, что операционный усилитель содержит первый (1) и второй (2) входные транзисторы, базы которых соединены с неинвертирующим входом (3) устройства, первый (4) и второй (5) последовательно соединенные прямосмещенные р-n переходы, включенные между эмиттерами первого (1) и второго (2) входных транзисторов, причем общий узел указанных прямосмещенных р-n переходов соединен с инвертирующим (6) входом устройства, первый (7) токостабилизирующий двухполюсник, включенный между эмиттером первого (1) входного транзистора и первой (8) шиной источника питания, второй (9) токостабилизирующий двухполюсник, включенный между эмиттером второго (2) входного транзистора и второй (10) шиной источника питания, первый (11) промежуточный транзистор, база которого соединена с первым (12) вспомогательным источником напряжения питания, а эмиттер соединен с коллектором второго (2) входного транзистора и через первый (13) токостабилизирующий резистор связан с первой (8) шиной источника питания, второй (14) промежуточный транзистор, база которого соединена со вторым (15) вспомогательным источником напряжения питания, а эмиттер соединен с коллектором первого (1) входного транзистора и через второй (16) токостабилизирующий резистор связан со второй (10) шиной источника питания, причем коллектор первого (11) вспомогательного транзистора соединен с первым выходом (20) второго (22) токового зеркала, а коллектор второго (14) вспомогательного транзистора соединен с первым выходом (17) первого (19) токового зеркала, вторые выходы (18 и 21) первого (19) и второго (22) токовых зеркал соединены с токовым выходом устройства.

Частным существенным признаком является то, что токовый выход устройства соединен с входом дополнительного буферного каскада (23), выход которого является потенциальным выходом устройства.

Сущность изобретения поясняется фиг. 2, на которой представлена схема заявляемого устройства, соответствующая пп. 1 и 2 формулы изобретения.

Операционный усилитель содержит первый (1) и второй (2) входные транзисторы, базы которых соединены с неинвертирующим входом (3) устройства, первый (4) и второй (5) последовательно соединенные прямосмещенные р-n-переходы, включенные между базами эмиттерами первого (1) и второго (2) входных транзисторов и соединенные с инвертирующим (6) входом устройства, первый (7) токостабилизирующий двухполюсник, включенный между эмиттером первого (1) входного транзистора и первой (8) шиной источника питания, второй (9) токостабилизирующий двухполюсник, включенный между эмиттером второго (2) входного транзистора и второй (10) шиной источника питания, первый (11) промежуточный транзистор, база которого соединена с первым (12) вспомогательным источником напряжения питания, а эмиттер соединен с коллектором второго (2) входного транзистора и через первый (13) токостабилизирующий резистор связан с первой (8) шиной источника питания, второй (14) промежуточный транзистор, база которого соединена со вторым (15) вспомогательным источником напряжения питания, а эмиттер соединен с коллектором первого (1) входного транзистора и через второй (16) токостабилизирующий резистор связан со второй (10) шиной источника питания, причем коллектор первого (11) вспомогательного транзистора соединен с первым выходом (20) второго (22) токового зеркала, а коллектор второго (14) вспомогательного транзистора соединен с первым выходом (17) первого (19) токового зеркала, второй выход (18) первого (19) токового зеркала и второй выход (21) второго (22) токового зеркала соединены с токовым выходом устройства.

В соответствии с п. 2 формулы изобретения токовый выход устройства Вых (i) соединен со входом дополнительного буферного канала (23), выход которого является потенциальным выходом устройства Вых (u).

При нарастающем напряжении входного сигнала на неинвертирующем входе (3) при включении ОУ без отрицательной обратной связи (ООС) напряжение база-эмиттер транзистора (1) будет уменьшаться, а напряжение база-эмиттер транзистора (2) увеличиваться. Это приведет к уменьшению тока базы транзистора (1) и, следовательно, к уменьшению токов эмиттера и коллектора, а на транзисторе (2) эти токи увеличатся. Так как токи токостабализирующих двухполюсников (7) и (9) остаются практически неизменными, то уменьшение тока эмиттера транзистора (1) приводит к увеличению тока прямосмещенного р-n перехода (4) на ту же величину, а ток прямосмещенного р-n перехода (5), соответственно, уменьшится. Это приводит к появлению тока ошибки на инвертирующем входе (6). Уменьшение тока коллектора транзистора (1) вызывает уменьшение падения напряжению на резисторе (16) и, следовательно, к увеличению напряжения база-эмиттер транзистора (14) и увеличению его тока коллектора, что приводит к увеличению токов на входах (17) и (18) токового зеркала (19). На симметричной половине схемы ОУ будут происходить противоположные процессы, т.е. ток на входах (20) и (21) токового зеркала (22) уменьшится. Это приведет к возрастанию напряжения на выходах Вых (i) и Вых (u). При включении ОУ с ООС через резистор обратной связи, включенный между Вых (и) и инвертирующим входом (6), происходит компенсация тока ошибки так, чтобы результирующий ток через неинвертирующий вход (3) стремился к нулю, т.е. ООС будет компенсировать погрешность усилителя.

Результаты моделирования показывают существенно лучшие динамические характеристики при одинаковых режимах и способе включения схемы: скорость нарастания выходного напряжения составляет 1800 и 300 В/мкс для заявляемой схемы и схемы-прототипа соответственно, а малосигнальная ширина полосы пропускания - 760 и 290 МГц соответственно. Кроме того, схема-прототип склонна к возбуждению, что проявляется в виде затухающих колебаний выходного сигнала при импульсном воздействии и в виде пика на амплитудно-частотной характеристике.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 4502020.

2. Патент US 5003269.

3. Патент US 5537079.

4. Патент US 5742154.

5. Патент US 5623232.

6. Патент US 5789982.

7. Патент US 5977829.

8. Патент US 6710654.

9. Патент US 6710655.

10. Патент US 6724260.

11. Патент US 7479831.

12. Патент RU 2391768.

13. Патент RU 2474952.

| название | год | авторы | номер документа |

|---|---|---|---|

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2474952C1 |

| ИЗБИРАТЕЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2475945C1 |

| ИЗБИРАТЕЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2468506C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ ПРИ НИЗКООМНОЙ НАГРУЗКЕ | 2010 |

|

RU2421891C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2015 |

|

RU2613842C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ ПРИ НИЗКООМНОЙ НАГРУЗКЕ | 2010 |

|

RU2421885C1 |

| ТОКОВОЕ ЗЕРКАЛО | 2007 |

|

RU2365970C1 |

| Быстродействующий операционный усилитель | 2023 |

|

RU2810548C1 |

| ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2012 |

|

RU2509406C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ "ПЕРЕГНУТОГО" КАСКОДА | 2015 |

|

RU2604684C1 |

Изобретение относится к области радиотехники и связи. Техническим результатом является увеличение ширины полосы пропускания операционного усилителя (ОУ), а также повышение быстродействия ОУ при импульсных входных сигналах. ОУ содержит два входных транзистора, два последовательно соединенных прямосмещенных р-n-перехода, два токостабилизирующих двухполюсника, две шины источника питания, два промежуточных транзистора, два вспомогательных источника напряжения питания, два токостабилизирующих резистора и два токовых зеркала. 1 з.п. ф-лы, 2 ил.

1. Операционный усилитель содержит первый и второй входные транзисторы, базы которых соединены с неинвертирующим входом устройства, первый и второй последовательно соединенные прямосмещенные р-n-переходы, включенные между эмиттерами первого и второго входных транзисторов, причем общий узел указанных переходов соединен с инвертирующим входом устройства, первый токостабилизирующий двухполюсник, включенный между эмиттером первого входного транзистора и первой шиной источника питания, второй токостабилизирующий двухполюсник, включенный между эмиттером второго входного транзистора и второй шиной источника питания, первый промежуточный транзистор, база которого соединена с первым вспомогательным источником напряжения питания, а эмиттер соединен с коллектором второго входного транзистора и через первый токостабилизирующий резистор связан с первой шиной источника питания, второй промежуточный транзистор, база которого соединена со вторым вспомогательным источником напряжения питания, а эмиттер соединен с коллектором первого входного транзистора и через второй токостабилизирующий резистор связан со второй шиной источника питания, причем коллектор первого вспомогательного транзистора соединен с первым выходом второго токового зеркала, а коллектор второго вспомогательного транзистора соединен с первым выходом первого токового зеркала, вторые выходы первого и второго токовых зеркал соединены с токовым выходом устройства.

2. Операционный усилитель по п. 1, отличающийся тем, что токовый выход устройства соединен с входом дополнительного буферного каскада, выход которого является потенциальным выходом устройства.

| ВЫХОДНОЙ КАСКАД ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2006 |

|

RU2311729C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2474952C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2450425C1 |

| US 7522001 B2, 21.04.2009 | |||

| US 7262662 B2, 28.08.2007. | |||

Авторы

Даты

2016-03-10—Публикация

2015-03-27—Подача