Изобретение относится к радиоэлектронике и может быть использовано в качестве операционных усилителей (ОУ), предназначенных для применения в подклассе так называемых дискретно-аналоговых SC-фильтров на переключаемых конденсаторах [1-2], для которых (в ряде важных случаев) требуются повышенные значения максимальной скорости нарастания выходного напряжения ОУ, а также в драйверах быстродействующих аналого-цифровых преобразователей.

В настоящее время в современных микроэлектронных операционных усилителях применяются схемы входных каскадов, в которых для повышения максимальной скорости нарастания выходного напряжения (SR) в режиме большого сигнала предусмотрено (во время фронта переходного процесса) существенное увеличение выходных токов входного дифференциального каскада [3-12]. Данные схемотехнические решения повышают SR ОУ для многих технологических процессов до уровня средних значений (SR=200-400 В/мкс), однако не позволяют получить предельно возможные SRmax из-за влияния паразитных емкостей в цепи баз выходных транзисторов промежуточного каскада.

Ближайшим прототипом заявляемого устройства является схема ОУ, представленная в монографии «Матавкин В.В. Быстродействующие операционные усилители. – М.: Радио и связь, 1989, рис. 4.16». Кроме этого, данная схема применяется в ряде серийных операционных усилителей зарубежного производства HA-2700/2704/2705 [11].

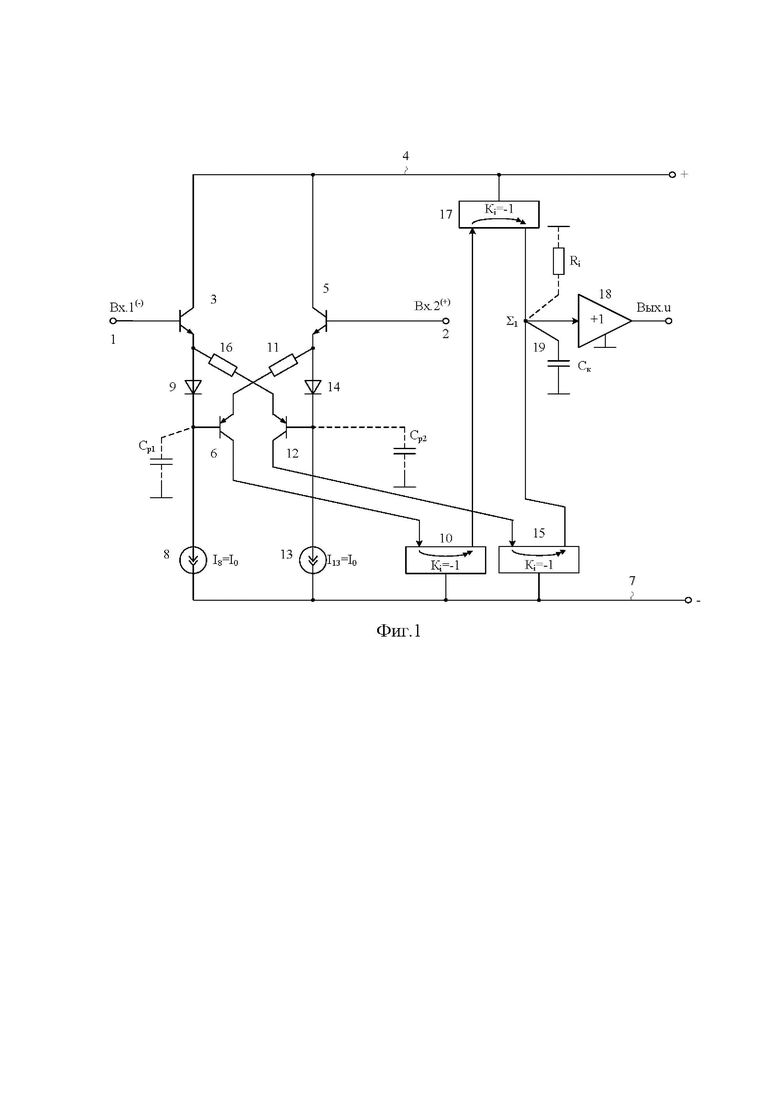

ОУ-прототип (фиг.1) содержит первый 1 и второй 2 входы, первый 3 входной транзистор, база которого соединена с первым 1 входом, а коллектор связан с первой 4 шиной источника питания, второй 5 входной транзистор, база которого подключена ко второму 2 входу, а коллектор связан с первой 4 шиной источника питания, первый 6 транзистор промежуточного каскада, база которого связана со второй 7 шиной источника питания через первый 8 токостабилизирующий двухполюсник и подключена к эмиттеру первого 3 входного транзистора через цепь смещения потенциалов 9, коллектор соединен с первым 10 токовым зеркалом, согласованным со второй 7 шиной источника питания, а эмиттер соединен с эмиттером второго 5 входного транзистора через первый 11 вспомогательный резистор, второй 12 транзистор промежуточного каскада, база которого связана со второй 7 шиной источника питания через второй 13 токостабилизирующий двухполюсник и подключена к эмиттеру второго 5 входного транзистора через цепь смещения потенциалов 14, коллектор соединен со вторым 15 токовым зеркалом, согласованным со второй 7 шиной источника питания, а эмиттер соединен с эмиттером первого 3 входного транзистора через второй 16 вспомогательный резистор, выход первого 10 токового зеркала соединен со входом третьего 17 токового зеркала, согласованного с первой 4 шиной источника питания, выход второго 15 токового зеркала соединен с выходом третьего 17 токового зеркала и подключен ко входу буферного усилителя 18 и корректирующему конденсатору 19.

Существенный недостаток известного ОУ фиг. 1, например, при его неинвертирующем включении, состоит в том, что он не обеспечивает при использовании многих технологических процессов, освоенных российскими предприятиями, получение предельно возможных для данной архитектуры значений SRmax при отрицательных импульсных входных сигналах. Это обусловлено влиянием паразитных емкостей Ср1, Ср2 в цепи баз выходных транзисторов 6 и 12 промежуточного каскада. Повысить SR(-) здесь можно за счет применения более дорогостоящих технологических процессов, например, SiGe, уменьшающих Ср1 и Ср2.

Основная задача предполагаемого изобретения состоит в дальнейшем увеличении максимальной скорости нарастания выходного напряжения отрицательного фронта с уровня 200-400 В/мкс до уровня 12000 В/мкс без уменьшения технологических норм процесса его изготовления. Это позволит выпускать быстродействующие ОУ по имеющимся в России технологиям с SR(+)≈SR(-).

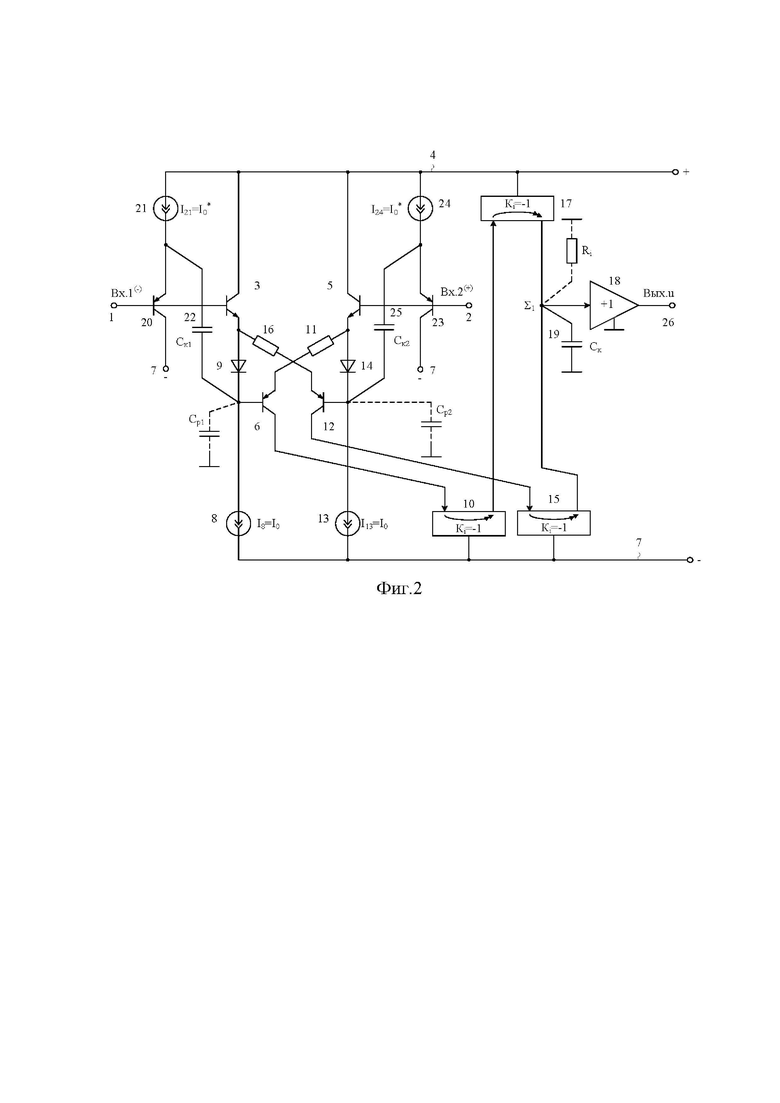

Поставленная задача достигается тем, что в операционном усилителе фиг.1, содержащем первый 1 и второй 2 входы, первый 3 входной транзистор, база которого соединена с первым 1 входом, а коллектор связан с первой 4 шиной источника питания, второй 5 входной транзистор, база которого подключена ко второму 2 входу, а коллектор связан с первой 4 шиной источника питания, первый 6 транзистор промежуточного каскада, база которого связана со второй 7 шиной источника питания через первый 8 токостабилизирующий двухполюсник и подключена к эмиттеру первого 3 входного транзистора через цепь смещения потенциалов 9, коллектор соединен с первым 10 токовым зеркалом, согласованным со второй 7 шиной источника питания, а эмиттер соединен с эмиттером второго 5 входного транзистора через первый 11 вспомогательный резистор, второй 12 транзистор промежуточного каскада, база которого связана со второй 7 шиной источника питания через второй 13 токостабилизирующий двухполюсник и подключена к эмиттеру второго 5 входного транзистора через цепь смещения потенциалов 14, коллектор соединен со вторым 15 токовым зеркалом, согласованным со второй 7 шиной источника питания, а эмиттер соединен с эмиттером первого 3 входного транзистора через второй 16 вспомогательный резистор, выход первого 10 токового зеркала соединен со входом третьего 17 токового зеркала, согласованного с первой 4 шиной источника питания, выход второго 15 токового зеркала соединен с выходом третьего 17 токового зеркала и подключен ко входу буферного усилителя 18 и корректирующему конденсатору 19, предусмотрены новые элементы и связи – в схему введен первый 20 дополнительный транзистор, эмиттер которого связан с первой 4 шиной источника питания через первый 21 дополнительный токостабилизирующий двухполюсник и соединен с базой первого 6 транзистора промежуточного каскада через первый 22 дополнительный корректирующий конденсатор, коллектор согласован со второй 7 шиной источника питания, второй 23 дополнительный транзистор, база которого соединена со вторым 2 входом, эмиттер связан с первой 4 шиной источника питания через второй 24 дополнительный токостабилизирующий двухполюсник и связан с базой второго 12 транзистора промежуточного каскада через второй 25 дополнительный корректирующий конденсатор, коллектор второго 23 дополнительного транзистора согласован со второй 7 шиной источника питания.

На чертеже фиг. 1 приведена схема операционного усилителя – прототипа.

На чертеже фиг. 2 показана схема заявляемого ОУ в соответствии с формулой изобретения.

На чертеже фиг. 3 представлен статический режим ОУ на чертеже фиг. 2 в среде LTSpice на моделях транзисторов базового матричного кристалла MH2XA031_25.01.21 при 27°С, первом 11 и втором 16 вспомогательных резисторах (R1=R2=100 Ом), сопротивлении высокоимпедансного узла R3=1 МОм, источниках опорного тока I1=I2=I3=I4=200мкА, паразитных конденсаторах Сp1=Cp2=1.5пФ, интегрирующем корректирующем конденсаторе 19 (С1=Ск=С19=1пФ), первом 22 и втором 25 дополнительных корректирующих конденсаторах (Cк1=С22=Ск2=С25=0пФ), напряжениях на шинах питания V1=V2=±5В.

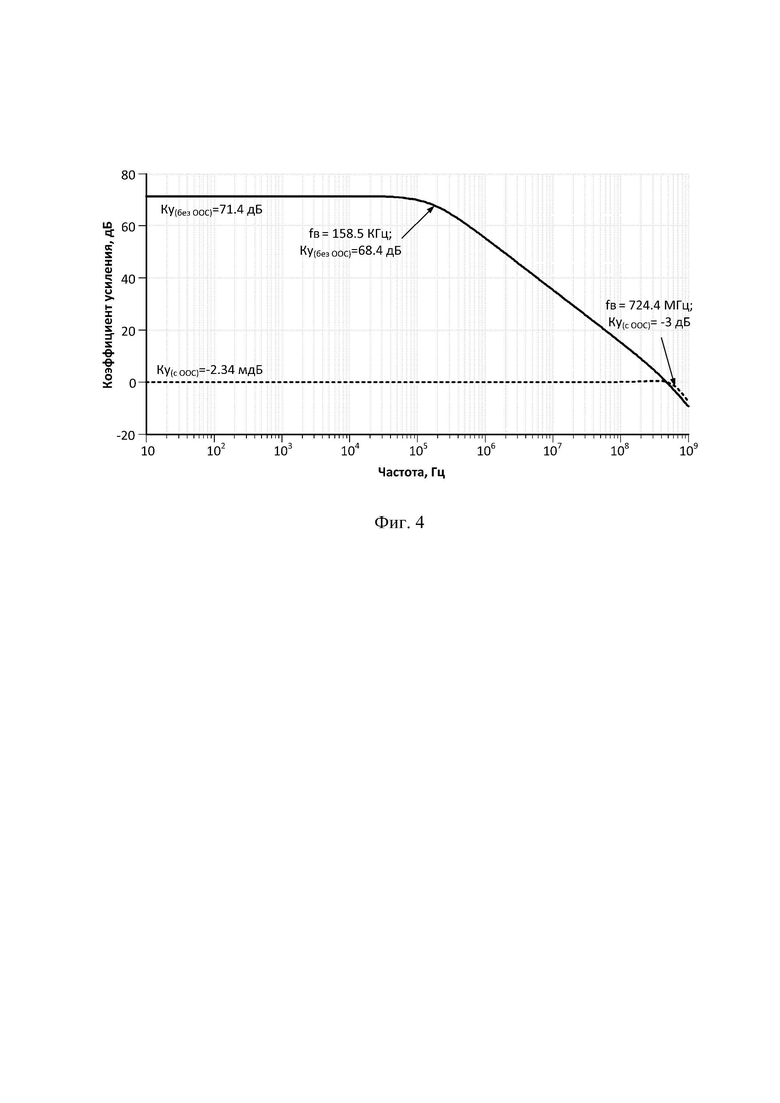

На чертеже фиг. 4 приведена логарифмическая амплитудно-частотная характеристика коэффициента усиления по напряжению ОУ фиг.3.

На чертеже фиг. 5 показан передний фронт переходного процесса в ОУ фиг. 3 при разных значениях емкости первого 22 и второго 25 дополнительных корректирующих конденсаторов (Cк1=С22=Ск2=С25).

На чертеже фиг. 6 представлен задний фронт переходного процесса в ОУ фиг. 3 при разных значениях емкости первого 22 и второго 25 дополнительных корректирующих конденсаторов (Cк1=С22=Ск2=С25).

Быстродействующий операционный усилитель фиг. 2 содержит первый 1 и второй 2 входы, первый 3 входной транзистор, база которого соединена с первым 1 входом, а коллектор связан с первой 4 шиной источника питания, второй 5 входной транзистор, база которого подключена ко второму 2 входу, а коллектор связан с первой 4 шиной источника питания, первый 6 транзистор промежуточного каскада, база которого связана со второй 7 шиной источника питания через первый 8 токостабилизирующий двухполюсник и подключена к эмиттеру первого 3 входного транзистора через цепь смещения потенциалов 9, коллектор соединен с первым 10 токовым зеркалом, согласованным со второй 7 шиной источника питания, а эмиттер соединен с эмиттером второго 5 входного транзистора через первый 11 вспомогательный резистор, второй 12 транзистор промежуточного каскада, база которого связана со второй 7 шиной источника питания через второй 13 токостабилизирующий двухполюсник и подключена к эмиттеру второго 5 входного транзистора через цепь смещения потенциалов 14, коллектор соединен со вторым 15 токовым зеркалом, согласованным со второй 7 шиной источника питания, а эмиттер соединен с эмиттером первого 3 входного транзистора через второй 16 вспомогательный резистор, выход первого 10 токового зеркала соединен со входом третьего 17 токового зеркала, согласованного с первой 4 шиной источника питания, выход второго 15 токового зеркала соединен с выходом третьего 17 токового зеркала и подключен ко входу буферного усилителя 18 и корректирующему конденсатору 19. В схему введен первый 20 дополнительный транзистор, эмиттер которого связан с первой 4 шиной источника питания через первый 21 дополнительный токостабилизирующий двухполюсник и соединен с базой первого 6 транзистора промежуточного каскада через первый 22 дополнительный корректирующий конденсатор, коллектор согласован со второй 7 шиной источника питания, второй 23 дополнительный транзистор, база которого соединена со вторым 2 входом, эмиттер связан с первой 4 шиной источника питания через второй 24 дополнительный токостабилизирующий двухполюсник и связан с базой второго 12 транзистора промежуточного каскада через второй 25 дополнительный корректирующий конденсатор, коллектор второго 23 дополнительного транзистора согласован со второй 7 шиной источника питания.

Рассмотрим работу заявляемого ОУ фиг. 2.

При подаче большого импульсного сигнала положительной полярности на неинвертирующий вход 2 в схеме ОУ фиг. 2 со 100% отрицательной обратной связью на инвертирующий вход 1 транзисторы 5 и 6 формируют большой импульс тока на входе токового зеркала 10, токового зеркала 17, который передается в интегрирующий корректирующий конденсатор 19 (Ск=С19). Максимальное значение этого тока определяется сопротивлением первого 11 вспомогательного резистора. Таким образом, для положительных импульсных сигналов схема ОУ фиг. 2, также как и схема фиг. 1 обеспечивает повышенные значения SR(+), которые не зависят от наличия паразитных емкостей Ср1 и Ср2.

Однако, в такой схеме SR(-) меньше SR(+) на несколько порядков. Действительно, при отрицательном входном импульсном сигнале на неинвертирующем входе 2 происходит практически мгновенное запирание транзисторов 5 и 6, а коллекторный ток второго 12 транзистора промежуточного каскада медленно изменяется из-за наличия емкости Ср2. Введение в схему фиг. 2 конденсатора второго 25 дополнительного корректирующего конденсатора Ск2=С25 существенно уменьшает влияние паразитной емкости Ср2 и приводит к достаточно быстрому изменению тока коллектора второго 12 транзистора промежуточного каскада, выходного тока второго 15 токового зеркала и тока через интегрирующую емкость коррекции Ск=С19. Как следствие, максимальная скорость нарастания выходного напряжения ОУ (SR(-)) для отрицательных импульсных входных сигналов повышается более чем в 90 раз (см. таблицу 1) и становится соизмеримой с SR(+).

Таблица 1 - Зависимости максимальной скорости нарастания выходного напряжения предлагаемого ОУ фиг. 2 от емкостей дополнительных корректирующих конденсаторов 22 и 25 (С22=Ск1, С25=Ск2)

Ск1=С22, Ск2=С25 в схеме фиг. 2

Из таблицы 1 следует, что предлагаемое схемотехническое решение практически не влияет на передний фронт переходного процесса в ОУ, однако более чем в 90 раз обеспечивает увеличение SR(-) заднего фронта до уровня 12000 В/мкс.

Таким образом, заявляемое устройство имеет существенные преимущества в сравнении с ОУ-прототипом по уровню максимальной скорости нарастания выходного напряжения замкнутого ОУ.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. E. J. Wyers, "Accurate Geometric Programming-Compatible Slew Rate Modeling for Two-Stage Operational Amplifier Design Optimization," 2022 IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), Shenzhen, China, 2022, pp. 185-189. doi: 10.1109/APCCAS55924.2022.10090335

2. J. Ramirez-Angulo and M. Holmes, "A simple technique to significantly enhance slew rate and bandwidth of one-stage CMOS operational amplifiers," 2002 IEEE International Symposium on Circuits and Systems. Proceedings (Cat. No.02CH37353), Phoenix-Scottsdale, AZ, USA, 2002, pp. II-II. doi: 10.1109/ISCAS.2002.1011483

3. Матавкин В.В. Быстродействующие операционные усилители. – М.: Радио и связь, 1989, рис. 4.16

4. Патент US 3.668.538, fig. 1, 1972 г.

5. Патент RU 2319290, фиг. 1, 2008 г.

6. Патент US 5140074, fig. 1, 1992 г.

7. Патент US 6437645, fig. 1, 2002 г.

8. Патент US 5343164, fig. 2, fig. 3, 1994 г.

9. Патент US 6600343, fig. 1, 2003 г.

10. Патент US 5374897, fig.4, 1994 г.

11. Linear & Data Acquisition Products // Harris Semiconductor Analog Products, Volume 1, 1977, pp. 2-59: HA-2700/2704/2705. URL: http://www.bitsavers.org/components/harris/1977_Harris_Linear_and_Data_Acquisition_Products_Volume_1.pdf

12. Полонников Д.Е. Операционные усилители: Принципы построения, теория, схемотехника. – М.: Энергоатомиздат, 1983. – С. 115, рис. 3.27

| название | год | авторы | номер документа |

|---|---|---|---|

| Операционный усилитель с повышенной максимальной скоростью нарастания выходного напряжения | 2023 |

|

RU2810544C1 |

| Быстродействующий операционный усилитель с дифференцирующей цепью коррекции переходного процесса | 2023 |

|

RU2811071C1 |

| Быстродействующий операционный усилитель на основе "перегнутого" каскода | 2023 |

|

RU2811070C1 |

| Быстродействующий операционный усилитель на основе комплементарного "перегнутого" каскода | 2023 |

|

RU2813280C1 |

| Быстродействующий операционный усилитель на основе комплементарных «перегнутых» каскодов | 2023 |

|

RU2813010C1 |

| Быстродействующий операционный усилитель | 2024 |

|

RU2822112C1 |

| Быстродействующий операционный усилитель на основе "перегнутого" каскода с дифференцирующей цепью коррекции переходного процесса | 2023 |

|

RU2813133C1 |

| Многоканальный быстродействующий операционный усилитель | 2018 |

|

RU2683851C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ДИФФЕРЕНЦИРУЮЩИМИ ЦЕПЯМИ КОРРЕКЦИИ | 2018 |

|

RU2684500C1 |

| Быстродействующий дифференциальный операционный усилитель | 2018 |

|

RU2688227C1 |

Изобретение относится к радиоэлектронике. Технический результат - увеличение максимальной скорости нарастания выходного напряжения отрицательного фронта переходного процесса в операционном усилителе. Для этого в схему быстродействующего операционного усилителя введен первый (20) дополнительный транзистор, эмиттер которого связан с первой (4) шиной источника питания через первый (21) дополнительный токостабилизирующий двухполюсник и соединен с базой первого (6) транзистора промежуточного каскада через первый (22) дополнительный корректирующий конденсатор, коллектор согласован со второй (7) шиной источника питания, второй (23) дополнительный транзистор, база которого соединена со вторым (2) входом, эмиттер связан с первой (4) шиной источника питания через второй (24) дополнительный токостабилизирующий двухполюсник и связан с базой второго (12) транзистора промежуточного каскада через второй (25) дополнительный корректирующий конденсатор, коллектор второго (23) дополнительного транзистора согласован со второй (7) шиной источника питания. 6 ил., 1 табл.

Быстродействующий операционный усилитель, содержащий первый (1) и второй (2) входы, первый (3) входной транзистор, база которого соединена с первым (1) входом, а коллектор связан с первой (4) шиной источника питания, второй (5) входной транзистор, база которого подключена ко второму (2) входу, а коллектор связан с первой (4) шиной источника питания, первый (6) транзистор промежуточного каскада, база которого связана со второй (7) шиной источника питания через первый (8) токостабилизирующий двухполюсник и подключена к эмиттеру первого (3) входного транзистора через цепь смещения потенциалов (9), коллектор соединен с первым (10) токовым зеркалом, согласованным со второй (7) шиной источника питания, а эмиттер соединен с эмиттером второго (5) входного транзистора через первый (11) вспомогательный резистор, второй (12) транзистор промежуточного каскада, база которого связана со второй (7) шиной источника питания через второй (13) токостабилизирующий двухполюсник и подключена к эмиттеру второго (5) входного транзистора через цепь смещения потенциалов (14), коллектор соединен со вторым (15) токовым зеркалом, согласованным со второй (7) шиной источника питания, а эмиттер соединен с эмиттером первого (3) входного транзистора через второй (16) вспомогательный резистор, выход первого (10) токового зеркала соединен со входом третьего (17) токового зеркала, согласованного с первой (4) шиной источника питания, выход второго (15) токового зеркала соединен с выходом третьего (17) токового зеркала и подключен ко входу буферного усилителя (18) и корректирующему конденсатору (19), отличающийся тем, что в схему введен первый (20) дополнительный транзистор, эмиттер которого связан с первой (4) шиной источника питания через первый (21) дополнительный токостабилизирующий двухполюсник и соединен с базой первого (6) транзистора промежуточного каскада через первый (22) дополнительный корректирующий конденсатор, коллектор согласован со второй (7) шиной источника питания, второй (23) дополнительный транзистор, база которого соединена со вторым (2) входом, эмиттер связан с первой (4) шиной источника питания через второй (24) дополнительный токостабилизирующий двухполюсник и связан с базой второго (12) транзистора промежуточного каскада через второй (25) дополнительный корректирующий конденсатор, коллектор второго (23) дополнительного транзистора согласован со второй (7) шиной источника питания.

| МАТАВКИН В.В., Быстродействующие операционные усилители, М.: Радио и связь, 1989, рис | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ "ПЕРЕГНУТОГО" КАСКОДА | 2008 |

|

RU2391768C2 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2017 |

|

RU2652504C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2615066C1 |

| US 5225791 A1, 06.07.1993. | |||

Авторы

Даты

2023-12-27—Публикация

2023-10-15—Подача