Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, SiGe-операционных усилителях (ОУ), компараторах, стабилизаторах напряжения, различных аналогово-цифровых интерфейсах и т.п.).

В современной аналоговой микроэлектронике применяются двухкаскадные дифференциальные усилители (ДУ) на n-p-n транзисторах с активными нагрузками в виде двух источников опорного тока [1-8]. Данная архитектура ДУ относится к числу достаточно низковольтных и широкополосных и, как следствие, весьма часто используется в ВЧ и СВЧ аналоговых устройствах, в интегральных стабилизаторах напряжения, фильтрах и т.п. Однако при низкоомных нагрузках (например, волновых сопротивлениях СВЧ линий связи R0=50 Ом=RH), такие ДУ имеют небольшие коэффициенты усиления по напряжению без обратной связи (Ку). При введении обратной связи невысокие значения Ку не позволяют получить в данной архитектуре заданный уровень петлевого усиления, определяющего погрешность устройства, величину его выходного сопротивления и другие динамические параметры.

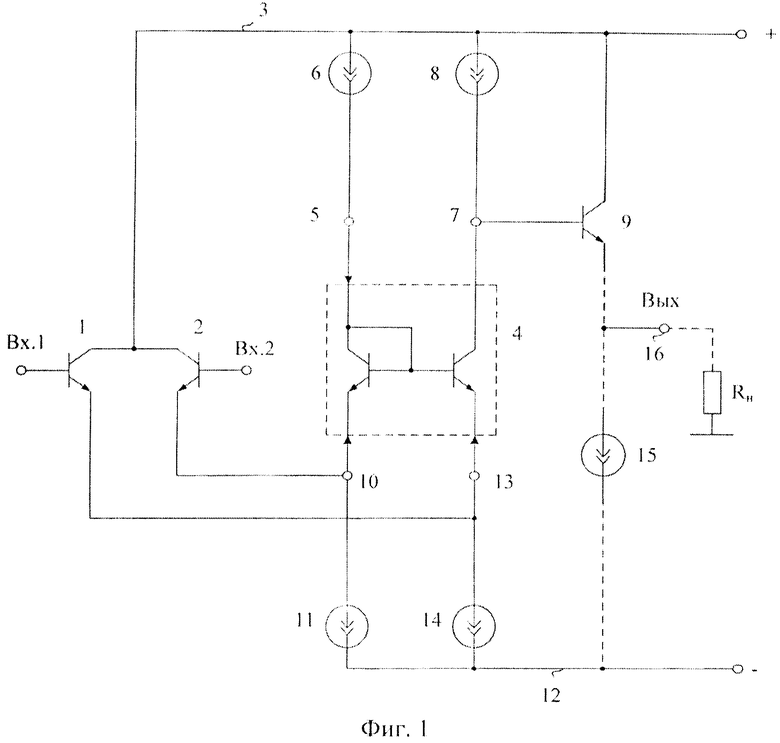

Наиболее близким по технической сущности к заявляемому устройству является ДУ (фиг.1), рассмотренный в патенте RU №2384934, фиг.13. Он содержит первый 1 и второй 2 входные транзисторы, коллекторы которых соединены с первым 3 источником питания, первое 4 токовое зеркало, базовый вход 5 которого соединен с первым 3 источником питания через первый 6 источник опорного тока, токовый выход 7 первого 4 токового зеркала связан с первым 3 источником питания через второй 8 источник опорного тока и соединен с базой первого 9 выходного транзистора, инвертирующий эмиттерный вход 10 первого 4 токового зеркала соединен с эмиттером второго 2 входного транзистора и через третий 11 источник опорного тока связан со вторым 12 источником питания, неинвертирующий эмиттерный вход 13 первого 4 токового зеркала связан со вторым 12 источником питания через четвертый 14 источник опорного тока и соединен с эмиттером первого 1 входного транзистора, пятый 15 токостабилизирующий двухполюсник, включенный между выходом устройства 16 и вторым 12 источником питания, причем коллектор первого 9 выходного транзистора соединен с первым 3 источником питания.

Существенный недостаток известного устройства состоит в том, что при выполнении его нагрузки RH в виде низкоомного резистора (например, 5 Ом или 50 Ом) его коэффициент усиления получается небольшим.

Основная задача предлагаемого изобретения состоит в повышении на один-два порядка коэффициента усиления по напряжению разомкнутого ДУ при использовании сравнительно низкоомных двухполюсников нагрузки (например, RH=R0=5÷50 Ом). Дополнительная цель - повышение стабильности нулевого уровня.

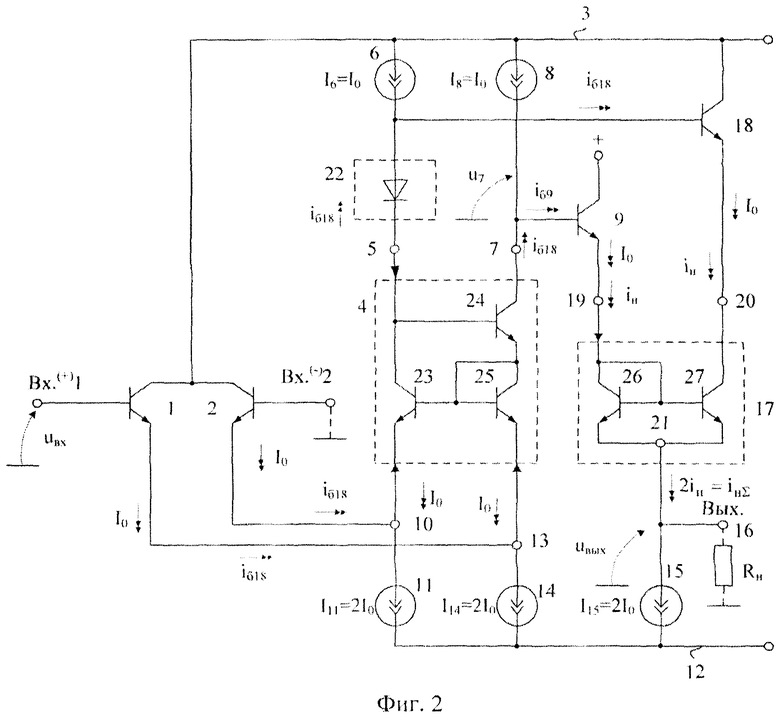

Поставленная задача достигается тем, что в дифференциальном усилителе фиг.1, содержащем первый 1 и второй 2 входные транзисторы, коллекторы которых соединены с первым 3 источником питания, первое 4 токовое зеркало, базовый вход 5 которого соединен с первым 3 источником питания через первый 6 источник опорного тока, токовый выход 7 первого 4 токового зеркала связан с первым 3 источником питания через второй 8 источник опорного тока и соединен с базой первого 9 выходного транзистора, инвертирующий эмиттерный вход 10 первого 4 токового зеркала соединен с эмиттером второго 2 входного транзистора и через третий 11 источник опорного тока связан со вторым 12 источником питания, неинвертирующий эмиттерный вход 13 первого 4 токового зеркала связан со вторым 12 источником питания через четвертый 14 источник опорного тока и соединен с эмиттером первого 1 входного транзистора, пятый 15 токостабилизирующий двухполюсник, включенный между выходом устройства 16 и вторым 12 источником питания, причем коллектор первого 9 выходного транзистора соединен с первым 3 источником питания, предусмотрены новые элементы и связи - в схему введено второе 17 токовое зеркало и второй 18 выходной транзистор, базовый вход 19 второго 17 токового зеркала соединен с эмиттером первого 9 выходного транзистора, токовый выход 20 второго 17 токового зеркала подключен к эмиттеру второго 18 выходного транзистора, общий эмиттерный выход 21 второго 17 токового зеркала соединен с выходом устройства 16, коллектор второго 18 выходного транзистора подключен к первому 3 источнику питания, причем базовый вход 5 первого 4 токового зеркала соединен с первым 3 источником питания через последовательно соединенные цепь смещения потенциалов 22 и первый 6 источник опорного тока, общий узел последовательно соединенных цепи смещения потенциалов 22 и первого 6 источника опорного тока соединен с базой второго 18 выходного транзистора, а цепь смещения потенциалов 22 включена между базой второго 18 выходного транзистора и базовым входом 5 первого 4 токового зеркала.

На фиг.1 приведена схема ДУ-прототипа.

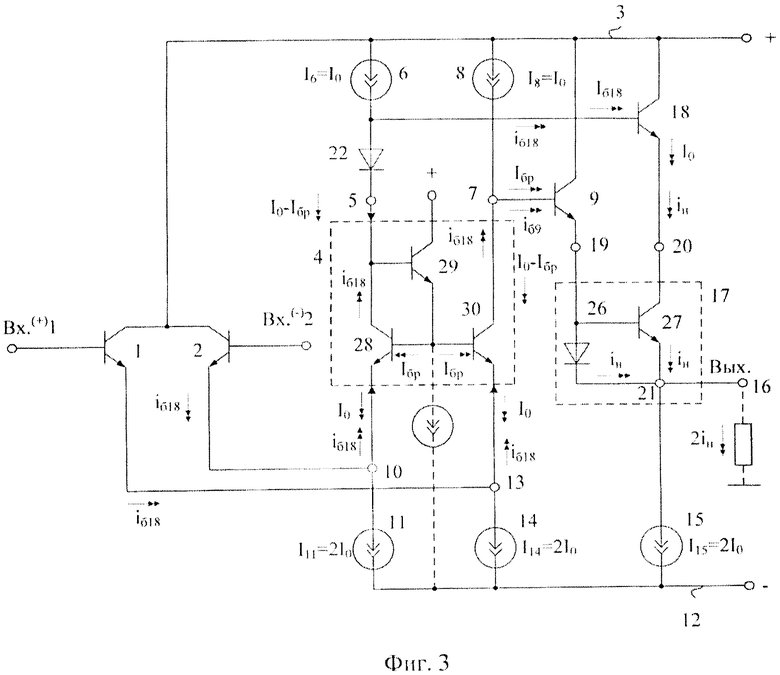

На фиг.2 представлена схема заявляемого устройства, соответствующего п.1, п.2 и п.3 формулы изобретения, а на фиг.3 - его конкретное выполнение по п.4 для случая, когда первое 4 токовое зеркало реализовано на транзисторах 28, 29, 30. Таким образом, схема фиг.3 соответствует п.4 формулы изобретения.

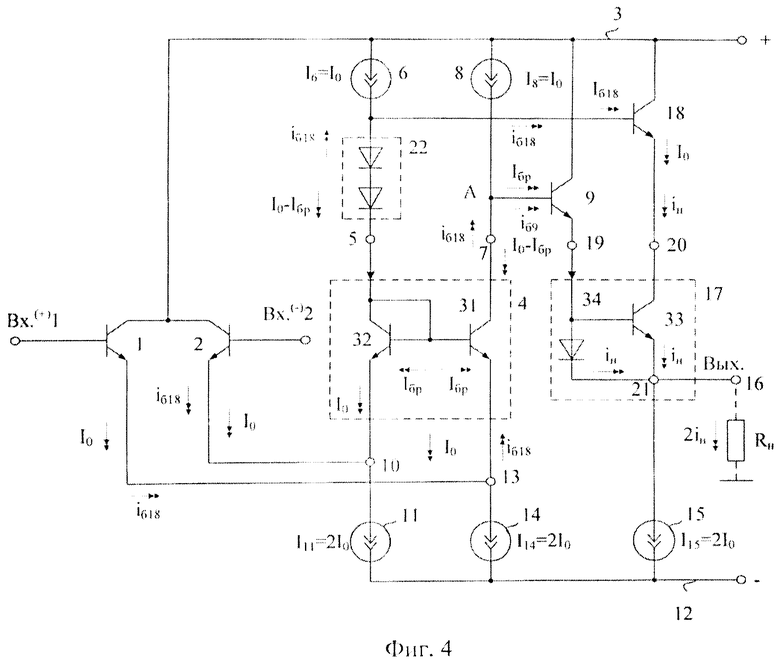

На фиг.4 приведена схема фиг.2 для случая, когда токовое зеркало 4 выполнено в соответствии с п.5 формулы изобретения.

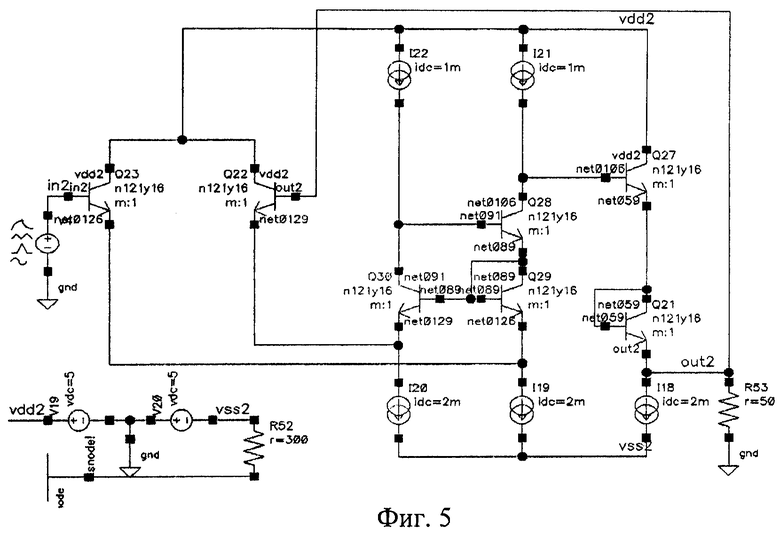

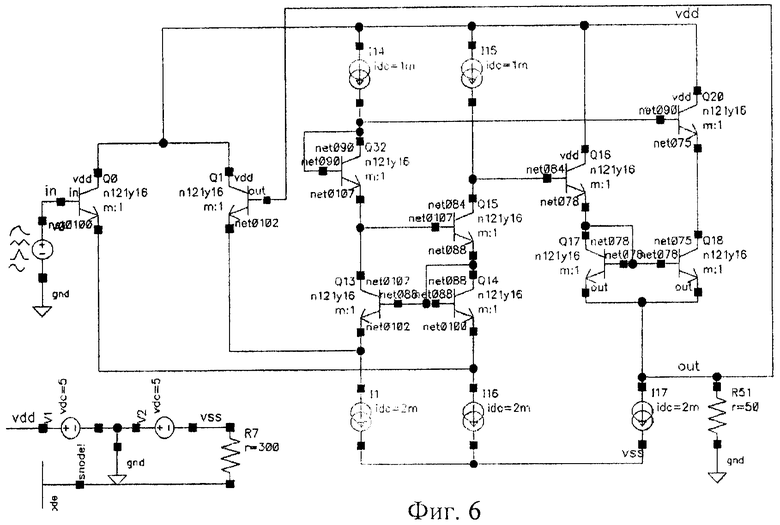

На фиг.5 показана схема ДУ-прототипа фиг.1, а на фиг.6 - схема заявляемого ДУ фиг.2 в среде компьютерного моделирования Cadance на моделях интегральных транзисторов HJW ФГУП НПП «Пульсар».

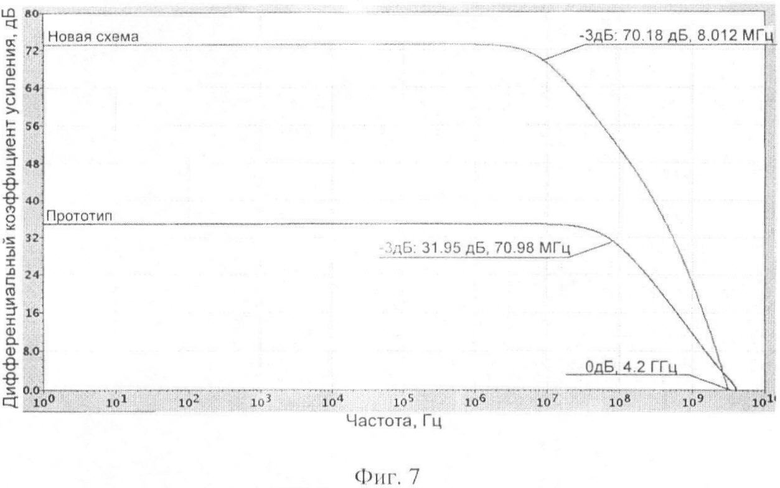

На фиг.7 показана зависимость коэффициента усиления по напряжению сравниваемых схем (фиг.5, фиг.6) от частоты. Данные графики показывают, что заявляемый ДУ, несмотря на применение низкоомной нагрузки (RH=50 Ом), имеет коэффициент усиления по напряжению на 39,0 дБ (в сто раз) лучше в сравнении с Ку известного устройства. Это важное достоинство предлагаемого ДУ.

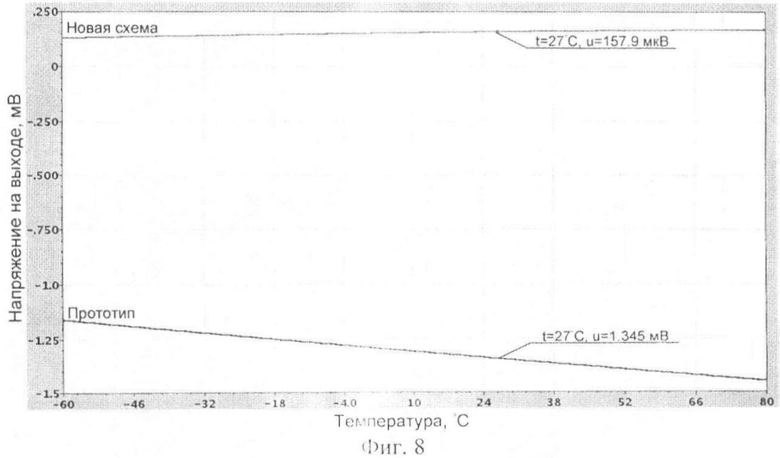

На фиг.8 показана температурная зависимость напряжения смещения нуля UCM сравниваемых схем фиг.5 и фиг.6, из которого следует, что заявляемое устройство имеет более высокую стабильность нулевого уровня.

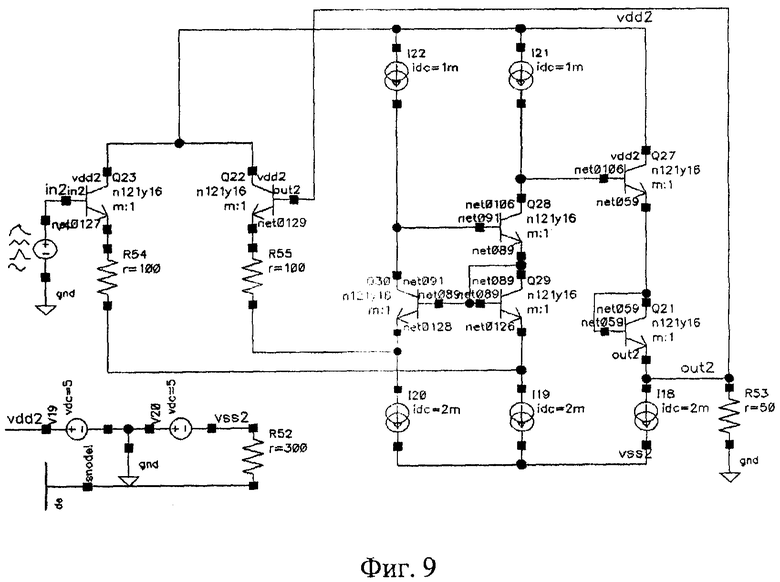

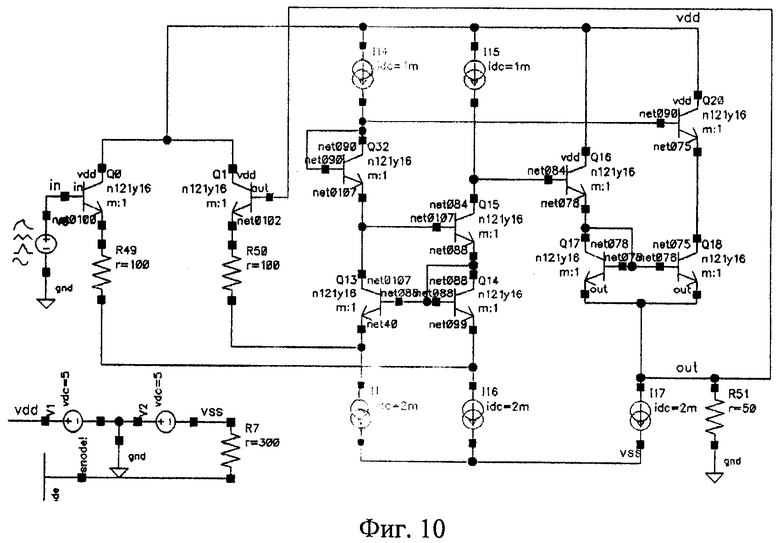

На фиг.9 показана схема ДУ-прототипа фиг.1, а на фиг.10 - схема заявляемого ДУ фиг.2 в среде компьютерного моделирования Cadance на моделях интегральных транзисторов HJW ФГУП НПП «Пульсар» для случая, когда в эмиттерной цепи входных транзисторов 1 и 2 введены резисторы местной отрицательной обратной связи с сопротивлением 100 Ом.

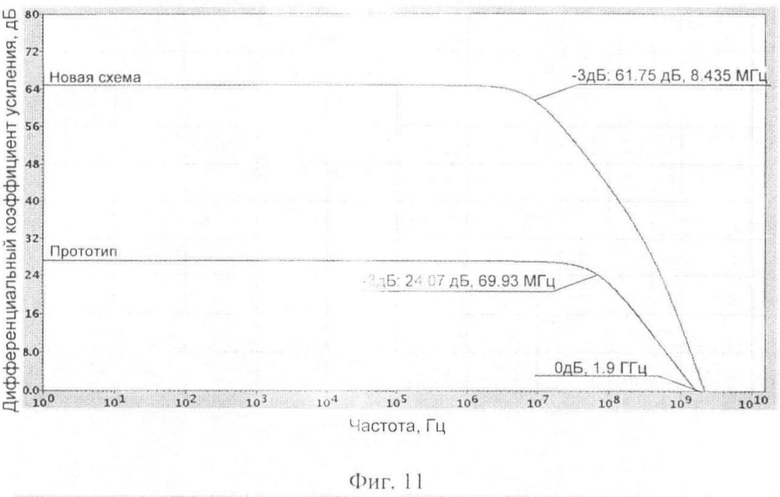

На фиг.11 показана зависимость коэффициента усиления по напряжению сравниваемых схем (фиг.9, фиг.10) от частоты. Данные графики показывают, что заявляемый ДУ, несмотря на применение низкоомной нагрузки (RH=50 Ом), имеет коэффициент усиления по напряжению на 37,0 дБ (почти в сто раз) лучше в сравнении с Ку известного устройства.

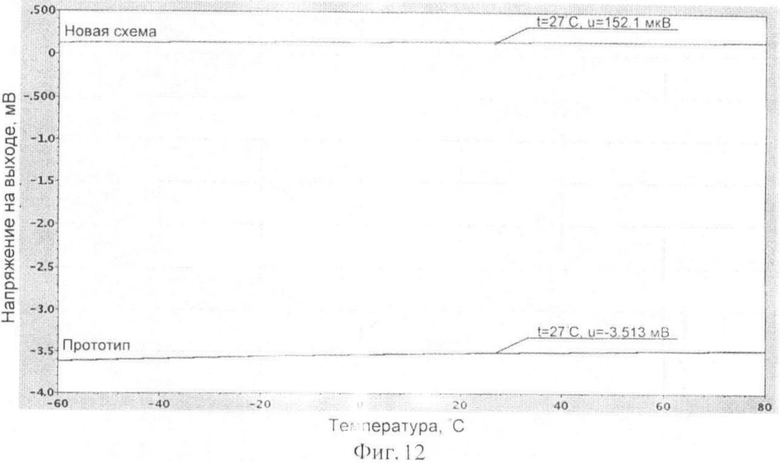

На фиг.12 показана температурная зависимость напряжения смещения нуля UCM сравниваемых схем фиг.9 и фиг.10, из которого следует, что заявляемое устройство имеет более высокую стабильность нулевого уровня.

Дифференциальный усилитель с повышенным коэффициентом усиления при низкоомной нагрузке фиг.2 содержит первый 1 и второй 2 входные транзисторы, коллекторы которых соединены с первым 3 источником питания, первое 4 токовое зеркало, базовый вход 5 которого соединен с первым 3 источником питания через первый 6 источник опорного тока, токовый выход 7 первого 4 токового зеркала связан с первым 3 источником питания через второй 8 источник опорного тока и соединен с базой первого 9 выходного транзистора, инвертирующий эмиттерный вход 10 первого 4 токового зеркала соединен с эмиттером второго 2 входного транзистора и через третий 11 источник опорного тока связан со вторым 12 источником питания, неинвертирующий эмиттерный вход 13 первого 4 токового зеркала связан со вторым 12 источником питания через четвертый 14 источник опорного тока и соединен с эмиттером первого 1 входного транзистора, пятый 15 токостабилизирующий двухполюсник, включенный между выходом устройства 16 и вторым 12 источником питания, причем коллектор первого 9 выходного транзистора соединен с первым 3 источником питания. В схему введено второе 17 токовое зеркало и второй 18 выходной транзистор, базовый вход 19 второго 17 токового зеркала соединен с эмиттером первого 9 выходного транзистора, токовый выход 20 второго 17 токового зеркала подключен к эмиттеру второго 18 выходного транзистора, общий эмиттерный выход 21 второго 17 токового зеркала соединен с выходом устройства 16, коллектор второго 18 выходного транзистора подключен к первому 3 источнику питания, причем базовый вход 5 первого 4 токового зеркала соединен с первым 3 источником питания через последовательно соединенные цепь смещения потенциалов 22 и первый 6 источник опорного тока, общий узел последовательно соединенных цепи смещения потенциалов 22 и первого 6 источника опорного тока соединен с базой второго 18 выходного транзистора, а цепь смещения потенциалов 22 включена между базой второго 18 выходного транзистора и базовым входом 5 первого 4 токового зеркала.

На фиг.2, в соответствии с п.2 формулы изобретения, первое 4 токовое зеркало содержит первый 23, второй 24 и третий 25 вспомогательные транзисторы, эмиттер первого 23 вспомогательного транзистора является инвертирующим эмиттерным входом 10 первого 4 токового зеркала, эмиттер третьего 25 вспомогательного транзистора является неинвертирующим эмиттерным входом 13 первого 4 токового зеркала, коллектор второго 24 вспомогательного транзистора связан с токовым выходом 7 первого 4 токового зеркала, его база соединена с базовым входом 5 первого 4 токового зеркала и коллектором первого 23 вспомогательного транзистора, причем база первого 23 вспомогательного транзистора соединена с базой третьего 25 вспомогательного транзистора, а также подключена к эмиттеру второго 24 вспомогательного транзистора и коллектору третьего 25 вспомогательного транзистора, а цепь смещения потенциалов 22 выполнена в виде нескольких прямосмещенных р-n переходов.

Кроме того, на фиг.2, в соответствии с п.3 формулы изобретения, второе 17 токовое зеркало содержит четвертый 26 и пятый 27 вспомогательные транзисторы, эмиттеры которых связаны с общим эмиттерным выходом 21 второго 17 токового зеркала, база четвертого 26 и пятого 27 вспомогательных транзисторов соединены с коллектором четвертого 26 вспомогательного транзистора и базовым входом 19 второго 17 токового зеркала, причем коллектор пятого 27 вспомогательного транзистора соединен с токовым выходом 20 второго 17 токового зеркала.

На фиг.3, в соответствии с п.4 формулы изобретения, первое 4 токовое зеркало содержит шестой 28, седьмой 29 и восьмой 30 вспомогательные транзисторы, эмиттер шестого 28 вспомогательного транзистора является инвертирующим эмиттерным входом 10 первого 4 токового зеркала, эмиттер восьмого 30 вспомогательного транзистора является неинвертирующим эмиттерным входом 13 первого 4 токового зеркала, коллектор восьмого 30 вспомогательного транзистора связан с токовым выходом 7 первого 4 токового зеркала, его база соединена с базой шестого 28 вспомогательного транзистора и эмиттером седьмого 29 вспомогательного транзистора, коллектор седьмого 29 вспомогательного транзистора соединен с первым 3 источником питания, причем база седьмого 29 вспомогательного транзистора соединена с коллектором шестого 28 вспомогательного транзистора, а также подключена к базовому входу 5 первого 4 токового зеркала, а цепь смещения потенциалов 22 выполнена в виде прямосмещенного р-n перехода.

На фиг.4, в соответствии с п.5 формулы изобретения, первое 4 токовое зеркало содержит девятый 31 и десятый 32 вспомогательные транзисторы, эмиттер десятого 32 вспомогательного транзистора является инвертирующим эмиттерным входом 10 первого 4 токового зеркала, эмиттер девятого 31 вспомогательного транзистора является неинвертирующим эмиттерным входом 13 первого 4 токового зеркала, коллектор девятого 31 вспомогательного транзистора связан с токовым выходом 7 первого 4 токового зеркала, его база соединена с базой и коллектором десятого 32 вспомогательного транзистора и базовым входом 5 первого токового зеркала 4, а цепь смещения потенциалов 22 реализована в виде нескольких прямосмещенных р-n переходов.

Рассмотрим работу ДУ фиг.2.

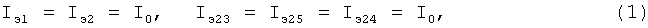

Статический режим транзисторов 1, 2, 23, 24 и 25 ДУ фиг.2 устанавливается источниками опорного тока 6, 8, 11, и 14. Если выбрать I6=I8=I0, а I11=I14=2I0, то

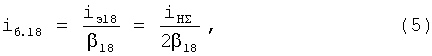

где Iэi - эмиттерный ток i-гo транзистора.

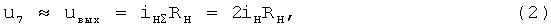

Если на вход Вх.(+)1 подается положительное напряжение uвх, то это вызывает увеличение напряжения на токовом выходе 7 (u7), а также напряжения на выходе 16 и, как следствие, напряжения на нагрузке RH:

где iHΣ=2iH - ток в нагрузке RH, iH - приращение эмиттерных токов транзисторов 26 и 27.

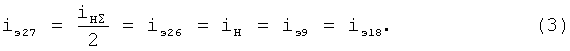

При этом ток в нагрузке RH увеличивается за счет изменения токов эмиттеров транзисторов 26 и 27 (9 и 18):

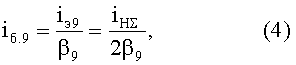

Как следствие, токи базы транзисторов 9 и 18:

где β9, β18 - коэффициенты усиления по току базы транзисторов 9 и 18.

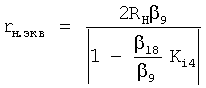

Приращение тока базы транзистора 18 iб18 передается на базовый вход 5 первого 4 токового зеркала, выходной ток которого i7 равен его входному току i7=iб18, так как коэффициент передачи по току первого 4 токового зеркала Ki4=1. Поэтому в узле 7 происходит взаимная компенсация двух близких по величине токов i7=iб18 и тока iб9 Как следствие, эквивалентное сопротивление нагрузки rн.экв, приведенное к узлу 7, повышается. Действительно эквивалентное сопротивление в узле 7, определяющее Ку дифференциального усилителя, определяется формулой

где

- эквивалентное сопротивление низкоомной нагрузки RH, приведенное к базовой цепи транзистора 9;

- эквивалентное сопротивление низкоомной нагрузки RH, приведенное к базовой цепи транзистора 9;

Rвых.8 - выходное сопротивление второго 8 источника опорного тока (Rвых.8>>rн.экв);

Rвых.4>>rн.экв - выходное сопротивление входного дифференциального каскада, образованного входными транзисторами 1 и 2 и токовым зеркалом 4, относительно его токового выхода 7;

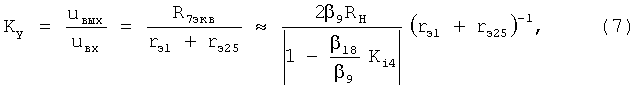

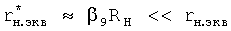

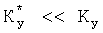

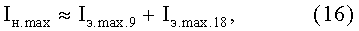

Ki4=1 - коэффициент усиления по току токового зеркала 4. Причем коэффициент усиления по напряжению

Для ДУ-прототипа  и, следовательно, его коэффициент усиления по напряжению

и, следовательно, его коэффициент усиления по напряжению  где

где

- эквивалентное сопротивление в узле 7 ДУ-прототипа;

- эквивалентное сопротивление в узле 7 ДУ-прототипа;

rэ1, rэ25 сопротивление эмиттерных переходов транзисторов 1 и 25.

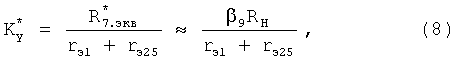

Таким образом, выигрыш по коэффициенту усиления, который дает предлагаемое техническое решение при β18=β9, Ki4=1, Rвых.8>>rн.экв

Предельные значения коэффициента NR (9) зависят от соотношений Rвых.4, Rвых.8 и rн.экв. Для получения наибольшего выигрыша по Ку необходимо использовать в качестве первого 4 токового зеркала схемы токовых зеркал Вильсона (фиг.2), которые обеспечивают наиболее высокие выходные сопротивления (см. п.2 формулы изобретения).

Анализ чертежа фиг.7 показывает, что предлагаемый ДУ имеет при RH=50 Ом почти в 100 раз лучшее усиление, чем ДУ-прототип. Еще больший выигрыш по Ку обеспечивается при более малых RH=4 Ом, например, в схемах компенсационного стабилизатора напряжения, реализованного на базе ДУ фиг.2 при подаче на его вход Вх.1(+) опорного напряжения и введения 100% обратной связи.

Таким образом, заявляемое техническое решение обеспечивает не только повышенный Ку, но и создает условия, когда дополнительные элементы, вводимые для повышения Ку, повышают стабильность нулевого уровня (фиг.8), (фиг.12).

Другие варианты выполнения первого 4 токового зеркала (фиг.3, фиг.4) дают несколько меньшие значения коэффициента N 9. Однако характеризуются другими достоинствами, повышающими параметры ДУ (частотный диапазон, диапазон изменения uвых и т.п.)

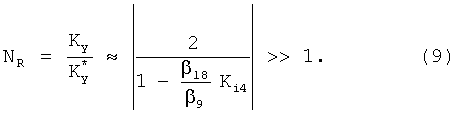

Максимальный рабочий ток в нагрузке RH заявляемого устройства Iн.max может быть в два раза больше, чем у ДУ-прототипа. Это связано с тем, что ток в RH создается двумя транзисторами 9 и 18:

где Iэ.mах.9, Iэ.mах.18 - предельные значения эмиттерного (коллекторного) тока транзисторов 9 и 18, зависящие от их конструктивных особенностей и тепловых эффектов.

Таким образом, предлагаемое техническое решение имеет ряд существенных преимуществ по сравнению с известной схемой.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Будяков П.С. Дифференциальные усилители для IP-модулей с малым напряжением питания [Текст] / П.С.Будяков // Проблемы современной аналоговой микросхемотехники: VII международный научно-практический семинар. В 2 ч. Ч.1 / гл. ред. Н.Н.Прокопенко; редкол.: В.Г.Немудров [и др.]. - Шахты: ГОУ ВПО «ЮРГУЭС», 2009. - С.63, рис.3.

2. Будяков П.С. Комплементарные СВЧ дифференциальные усилители с повышенной симметрией входных цепей для большого сигнала [Текст] / П.С.Будяков, А.И.Серебряков, Н.Н.Прокопенко // Проблемы современной аналоговой микросхемотехники: VII международный научно-практический семинар. В 2 Ч. 4.1 / гл. ред. Н.Н. Прокопенко; редкол.: В.Г.Немудров [и др.]. - Шахты: ГОУ ВПО «ЮРГУЭС», 2009. - С.47, рис.2.

3. Прокопенко Н.Н. Архитектура дифференциальных усилителей для технологического процесса SGB25VD [Текст] / Н.Н.Прокопенко, Д.Н.Конев, П.С.Будяков // Проблемы современной аналоговой микросхемотехники: VII международный научно-практический семинар. В 2 ч. Ч.1 / гл. ред. Н.Н. Прокопенко; редкол.: В.Г.Немудров [и др.]. - Шахты: ГОУ ВПО «ЮРГУЭС», 2009. - С.59, рис.6.

4. Операционные усилители и компараторы [Текст]. - М.: Издательский дом «Додэка - XXI», 2001. - С.240. Операционный усилитель ОР-42 (140УД30).

5. Патент US 6456162, fig.1, fig.2.

6. Патент US 5952882.

7. Патент US 4293824, fig.5.

8. Патент US 5523718, fig.2.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ ПРИ НИЗКООМНОЙ НАГРУЗКЕ | 2010 |

|

RU2421891C1 |

| КОМПЛЕМЕНТАРНЫЙ КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2439779C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ ПО НАПРЯЖЕНИЮ | 2010 |

|

RU2419186C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ ПО НАПРЯЖЕНИЮ | 2010 |

|

RU2420861C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2446554C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННОЙ СТАБИЛЬНОСТЬЮ НУЛЕВОГО УРОВНЯ | 2010 |

|

RU2419187C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2010 |

|

RU2432666C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412529C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2401507C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ | 2011 |

|

RU2455756C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, SiGe-операционных усилителях (ОУ), компараторах, стабилизаторах напряжения, различных аналогово-цифровых интерфейсах и т.п.). Технический результат: повышение на один-два порядка коэффициента усиления по напряжению разомкнутого ДУ при использовании сравнительно низкоомных двухполюсников нагрузки (например, RН=R0=5÷50 Ом). Дифференциальный усилитель содержит первый (1) и второй (2) входные транзисторы (Т), коллекторы которых соединены с первым (3) источником питания (ИП), первое (4) токовое зеркало (ТЗ), базовый вход (5) которого соединен с первым (3) ИП через первый (6) источник опорного тока (ИОТ), токовый выход (7) первого (4) ТЗ связан с первым (3) ИП через второй (8) ИОТ и соединен с базой первого (9) выходного Т, инвертирующий эмиттерный вход (10) первого (4) ТЗ соединен с эмиттером второго (2) входного Т и через третий (11) ИОТ связан со вторым (12) ИП, неинвертирующий эмиттерный вход (13) первого (4) ТЗ связан со вторым (12) ИП через четвертый (14) ИОТ и соединен с эмиттером первого (1) входного Т, пятый (15) токостабилизирующий двухполюсник, включенный между выходом устройства (16) и вторым (12) ИП, причем коллектор первого (9) выходного Т соединен с первым (3) ИП. В схему введено второе (17) ТЗ и второй (18) выходной Т, базовый вход (19) второго (17) ТЗ соединен с эмиттером первого (9) выходного Т, токовый выход (20) второго (17) ТЗ подключен к эмиттеру второго (18) выходного Т, общий эмиттерный выход (21) второго (17) ТЗ соединен с выходом устройства (16), коллектор второго (18) выходного Т подключен к первому (3) ИП, причем базовый вход (5) первого (4) ТЗ соединен с первым (3) ИП через последовательно соединенные цепь смещения потенциалов (22) и первый (6) ИОТ, общий узел последовательно соединенных цепи смещения потенциалов (22) и первого (6) ИОТ соединен с базой второго (18) выходного Т, а цепь смещения потенциалов (22) включена между базой второго (18) выходного Т и базовым входом (5) первого (4) ТЗ. 4 з.п. ф-лы, 12 ил.

1. Дифференциальный усилитель с повышенным коэффициентом усиления при низкоомной нагрузке, содержащий первый (1) и второй (2) входные транзисторы, коллекторы которых соединены с первым (3) источником питания, первое (4) токовое зеркало, базовый вход (5) которого соединен с первым (3) источником питания через первый (6) источник опорного тока, токовый выход (7) первого (4) токового зеркала связан с первым (3) источником питания через второй (8) источник опорного тока и соединен с базой первого (9) выходного транзистора, инвертирующий эмиттерный вход (10) первого (4) токового зеркала соединен с эмиттером второго (2) входного транзистора и через третий (11) источник опорного тока связан со вторым (12) источником питания, неинвертирующий эмиттерный вход (13) первого (4) токового зеркала связан со вторым (12) источником питания через четвертый (14) источник опорного тока и соединен с эмиттером первого (1) входного транзистора, пятый (15) токостабилизирующий двухполюсник, включенный между выходом устройства (16) и вторым (12) источником питания, причем коллектор первого (9) выходного транзистора соединен с первым (3) источником питания, отличающийся тем, что в схему введено второе (17) токовое зеркало и второй (18) выходной транзистор, базовый вход (19) второго (17) токового зеркала соединен с эмиттером первого (9) выходного транзистора, токовый выход (20) второго (17) токового зеркала подключен к эмиттеру второго (18) выходного транзистора, общий эмиттерный выход (21) второго (17) токового зеркала соединен с выходом устройства (16), коллектор второго (18) выходного транзистора подключен к первому (3) источнику питания, причем базовый вход (5) первого (4) токового зеркала соединен с первым (3) источником питания через последовательно соединенные цепь смещения потенциалов (22) и первый (6) источник опорного тока, общий узел последовательно соединенных цепи смещения потенциалов (22) и первого (6) источника опорного тока соединен с базой второго (18) выходного транзистора, а цепь смещения потенциалов (22) включена между базой второго (18) выходного транзистора и базовым входом (5) первого (4) токового зеркала.

2. Дифференциальный усилитель с повышенным коэффициентом усиления при низкоомной нагрузке по п.1, отличающийся тем, что первое (4) токовое зеркало содержит первый (23), второй (24) и третий (25) вспомогательные транзисторы, эмиттер первого (23) вспомогательного транзистора является инвертирующим эмиттерным входом (10) первого (4) токового зеркала, эмиттер третьего (25) вспомогательного транзистора является неинвертирующим эмиттерным входом (13) первого (4) токового зеркала, коллектор второго (24) вспомогательного транзистора связан с токовым выходом (7) первого (4) токового зеркала, его база соединена с базовым входом (5) первого (4) токового зеркала и коллектором первого (23) вспомогательного транзистора, причем база первого (23) вспомогательного транзистора соединена с базой третьего (25) вспомогательного транзистора, а также подключена к эмиттеру второго (24) вспомогательного транзистора и коллектору третьего (25) вспомогательного транзистора, а цепь смещения потенциалов (22) выполнена в виде нескольких прямосмещенных p-n переходов.

3. Дифференциальный усилитель с повышенным коэффициентом усиления при низкоомной нагрузке по п.1, отличающийся тем, что второе (17) токовое зеркало содержит четвертый (26) и пятый (27) вспомогательные транзисторы, эмиттеры которых связаны с общим эмиттерным выходом (21) второго (17) токового зеркала, базы четвертого (26) и пятого (27) вспомогательных транзисторов соединены с коллектором четвертого (26) вспомогательного транзистора и базовым входом (19) второго (17) токового зеркала, причем коллектор пятого (27) вспомогательного транзистора соединен с токовым выходом (20) второго (17) токового зеркала.

4. Дифференциальный усилитель с повышенным коэффициентом усиления при низкоомной нагрузке по п.1, отличающийся тем, что первое (4) токовое зеркало содержит шестой (28), седьмой (29) и восьмой (30) вспомогательные транзисторы, эмиттер шестого (28) вспомогательного транзистора является инвертирующим эмиттерным входом (10) первого (4) токового зеркала, эмиттер восьмого (30) вспомогательного транзистора является неинвертирующим эмиттерным входом (13) первого (4) токового зеркала, коллектор восьмого (30) вспомогательного транзистора связан с токовым выходом (7) первого (4) токового зеркала, его база соединена с базой шестого (28) вспомогательного транзистора и эмиттером седьмого (29) вспомогательного транзистора, коллектор седьмого (29) вспомогательного транзистора соединен с первым (3) источником питания, причем база седьмого (29) вспомогательного транзистора соединена с коллектором шестого (28) вспомогательного транзистора, а также подключена к базовому входу (5) первого (4) токового зеркала, а цепь смещения потенциалов (22) выполнена в виде прямосмещенного p-n перехода.

5. Дифференциальный усилитель с повышенным коэффициентом усиления при низкоомной нагрузке по п.1, отличающийся тем, что первое (4) токовое зеркало содержит девятый (31) и десятый (32) вспомогательные транзисторы, эмиттер десятого (32) вспомогательного транзистора является инвертирующим эмиттерным входом (10) первого (4) токового зеркала, эмиттер девятого (31) вспомогательного транзистора является неинвертирующим эмиттерным входом (13) первого (4) токового зеркала, коллектор девятого (31) вспомогательного транзистора связан с токовым выходом (7) первого (4) токового зеркала, его база соединена с базой и коллектором десятого (32) вспомогательного транзистора и базовым входом (5) первого токового зеркала (4), а цепь смещения потенциалов (22) реализована в виде нескольких прямосмещенных p-n переходов.

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2008 |

|

RU2384934C2 |

| Дифференциальный усилитель | 1983 |

|

SU1138922A1 |

| US 5568092 А, 22.10.1996 | |||

| US 5886577 А, 23.03.1999. | |||

Авторы

Даты

2011-06-20—Публикация

2010-04-05—Подача