Изобретение относится к области техники кодирования, программируемого декодирования или преобразования кода для обнаружения ошибок и их исправления и может быть использовано в приемных устройствах фазоманипулированных сигналов для оптимального декодирования принятой кодовой комбинации.

Из уровня техники известно устройство для определения логарифмического отношения правдоподобия с предварительным кодированием, содержащее радиоканал, на приемной стороне которого установлен радиоприемник, выход которого подключен к входу приемника данных через процессор принимаемых данных [Патент RU 2304352, МПК H04L 1/00, H04L 27/26, Н03М 13/45, 2002]. С помощью процессора принимаемых данных в известном устройстве уменьшается негативный эффект размножения ошибок при использовании турбокодов и сверточных кодов в качестве средств предварительного кодирования.

Недостаток известного устройство для определения логарифмического отношения правдоподобия состоит в том, что для его реализации требуется сложное оборудование и необходимо большое время для принятия «мягкого» решения по результату декодирования. Кроме того, применяемые турбокод и сверточный код в качестве средства предварительного кодирования способны выявить ошибку декодирования только при воздействии в радиоканале идеализированной случайной помехи в виде «белого» шума, которая имеет нулевое математическое ожидание и отсутствие какой-либо корреляции между всплесками ее проявления.

Наиболее близким к предлагаемому известным техническим решением в качестве прототипа является декодирующее устройство, содержащее фазовый детектор с выходным фильтром низкой частоты [Галкин В.А. Цифровая мобильная радиосвязь. Учебное пособие для вузов // М.: Горячая линия. - Телеком. - 2007. - С. 107, рис. 3.21. - 432 с.] и вычислитель логарифмических отношений функций правдоподобия (процессор принимаемых данных) с «мягким» входным и «мягким» выходным решениями [Скляр Б. Цифровая связь. Теоретические основы и практическое применение. 2-е изд., испр. Пер. с англ. М.: Издательский дом «Вильямс», 2007. - С. 502-519, рис. 8.21. - 1104 с.], с помощью которого реализуются дискретные апостериорные значения логарифмического отношения функций правдоподобия, что обеспечивает снижение вероятности появления битовой ошибки как функции отношения энергии элементарного (битового) символа к мощности шума (Eb/N0) при увеличении количества итераций.

Недостаток прототипа заключается в том, что для вынесения «мягкого» решения о результате итеративного (турбо) декодирования принятой кодовой комбинации принимаются «жесткие» решения, а именно: «1» или «0» на входе декодера, что не отвечает в полной мере критерию энергетической эффективности сигнально-кодовой конструкции бинарного цифрового сигнала. Низкая энергетическая эффективность сигнально-кодовой конструкции бинарного цифрового сигнала снижает дальность радиосвязи для обеспечения заданной необходимой достоверности принятого сообщения. Другой недостаток прототипа состоит в том, что большое количество итераций определяет требуемую точность работы демодулятора бинарного цифрового сигнала с одновременным увеличением времени демодуляции.

Технической задачей изобретения является повышение энергетической эффективности сигнально-кодовой конструкции передаваемого бинарного цифрового сигнала с одновременным уменьшением времени демодуляции.

Технический результат изобретения состоит в том, что повышаются быстродействие некогерентного демодулятора бинарного цифрового сигнала с мягким итеративным декодированием данных с обеспечением наивысшей достоверности его работы до значения, близкого к предельно возможной границе (пределу) Клода Шеннона.

Сущность изобретения состоит в том, что, кроме известных и общих существенных отличительных признаков, а именно: фазового детектора бинарного цифрового сигнала с выходным фильтром низкой частоты и вычислителя логарифмического отношения функций правдоподобия, предлагаемый некогерентный демодулятор бинарного цифрового сигнала с мягким итеративным декодированием данных содержит последовательно соединенные элемент ИЛИ на два входа, частотомер и решающий блок на два входа, дискретизатор и последовательно соединенные генератор тактовых импульсов, реверсивный счетчик, цифроаналоговый преобразователь и блок сравнения на два входа и два выхода, второй вход которого подключен к выходу дискретизатора, один вход которого связан с выходом генератора тактовых импульсов и с вторым входом решающего блока, другой вход дискретизатора подсоединен к выходу фильтра низкой частоты, один выход блока сравнения подключен к прямому счетному входу реверсивного счетчика, а другой выход блока сравнения связан с инверсным счетным входом реверсивного счетчика, выходы реверсивного счетчика подключены к входам вычислителя логарифмического отношения функций правдоподобия, управляющий вход которого подключен к выходу решающего блока, выходы блока сравнения подсоединены к входам элемента ИЛИ.

Новизна изобретения заключается в том, что предлагаемый некогерентный демодулятор бинарного цифрового сигнала с мягким итеративным декодированием данных содержит последовательно соединенные элемент ИЛИ на два входа, частотомер и решающий блок на два входа, дискретизатор и последовательно соединенные генератор тактовых импульсов, реверсивный счетчик, цифроаналоговый преобразователь и блок сравнения на два входа и два выхода, второй вход которого подключен к выходу дискретизатора, один вход которого связан с выходом генератора тактовых импульсов и с вторым входом решающего блока, другой вход дискретизатора подсоединен к выходу фильтра низкой частоты, один выход блока сравнения подключен к прямому счетному входу реверсивного счетчика, а другой выход блока сравнения связан с инверсным счетным входом реверсивного счетчика, выходы реверсивного счетчика подключены к информационным входам вычислителя логарифмического отношения функций правдоподобия, управляющий вход которого подключен к выходу решающего блока, выходы блока сравнения подсоединены к входам элемента ИЛИ, что обеспечивает повышение быстродействия демодулятора с мягким итеративным декодированием данных с обеспечением наивысшей достоверности декодирования до значения, близкого к предельно возможной границе Клода Шеннона.

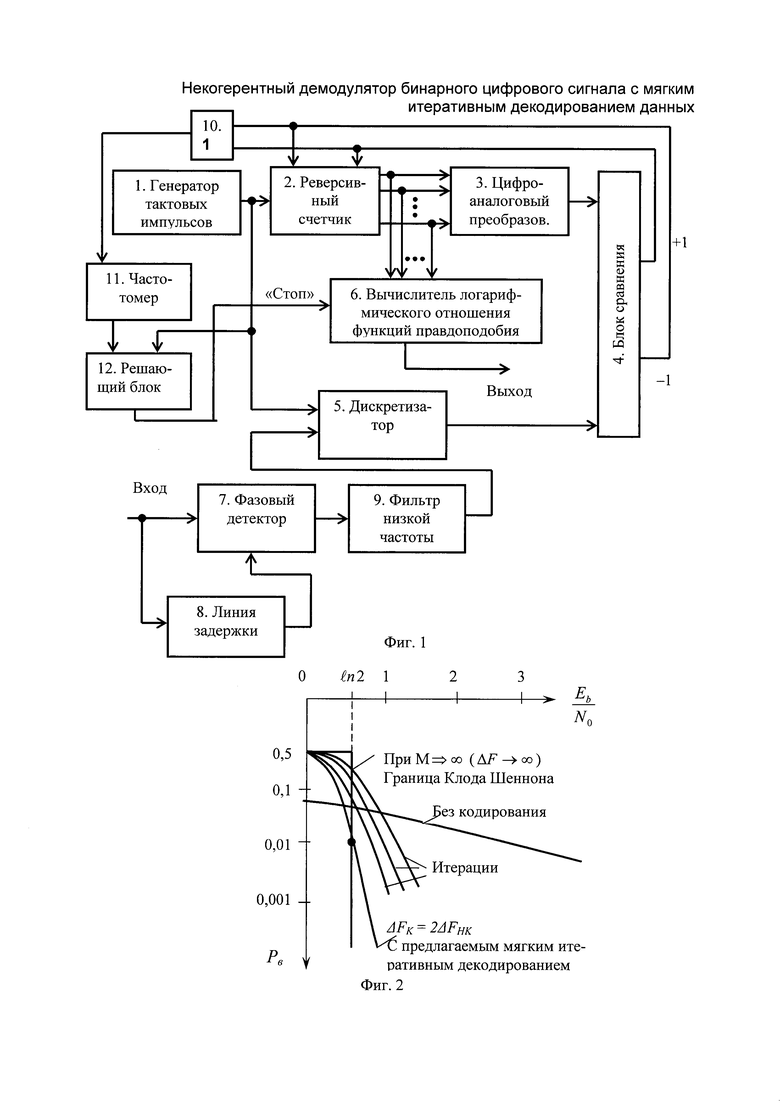

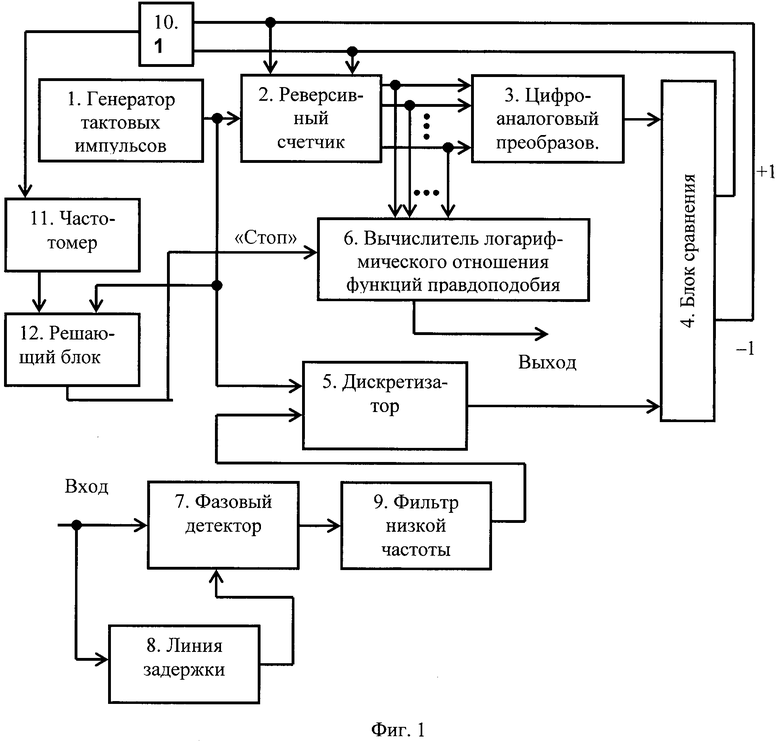

Схема предлагаемого некогерентного демодулятора бинарного цифрового сигнала с мягким итеративным декодированием данных приведена на фиг. 1, семейство графических зависимостей вероятностей безошибочного приема элементарного дискретного символа принимаемого бинарного цифрового сигнала от соотношения мощностей элементарного (битового) символа бинарного цифрового сигнала и помехи изображено на фиг. 2.

На фиг. 1 обозначено:

1 - генератор тактовых импульсов;

2 - реверсивный счетчик;

3 - цифроаналоговый преобразователь;

4 - блок сравнения на два входа и два выхода с возможностью оценки результата сравнения амплитуд;

5 - дискретизатор;

6 - вычислитель логарифмического отношения функций правдоподобия (процессор);

7 - фазовый детектор;

8 - линия задержки на интервал времени, равный длительности радиоимпульса фазоманипулированного сигнала;

9 - фильтр низкой частоты;

10 - элемент ИЛИ на два входа;

11 - частотомер;

12 - решающий блок на два входа.

В исходном положении (статика) выход генератора тактовых импульсов 1 подключен через последовательно соединенные реверсивный счетчик 2 и цифроаналоговый преобразователь 3 к одному входу блока сравнения 4, другой вход которого подключен к выходу дискретизатора 6. Выходы реверсивного счетчика 2 соединены с входами вычислителя логарифмического отношения функций правдоподобия 6. Один выход блока сравнения 4 подключен к прямому счетному входу реверсивного счетчика 2, а другой выход блока сравнения 4 связан с инверсным счетным входом реверсивного счетчика 2. Тактовый вход дискретизатора 5 подсоединен к выходу генератора тактовых импульсов 1. Вход предлагаемого некогерентного демодулятора бинарного цифрового сигнала с мягким итеративным декодированием данных подключен к одному входу фазового детектора 7 непосредственно, а к другому входу фазового детектора 7 подсоединена входная цепь предлагаемого устройства через линию задержки 8. Выход фазового детектора 7 связан через фильтр низкой частоты 9 с информационным входом дискретизатора 5. Выходы вычислителя логарифмического отношения функций правдоподобия 6 являются выходом предлагаемого некогерентного демодулятора бинарного цифрового сигнала с мягким итеративным декодированием данных. Выходы блока сравнения 4 подключены через элемент ИЛИ 10 и частотомер 11 к одному входу решающего блока 12, другой вход которого связан с выходом генератора тактовых импульсов 1. Выход решающего блока 12 подключен к управляющему входу вычислителя логарифмического отношения функций правдоподобия 6.

Предлагаемый некогерентный демодулятор бинарного цифрового сигнала с мягким итеративным декодированием данных работает следующим образом.

Входной бинарный, например фазоманипулированный, цифровой сигнал поступает на один вход фазового детектора 7 непосредственно, на другой вход этого фазового детектора 7 принимаемый бинарный цифровой сигнал направляется через линию задержки 8. Время задержки линии задержки 8 равно временному интервалу t0 передачи одного элементарного (бинарного) символа цифрового сигнала, что обеспечивает его некогерентный прием. Генератор тактовых импульсов 1 вырабатывает тактовые импульсы с периодом следования tТ, удовлетворяющим неравенству вида:

Реверсивный счетчик 2 накапливает поступающие на его счетный вход тактовые импульсы, если амплитуды выходного дискретного сигнала дискретизатора 5 U5 превышают амплитуды выходного сигнала цифроаналогового преобразователя 3 U3 в каждом такте работы генератора тактовых импульсов 1, то есть при каждой итерации. Сравнение упомянутых амплитуд сигналов U5 и U3 происходит на входах блока сравнения 4. При выполнении условия

с одного из двух выходов блока сравнения 4 поступает управляющий импульс на прямой вход (+1) реверсивного счетчика 2 для увеличения его накопленного значения импульсов.

Если условие (2) не выполняется, а имеет место неравенство вида

то с другого выхода блока сравнения 4 поступает управляющий импульс на инверсный вход (-1) реверсивного счетчика 2 для уменьшения его накопленного значения счетных импульсов. Одновременно с выходов блока сравнения управляющие импульсы поступают через элемент ИЛИ 10 на вход частотомера 11, с помощью которого определяется частота, то есть длительность итерации в единицу времени. Выходной сигнал частотомера 11 сравнивается с выходным сигналом генератора тактовых импульсов 1 по частоте (по периоду следования) с помощью решающего блока 12. Если сравниваемые частоты близки между собой, то выходной сигнал решающего блока 12 «Стоп» направляется на управляющий вход вычислителя логарифмического отношения функций правдоподобия 6 для его остановки. До поступления управляющего сигнала «Стоп» выходные импульсные сигналы реверсивного счетчика 2 направлялись на информационные входы вычислителя логарифмического отношения функций правдоподобия 6, с помощью которых обеспечивается наивысшая достоверность декодирования бинарного цифрового сигнала, что проиллюстрировано на фиг. 2. Из фиг. 2 следует, что наивысшая достоверность декодирования бинарного цифрового сигнала приближается до значения, близкого к предельно возможной границе (пределу) Клода Шеннона. В прототипе требовалось чрезмерно большое значение итераций и, соответственно, времени демодуляции. В предлагаемом устройстве за счет автоматического отслеживания времени итерации с периодом следования тактовых импульсов обеспечивается максимальное быстродействие некогерентного демодулятора бинарного цифрового сигнала с мягким итеративным декодированием данных.

Промышленная осуществимость изобретения обосновывается тем, что в нем использованы известные в аналоге и прототипе узлы и элементы по своему прямому функциональному назначению. В организации-заявителе изготовлена модель заявленного некогерентного демодулятора бинарного цифрового сигнала с «мягким» итеративным декодированием данных в 2015 г.

Положительный эффект от использования изобретения состоит в том, что повышается быстродействие некогерентного демодулятора бинарного цифрового сигнала с обеспечением максимальной достоверности декодирования бинарного цифрового сигнала до значения, близкого к предельно возможной границе (пределу) Клода Шеннона.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ И УСТРОЙСТВО ПОМЕХОУСТОЙЧИВОГО ДЕКОДИРОВАНИЯ СИГНАЛОВ, ПОЛУЧЕННЫХ С ИСПОЛЬЗОВАНИЕМ КОДА ПРОВЕРКИ НА ЧЕТНОСТЬ С НИЗКОЙ ПЛОТНОСТЬЮ | 2013 |

|

RU2522299C1 |

| УСТРОЙСТВО ИТЕРАТИВНОГО ДЕКОДИРОВАНИЯ БЛОКОВЫХ ТУРБОКОДОВ И SISO ДЕКОДЕР ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2012 |

|

RU2504901C2 |

| РАДИОМОДЕМ | 2024 |

|

RU2830959C1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ ТУРБОКОДОВ | 2009 |

|

RU2393633C1 |

| ЦЕНТРАЛЬНАЯ СТАНЦИЯ СИСТЕМЫ РАДИОСВЯЗИ С ПОДВИЖНЫМИ ОБЪЕКТАМИ | 2022 |

|

RU2780810C1 |

| СПОСОБ ИТЕРАТИВНОГО ДЕТЕКТИРОВАНИЯ И ДЕКОДИРОВАНИЯ СИГНАЛА В СИСТЕМАХ СВЯЗИ С MIMO КАНАЛОМ | 2012 |

|

RU2523190C1 |

| СИСТЕМА ПЕРЕДАЧИ ДАННЫХ ОРТОГОНАЛЬНЫМИ КОДОВЫМИ ПОСЛЕДОВАТЕЛЬНОСТЯМИ И ДВУХСТУПЕНЧАТОЙ ФАЗОВОЙ СИНХРОНИЗАЦИЕЙ | 2022 |

|

RU2829154C2 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ ТУРБОКОДОВ | 2007 |

|

RU2369961C2 |

| ЦИФРОВОЙ МОДЕМ КОМАНДНОЙ РАДИОЛИНИИ ЦМ КРЛ | 2013 |

|

RU2548173C2 |

| ПРИЕМНИК СИГНАЛОВ С ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 1989 |

|

RU2018206C1 |

Изобретение относится к области техники кодирования, программируемого декодирования и может быть использовано в приемных устройствах для оптимального декодирования принятой кодовой комбинации. Достигаемый технический результат - повышение быстродействия с обеспечением наивысшей достоверности его работы до значения, близкого к предельно возможному пределу Клода Шеннона. Некогерентный демодулятор бинарного цифрового сигнала с мягким итеративным декодированием данных содержит фазовый детектор с выходным фильтром низкой частоты, вычислитель логарифмического отношения функций правдоподобия, последовательно соединенные элемент ИЛИ, частотомер и решающий блок, дискретизатор и последовательно соединенные генератор тактовых импульсов, реверсивный счетчик, цифроаналоговый преобразователь и блок сравнения. 2 ил.

Некогерентный демодулятор бинарного цифрового сигнала с мягким итеративным декодированием данных, содержащий фазовый детектор с выходным фильтром низкой частоты и вычислитель логарифмического отношения функций правдоподобия, отличающийся тем, что содержит последовательно соединенные элемент ИЛИ на два входа, частотомер и решающий блок на два входа, дискретизатор и последовательно соединенные генератор тактовых импульсов, реверсивный счетчик, цифроаналоговый преобразователь и блок сравнения на два входа и два выхода, второй вход которого подключен к выходу дискретизатора, один вход которого связан с выходом генератора тактовых импульсов и с вторым входом решающего блока, другой вход дискретизатора подсоединен к выходу фильтра низкой частоты, один выход блока сравнения подключен к прямому счетному входу реверсивного счетчика, а другой выход блока сравнения связан с инверсным счетным входом реверсивного счетчика, выходы реверсивного счетчика подключены к информационным входам вычислителя логарифмического отношения функций правдоподобия, управляющий вход которого подключен к выходу решающего блока, выходы блока сравнения подсоединены к входам элемента ИЛИ.

| СПОСОБ И УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ЛОГАРИФМИЧЕСКОГО ОТНОШЕНИЯ ПРАВДОПОДОБИЯ С ПРЕДВАРИТЕЛЬНЫМ КОДИРОВАНИЕМ | 2002 |

|

RU2304352C2 |

| УСТРОЙСТВО ДЛЯ НЕКОГЕРЕНТНОЙ ДЕМОДУЛЯЦИИ ЧАСТОТНО-МАНИПУЛИРОВАННЫХ СИГНАЛОВ С НЕПРЕРЫВНОЙ ФАЗОЙ | 2005 |

|

RU2308165C1 |

| US 5260975 A, 09.11.2993 | |||

| Топчак-трактор для канатной вспашки | 1923 |

|

SU2002A1 |

Авторы

Даты

2016-03-10—Публикация

2015-02-11—Подача