Группа изобретений относится к устройству декодирования блоковых турбокодов и SISO декодеру для его реализации и может быть использована в цифровых системах связи.

Известно, что блоковые турбокоды формируются на основе объединения блоковых кодов, в частности объединения кодов Хэмминга или расширенных кодов Хэмминга [1].

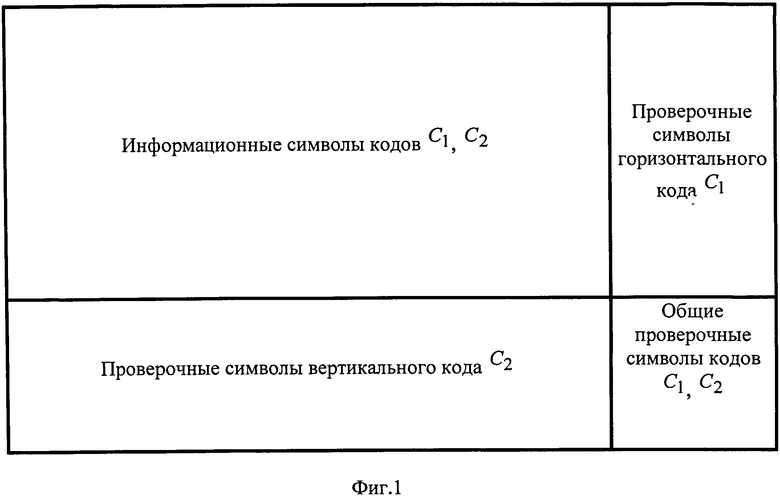

На фиг.1 приведена схема блокового турбокода. Кодовые слова блокового турбокода эквивалентны двумерной матрице - строки матрицы соответствуют кодовым словам составляющего блокового кода C1 с параметрами (n1, k1), столбцы матрицы соответствуют кодовым словам составляющего блокового кода C2 с параметрами (n2, k2). Здесь n - количество кодовых символов в кодовых словах, k - количество информационных символов составляющего кода. Общее количество информационных символов турбокода равно k=k1k2, общее количество кодовых символов в кодовых словах равно n=n1n2.

Для турбокодов применяются алгоритмы итеративного декодирования [1], суть итерации которых - вычисление мягких символьных решений на основе алгоритма посимвольного декодирования для горизонтальных (вертикальных) составляющих кодов и использование данных символьных мягких решений для последующей итерации при декодировании вертикальных (горизонтальных) составляющих кодов.

Вычисление мягких символьных решений производится при помощи SISO декодера (Soft Input - Soft Output) с мягким входом и мягким выходом.

Окончание декодирования происходит после выполнения задаваемого количества итераций. После завершения последней итерации принимаются жесткие (бинарные) решения о передаваемых информационных символах.

Из уровня техники известно устройство [2] итеративного декодирования блоковых турбокодов и SISO декодер. Устройство содержит три блока оперативной памяти, два сумматора, SISO (Soft Input - Soft Output) декодер, блок принятия решений и схему нормировки. Обрабатываемые отсчеты демодулятора сигналов хранятся в первом блоке оперативной памяти, выход которого соединен с первым входом первого сумматора и с инвертированным входом второго сумматора, выход первого сумматора подключен к входу SISO декодера, выход которого соединен с первым входом второго сумматора и с входом блока принятия решений, выход второго сумматора подключен к входу второго блока оперативной памяти, выход которого соединен с входом схемы нормировки, выход которой подключен к второму входу первого сумматора, выход блока принятия решений соединен с входом третьего блока оперативной памяти, в котором помещены жесткие решения относительно переданных кодовых символов при выполнении заданного числа итераций, выход третьего блока оперативной памяти является выходом устройства итеративного декодирования блоковых турбокодов. SISO декодер включает в себя последовательно соединенные блок декодирования по алгоритму Чейза [3], блок вычисления правдоподобия гипотетических кодовых слов и блок вычисления мягких выходных решений. Декодер реализует правило посимвольного приема сигналов на основе блоковых кодов. Этот декодер содержит последовательно соединенные блоки: блок вычисления разности апостериорных символьных вероятностей, первый и второй блоки формирования анализируемой последовательности, первый формирователь сигналов коэффициентов функции Уолша, первый сумматор и первый блок вычитания, блок вычисления функции экспоненциального типа, второй формирователь сигналов коэффициентов функции Уолша, блок изменения знаков, третий блок формирования анализируемой последовательности, второй сумматор, третий формирователь сигналов коэффициентов функции Уолша, третий сумматор, второй блок вычитания и блок оценки апостериорных символьных вероятностей.

Недостатком описанного устройства является сложность его аппаратной реализации, которая определяется сложностью выполнения SISO декодера. Недостатком данного декодера является то, что в нем не вычисляются мягкие решения относительно передаваемых кодовых символов, а также сложность его реализации, обусловленная сложностью промежуточных вычислений при оценке апостериорных символьных вероятностей с использованием трех формирователей сигналов коэффициентов функции Уолша.

Из уровня техники известно устройство [4] итеративного декодирования блоковых турбокодов, отчасти преодолевающее сложность выполнения SISO декодера, и SISO декодер, содержащий последовательно соединенные блок декодирования по алгоритму Чейза и блок вычисления мягких выходных значений. Данное устройство содержит три блока оперативной памяти, два сумматора, SISO декодер, блок принятия решений и схему нормировки. Входом устройства является вход первого блока оперативной памяти, выход которого соединен с первым входом первого сумматора и с инверсным входом второго сумматора, выход первого сумматора подключен к входу SISO декодера, выход которого соединен с первым входом второго сумматора и с входом блока принятия решений, выход которого соединен с входом третьего блока оперативной памяти, выход второго сумматора соединен с входом второго блока оперативной памяти, выход которого подключен к схеме нормировки, выход которой соединен со вторым входом первого сумматора. SISO декодер включает последовательно соединенные блок декодирования по алгоритму Чейза и блок вычисления мягких выходных значений.

Недостатком устройства итеративного декодирования блоковых турбокодов является низкая помехоустойчивость по отношению к потенциально возможной помехоустойчивости данных турбокодов вследствие использования неоптимального алгоритма декодирования Чейза.

Известен декодер [5] на основе алгоритма Рудольфа-Хартмана. Устройство содержит блок оперативной памяти, формирователь сигналов коэффициентов функции Уолша, детектор максимального сигнала, формирователь знака, генератор тактовых импульсов, ключ, два счетчика, блок поразрядного умножения, блок постоянной памяти, блок контроля четности. Вход детектора максимального сигнала соединен с первым выходом формирователя сигналов коэффициентов функции Уолша, информационные входы формирователя знака соединены с соответствующими выходами блока оперативной памяти, выходы формирователя знаков соединены с соответствующими информационными входами формирователя сигналов коэффициентов функции Уолша, второй выход которого соединен с первым входом ключа, второй вход которого соединен с выходом генератора тактовых импульсов, а выход соединен с входом первого счетчика, первые установочные выходы которого соединены с соответствующими адресными входами блока оперативной памяти и блока постоянной памяти, другой установочный выход первого счетчика соединен с входом второго счетчика, с синхронизирующим входом формирователя сигналов коэффициентов Уолша и с третьим входом ключа, первые установочные выходы второго счетчика соединены с соответствующими первыми входами блока поразрядного умножения, вторые входы которого соединены с соответствующими выходами блока постоянной памяти, выход блока поразрядного умножения соединен с входом блока контроля четности, выход которого соединен с управляющим входом формирователя знака, установочный выход второго счетчика соединен с четвертым входом ключа. Вход блока оперативной памяти является входом устройства, выход детектора максимального сигнала является выходом устройства.

Недостатком данного устройства является то, что в нем не вычисляются мягкие решения относительно передаваемых кодовых символов, а вычисляются только бинарные (жесткие) решения.

Техническим результатом заявленных изобретений (устройства итеративного декодирования блоковых турбокодов и SISO декодера его реализации) является повышение помехоустойчивости блоковых турбокодов.

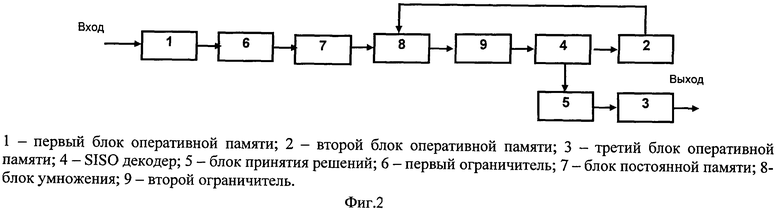

Технический результат заявленного изобретения - устройства достигается тем, что устройство итеративного декодирования блоковых турбокодов содержит первый, второй и третий блоки оперативной памяти, SISO декодер, блок принятия решений, вход которого соединен с первым выходом SISO декодера, а выход подключен к входу третьего блока оперативной памяти, выход которого является выходом устройства, а входом устройства является вход первого блока оперативной памяти, при этом в устройство введены блок умножения, первый и второй ограничители, блок постоянной памяти, при этом выход первого блока оперативной памяти подключен к входу первого ограничителя, выход которого соединен с входом блока постоянной памяти, выход которого подключен к первому входу блока умножения, второй вход которого соединен с выходом второго блока оперативной памяти, а выход подключен к входу второго ограничителя, выход которого соединен с входом SISO декодера, второй выход которого подключен к входу второго блока оперативной памяти.

SISO декодер для устройства итеративного декодирования блоковых турбокодов содержит блок оперативной памяти, вход которого является входом SISO декодера, последовательно соединенные соответственно тактовый генератор, ключ и счетчик, блок постоянной памяти, формирователь сигналов коэффициентов функции Уолша, адресный вход которого подключен к выходу счетчика, при этом в SISO декодер введены формирователь анализируемой последовательности, первый, второй и третий сумматоры, первый и второй блоки вычитания, блок умножения на два, блок умножения, первый, второй и третий блоки деления, ограничитель, при этом выход счетчика соединен с адресными входами блока оперативной памяти, первый выход которого соединен с входом блока постоянной памяти, первый выход которого подключен к входу формирователя анализируемой последовательности, выход которого соединен с сигнальным входом формирователя сигналов коэффициентов функции Уолша, первый выход формирователя сигналов коэффициентов функции Уолша соединен с первым входом первого сумматора и с первым входом первого блока вычитания, а его второй выход подключен к второму входу первого сумматора, к второму входу первого блока вычитания и к входу блока умножения на два, выход первого блока вычитания соединен с первым входом первого блока деления, выход первого сумматора подключен к первому входу блока умножения, второй вход которого и второй вход первого блока деления соединены с вторым выходом блока постоянной памяти, выход первого блока деления подключен к первому входу второго сумматора, второй вход которого соединен с выходом блока умножения, выход второго сумматора подключен к первому входу второго блока вычитания и к первому входу третьего сумматора, второй вход которого и второй вход второго блока вычитания соединены с выходом блока умножения на два, выход второго блока вычитания соединен с первым входом второго блока деления, второй вход которого подключен к выходу третьего сумматора, первый выход второго блока деления является первым выходом SISO декодера, а его второй выход соединен с первым входом третьего блока деления, второй вход которого подключен к второму выходу блока оперативной памяти, выход третьего блока деления соединен с входом ограничителя, выход которого является вторым выходом SISO декодера, второй вход ключа является управляющим входом SISO декодера.

SISO декодер вычисляет наряду с жесткими решениями также и мягкие решения на основе алгоритма Рудольфа-Хартмана и позволяет повысить помехоустойчивость блоковых турбокодов.

Сущность заявленной группы изобретений поясняется чертежами, где показано следующее:

Фиг.1 - структура блоковых турбокодов, где

C1, C2 - составляющие блоковые коды блокового турбокода.

Фиг.2 - блок-схема устройства итеративного декодирования блоковых турбокодов, где

1 - первый блок оперативной памяти;

2 - второй блок оперативной памяти;

3 - третий блок оперативной памяти;

4 - SISO декодер;

5 - блок принятия решений;

6 - первый ограничитель;

7 - блок постоянной памяти;

8 - блок умножения;

9 - второй ограничитель.

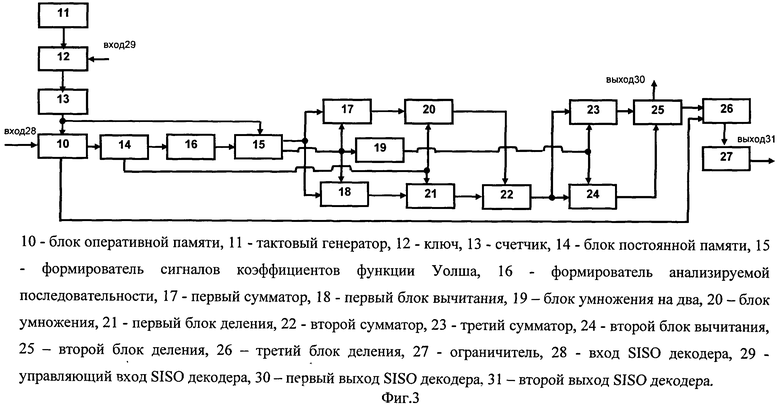

Фиг.3 - блок-схема SISO декодера для устройства итеративного декодирования блоковых турбокодов, где

10 - блок оперативной памяти;

11 - тактовый генератор;

12 - ключ;

13 - счетчик;

14 - блок постоянной памяти;

15 - формирователь сигналов коэффициентов функции Уолша;

16 - формирователь анализируемой последовательности;

17 - первый сумматор;

18 - первый блок вычитания;

19 - блок умножения на два;

20 - блок умножения;

21 - первый блок деления;

22 - второй сумматор;

23 - третий сумматор;

24 - второй блок вычитания;

25 - второй блок деления;

26 - третий блок деления;

27 - ограничитель;

28 - вход декодера;

29 - управляющий вход SISO декодера;

30 - первый выход SISO декодера;

31 - второй выход SISO декодера.

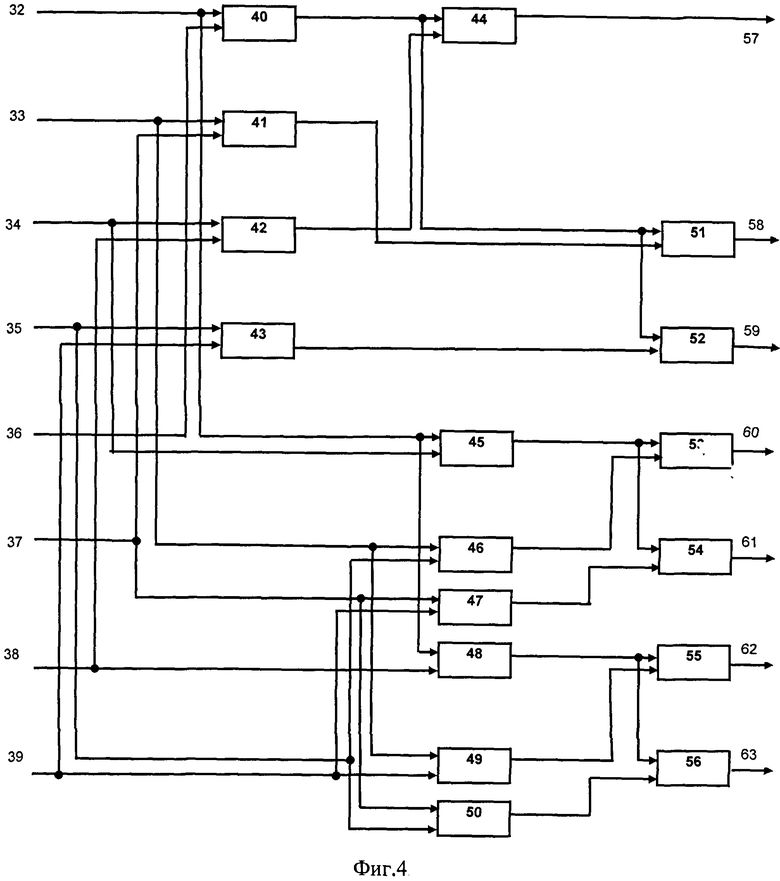

Фиг.4 - блок-схема формирователя анализируемой последовательности, где 32, 33, 34, 35, 36, 37, 38, 39 - входы формирователя анализируемой последовательности;

40, 41, 42, 43 - блоки умножения первого столбца блок-схемы;

44, 45, 46, 47, 48, 49, 50 - пятнадцатый, шестнадцатый, семнадцатый, восемнадцатый, девятнадцатый, двадцатый, двадцать первый, двадцать второй, двадцать третий, двадцать четвертый и двадцать пятый блоки умножения второго столбца блок-схемы;

51, 52, 53, 54, 55, 56 - блоки умножения третьего столбца блок-схемы;

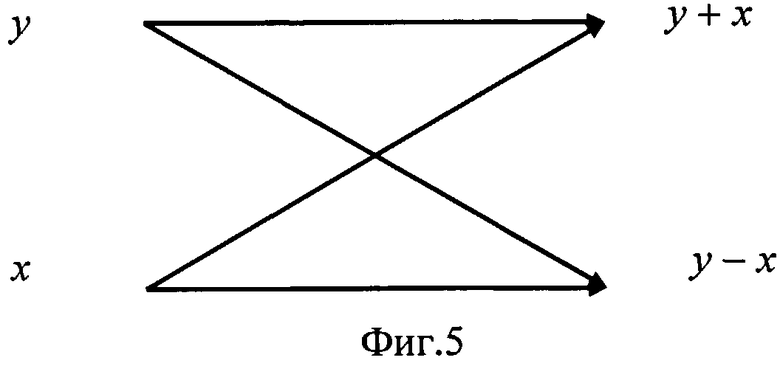

Фиг.5 - схема базового элемента алгоритма быстрого спектрального преобразования в базисе Уолша с операциями "сложение-вычитание";

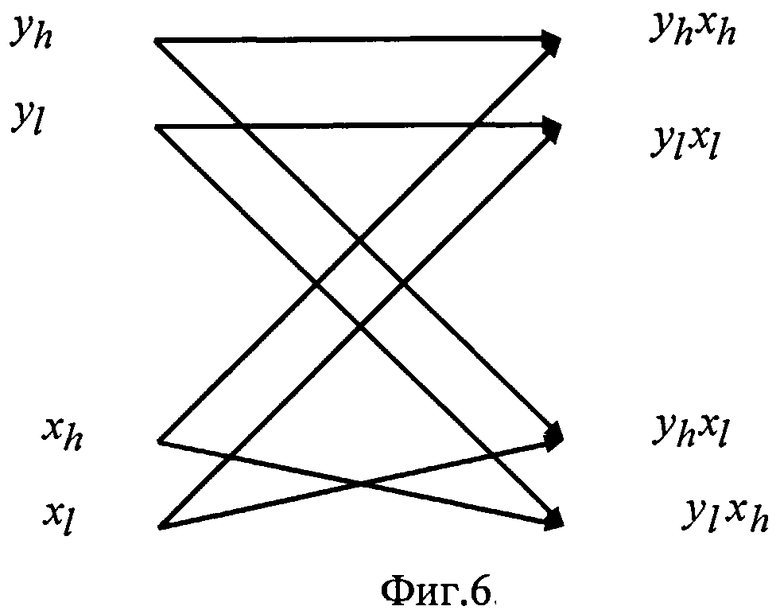

Фиг.6 - схема базового элемента модифицированного алгоритма быстрого спектрального преобразования в базисе Уолша с операцией "умножение".

Выход первого блока оперативной памяти 1 подключен к входу первого ограничителя 6. Выход первого ограничителя 6 соединен с входом блока постоянной памяти 7. Выход блока постоянной памяти 7 подключен к первому входу блока умножения 8, второй вход которого подключен к выходу второго блока оперативной памяти 2. Выход блока умножения 8 соединен с входом второго ограничителя 9. Выход второго ограничителя 9 подключен к входу SISO декодера 4. Первый выход SISO декодера 4 соединен с входом блока принятия решений 5. Второй выход SISO декодера 4 подключен к входу второго блока оперативной памяти 2. Выход блока принятия решений 5 соединен с входом третьего блока оперативной памяти 3. Выход третьего блока оперативной памяти 3 является выходом устройства итеративного декодирования блоковых турбокодов.

Входом SISO декодера ("вход 28") является вход блока оперативной памяти 10. Выход тактового генератора 11 соединен с входом ключа 12. Выход ключа 12 подключен к входу счетчика 13. Выход счетчика 13 соединен с адресными входами блока оперативной памяти 10 и формирователя сигналов коэффициентов функции Уолша 15. Первый выход блока оперативной памяти 10 подключен к входу блока постоянной памяти 14. Первый выход блока 14 соединен с входом формирователя анализируемой последовательности 16. Выход формирователя 16 подключен к сигнальным входам формирователя сигналов коэффициентов функции Уолша 15. Первый выход формирователя 15 соединен с первым входом первого сумматора 17 и с первым входом (уменьшаемого) первого блока вычитания 18. Второй выход формирователя 15 соединен с вторым входом первого сумматора 17, с вторым входом (вычитаемого) первого блока вычитания 18 и с входом блока умножения на два 19. Выход первого блока вычитания 18 подключен к первому входу (делимого) первого блока деления 2. Выход первого сумматора 17 соединен с первым входом блока умножения 20. Второй вход блока 20 и второй вход (делителя) первого блока деления 21 подключены к второму выходу блока постоянной памяти 14. Выход первого блока деления 21 соединен с первым входом второго сумматора 22. Второй вход сумматора 22 подключен к выходу блока умножения 20. Выход сумматора 22 соединен с первым входом (вычитаемого) второго блока вычитания 24 и с первым входом третьего сумматора 23. Второй вход сумматора 23 соединен с выходом блока умножения на два 19 и с вторым входом (уменьшаемого) второго блока вычитания 24. Выход блока 24 соединен с первым входом (делителя) второго блока деления 25. Второй вход (делимого) блока 25 соединен с выходом третьего сумматора 23. Первый выход второго блока деления 25 является первым выходом 30 SISO декодера. Второй выход декодера соединен с вторым входом (делимого) третьего блока деления 26. Второй вход (делителя) блока 26 соединен с вторым выходом блока оперативной памяти 10. Выход третьего блока деления 26 соединен с входом ограничителя 27. Выход ограничителя 27 является вторым выходом SISO декодера - "выход 31". Вход ключа 12 "вход 29" является управляющим входом SISO декодера.

Блок-схема формирователя анализируемой последовательности 16 приведена на фиг.4 для частного случая составляющего блокового кода Хэмминга с параметрами (7, 4), то есть объем кодовых слов кода равен 24 (k=4), длительность кодовых слов равна n=7. Основу вычислительной процедуры, которая реализуется формирователем 16 при подготовке анализируемой последовательности, составляет модифицированный алгоритм быстрого спектрального преобразования в базисе Уолша-Адамара с базовой операцией "умножение". Исходный алгоритм быстрого спектрального преобразования в базисе Уолша размерностью 2l (здесь l - параметр алгоритма спектрального преобразования) представляется направленным графом, содержащем l столбцов, каждый столбец содержит 2l-1 базовых элементов с операциями "сложение-вычитание".

Входы 32, 33, 34, 35, 36, 37, 38, 39 формирователя анализируемой последовательности 16 подключены к соответствующим сигнальным выходам блока постоянной памяти 14, Блок-схема содержит три столбца. Входы блоков умножения 40, 41, 42, 43 в составе первого столбца подключены соответственно к 32 и 36, к 33 и 37, к 34 и 38, к 35 и 39 сигнальным входам формирователя 16 анализируемой последовательности.

Входы блока умножения 44 в составе второго столбца подключены соответственно к выходу блока умножения 40 и выходу блока умножения 42.

Входы блока умножения 44 в составе второго столбца соединены соответственно с выходами блоков умножения 40 и 42. Входы блоков умножения 45, 46, 47, 48, 49, 50 в составе второго столбца подключены соответственно к 32 и 34, к 33 и 35, к 37 и 39, к 32 и 38, к 33 и 39, к 35 и 37 сигнальным входам формирователя 16.

Входы блоков умножения 51, 52, 53, 54, 55, 56 в составе третьего столбца подключены соответственно к выходу блоков умножения 40 и 41, к выходу блоков умножения 40 и 43, к выходу блоков умножения 45 и 46, к выходу блоков умножения 45 и 47, к выходу блоков умножения 48 и 49, к выходу блоков умножения 48 и 50.

Выходы блоков умножения 44, 51, 52, 53, 54, 55, 56 являются соответственно выходами 57, 58, 59, 60, 61, 62, 63 формирователя 16 анализируемой последовательности.

В общем случае формирователь 16 анализируемой последовательности содержит блоки умножения, которые расположены в n-k столбцах. Первый столбец содержит 2n-k-1 блоков умножения, столбец с номером i, 2≤i<n-k) содержит 2n-k+1-2n-k-i+2-1 блоков умножения, (n-k)-й столбец содержит n-1 блоков умножения.

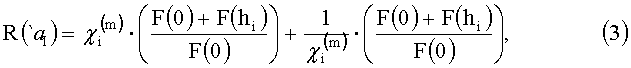

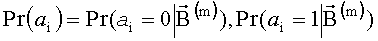

Опишем процедуру итеративного декодирования, которая реализуется в предлагаемом устройстве при передаче последовательности кодовых символов a i блокового турбокода (i=1, 2, …, N).

Начало работы начинается с этапа инициализации - формируется входной обрабатываемый блок отсчетов yi (i=1, 2, …, N), соответствующий блоковому турбокоду.

После инициализации реализуется заданное число итераций итеративного декодирования, обрабатывая блок λi=ехр(yi). При выполнении четных итераций декодируются составляющие коды C1 (горизонтальные коды), и вычисляются мягкие решения для составляющих кодов C2 (вертикальные коды). При выполнении нечетных итераций декодируются составляющие коды C2 (вертикальные коды), и вычисляются мягкие решения для составляющих кодов C1 (горизонтальные коды).

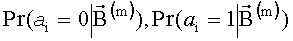

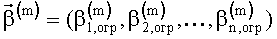

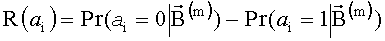

Вычисление мягких решений

Здесь

Мягкие решения

На первой итерации полагают

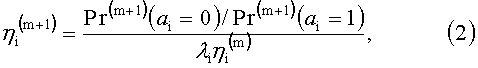

На последующей (m+2)-й итерации вычисляются новые мягкие решения

При выполнении задаваемого числа t итераций принимаются решения: если Pr(t)(a i=0)>Pr(t)(a i=1), то a i=0, иначе a i=1.

Устройство итеративного декодирования блоковых турбокодов, реализующее приведенную процедуру, работает следующим образом.

Работа устройства начинается после поступления дискретной реализации

В первом ограничителе 6 осуществляется нелинейное преобразование значений yi при помощи симметричного ограничителя по уровню ±П1 с зоной линейности с целью уменьшения динамического диапазона входных величин и увеличения помехоустойчивости устройства итеративного декодирования блоковых турбокодов - формируется последовательность yi, огр. Значение порога П1 хранится в блоке ограничения 6.

В блоке постоянной памяти 7 вычисляются табличным способом значения λi=exp(yi, огр) для значений yi, огр.

В блоке умножения 8 осуществляется вычисление величин

Во втором ограничителе 9 осуществляется нелинейное преобразование значений

Последовательность отсчетов с выхода второго ограничителя 9

В SISO декодере 4 вычисляются мягкие решения

В блоке принятия решений 5 вычисляются жесткие решения: если

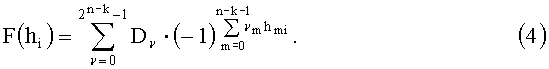

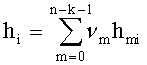

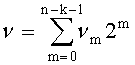

Опишем работу SISO декодера 4 при декодировании составляющего блокового кода с параметрами (n, k). В SISO декодере 4 вычисляются мягкие решения

где

Здесь=

При вычислении значений F(hi) (4) применяется алгоритм быстрого преобразования в базисе Уолша с базовыми операциями "сложение-вычитание". При вычислении множества Dν (5) применяется модифицированный алгоритм быстрого преобразования в базисе Уолша с базовой операцией "умножение".

Работа SISO декодера начинается после поступления реализации

Формирователь анализируемой последовательности 16 вычисляет величины Dν, ν=0, 1, …, 2n-k-1 (5), используя величины

В формирователе 16 реализован модифицированный алгоритм быстрого преобразования в базисе Уолша с базовой операцией «умножение», схемы которой приведена на фиг.6. На входы 32-39 поступают входные величины. После выполнения базовых операций с операцией «умножение» блоками умножения 40-56 на выходы 57-63 формирователя 16 поступают вычисленные значения.

Формирователь сигналов коэффициентов функции Уолша 15 осуществляет вычисление множества F(hi) (4) с использованием алгоритма быстрого спектрального преобразования в базисе Уолша с базовыми операциями "сложение-вычитание", используя анализируемую последовательность Dν, ν=0, 1, …, 2n-k-1, поступающую из формирователя анализируемой последовательности 16.

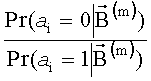

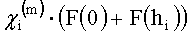

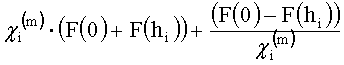

Вычисление мягких решений

После вычисления n величин мягких решений, символьных вероятностей и их отношений счетчик 13 переводится в нулевое состояние, и ключ 12 закрывается сигналом "упр.вход 29". Вычисление этих величин осуществляется в соответствии с соотношениями (3)-(5), используя:

- первый сумматор 17 и первый блок вычитания 18, в которых вычисляется сумма F(0)+F(hi) и разность F(0)-F(hi), значение F(0) поступает с первого выхода формирователя сигналов коэффициентов функции Уолша 15, а значения F(hш) поступают со второго выхода формирователя сигналов коэффициентов функции Уолша 15;

- блок умножения на два 19, в котором вычисляются величины 2·F(0);

- блок умножения 20, в котором вычисляются величины

- первый блок деления 21, в котором вычисляются величины

- второй сумматор 22, в котором вычисляются значения

- третий сумматор 23, в котором вычисляется апостериорная вероятность

- второй блок вычитания 24, в котором вычисляется апостериорная вероятность

- второй блок деления 25, в котором вычисляются отношения вероятностей

- третий блок деления 26, в котором вычисляются мягкие решения

- ограничитель 27, в котором происходит ограничение вычисленных мягких решений

Путем компьютерного моделирования показано, что предлагаемые устройство и декодер обеспечивают энергетический выигрыш до 2 дБ (что эквивалентно повышению помехоустойчивости) по отношению к прототипу, использующему алгоритм Чейза, для канала передачи информации с релеевскими замираниями символов и аддитивным белым гауссовским шумом.

Таким образом, устройство и декодер решает задачу повышения помехоустойчивости блоковых турбокодов путем замены подоптимального алгоритма Чейза при вычислении мягких решений оптимальным алгоритмом Хартмана-Рудольфа в SISO декодере.

Источники информации

1. Труды по теории информации. Институт инженеров электротехники и электроники. IEEE Transactions on Information Theory. 1996. V.IT-42. N2. P.429-448.

2. Патент США 7185259, МПК H03M 13/00, опубл. 27.02.2007.

3. Труды по теории информации. Институт инженеров электротехники и электроники. IEEE Transactions on Information Theory, 1972, Vol.IT-18, pp.170-182.

4. Патент на полезную модель №79361, H03M 13/29 от 01.02.2007 (прототип).

5. Авторское свидетельство 1372344, кл. G08C 19/18 (прототип), опубл. 07.02.88.

6. Труды по теории информации. Институт инженеров электротехники и электроники. IEEE Transactions on Information Theory. 1976. V.IT-22. N5. P.514-517.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПРИЕМА ДИСКРЕТНЫХ СИГНАЛОВ | 2012 |

|

RU2480839C1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ ТУРБОКОДОВ | 2007 |

|

RU2369961C2 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ ТУРБОКОДОВ | 2009 |

|

RU2393633C1 |

| СПОСОБ ДЕКОДИРОВАНИЯ ТУРБОКОДА (ВАРИАНТЫ) | 2006 |

|

RU2340090C2 |

| Устройство для мажоритарного декодирования | 1987 |

|

SU1517137A1 |

| Анализатор спектра случайныхпРОцЕССОВ | 1979 |

|

SU838600A1 |

| ЦИФРОВОЙ МОДЕМ ИНФОРМАЦИОННОЙ РАДИОЛИНИИ ЦМ ИРЛ | 2013 |

|

RU2583715C2 |

| УСТРОЙСТВО И СПОСОБ КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ БЛОКОВЫХ КОДОВ НИЗКОЙ ПЛОТНОСТИ С КОНТРОЛЕМ НА ЧЕТНОСТЬ В СИСТЕМЕ МОБИЛЬНОЙ СВЯЗИ | 2004 |

|

RU2316111C2 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

| КОМПОНЕНТНЫЙ ДЕКОДЕР И СПОСОБ ДЕКОДИРОВАНИЯ В СИСТЕМЕ МОБИЛЬНОЙ СВЯЗИ | 2000 |

|

RU2247471C2 |

Изобретение относится к устройству декодирования блоковых турбокодов и SISO декодеру и может быть использовано в цифровых системах связи. Технический результат заключается в повышении помехоустойчивости блоковых турбокодов. Устройство декодирования блоковых турбокодов содержит первый блок оперативной памяти 1, второй блок оперативной памяти 2, третий блок оперативной памяти 3, SISO декодер 4, блок принятия решений 5, первый ограничитель 6, блок постоянной памяти 7, блок умножения 8, второй ограничитель 9. SISO декодер содержит блок оперативной памяти 10, тактовый генератор 11, ключ 12, счетчик 13, блок постоянной памяти 14, формирователь сигналов коэффициентов функции Уолша 15, формирователь анализируемой последовательности 16, первый сумматор 17, первый блок вычитания 18, блок умножения на два 19, блок умножения 20, первый блок деления 21, второй сумматор 22, третий сумматор 23, второй блок вычитания 24, второй блок деления 25, третий блок деления 26, ограничитель 27. Технической задачей, решаемой предлагаемыми устройством и SISO декодером, является повышение помехоустойчивости блоковых турбокодов путем вычисления в SISO декодере мягких решений с использованием оптимального алгоритма Рудольфа-Хартмана. 2 н.и 1 з.п. ф-лы, 6 ил.

1. Устройство итеративного декодирования блоковых турбокодов, содержащее первый, второй и третий блоки оперативной памяти, SISO декодер, блок принятия решений, вход которого соединен с первым выходом SISO декодера, а выход подключен к входу третьего блока оперативной памяти, выход которого является выходом устройства, а входом устройства является вход первого блока оперативной памяти, отличающееся тем, что в него введены блок умножения, первый и второй ограничители, блок постоянной памяти, при этом выход первого блока оперативной памяти подключен к входу первого ограничителя, выход которого соединен с входом блока постоянной памяти, выход которого подключен к первому входу блока умножения, второй вход которого соединен с выходом второго блока оперативной памяти, а выход подключен к входу второго ограничителя, выход которого соединен с входом SISO декодера, второй выход которого подключен к входу второго блока оперативной памяти.

2. Устройство по п.1, отличающееся тем, что SISO декодер содержит блок оперативной памяти, тактовый генератор, ключ, счетчик, блок постоянной памяти, формирователь сигналов коэффициентов функции Уолша, формирователь анализируемой последовательности, первый сумматор, первый блок вычитания, блок умножения на два, блок умножения, первый блок деления, второй сумматор, третий сумматор, второй блок вычитания, второй блок деления, третий блок деления, ограничитель, при этом вход блока оперативной памяти является входом SISO декодера, последовательно соединенные соответственно тактовый генератор ключ и счетчик, выход счетчика подключен к адресному входу формирователя сигналов коэффициентов функции Уолша, выход счетчика соединен с адресными входами блока оперативной памяти, первый выход которого соединен с входом блока постоянной памяти, первый выход которого подключен к входу формирователя анализируемой последовательности, выход которого соединен с сигнальным входом формирователя сигналов коэффициентов функции Уолша, первый выход формирователя сигналов коэффициентов функции Уолша соединен с первым входом первого сумматора и с первым входом первого блока вычитания, а его второй выход подключен к второму входу первого сумматора, к второму входу первого блока вычитания и к входу блока умножения на два, выход первого блока вычитания соединен с первым входом первого блока деления, выход первого сумматора подключен к первому входу блока умножения, второй вход которого и второй вход первого блока деления соединены с вторым выходом блока постоянной памяти, выход первого блока деления подключен к первому входу второго сумматора, второй вход которого соединен с выходом блока умножения, выход второго сумматора подключен к первому входу второго блока вычитания и к первому входу третьего сумматора, второй вход которого и второй вход второго блока вычитания соединены с выходом блока умножения на два, выход второго блока вычитания соединен с первым входом второго блока деления, второй вход которого подключен к выходу третьего сумматора, первый выход второго блока деления является первым выходом SISO декодера, а его второй выход соединен с первым входом третьего блока деления, второй вход которого подключен к второму выходу блока оперативной памяти, выход третьего блока деления соединен с входом ограничителя, выход которого является вторым выходом SISO декодера, второй вход ключа является управляющим входом SISO декодера.

3. SISO декодер для устройства итеративного декодирования блоковых турбокодов, содержащий блок оперативной памяти, вход которого является входом SISO декодера, последовательно соединенные соответственно тактовый генератор, ключ и счетчик, блок постоянной памяти, формирователь сигналов коэффициентов функции Уолша, адресный вход которого подключен к выходу счетчика, отличающийся тем, что в него введены формирователь анализируемой последовательности, первый, второй и третий сумматоры, первый и второй блоки вычитания, блок умножения на два, блок умножения, первый, второй и третий блоки деления, ограничитель, при этом выход счетчика соединен с адресными входами блока оперативной памяти, первый выход которого соединен с входом блока постоянной памяти, первый выход которого подключен к входу формирователя анализируемой последовательности, выход которого соединен с сигнальным входом формирователя сигналов коэффициентов функции Уолша, первый выход формирователя сигналов коэффициентов функции Уолша соединен с первым входом первого сумматора и с первым входом первого блока вычитания, а его второй выход подключен к второму входу первого сумматора, к второму входу первого блока вычитания и к входу блока умножения на два, выход первого блока вычитания соединен с первым входом первого блока деления, выход первого сумматора подключен к первому входу блока умножения, второй вход которого и второй вход первого блока деления соединены с вторым выходом блока постоянной памяти, выход первого блока деления подключен к первому входу второго сумматора, второй вход которого соединен с выходом блока умножения, выход второго сумматора подключен к первому входу второго блока вычитания и к первому входу третьего сумматора, второй вход которого и второй вход второго блока вычитания соединены с выходом блока умножения на два, выход второго блока вычитания соединен с первым входом второго блока деления, второй вход которого подключен к выходу третьего сумматора, первый выход второго блока деления является первым выходом SISO декодера, а его второй выход соединен с первым входом третьего блока деления, второй вход которого подключен к второму выходу блока оперативной памяти, выход третьего блока деления соединен с входом ограничителя, выход которого является вторым выходом SISO декодера, второй вход ключа является управляющим входом SISO декодера.

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| Устройство для декодирования кодов Рида-Соломона | 1985 |

|

SU1309317A1 |

| Устройство для кодирования | 1985 |

|

SU1275782A1 |

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

| Способ приготовления мыла | 1923 |

|

SU2004A1 |

Авторы

Даты

2014-01-20—Публикация

2012-04-11—Подача