Предлагаемое устройство относится к области радиотехники и может найти широкое применение при построении систем радиосвязи.

Известно устройство декодирования турбокодов, описанное в [1], в котором для обнаружения ошибок совместно с турбокодами используются блоковые коды.

Известно также устройство декодирования турбокодов, описанное в [2], в котором сформированные пакеты кодируются циклическим кодом (CRC кодом), затем кодируются турбокодом и передаются получателю через канал радиосвязи.

Недостатком данных устройств декодирования является то, что блоковые и циклические коды, используемые совместно с турбокодами, вносят избыточность, чем снижают пропускную способность канала радиосвязи.

Наиболее близким по технической сущности к предлагаемому изобретению является устройство, представленное на рис.12 в [3].

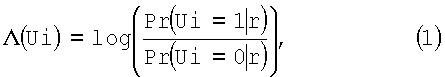

Функциональная схема устройства-прототипа приведена на фиг.1, где введены следующие обозначения:

1 - турбодекодер;

1.1 - первый декодер;

1.2 - второй декодер;

1.3 - первый деперемежитель;

1.4 - второй деперемежитель;

1.5 - перемежитель;

1.6 - формирователь жестких решений.

Устройство-прототип представляет собой турбодекодер 1, содержащий последовательно соединенные первый декодер 1.1, перемежитель 1.5, второй декодер 1.2, второй деперемежитель 1.4 и формирователь жестких решений 1.6, выход которого является выходом устройства. Второй выход второго декодера 1.2 через первый деперемежитель 1.3 соединен со вторым входом первого декодера 1.1, первый вход которого, являющийся входом устройства, соединен со вторым входом второго декодера 1.2.

Устройство-прототип работает следующим образом.

Вначале на первый декодер 1.1 поступает кодированный пакет данных (от демодулятора), содержащий информационные и проверочные символы.

Первый декодер 1.1, используя полученные искаженные в канале информационные и проверочные символы, выдает мягкое решение для информационных символов пакета данных (см. стр.3-15 в [3]).

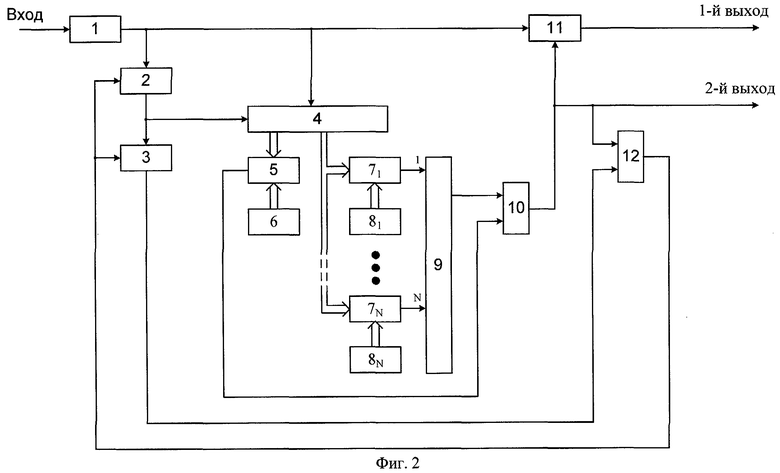

Мягкое решение представляет собой оценку логарифмического отношения правдоподобия (Log likehood ratio) (см. стр.201-230 в [6]):

где Λ(Ui) - логарифмическое отношение правдоподобия;

Ui - значение передаваемого символа исходного пакета;

r - принятая последовательность.

Полученное решение поступает на перемежитель 1.5, и после перемежения подается в качестве априорной информации на первый вход второго декодера 1.2.

Второй декодер 1.2, используя полученную априорную информацию, декодирует принятый пакет данных, по результатам декодирования выдает улучшенное мягкое решение для информационных символов, которое затем поступает на первый деперемежитель 1.3 и на второй деперемежитель 1.4, с выхода которого подается на формирователь жестких решений 1.6.

С выхода первого деперемежителя 1.3 мягкие решения поступают на второй вход первого декодера 1.1, замыкая тем самым итеративную обратную связь.

Подобную итерацию можно повторять многократно с целью улучшения результатов декодирования на каждой итерации.

Выходные биты Ui согласно формуле (1) формируются по правилу: если Λ(Ui)>0, то Ui=1, в противном случае Ui=0.

Компоненты элементарных первого 1.1 и второго 1.2 декодеров обычно работают по алгоритму максимальной апостериорной вероятности MAP (maximum aposteriory probability) или алгоритму Витерби с мягким выходом SOVA (Soft Output Viterbi Algorithm). Также могут использоваться любые декодеры сверточного кода типа SISO (soft input - soft output), т.е. мягкий вход - мягкий выход (см. стр.201-230 в [6]).

Формирователь жестких решений 1.6 осуществляет преобразование декодированного пакета, представленного в виде мягких решений, к виду жестких решений. Таким образом, с выхода блока 1.6 декодированный пакет данных подается на выход устройства.

Однако устройство-прототип имеет существенный недостаток, заключающийся в том, что в нем отсутствует контроль правильности принятия пакета данных. Это приводит к тому, что итеративное декодирование будет происходить сколь угодно долго, при этом отсутствует возможность контроля правильности принятия сообщения и возможность распознавания своих абонентов.

В основу настоящего изобретения положена задача создать устройство декодирования турбокодов с контролем правильности принятия пакета от одного из N возможных отправителей. Достигаемый при этом технический результат - повышение пропускной способности канала связи с N абонентами.

Для решения поставленной задачи в устройство декодирования турбокодов, содержащее турбодекодер, вход которого является входом устройства, согласно изобретению введены буфер логической обработки пакета, буфер хранения пакета, компаратор адреса получателя, запоминающее устройство адреса получателя, N компараторов адреса отправителя, N запоминающих устройств адреса отправителя, первый и второй логические элементы ИЛИ, логический элемент И, счетчик символов и счетчик итераций; при этом выход турбодекодера соединен с информационными входами буфера логической обработки пакета, буфера хранения пакета и со счетным входом счетчика символов, выход которого соединен со счетным входом счетчика итераций и с управляющим входом буфера логической обработки пакета, первая группа выходов которого шиной соединена со второй группой входов компаратора адреса получателя, первая группа входов которого шиной соединена с группой выходов запоминающего устройства адреса получателя; вторая группа выходов буфера логической обработки пакета шиной соединена со вторыми группами входов каждого из N компараторов адреса отправителя, первые группы входов которых шинами соединены соответственно с группами выходов соответствующих N запоминающих устройств адреса отправителя; выход компаратора адреса получателя соединен с первым входом логического элемента И, выход которого является вторым выходом устройства для выдачи сигнала «пакет принят», соединенным со вторым входом второго логического элемента ИЛИ и с управляющим входом буфера хранения пакета, выход которого является первым выходом устройства для выдачи пакета данных получателям, выход счетчика итераций соединен с первым входом второго логического элемента ИЛИ, выход которого соединен с обнуляющими входами счетчика символов и счетчика итераций; выход каждого из N компараторов адреса отправителя соединен соответственно с соответствующим входом первого логического элемента ИЛИ, выход которого соединен со вторым входом логического элемента И.

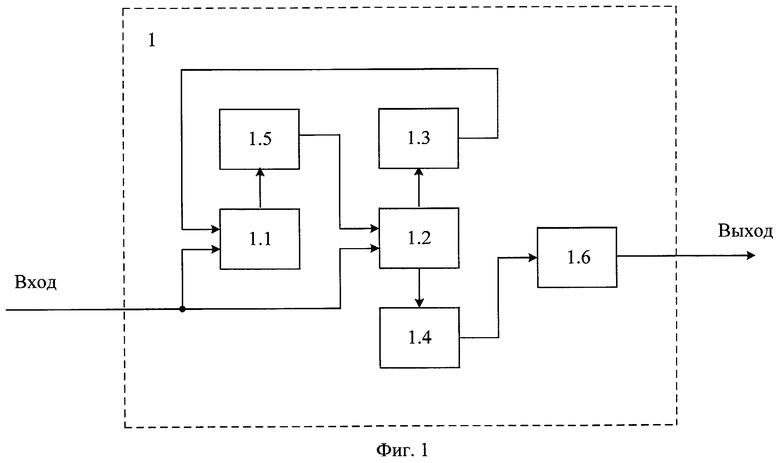

Функциональная схема предлагаемого устройства приведена на фиг.2, где введены следующие обозначения:

1 - турбодекодер;

2 - счетчик символов;

3 - счетчик итераций;

4 - буфер логической обработки пакета;

5 - компаратор адреса получателя;

6 - запоминающее устройство адреса получателя;

71-7N - N компараторов адреса отправителя;

81-8N - N запоминающих устройств адреса отправителя;

9 - первый логический элемент ИЛИ;

10 - логический элемент И;

11 - буфер хранения пакета;

12 - второй логический элемент ИЛИ.

Предлагаемое устройство содержит турбодекодер 1, вход которого является входом устройства, а выход турбодекодера 1 соединен со счетным входом счетчика символов 2, с информационным входом буфера логической обработки пакета 4 и информационным входом буфера хранения пакета 11, выход которого является первым выходом устройства; выход счетчика символов 2 соединен с управляющим входом буфера логической обработки пакета 4 и счетным входом счетчика итераций 3, выход которого соединен с первым входом второго логического элемента ИЛИ 12; группа выходов запоминающего устройства адреса получателя 6 шиной соединена с первой группой входов компаратора адреса получателя 5, вторая группа входов которого шиной соединена с первой группой выходов буфера логической обработки пакета 4, а выход компаратора адреса получателя 5 соединен с первым входом логического элемента И 10, выход которого является вторым выходом устройства, соединенным с управляющим входом буфера хранения пакета 11 и со вторым входом второго логического элемента ИЛИ 12, выход которого соединен с обнуляющими входами счетчика итераций 3 и счетчика символов 2; группы выходов N запоминающих устройств адреса отправителя 81-8N шинами соединены соответственно с первыми группами входов соответствующих компараторов адреса отправителя 71-7N, вторые группы входов которых шиной соединены между собой и со второй группой выходов буфера логической обработки пакета 4, а выход каждого из N компараторов адреса отправителя 71-7N соединен соответственно с одним из N входов первого логического элемента ИЛИ 9, выход которого соединен со вторым входом логического элемента И.

Предлагаемое устройство работает следующим образом.

В исходном состоянии все счетчики обнулены. Со входа устройства закодированный пакет данных поступает на турбодекодер 1, где выполняется итеративное декодирование. После каждой итерации декодирования полученный пакет данных подается одновременно на информационные входы буфера логической обработки пакета 4, буфера хранения пакета 11 и на счетный вход счетчика символов 2.

Счетчик символов 2 рассчитан на число двоичных символов М, которое равно числу символов в пакете на выходе турбодекодера 1. После того, как в счетчик символов 2 проступит М символов, на выходе этого счетчика образуется кратковременный импульс в виде логической единицы. Этот импульс поступает на счетный вход счетчика итераций 3 и на управляющий вход буфера логической обработки пакета 4.

В результате этого счетчик итераций 3 перейдет в другое состояние, а на первой и второй группах выходов буфера логической обработки пакета 4 будут выдаваться сигналы, соответствующие адресу получателя и адресу отправителя.

Сигналы с первой группы выходов буфера логической обработки пакета 4 поступают соответственно на вторую группу входов компаратора адреса получателя 5, на первую группу входов которого поступают соответственно сигналы с группы выходов запоминающего устройства адреса получателя 6. Если адрес принятого пакета совпадет с адресом, записанным заранее в запоминающем устройстве адреса получателя 6, то с выхода компаратора адреса получателя 5 на первый вход логического элемента И 10 поступит сигнал логической единицы.

Одновременно, со второй группы выходов буфера логической обработки пакета 4 сигналы поступают на вторые группы входов каждого из N компараторов адреса отправителя 71-7N, на первые группы входов этих компараторов поступают сигналы с соответствующих запоминающих устройств адреса отправителя 81-8N. В этих N запоминающих устройствах записано соответственно N адресов потенциальных отправителей. Если адрес отправителя совпадет с адресом, записанным ранее в одном из N запоминающих устройств адреса отправителя 81-8N, то с выхода соответствующего компаратора адреса отправителя 71-7N через первый логический элемент ИЛИ 9 на второй вход логического элемента И 10 поступит сигнал логической единицы.

Пакет считается принятым правильно, если адрес получателя и адрес отправителя в декодированном пакете совпали соответственно с адресом получателя и одним из N потенциальных адресов отправителей, записанных в соответствующих запоминающих устройствах. В таком случае с выходов соответствующих компараторов на соответствующие входы логического элемента И 10 поступят две логические единицы, и с выхода логического элемента И 10 сигнал логической единицы поступит на управляющий вход буфера хранения пакета 11, в результате чего произойдет выдача декодированного пакета данных получателю с первого выхода устройства. В то же время произойдет выдача сигнала логической единицы на второй выход устройства, что означает «пакет принят». И, кроме того, тот же сигнал логической единицы через второй логический элемент ИЛИ 12 поступит на обнуляющие входы счетчика символов 2 и счетчика итераций 3, в результате чего произойдет обнуление этих счетчиков. Таким образом, устройство готово к приему нового пакета.

Пакет считается не принятым, если в процессе декодирования пакета не оказалось ситуации, когда в декодированном пакете адрес получателя и адрес отправителя совпали с записанными в соответствующих устройствах адресом получателя и одним из адресов отправителя. Это могло произойти по причине прихода пакета от чужого абонента, или по причине искажения пакета от одного из N своих абонентов. То есть на вход логического элемента И 10 не поступили две логические единицы. В этом случае, счетчик числа итераций 3, досчитав до максимального числа итераций, заложенного в этом счетчике, выдает импульс логической единицы, который поступает через второй логический элемент ИЛИ 12 на обнуляющие входы счетчика символов 2 и счетчика итераций 3, в результате чего произойдет обнуление этих счетчиков.

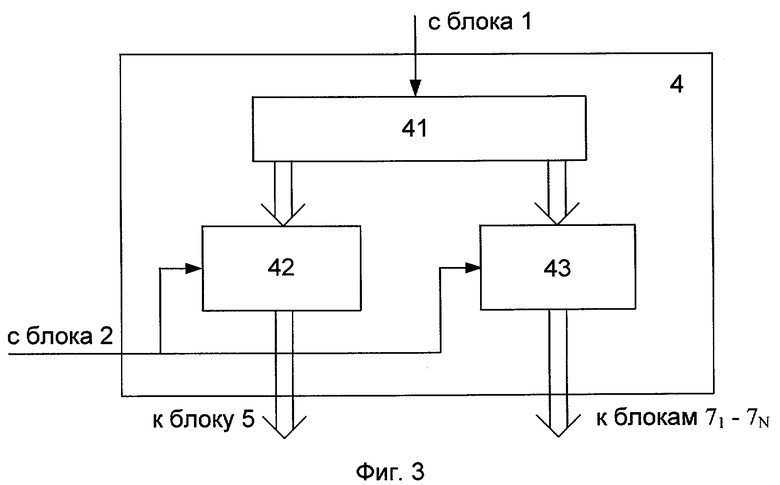

Вариант реализации буфера логической обработки пакета 4 приведен на фиг.3, где введены следующие обозначения:

41 - регистр сдвига;

42 - первый блок ключей;

43 - второй блок ключей.

Буфер логической обработки пакета 4 содержит М-разрядный последовательный регистр сдвига 41, первая и вторая группы выходов которого соединены соответственно с группами входов соответствующих первого 42 и второго 43 блоков ключей, группы выходов которых являются соответственно первой и второй группами выходов буфера логической обработки пакета 4. Вход регистра сдвига 41 является информационным входом буфера логической обработки пакета 4, управляющий вход которого соединен с одиночными управляющими входами первого 42 и второго 43 блоков ключей.

В декодированном пакете, содержащем М символов в виде последовательности нулей и единичек, служебные поля (адреса) отправителя и получателя находятся на строго определенных местах. После того, как декодированный пакет запишется в М-разрядный последовательный регистр сдвига 41, на соответствующих выходах регистра сдвига будут находиться адреса отправителя и получателя.

В это время с выхода счетчика символов 2 на управляющий вход буфера логической обработки пакета 4 поступит логическая единица в виде короткого импульса, которая поступает на управляющие входы первого 42 и второго 43 блоков ключей, в результате чего ключи откроются, и на входы компаратора адреса получателя 5 и компараторов адреса отправителя 71-7N поступят те значения нулей и единиц, которые находятся в тех полях, где должны находиться адрес получателя и адрес отправителя.

Буфер хранения пакета 11 может быть реализован на микропроцессоре со встроенным оперативным запоминающим устройством (ОЗУ).

Алгоритм работы этого микропроцессора может быть следующий. Сигнал с выхода турбодекодера 1 поступает на информационный вход буфера хранения пакета 11, где микропроцессор сбрасывает его в ОЗУ. После того, как на управляющий вход буфера хранения пакета 11 поступает сигнал с выхода логического элемента И 10, микропроцессор извлекает последовательность нулей и единиц из ОЗУ и передает его на первый выход устройства. В качестве микропроцессора могут быть использованы микросхемы серии C8051F040.

Реализация других блоков не вызывает затруднений, т.к. они широко описаны в технической литературе [4], [5], [6], [7].

Таким образом, предлагаемое устройство осуществляет адаптивное итеративное турбодекодирование и распознавание пакета данных только N своих возможных абонентов, а также контроль правильности принятия пакета. В случае правильного принятия пакета осуществляется прекращение итеративного декодирования, передача пакета получателю и формирование сигнала о том, что пакет принят. В случае, если пакет пришел от другого абонента, или пакет пришел от своего абонента, но с ошибками и не может быть восстановлен даже путем многократного декодирования, то осуществляется отбраковка пакета.

Следовательно, за счет применения в предлагаемом устройстве адаптивного числа итераций турбодекодера осуществляется повышение пропускной способности канала связи с N абонентами, так как сокращается время декодирования и обработки каждого пакета.

Источники информации

1. Патент USA №1003372, H04L 7/02, 1981 г.

2. Патент USA №5983984 H03M 13/00. "Turbo-coding with staged data transmission and processing" Турбокодирование с каскадной передачей и обработкой данных, 1999 г.

3. Панько С.П., Югай В.В. Турбокодирование // Успехи современной радиоэлектроники. - М.: Радиотехника, 2004. - №2. - С.3-15.

4. А.П.Антонов Язык описания цифровых устройств ALteraHDL. Практический курс. 2-е изд., стереотип. М.: ИП Радиософт, 2002. - 224 с.: ил.

5. Аналоговая и цифровая электроника (Полный курс): Учебник для вузов / Ю.Ф.Опадчий, О.П.Глудкин, А.И.Гуров; Под ред. О.П.Глудкина. - М.: Горячая Линия - Телеком, 2000. 768 с.: ил. с.710-719.

6. Р.Морелос-Сарагоса / Искусство помехоустойчивого кодирования. Методы, алгоритмы, применение. М.: Техносфера, 2005. - 320 с., с.201-230.

7. У.Титце К.Шенк / Полупроводниковая схемотехника. Справочное руководство. Пер. с нем. - М.: 1982. 512 с., ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ ТУРБОКОДОВ | 2007 |

|

RU2369961C2 |

| УСТРОЙСТВО И СПОСОБ ГЕНЕРИРОВАНИЯ И ДЕКОДИРОВАНИЯ КОДОВ В СИСТЕМЕ СВЯЗИ | 2002 |

|

RU2236756C2 |

| УСТРОЙСТВО И СПОСОБ ТУРБОКОДИРОВАНИЯ/ДЕКОДИРОВАНИЯ ДЛЯ ОБРАБОТКИ ДАННЫХ КАДРА В СООТВЕТСТВИИ С КАЧЕСТВОМ ОБСЛУЖИВАНИЯ | 1999 |

|

RU2210185C2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ОЦЕНКИ КАЧЕСТВА УСЛУГ НА КАНАЛАХ ПЕРЕДАЧИ В ЦИФРОВОЙ СИСТЕМЕ ПЕРЕДАЧИ | 1998 |

|

RU2202153C2 |

| МНОГОКАНАЛЬНОЕ ПРИЕМНО-ДЕМОДУЛИРУЮЩЕЕ УСТРОЙСТВО ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ СИСТЕМ СВЯЗИ | 2005 |

|

RU2305375C2 |

| АРХИТЕКТУРА ТУРБОДЕКОДЕРА ДЛЯ ИСПОЛЬЗОВАНИЯ В ПРОГРАММНО-ОПРЕДЕЛЯЕМЫХ РАДИОСИСТЕМАХ | 2006 |

|

RU2383992C2 |

| Способ передачи данных в системе цифровой радиосвязи на основе кодов с низкой плотностью проверок на четность и способ перемежения кодовых символов | 2018 |

|

RU2700398C1 |

| ТУРБОДЕКОДЕР, ИСПОЛЬЗУЮЩИЙ ЛИНЕЙНЫЕ КОНГРУЭНТНЫЕ ПОСЛЕДОВАТЕЛЬНОСТИ | 1999 |

|

RU2313177C2 |

| ТУРБОДЕКОДЕР, ИСПОЛЬЗУЮЩИЙ ЛИНЕЙНЫЕ КОНГРУЭНТНЫЕ ПОСЛЕДОВАТЕЛЬНОСТИ | 2007 |

|

RU2376702C2 |

| СПОСОБ ПЕРЕДАЧИ ИНФОРМАЦИИ | 2007 |

|

RU2343629C1 |

Изобретение относится к области радиотехники и может найти применение при построении систем радиосвязи. Техническим результатом является повышение пропускной способности канала связи с N абонентами. Указанный технический результат достигается тем, что устройство содержит турбодекодер (1), счетчик символов (2), счетчик итераций (3), буфер логической обработки пакета (4), компаратор адреса получателя (5), запоминающее устройство адреса получателя (6), N компараторов адреса отправителя (71-7N), N запоминающих устройств адреса отправителя (81-8N), первый (9) и второй (12) логические элементы ИЛИ, буфер хранения пакета (11) и логический элемент И (10). Буфер логической обработки пакета (4) позволяет выделять из декодированного пакета адреса отправителя и адреса получателя, а буфер хранения пакета (11) позволяет осуществлять запись, хранение и выдачу декодированного пакета получателям. 2 з.п. ф-лы, 3 ил.

1. Устройство декодирования турбокодов, содержащее турбодекодер, вход которого является входом устройства, отличающееся тем, что введены буфер логической обработки пакета, буфер хранения пакета, компаратор адреса получателя, запоминающее устройство адреса получателя, N компараторов адреса отправителя, N запоминающих устройств адреса отправителя, первый и второй логические элементы «ИЛИ», логический элемент «И», счетчик символов и счетчик итераций; при этом выход турбодекодера соединен с информационными входами буфера логической обработки пакета, буфера хранения пакета и со счетным входом счетчика символов, выход которого соединен со счетным входом счетчика итераций и с управляющим входом буфера логической обработки пакета, первая группа выходов которого шиной соединена со второй группой входов компаратора адреса получателя, первая группа входов которого шиной соединена с группой выходов запоминающего устройства адреса получателя; вторая группа выходов буфера логической обработки пакета шиной соединена со вторыми группами входов каждого из N компараторов адреса отправителя, первые группы входов которых шинами соединены соответственно с группами выходов соответствующих N запоминающих устройств адреса отправителя; выход компаратора адреса получателя соединен с первым входом логического элемента «И», выход которого является вторым выходом устройства для выдачи сигнала «пакет принят», соединенным со вторым входом второго логического элемента «ИЛИ» и с управляющим входом буфера хранения пакета, выход которого является первым выходом устройства для выдачи пакета данных получателям, выход счетчика итераций соединен с первым входом второго логического элемента «ИЛИ», выход которого соединен с обнуляющими входами счетчика символов и счетчика итераций; выход каждого из N компараторов адреса отправителя соединен соответственно с соответствующим входом первого логического элемента «ИЛИ», выход которого соединен со вторым входом логического элемента «И».

2. Устройство по п.1, отличающееся тем, что буфер логической обработки пакета выполнен с возможностью выделения из декодированного пакета адреса отправителя и адреса получателя.

3. Устройство по п.1, отличающееся тем, что буфер хранения пакета выполнен с возможностью записи, хранения и выдачи декодированного пакета получателям.

| US 5983384 А, 09.11.1999 | |||

| RU 2007119759 А, 10.12.2008 | |||

| УСТРОЙСТВО И СПОСОБ ГЕНЕРИРОВАНИЯ И ДЕКОДИРОВАНИЯ КОДОВ В СИСТЕМЕ СВЯЗИ | 2002 |

|

RU2236756C2 |

| WO 9724850 А1, 10.07.1997 | |||

| US 2009006928 А1, 01.01.2009. | |||

Авторы

Даты

2010-06-27—Публикация

2009-03-10—Подача