Изобретение относится к импульсной технике и может быть использовано в устройствах обработки информации, управления и измерения, в частности в устройствах приема униполярных старт-стоповых последовательных комбинаций импульсов для контроля отклонения длительности и количества импульсов от заданного значения, контроля местоположения импульсов в комбинации и сравнения с эталонными значениями.

Известен блок исполнительный (патент РФ №2406111, приоритет от 30.10.2009, «Блок исполнительный» авторов Фомченко В.Н., Ведерникова В.Л. и др., МПК 6: G06F 9/00, G06F 13/10, опубл. 10.12.2010, бюл. №34), содержащий схему начальной установки, выход которой соединен с первым входом программника, второй вход и первый выход которого соединены с выходом и входом схемы кварцевого генератора соответственно, схему согласования приемника, выход которой соединен с третьим входом программника, а вход - с выходом последовательного интерфейса, вход которого соединен с выходом схемы согласования передатчика, при этом вход/выход последовательного интерфейса является входом/выходом блока исполнительного, схему управления, первая группа выходов которой соединена с первой группой входов первой схемы совпадения, группа выходов которой является группой выходов блока исполнительного, отличающийся тем, что дополнительно введены схема контроля режима, группа входов которой является группой входов блока исполнительного, а выходы соединены с четвертым и пятым входами программника, второй выход которого соединен с входом схемы согласования передатчика, запоминающее устройство, вход и выход которого соединены с третьим выходом и шестым входом программника соответственно, группа выходов которого соединена с группой входов схемы управления, вторая группа выходов которой соединена со второй группой входов первой схемы совпадения, первый вход которой соединен с выходом схемы контроля питания.

Данное устройство является наиболее близким аналогом к заявляемому изобретению.

Недостатками данного устройства являются:

- отсутствие контроля состояния схемы совпадения;

- отсутствие возможности сохранения состояния группы выходов блока исполнительного при выключении питания;

- отсутствие возможности выборочной работы при одновременном подключении к последовательному интерфейсу нескольких блоков исполнительных;

- отсутствие функции контроля целостности коммуникаций.

Задача, на решение которой направлено заявляемое изобретение, заключается в создании блока исполнительного с расширенными функциональными возможностями.

Техническим результатом, на достижение которого направлено заявляемое изобретение, заключается в расширении функциональных возможностей за счет введения возможности контроля состояния схемы совпадения, возможности сохранения состояния группы выходов блока исполнительного при выключении питания, возможности выборочной работы с любым блоком исполнительным при одновременном подключении к последовательному интерфейсу нескольких блоков исполнительных, а также в возможности контроля целостности коммуникаций.

Данный технический результат достигается тем, что в блоке исполнительном, содержащем запоминающее устройство, схему начальной установки, выход которой соединен с первым входом программника, второй вход и первый выход которого соединены с выходом и входом схемы кварцевого генератора соответственно, третий вход программника соединен с выходом схемы согласования приемника, вход которой соединен с выходом последовательного интерфейса, вход/выход которого является входом/выходом блока исполнительного, а вход соединен с выходом схемы согласования передатчика, вход которого соединен со вторым выходом программника, первая группа выходов которого соединена с группой входов схемы управления, первая группа выходов которой соединена с группой входов первой схемы совпадения, группа выходов которой является первой группой выходов блока исполнительного, а вход соединен с выходом схемы контроля питания, новым является то, что дополнительно введены вторая схема совпадения и схема установки адреса, группа входов которой является группой входов блока исполнительного, а вход и группа выходов соединены соответственно с третьим выходом и первой группой входов программника, вторые группы выходов и входов которого соединены соответственно с группами входов и выходов запоминающего устройства, при этом вторая группа выходов схемы управления соединена с группой входов второй схемы совпадения, группа выходов которой является второй группой выходов блока исполнительного, а выход соединен с четвертым входом программника, пятый вход которого соединен с выходом первой схемы совпадения.

Введение второй схемы совпадения позволяет сохранять состояние группы выходов блока исполнительного при выключении питания за счет отсутствия связи со схемой контроля питания.

Введение дополнительных связей от схем совпадения к программнику позволяет контролировать состояние схем совпадения.

Введение схемы установки адреса дает возможность выборочной работы при одновременном подключении к последовательному интерфейсу нескольких блоков исполнительных.

Дополнительное применение схемы контроля целостности коммуникаций, первый вход и выход которой являются соответственно входом и выходом блока исполнительного, а второй вход соединен с четвертым выходом программника, позволяет осуществлять контроль целостности коммуникаций.

Указанная совокупность существенных признаков расширяет функциональные возможности блока исполнительного.

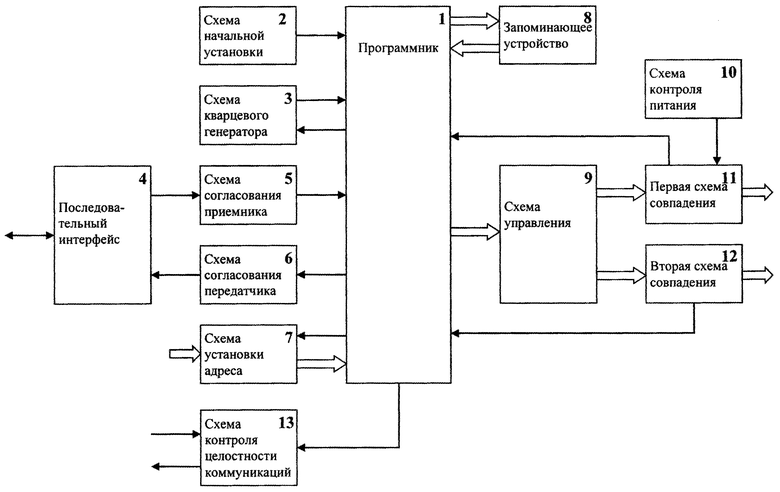

На чертеже представлен вариант функциональной схемы блока исполнительного.

Блок исполнительный содержит программник 1, схему 2 начальной установки, схему 3 кварцевого генератора, последовательный интерфейс 4, схему 5 согласования приемника, схему 6 согласования передатчика, схему 7 установки адреса, запоминающее устройство 8, схему 9 управления, схему 10 контроля питания, первую схему 11 совпадения, вторую схему 12 совпадения, схему 13 контроля целостности коммуникаций.

Выход схемы 2 начальной установки соединен с первым входом программника 1. Второй вход и первый выход программника 1 соединены с выходом и входом схемы 3 кварцевого генератора соответственно. Выход схемы 5 согласования приемника соединен с третьим входом программника 1, а вход - с выходом последовательного интерфейса 4. Вход/выход последовательного интерфейса 4 является входом/выходом блока исполнительного. Вход последовательного интерфейса 4 соединен с выходом схемы 6 согласования передатчика. Вход схемы 6 согласования передатчика соединен со вторым выходом программника 1. Первая группа выходов программника 1 соединена с группой входов схемы управления 9. Первая группа выходов схемы управления 9 соединена с группой входов первой схемы совпадения 11, группа выходов которой является первой группой выходов блока исполнительного. Вход первой схемы 11 совпадения соединен с выходом схемы 10 контроля питания, а выход - с пятым входом программника 1. Вторая группа выходов схемы управления 9 соединена с группой входов второй схемы 12 совпадения, группа выходов которой является второй группой выходов блока исполнительного, а выход соединен с четвертым входом программника 1. Группа выходов и вход схемы 7 установки адреса соединены соответственно с первой группой входов и третьим выходом программника 1. Группа входов схемы 7 установки адреса является группой входов блока исполнительного. Вторые группы выходов и входов программника 1 соединены соответственно с группами входов и выходов запоминающего устройства 8. Первый вход и выход схемы 13 контроля целостности коммуникаций являются соответственно входом и выходом блока исполнительного, а второй вход соединен с четвертым выходом программника 1.

Программник 1, содержащий микропроцессор, регистр, постоянное запоминающее устройство (ПЗУ), оперативное запоминающее устройство (ОЗУ), предназначен для приема униполярных старт-стоповых последовательных комбинаций импульсов (кодограмм), поступающих с последовательного интерфейса 4, их обработки в соответствии с внутренней программой, хранящейся в ПЗУ, обмена информацией с запоминающим устройством 8, формирования ответных кодограмм, а также формирования импульсов для управления схемами установки адреса, контроля целостности коммуникаций и формирования импульсов для управления первой 11 и второй 12 схемами совпадения.

Схема 2 начальной установки предназначена для формирования импульса сброса, необходимого для приведения в исходное состояние программника 1, при подаче напряжения питания на блок исполнительный.

Схема 3 кварцевого генератора предназначена для формирования импульсов тактовой частоты программника 1.

Схема 5 согласования приемника предназначена для преобразования уровня напряжения полученных от последовательного интерфейса 4 кодограмм в уровень напряжения, необходимый для работы программника 1.

Последовательный интерфейс 4 предназначен для подключения внешнего устройства управления (на фигуре не показано).

Схема 6 согласования передатчика предназначена для преобразования уровня напряжения кодограмм, сформированных программником 1, в уровень напряжения, необходимый для работы последовательного интерфейса 4.

Схема 7 установки адреса предназначена для задания адреса блока исполнительного посредством формирования импульсов, поступающих на первую группу входов программника 1 в соответствии с информацией, поступающей на группу входов блока исполнительного при поступлении импульса управления с программника 1.

Запоминающее устройство 8 предназначено для хранения значений эталонных последовательностей и номера последней использованной эталонной последовательности.

Схема 9 управления предназначена для преобразования уровня напряжения импульсов, сформированных программником 1, необходимого для управления схемами 11 и 12 совпадения.

Схема 10 контроля питания предназначена для контроля внутреннего напряжения питания и восстановления в исходное состояние первой схемы 11 совпадения при исчезновении внутреннего напряжения питания.

Первая схема 11 совпадения предназначена для управления состоянием первой группы выходов блока исполнительного в соответствии с импульсами, полученными от программника 1.

Вторая схема 12 совпадения предназначена для управления состоянием второй группы выходов блока исполнительного в соответствии с импульсами, полученными от программника 1.

Схема 13 контроля целостности коммуникаций предназначена для осуществления контроля целостности коммуникаций, посредством размыкания контактов реле, замыкающих вход и выход блока исполнительного на время импульса управления, поступающего с программника 1.

Программник 1 может быть выполнен на микропроцессоре, постоянном запоминающем устройстве и регистре. Схема 2 начальной установки может быть выполнена на микросхеме 5518АП1ТБМ и логическом инверторе. Схема 3 кварцевого резонатора может быть выполнена на кварцевом резонаторе и конденсаторах. Запоминающее устройство 8 может быть выполнено на микросхеме 1638РР1АУ. Схема 5 согласования приемника может быть выполнена на компараторе 1401СА1, транзисторах 2Т665 и микросхеме 249ЛП1А. Схема 6 согласования передатчика может быть выполнена на логических инверторах и оптопаре транзисторной 3ОТ110А(Б). Схема 7 установки адреса может быть выполнена на логическом инверторе, оптопарах транзисторных 3ОТ110А(Б), транзисторе 2Т664 и микросхемах 249ЛП1А. Схема 9 управления может быть выполнена на логических элементах, микросхеме 1554ИЕ10, оптопарах транзисторных 3ОТПОА(Б) и транзисторах 2Т664. Первая схема 11 совпадения может быть выполнена на поляризованном реле ТЭВ31 и реле РЭК81. Вторая схема 12 совпадения может быть выполнена на поляризованном реле ТЭВ31. Схема 10 контроля питания может быть выполнена на микросхеме 142ЕН8В и оптопаре транзисторной 3ОТПОА(Б). Последовательный интерфейс 4 представляет собой соединитель.

Блок исполнительный работает следующим образом.

Перед началом работы в запоминающее устройство 8 записываются эталонные последовательности.

При подаче напряжения питания на блок исполнительный на выходе схемы 2 начальной установки формируется импульс сброса, схема 3 кварцевого генератора формирует импульсы тактовой частоты программника 1, на выходах программника 1 устанавливается логическая «1». При этом со схемы 9 управления не поступают импульсы на первую 11 и вторую 12 схемы совпадения. После окончания импульса сброса программник 1 работает в соответствии с внутренней программой.

В соответствии с внутренней программой, программник 1 формирует импульс управления на схему 7 установки адреса. В соответствии с импульсами, принятыми от схемы 7 установки адреса, программник 1 определяет адрес блока исполнительного и сохраняет его во внутреннее оперативно-запоминающее устройство (ОЗУ).

От внешнего устройства управления (на фигуре не показано), подключенного к входу/выходу последовательного интерфейса 4, на блок исполнительный подаются кодограммы. С выхода последовательного интерфейса 4 кодограммы поступают через схему 5 согласования приемника на программник 1. Программник 1 после получения кодограммы выделяет из нее адрес, идентификатор, номер и последовательность. Выделенный адрес программник 1 сравнивает с адресом блока исполнительного, хранящимся в ОЗУ. В случае если адрес совпадает, программник 1 приступает к обработке принятой кодограммы и формированию ответной кодограммы.

В случае если принятый номер больше номера, хранимого в запоминающем устройстве 8, программник 1 считывает с запоминающего устройства 8 эталонную последовательность, соответствующую принятому номеру, и сравнивает с принятой последовательностью. В случае совпадения последовательностей программник 1 через схему 9 управления формирует импульсы, необходимые для управления первой схемой 11 совпадения либо второй схемой 12 совпадения, в зависимости от выделенного из управляющей кодограммы идентификатора. При получении импульсов управления первая схема 11 совпадения переводит выходы (в соответствии с идентификатором) первой группы выходов блока исполнительного в состояние, соответствующее логической «1». Вторая схема 12 совпадения работает аналогично, управляя второй группой выходов блока исполнительного. Программник 1 сохраняет принятый номер в запоминающем устройстве 8.

При получении кодограммы восстановления программник 1 выделяет из нее идентификатор и через схему 9 управления формирует импульсы, необходимые для управления первой схемой 11 совпадения, либо второй схемой 12 совпадения, в зависимости от выделенного из кодограммы восстановления идентификатора. Первая схема 11 совпадения при этом переводит выходы (в соответствии с идентификатором) первой группы выходов блока исполнительного в состояние, соответствующее логическому «0». Вторая схема 12 совпадения работает аналогично, управляя второй группой выходов блока исполнительного.

Ответная кодограмма формируется программником 1. Сформированная кодограмма через схему 6 согласования передатчика и последовательный интерфейс 4 поступает на вход/выход блока исполнительного.

При получении кодограммы запроса состояния программник 1 через четвертый и пятый входы определяет состояние второй и первой групп выходов блока исполнительного соответственно и формирует ответную кодограмму, содержащую информацию о состоянии групп выходов блока исполнительного.

В случае если при работе блока исполнительного происходит сбой напряжения питания, схема 10 контроля питания формирует импульс, необходимый для восстановления в исходное состояние первой схемы 11 совпадения.

При выключении питания состояние второй группы выходов блока исполнительного сохраняется вследствие отсутствия связи второй схемы 12 совпадения со схемой 10 контроля питания.

Для контроля целостности коммуникаций внешнее управляющее устройство передает в блок исполнительный соответствующую кодограмму. При обработке кодограммы программник 1 формирует импульс в схему 13 контроля коммуникаций. Схема 13 контроля целостности коммуникаций на время импульса размыкает контакты реле, замыкающие вход и выход блока исполнительного.

В случае если выделенный из принятой кодограммы адрес не совпадает с адресом в ОЗУ, программник 1 не приступает к обработке принятой кодограммы и формированию ответной кодограммы. Таким образом осуществляется возможность выборочной работы при одновременном подключении к последовательному интерфейсу нескольких блоков исполнительных.

Изготовлен макет, испытания которого подтвердили работоспособность блока исполнительного и достижение заявленного технического результата.

| название | год | авторы | номер документа |

|---|---|---|---|

| БЛОК ИСПОЛНИТЕЛЬНЫЙ | 2009 |

|

RU2406111C1 |

| УСТРОЙСТВО ОПЕРАТИВНОГО КОНТРОЛЯ | 2007 |

|

RU2337389C1 |

| МУЛЬТИПЛЕКСОР ПЕРЕДАЧИ ДАННЫХ | 2005 |

|

RU2295148C1 |

| МУЛЬТИПЛЕКСОР ТЕЛЕКОММУНИКАЦИОННЫЙ МНОГОФУНКЦИОНАЛЬНЫЙ | 2004 |

|

RU2269154C1 |

| Устройство передачи и приема информации | 1991 |

|

SU1793454A1 |

| Информационно-управляющая система центрального теплового пункта жилых общественных и промышленных зданий | 1987 |

|

SU1511751A1 |

| Устройство передачи и приема информации | 1987 |

|

SU1453605A1 |

| Устройство для контроля движения транспортных средств | 1987 |

|

SU1538178A1 |

| ЦЕНТРАЛИЗОВАННАЯ ДИСПЕТЧЕРСКАЯ СИСТЕМА С РАСПРЕДЕЛЕННЫМИ КОНТРОЛИРУЕМЫМИ ПУНКТАМИ | 2003 |

|

RU2240245C1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1980 |

|

SU918944A1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах обработки информации, управления и измерения, в частности в устройствах приема униполярных старт-стоповых последовательных комбинаций импульсов для контроля отклонения длительности и количества импульсов от заданного значения, контроля местоположения импульсов в комбинации. Технический результат заключается в обеспечении возможности сохранения состояния группы выходов блока исполнительного при выключении питания. Технический результат достигается за счет блока исполнительного, который содержит программник, схему начальной установки, схему кварцевого генератора, последовательный интерфейс, схему согласования приемника, схему согласования передатчика, схему установки адреса, запоминающее устройство, схему управления, схему контроля питания, первую схему совпадения, вторую схему совпадения, схему контроля целостности коммуникаций. 1 з.п. ф-лы, 1 ил.

1. Блок исполнительный, содержащий запоминающее устройство, схему начальной установки, выход которой соединен с первым входом программника, второй вход и первый выход которого соединены с выходом и входом схемы кварцевого генератора соответственно, третий вход программника соединен с выходом схемы согласования приемника, вход которой соединен с выходом последовательного интерфейса, вход/выход которого является входом/выходом блока исполнительного, а вход соединен с выходом схемы согласования передатчика, вход которого соединен со вторым выходом программника, первая группа выходов которого соединена с группой входов схемы управления, первая группа выходов которой соединена с группой входов первой схемы совпадения, группа выходов которой является первой группой выходов блока исполнительного, а вход соединен с выходом схемы контроля питания, отличающийся тем, что дополнительно введены вторая схема совпадения и схема установки адреса, группа входов которой является группой входов блока исполнительного, а вход и группа выходов соединены соответственно с третьим выходом и первой группой входов программника, вторые группы выходов и входов которого соединены соответственно с группами входов и выходов запоминающего устройства, при этом вторая группа выходов схемы управления соединена с группой входов второй схемы совпадения, группа выходов которой является второй группой выходов блока исполнительного, а выход соединен с четвертым входом программника, пятый вход которого соединен с выходом первой схемы совпадения.

2. Блок исполнительный по п. 1, отличающийся тем, что дополнительно введена схема контроля целостности коммуникаций, первый вход и выход которой являются соответственно входом и выходом блока исполнительного, а второй вход соединен с четвертым выходом программника.

| БЛОК ИСПОЛНИТЕЛЬНЫЙ | 2009 |

|

RU2406111C1 |

| Способ изготовления магнезитовых изделий | 1935 |

|

SU50018A1 |

| СПОСОБ ПОЛУЧЕНИЯ ИСКУССТВЕННОЙ СМОЛЫ | 1939 |

|

SU57930A1 |

| МНОГОКАНАЛЬНАЯ АППАРАТУРА ПЕРЕДАЧИ ДАННЫХ | 2009 |

|

RU2406121C2 |

| Устройство для измерения температуры с частотным выходом | 1986 |

|

SU1397747A1 |

Авторы

Даты

2016-04-10—Публикация

2015-03-20—Подача