Изобретение относится к технике радиосвязи и может использоваться для передачи коротких сообщений, например, кодограмм.

Известна сеть передачи данных, обеспечивающая передачу сообщений между главной станцией и несколькими подчиненными станциями, каждая из которых содержит передатчик, приемник и формирователь управляющего сигнала.

Недостаток этого устройства в том, что подчиненные станции не обеспечивают самостоятельное вхождение в связь с главной станцией, а так же имеют низкую помехоустойчивость.

Известно устройство передачи и приема информации, содержащее последовательно соединенные блок ввода сообщений, кодер, передатчик, управляющий вход которого соединен с выходом схемы совпадения, последовательно соединенные приемник, декодер и блок контроля занятости канала, один вход которого соединен с

выходом приемника, другой вход соединён с выходом хронизатора, третий вход соединен с выходом декодера, а выход соединен с первым входом схемы совпадения, второй вход которой соединен с выходом блока ввода сообщений.

Недостаток указанного устройства заключается в низкой пропускной способности и помехоустойчивости.

Наиболее близким по технической сущности и достигаемому положительному эффекту, к заявляемому устройству является устройство передачи и приема информации.

Прототип содержит приемник, второй вход которого соединен с выходом антенно- фидерной системы, а выход соединен со входом декодера, первый выход которого является выходом устройства передачи и приема информации, а второй выход соединен с третьим входом блока контроля занятости канала, второй вход которого соединен с выходом приемника, а выход со вторым входом схемы совпадения, выход

С

Л Q

ы

4 СЛ

которой параллельно подключен к третьим входам приемника и передатчика, а также к первому входу блока ввода сообщений, второй вход которого является входом устройства передачи и приема информации. Первый выход соединен со входом кодера, выходом соединенного с первым входом передатчика, а второй выход соединен с первым входом формирователя приоритетов, выход которого соединен с первым входом схемы совпадения, а второй вход соединен с первым выходом хронизатора, третий выход которого соединен с первым входом блока контроля занятости канала, а второй выход соединен со входом формирователя кода частоты, второй выход которого соединен с первым входом приемника, а первый выход соединен со вторым входом передатчика, выход которого соединен со входом антенно фидерной системы.

Недостатком прототипа является низкая помехоустойчивость в условиях мультипликативных помех.: ri .

Целью изобретенияГ является пЪвыше- ние помехоустойчивости устройства.

Поставленная цель достигается тем, что в устройство передачи и приема информации; содержащее передатчик, у которого выход подключен к антенно-фидерной системе, информационный вход к кодеру, а вход частотной перестройки соединен с первым выходом формирователя кода час- тоты, второй выход которого соединён с входом частотной перестройки приемника, а вход с выходом временного цикла хронизатора, выход интервала занятости канала которого соединён с входом синхронизации блока контроля занятости, канала, у которого информационный вход объединен с входом декодера и через приемник соединен с антенно-фидерной системой, управляющий вход соединен с выходом структуры преобразуемой информации декодера, а выход соединен с вторым входом схемы совпадения, выход которой соединен с входами блокировки передатчика w приемника и входом разрешения считывания блока ввода сообщений, выход кода приоритета которого соединен с входом формирователи приоритетов, кроме того содержит блок формирования, блок инвертирования и блок управлений, у которого первый вход соеди- н ён с Шх одом вреТмё интервала пёре- . дачи, второй вход с: выходом управления блока инвертирования, третий вход - с информационным выходом этого блока, четвертый вход - с выходом формирователя приоритетов, пятый вход - объединен с информационным входом блока инвертирования и подключен к информационному

выходу 5лока ввода сообщений, шестой вход - с выходом окончания передачи блока формирования, седьмой вход - объединен с входом синхронизации блока контроля занятости канала, первый выход подключен к входу кодера, второй выход - к управляющему входу блока формирования, третий выход - к управляющему входу блока инвертирования, четвертый выход - первому входу

0 схемы совпадений, а пятый выход - к тактовому входу формирователя, кроме того информационный выход декодера соединен с информационным входом блока формирования.

5 Блок формирования содержит генератор тактовых импульсов, второй вход которого является вторым входом первой схемы совпадения, со входом линии задержки, выход которой соединен параллельно со вто0 рым входом второй схемы совпадения и со входом первого совпадения, и со. вторым входом счетчика импульсов выходом соединенного со входом дешифратора, выход которого является вторым выходом блока

5 формирования и соединен параллельно с первым входом генератора тактовых импульсов, с первым входом счетчика импульсов и со входом Второго инвертора, выход которого соединен с первым входом второй

0 схемы совпадения, выходом параллельно соединенной с о вторым входом второго регистра, первый вход которого соединен с выходом третьего регистра, входы с номерами от 3 до п/2+2 соединены с выходами

5 первого регистра с номерами от 1 до n/2, a выход является первым выходом блока формирования, и с первым входом третьего регистра, входы которого с номерами от 2 до п/2+1 соединены с выходами первого реги0 стра с номерами от п + 1 до 3/2п, входы которого с номерами от 2 до 2п + 1 параллельно соединены с выходом первой схемы совпадения, а первый вход является первым входом блока формирования.

5 Блок управления содержит первый реверсивный счетчик, который соединен первым входом с выходом четвертой схемы Совпадения, вторым входом соединен с выходом пятой схемы совпадения, а выходом

0 соед йнен со вторым входом первого триггера, первый вход которого является вторым входом блока управления, а выход является вторым выходом блока управления и параллельно соединен с первым входом первой

5 схемы совпадения, второй вход которой является третьим входом блока управления, а выход является первым выходом блока уп- . равления, со вторым входом пятой схемы совпадения и со входом первого инвертора, выход которого параллельно соединен с

первым входом второй схемы совпадения, второй вход которой является четвертым входом блока управления, а выход соединен с первым входом схемы ИЛИ, с первым входом третьей схемы совпадения, второй вход которой является пятым входом блока управления, а йыход является первым выходом блока управления, со вторым входом четвертой схемы совпадения, и со вторым входом шестой схемы совпадения, первый вход которой совместно с первыми входами четвертой и пятой схем совпадения является первым входом блока управления, а выход соединен с первым входом десятой схемы совпадения, выход которой является пятым выходом блока управления, а второй вход соединен с выходом второго инвертора, с которым также соединен второй вход второй схемы ИЛИ, выход которой является четвёртым выходом блока управления, и второй вход восьмой схемы совпадения, первый вход которой совместно с первым входом девятой схемы совпадения является седьмым входом блока управления, а выход Соединен с первым входом второго реверсивного счетчика, второй вход которого со- едйнен с выходом девятой схемы, совпадения, а выход соединен с первым входом второго триггера, второй вход которого является шестым входом блока управления, а выход параллельно соединен со вторым входом девятой схемы совпадения, со входом второго инвертора и является также выходом блока управления,

Блок инвертирования содержит генератор тактовых импульсов, первый вход которого является вторым входом блока инвертирования, а выход параллельно соединен со входом линии задержки, соединенный со входом первого инвертора и с первым входом второй схемы совпадения второй вход которой соединен с выходом второго инвертора, а выход соединен с первым входом второго регистра, с первым входом счетчика импульсов, выход которого соединен со входом дешифратора, выход которого соединен со вторым входом генератора тактовых импульсов, со вторым входом счетчика импульсов, а также является вторым выходом блока инвертирования, и с первым входом первой схемы совпадения, второй вход которой соединен с выходом первого инвертора, а выход соединен с п входами считывания первого регистра, вхоД записи которого является первым входом блока инвертирования, а п информационных выходов которого соединены с п входами второго регистра, выход которого является первым выходом блока инвертирования.

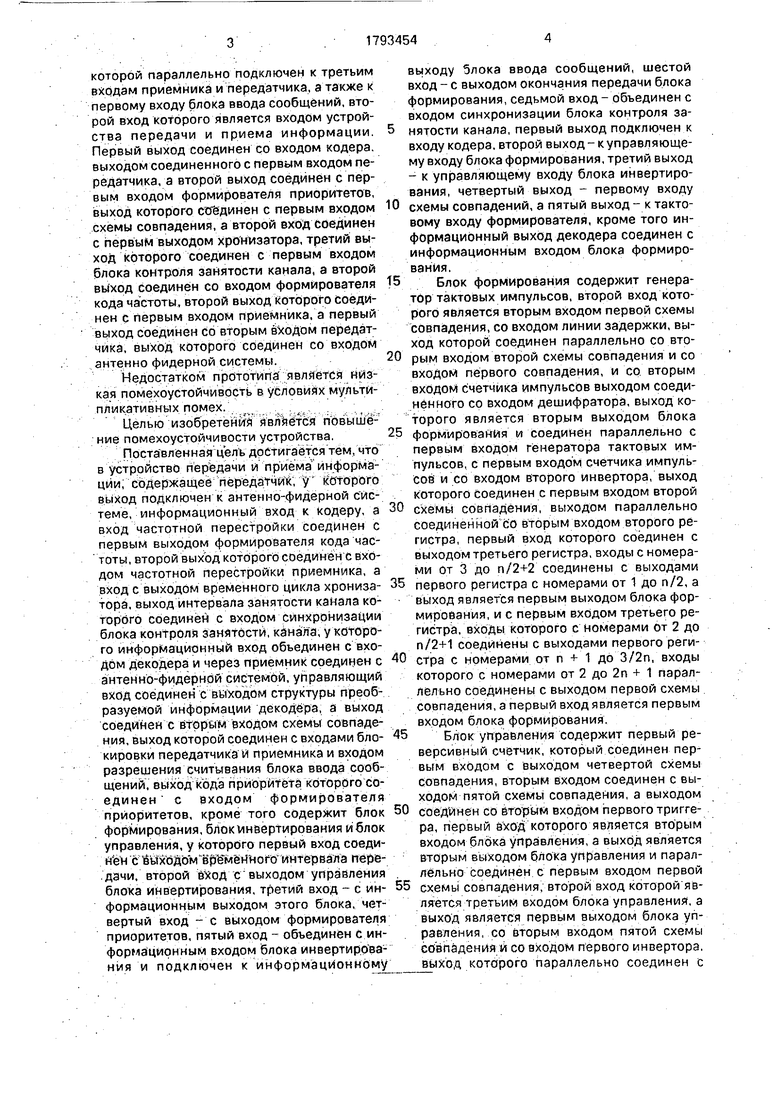

Изобретение поясняется фиг. 1-7. Структурная схема заявляемого устройства приведена на фиг. 1, где цифрами обозначено: 1 - блок ввода сообщений, 2 - кодер, 5 3 - передатчик, 4 - формирователь приоритетов, 5 - хронизатор, б - формирователь кода частоты, 7 - элемент И, 8 - блок контроля занятости канала, 9 - приемник, 10 - декодер, 11 - блок формирования кодог0 рамм, 12 - блок управления, 13 - блок инвертирования, 14 - вход устройства передачи и приема информации, 15 - выход устройства передачи и приема информации. Блок формирования кодограмм 11 пред5 назначен для приема и хранения кодограммы, приема и хранения инвертированной кодограмм, формирования комбинированной кодограммы и передачи её на выход 15 устройства передачи и приема информации.

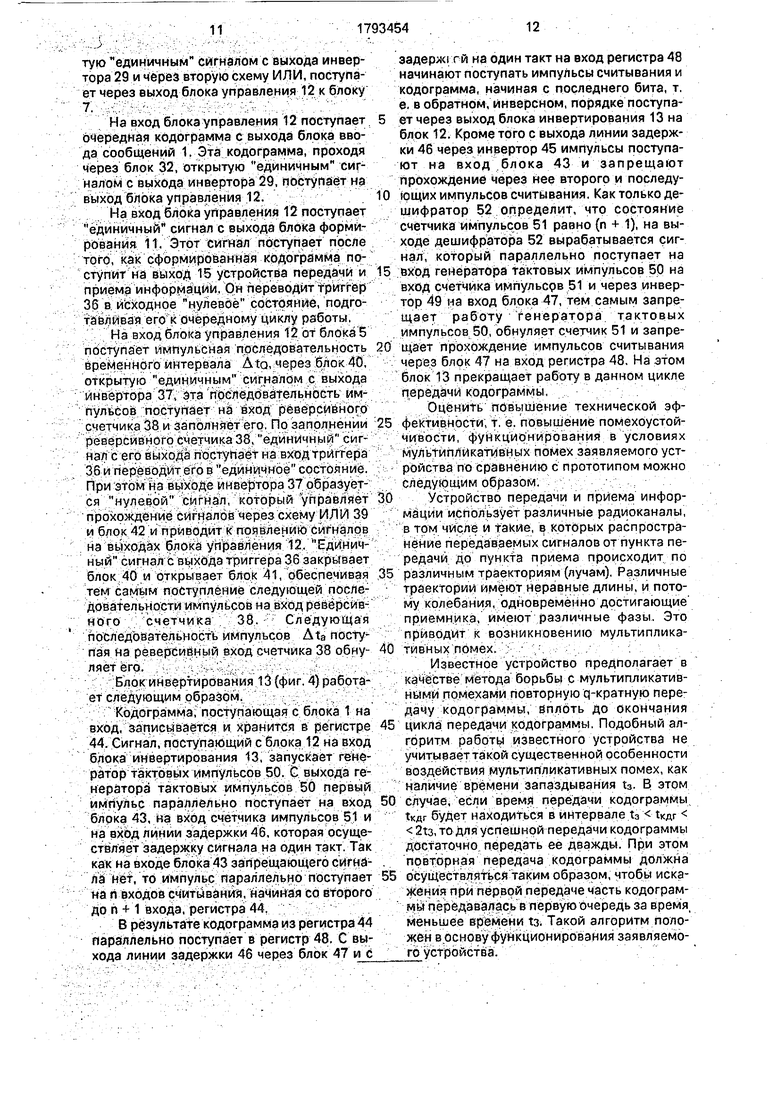

0 Структурная схема блока формирования 11 представлена на фиг. 2, где цифрами обозначено: 16 - первый регистр, 17 - второй регистр, 18 - третий регистр, 19 - первый элемент И, 20 - первый инвертор, 21 5 вторая схема совпадения, 22 - линия передачи, 23 - второй инвертор, 24. - дешифратор, 25 - счетчик импульсов, 26 - генератор тактовых импульсов.

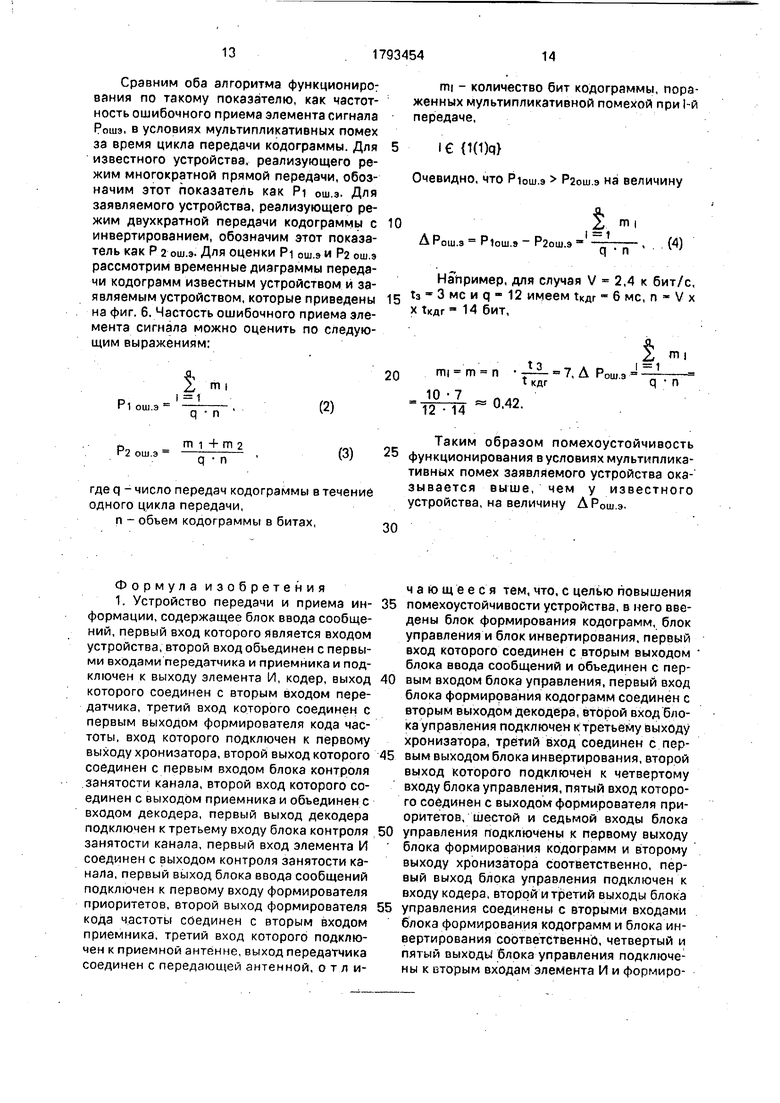

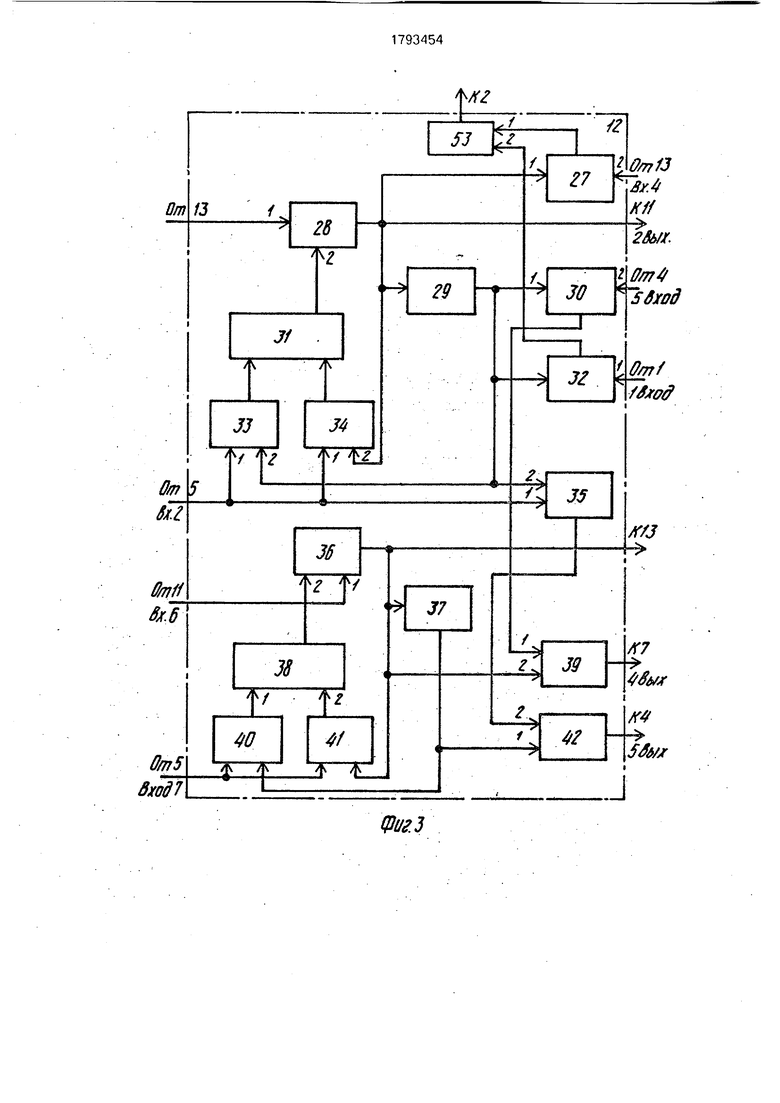

Блок управления 12 предназначен для0 координации процессов передачи, приема, инвертирования и формирования кодограмм путем создания и передачи в другие блоки соответствующих управляющих сигналов. Структурная схема блока управления

5 12 представлена на фиг. 3, где цифрами обозначено: 27 - первый элемент И, 28 - первый триггер, 29 - первый инвертор, 30 - второй элемент И, 31 - первый реверсивный счетчик, 32 - третий элемент И,.3.3 - четвер0 тый элемент И, 34 - пятый элемент И, 35 - шестой элемент И, 36 - второй триггер, 37 - второй инвертор, 38 - второй реверсивный счетчик, 39 - вторая схема ИЛИ, 40 - восьмой элемент И, 41 - девятый элемент И, 42

5 - десятый элемент И, 53 - первая схема ИЛИ,

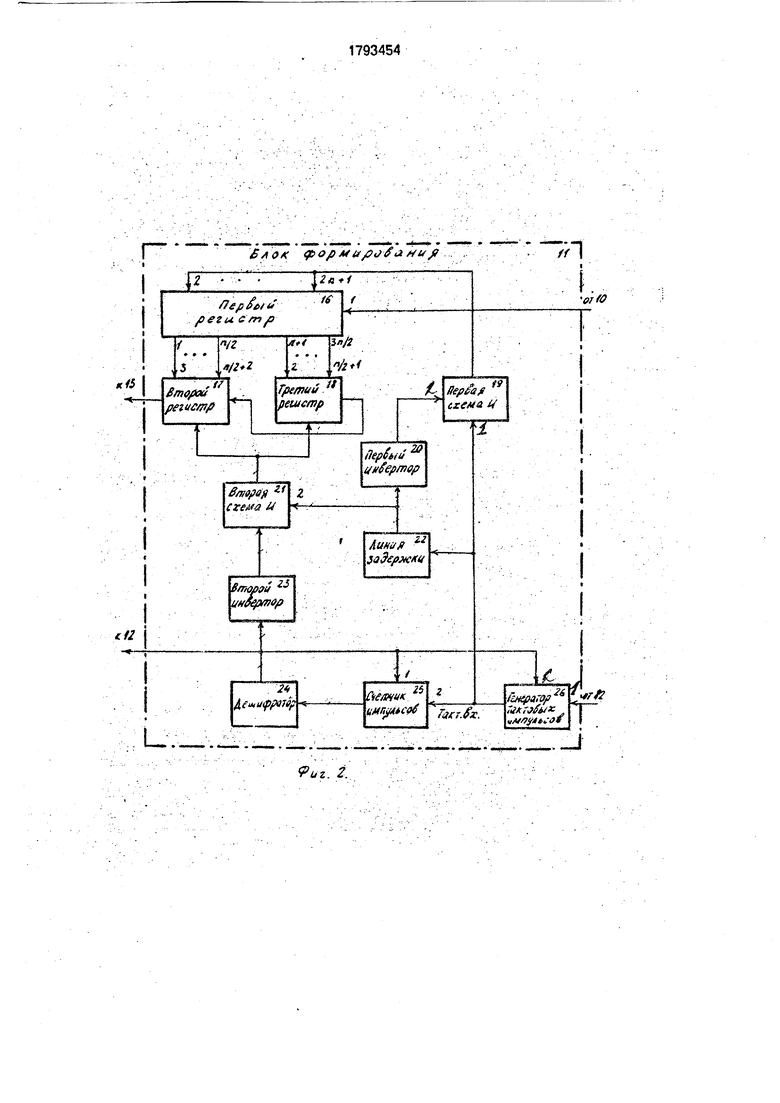

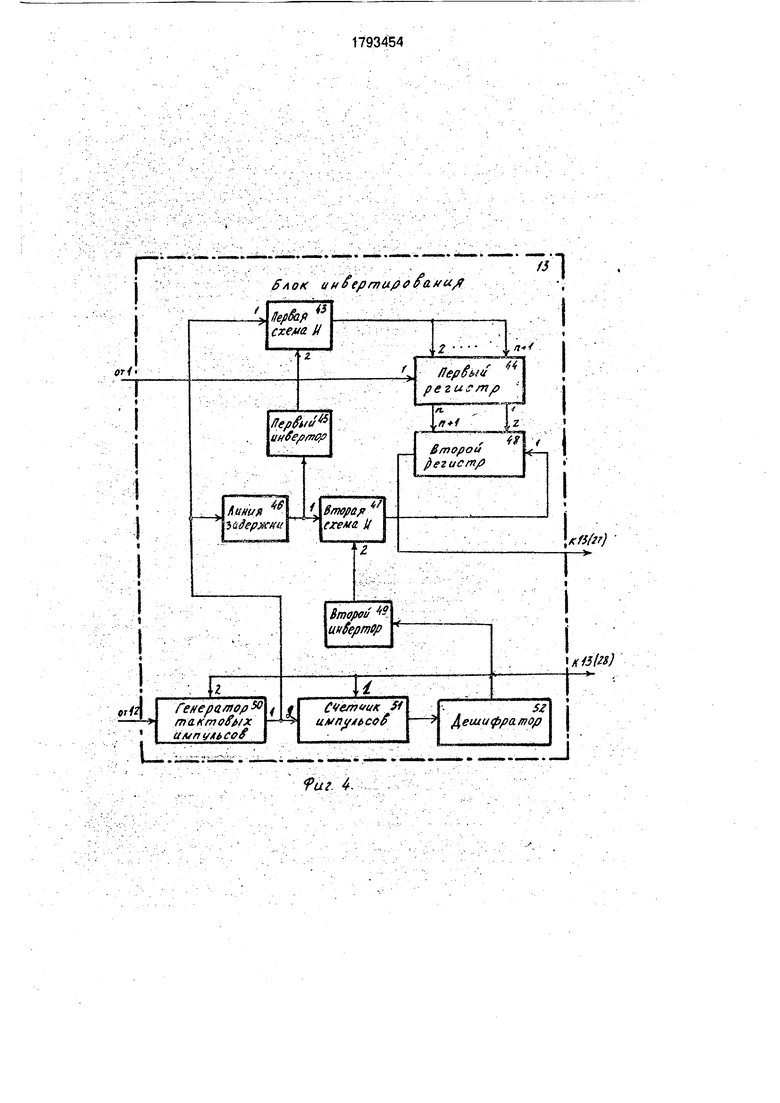

Блок инвертирования 13 предназначен для получения,хранения, инвертирования и передачи кодограммы в порядке обратном

0 исходному. Структурная схема блока инвертирования 13 представлена на фиг, 4, где цифрами обозначено: 43 - первая схема совпадения, 44 - первый регистр, 45 - первый инвертор,4б - вторая схема совпадения, 48

5 - второй регистр, 49 - второй инвертор, 50 - генератор тактовых импульсов, 51 - сметчик импульсов, 52-дешифратор.

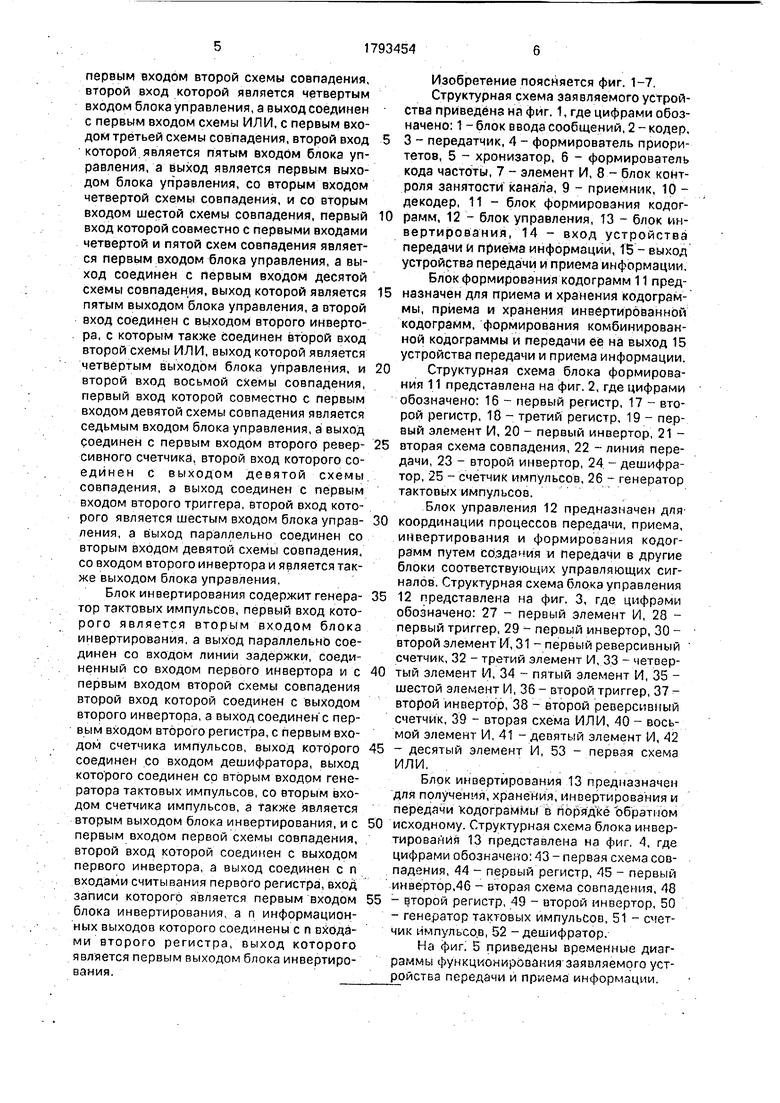

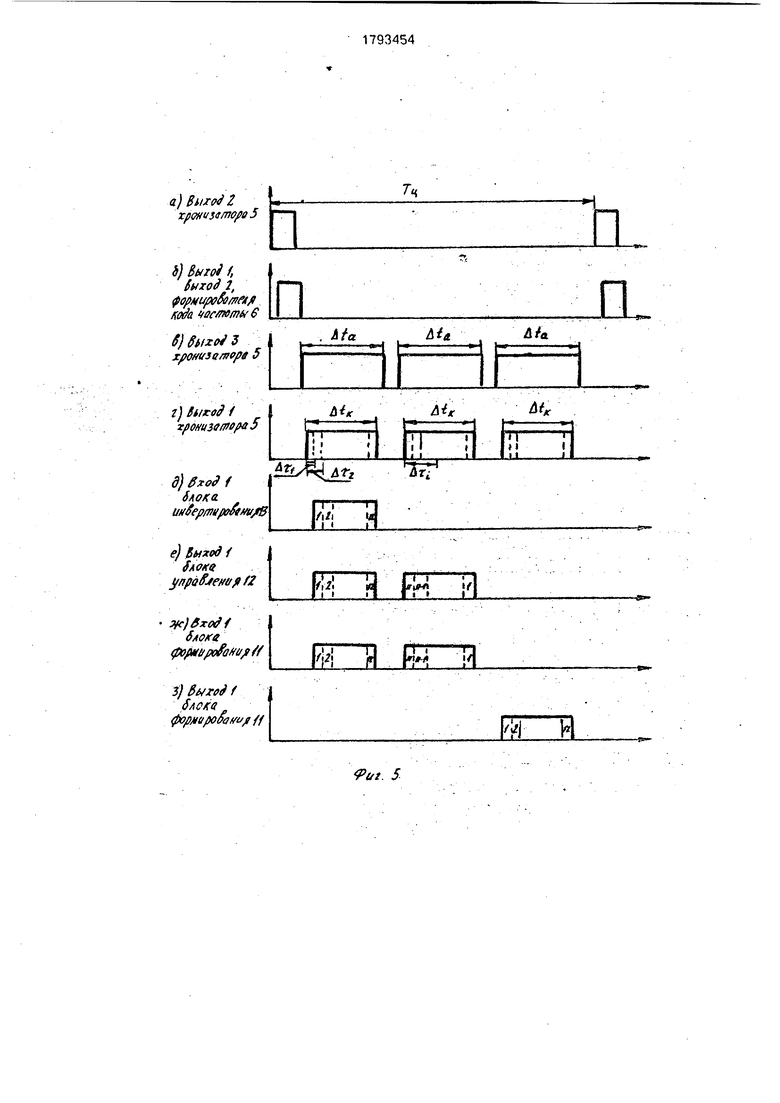

На фиг; 5 приведены временные диаграммы функционирования заявляемрго устройства передачи и приема информации.

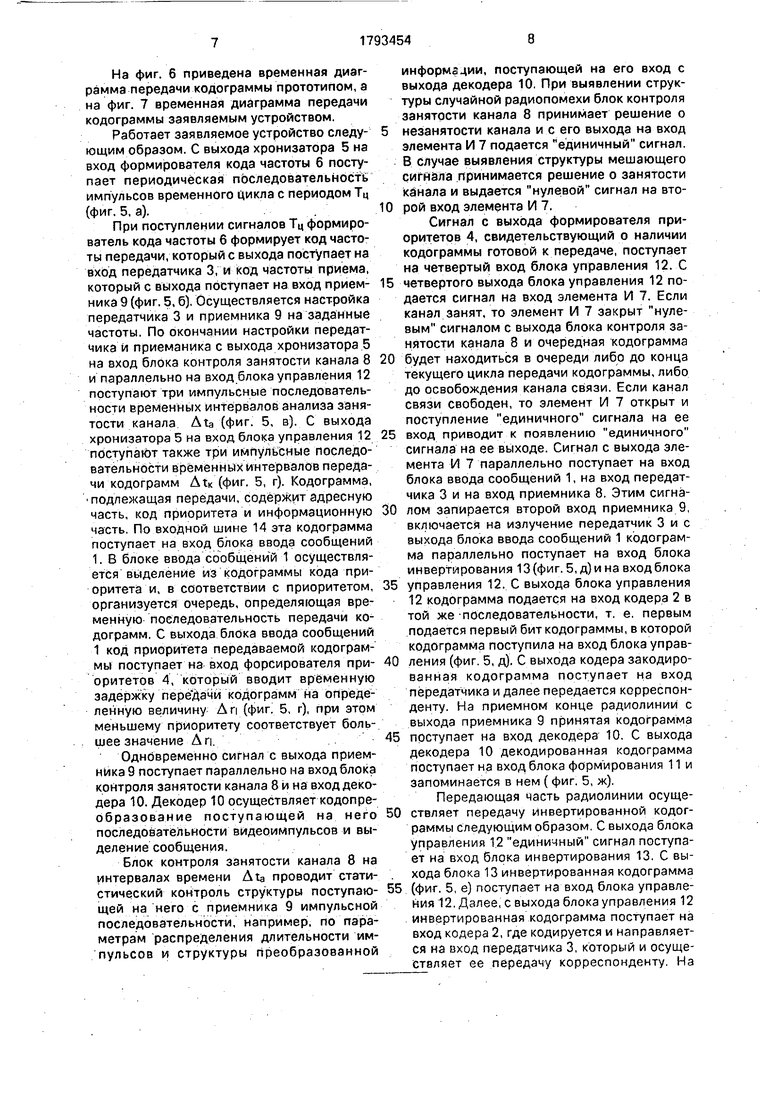

На фиг. 6 приведена временная диаграмма передачи кодограммы прототипом, а на фиг. 7 временная диаграмма передачи кодограммы заявляемым устройством.

Работает заявляемое устройство следующим образом. С выхода хронизатора 5 на вход формирователя кода частоты 6 поступает периодическая последовательность импульсов временного цикла с периодом Тц (фиг. 5, а).

При поступлении сигналов Тц формирователь кода частоты 6 формирует код частоты передачи, который с выхода поступает на вход передатчика 3, и код частоты приема, который с выхода поступает на вход приемника 9 (фиг. 5, б). Осуществляется настройка передатчика 3 и приемника 9 на заданные частоты. По окончании настройки передатчика и приеманика с выхода хронизатора 5 на вход блока контроля занятости канала 8 и параллельно на вход блока управления 12 поступают три импульсные последовательности временных интервалов анализа занятости канала Ata (фиг. 5, в), С выхода хронизатора 5 на вход блока управления 12 поступают также три импульсные последовательности временных интервалов передачи кодограмм AtK (фиг. 5, г). Кодограмма, подлежащая передачи, содержит адресную часть, код приоритета и информационную часть. По входной шине 14 эта кодограмма поступает на вход блока ввода сообщений 1. В блоке ввода сообщений 1 осуществляется выделение из кодограммы кода приоритета и, в соответствии с приоритетом, организуется очередь, определяющая временную последовательность передачи кодограмм, С выхода блока ввода сообщений 1 код приоритета передаваемой кодограммы поступает на вход форсирователя приоритетов 4, который вводит временную задержку пере дачй кодограмм на определенную величину An (фиг 5, г), при этом меньшему приоритету соответствует большее значение А п...

Одновременно сигнал с выхода приемника 9 поступает параллельно на вход блока контроля занятости канала 8 и на вход декодера 10. Декодер 10 осуществляет кодопре- образование поступающей на него последовательности видеоимпульсов и выделение сообщения.

Блок контроля занятости канала 8 на интервалах времени Ata проводит статистический контроль структуры поступающей на него с приемника 9 импульсной последовательности, например, по параметрам распределения длительности импульсов и структуры преобразованной

информздии, поступающей на его вход с выхода декодера 10. При выявлении структуры случайной радиопомехи блок контроля занятости канала 8 принимает решение о

незанятости канала и с его выхода на вход элемента И 7 подается единичный сигнал. В случае выявления структуры мешающего сигнала принимается решение о занятости канала и выдается нулевой сигнал на вто0 рой вход элемента И 7.

Сигнал с выхода формирователя приоритетов 4, свидетельствующий о наличии кодограммы готовой к передаче, поступает на четвертый вход блока управления 12. С

5 четвертого выхода блока управления 12 подается сигнал на вход элемента И 7. Если канал занят, то элемент И 7 закрыт нулевым сигналом с выхода блока контроля занятости канала 8 и очередная кодограмма

0 будет находиться в очереди либо до конца текущего цикла передачи кодограммы, либо до освобождения канала связи. Если канал связи свободен, то элемент И 7 открыт и поступление единичного сигнала на ее

5 вход приводит к появлению единичного сигнала на ее выходе. Сигнал с выхода элемента И 7 параллельно поступает на вход блока ввода сообщений 1, на вход передатчика 3 и на вход приемника 8. Этим сигна0 лом запирается второй вход приемника 9, включается на излучение передатчик 3 и с выхода блока ввода сообщений 1 кодограмма параллельно поступает на вход блока инвертирования 13 (фиг. 5, д) и на вход блока

5 управления 12. С выхода блока управления 12 кодограмма подается на вход кодера 2 в той же последовательности, т. е. первым .подается первый бит кодограммы, в которой кодограмма поступила на вход блока управ0 ления (фиг. 5, д). С выхода кодера закодированная кодограмма поступает на вход передатчика и далее передается корреспонденту. На приемном конце радиолиний с выхода приемника 9 принятая кодограмма

5 поступает на вход декодера 10. С выхода декодера 10 декодированная кодограмма поступает на вход блока формирования 11 и запоминается в нем (фиг. 5, ж).

Передающая часть радиолинии осуще0 ствляет передачу инвертированной кодограммы следующим образом. С выхода блока управления 1.2 единичный сигнал поступает на вход блока инвертирования 13. С выхода блока 13 инвертированная кодограмма

5 (фиг. 5, е) поступает на вход блока управления 12, Далее, с выхода блока управления 12 инвертированная кодограмма поступает на вход кодера 2, где кодируется и направляется на вход передатчика 3, который и осуществляет ее передачу корреспонденту. На

приемном конце радиолинии с выхода приемника 9 принятая инвертированная кодограмма, поступает на вход декодера 10, С выхода декодера 10 декодированная инвертированная кодограмма поступает на вход блока формирования 11 и запоминается в нем. С выхода блока формирования 11 единичный сигнал поступает на вход блока управления 12. С выхода блока формирования 11 сформированная кодограмма поступает на выход 15 устройства передачи и приема информации. На этом цикл передачи и приема кодограммы заканчивается.

Блок формирования 11 (фиг. 2) работает таким образом, что записанные в первом регистре 16 копии кодограммы (прямая и инверсная) по сигналу, поступающему на вход блока 11, перезаписывается во второй регистр 17 и третий регистр 18. Перезапись происходит следующим образом,

Сигнал, поступающий на вход блока формирования 11, запускает генератор тактовых импульсов 26. С выхода генератора тактовых импульсов 26 первый импульс параллельно поступает на вход блока 19, на второй вход счетчика импульсов и на вход линии задержки 22, которая осуществляет задержку сигнала на один такт. Так как на входе элемента И запрещающего сигнала нет, что импульс поступает на входы считывания первого регистра 16. При этом для того, чтобы в комбинированной кодограмме порядок следования информационных импульсов соответствовал исходному первая половина кодограммы с 1 по п/2 выходов первого регистра 16 поступает на входы с 3 до п/2+2 второго регистра 17 соответственно и запоминается в нем. Вторая часть кодограммы с п + 1 по 3/2п выходов первого pernctpa 16 поступает на входы со 2 по п/2+ + 1 третьего регистра 18 соответственно, и запоминается в нем. Затем с выхода линии задержки 22 через блок 21 с задержкой на один такт на вход второго регистра 17 и на вход третьего регистра 18 параллельно начинают поступать импульсы считывания и кодограмма поступает на выход блока формирования 11 в требуемой последовательности. Кроме того с выхода линии задержки 22 через инвертор 20 импульсы поступают на вход блока 19 и запрещают прохождение через нее второго и последующих импульсов считывания. Как только дешифратор 24 определит, что состояние счетчика импульсов 25 равно (п + 1), на выходе дешифратора 24 вырабатывается сигнал, который параллельно поступает на вход генератора тактовых импульсов 26. на вход счетчика импульсов 25 и через инвертор 23 на вход блока 21, тем самым запрещает работу генератора тактовых импульсов 26, обнуляет счетчик импульсов 25 и запрещает прохождение импульсов считывания через блок 21 на входы регистров 17 и 18. На этом блок 11

прекращает работу в данном цикле передачи кодограммы.

Блок управления 12 работает (фиг. 3) следующим образом.

В исходном положении триггер 28 и

триггер 36 находятся в нулевом состоянии, соответственно на выходе первого инвертора 29 и на выходе второго инвертора 37 будут единичные сигналы.

На вход блока управления 12 от хронизатора 5 поступает импульсная последовательность временного интервала At. Через блок 35, открытую единичным сигналом с выхода инвертора 29 и блок 42, открытую единичным сигналом с выхода

инвертора 37, последовательность импульсов временного интервала поступает Через выход блока управления 12 к блоку 4, Через блок 33, открытую единичным сигналом с выхода инвертора 29, эта последовательность импульсов A tic поступает на вход реверсивного счетчика 31 и заполняет его. По заполнении реверсивного счетчика 31 единичный сигнал с его выхода поступает на вход триггера 28 и переводит его в единичное состояние. При этом на выходе инвертора 29 образуется нулевой сигнал, который закрывает прохождение сигналов через блок 30, блок 32, блок 33 и блок 35. Единичный сигнал с выхода триггера 28

открывает блок 34, тем самым обеспечивая поступление следующей последовательности импульсов АТ.К на вход реверсивного счетчика 31. Следующая последовательность импульсов AtK, поступающая на реверсивный вход реверсивного счетчика 31 обнуляет его.

На вход блока управления 12 поступает единичный сигнал с выхода блока инвертирования 13. Этот сигнал поступает после

завершения передачи инвертированной кодограммы. Он переводит триггер 28 в исходное нулевое состояние,подготавливая его к очередному циклу работы.

На вход блока управления 12 от блока

13 поступает инвертированная кодограмма. Через блок 27, открытую единичным сигналом с выхода триггера 28, инвертированная кодограмма поступает через выход блока управления 12 на блок 2,

На сход блока управления 12 поступает сигнал с выхода формирователя приоритетов 4, который несет информацию о том, что очередная кодограмма готова к передаче. Этот сигнал, проходя через блок 30, открытую единичным сигналом с выхода инвертора 29 и через вторую схему ИЛИ, поступает через выход блока управления 12 к блоку

. :-Я-й: -Ь;:/ ::у--л:;-;: .;- :..f. Л На вход блока управления 12 поступает очередная кодограмма с выхода блока ввода сообщений -1. Эта кодограмма, проходя через блок 32, открытую единичным11 сигналов с выхода инверторе 29, поступает на выход блока управления 12.

Наi входiблока управления 12 поступает единичный сигнал с выхода блока формирования i1, Этот сигнал поступает после того, как сформированная кодограмма ncf- ступит на Bbixojai 15 устройства передачи и приёма инфорйа:ций, Он переводит триггер 36 в: й сходнре нулевдё состояние, подго- его; к очередному циклу работы. На вход блока управления 12 от блока 5

поступает импульсная последовательность

временного -интервалаДЧа,:чере ;тк40,

открытую единичным сигналом с выхода

V йнвертдра:37;,эта п сле;довё1тельност импульсой :поступает на йход реверсивного

счетчика 38 и заполняет его, По заполнений

- ё:ае; р..сДётч и.к:а -38/.ёдйн йч ый 1 сигнал с; его выхоДй постуИа|т н:а;вход триггера

36 и переводйт е гр В единичное состояние.

При этом из ёьифйе инвертора .разуетсяi нулевой сигнал,который управляет

про хр кденйё сйгйалов;чёрез схему ИЛИ 39 и блок 42 и приводит к пр аЛен юГсйт налов

. йа вУхрдах блрй упрабления -12.Едй(нич-; ный сигнал с выхода триггера 3.6 закрьтает блок.46 и открывает блок 41, обеспечивая тем бамгым поступление следующей после- доват ель ортй ммпулйсов на вход реверсивного счетчика .38. ;; Следующая последовательностЪ импульсов Ata поступая на реверсивный вход счетчика 38 обнуляет его. /;.: J .-- -.. ;:/. ;Бяок; инвертирования .13 (фиг 4) рабрта- ;етследующимрбразом. :- -6 :.; ,.;: : . / -/: ь ;1(одЬ | р .а м)Ц аГпрсту:пающэя с блока 1 на вход, записывается и хранится в регистре 44. Сигнал, поступающий с блока 12 на вход блока инвертирования 13, запускает генератор тактовых импульсов 50. С выхода генератора тактовых импульсов 50 первый импульс параллельно поступает на вход блока 43, на вход счетчика импульсов 51 и на вход линии задержки 46, которая осуществляет задержку сигнала на один такт. Так как на входе блока 43 запрещающего сигнала нет, то импульс парал лельнб поступает

а ri входЫв считйванйгя, наМййая со второго до h-И входа, регистра 44. ; J

В результате кодограмма из регистра 44 параллельно поступает в регистр 48. С выхода линии задержки 46 через блок 47 и с

задерж г и на один такт на вход регистра 48 начинают поступать импульсы считывания и кодограмма, начиная с последнего бита, т, е. в обратном, инверсном, порядке поступа5 ет через выход блока инвертирования 13 на блок 12. Кроме того с выхода линии задержки 46 через инвертор 45 импульсы поступают на вход блока 43 и запрещают Прохождение через нее второго и последу0 Ющйх импульсов считывания. Как только дешифратор 52 определит, что состояние счетчика импульсов 51 равно (п + 1), на выходе дешифратора 52 вырабатывается сигнал, который параллельно поступает на

5 ; вход генератора тактовых импульсов 50 на вход счетчика им пул ьср в 51 и через инвертор 49 на вход блока 47, тем самым запрещает работу генератора тактовых импульсов 50, обнуляет счетчик 51 и запре0 Щает прохождение импульсов считывания через блок 47 на вход регистра 48. На этом блок 13 прекращает работу в данном цикле передачи кодограммы,

Оценить повышение технической эф5 фективнрсти; Т. е. повышение помехоустойчивости, функционирования в условиях

мультипликативных помех заявляемого устi ройства по сравнению с прототипом можно следующим образом.у ..:

0 Устройство передачи и приема инфор- 7 мации использует различные радиоканалы, в том числе и такие, в: которых распространение передаваемых сигналов от пункта передачи до пункта приема происходит, по

5 различным траекториям (лучам), Различные траекторий имеют неравные длины, и потому колебания, одновременно достигающие приемника, имеют различные фазы. Это приводит к возникновению мультиплика0 т1/1вных .пОмех : . ;:. :; : .-

Известное устройство предполагает в качестве метода борьбы с мультипликативными помехами повторную q-кратную передачу кодограммы, вплоть до окончания

5 цикла передачи кодограммы, Подобный алгоритм работу известного устройства не учиты взет такой существен ной особен кости воздействия мультипликативных помех, как наличие времени запаздывания t3. В этом

0 случае если время передачи кодограммы Ткдг будет находиться в интервале t3 1кдг 2t3, то для успешной передачи кодограммы достаточно передать ее дважды. При этом повторная передача кодограммы должна

5 бсуЩествлятьсй таким образом, чтобы иска- при пёрврй передаче часть кодограм- мы пёрёдав;алась 8 первую очередь за время1 меньшее времени t3. Такой алгоритм положен в основу фуйкционйрованйя заявл яемо- ; го устрдйства.

Сравним оба алгоритма функциониро: вания по такому показателю, как частотность ошибочного приема элемента сигнала Рошэ, в условиях мультипликативных помех за время цикла передачи кодограммы. Для известного устройства, реализующего режим многократной прямой передачи, обозначим этот показатель как PI ош.э. Для заявляемого устройства, реализующего режим двухкратной передачи кодограммы с инвертированием, обозначим этот показатель как Р 2 ош.э. Для оценки Рч ош.э и Р2 ош.э рассмотрим временные диаграммы передачи кодограмм известным устройством и заявляемым устройством, которые приведены на фиг. 6. Частость ошибочного приема элемента сигнала можно оценить по следующим выражениям:

Ј

i 1

m i

q п

(2)

mi - количество бит кодограммы, пораженных мультипликативной помехой при 1-й передаче,

5l€ {1(1)q}

Очевидно, что Pioiu.s Р2ош.э на величину

102. m i

А РОШ.З Ploui.9 Р2ош.э ,

(4)

Например, для случая V 2,4 к бит/с, 15 ta - 3 мс и q - 12 имеем 1кдг - 6 мс, п - V х х 1кдг 14 бит,

i

ГП|

0

mi m n

t 3-т А П I 1

7, А РОШ.Э

10 -7 12 14

t КДГ

q П

0.42.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство передачи и приема информации | 1987 |

|

SU1453605A1 |

| УСТРОЙСТВО ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ | 1996 |

|

RU2107995C1 |

| Устройство для приема избыточных сигналов | 1989 |

|

SU1695353A1 |

| Устройство передачи и приема информации | 1982 |

|

SU1083382A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ ТОЧНОГО ВРЕМЕНИ | 1990 |

|

RU2033640C1 |

| Устройство передачи и приема информации | 1986 |

|

SU1478355A1 |

| Система передачи и приема дискретной информации | 1980 |

|

SU944146A1 |

| РАДИОСТАНЦИЯ | 2004 |

|

RU2280950C2 |

| Устройство для приема информации | 1986 |

|

SU1336074A1 |

| Устройство управления доступом к общему каналу связи | 1985 |

|

SU1290569A1 |

Предлагаемое устройство может быть использовано для передачи коротких сообщений, например команд управления, между совокупностью территориально распре- деленных радиостанций, Целью изобретения является повышение помехоустойчивости устройства. Устройство передачи и приема информации содержит блок ввода сообщений, кодер, передатчик, элемент И, приемник, декодер, блок контроля занятости канала, хроЯизатор, формирователь кода частоты, формирователь приоритета, блок инвертирования, блок управления и блок формирования кодог- рамм. 3 з. п. ф-лы, 7 ил.

Р2

m т + m 2 q n

(3)

где q - число передач кодограммы в течение одного цикла передачи,

п - объем кодограммы в битах,

Формула изобретения 1. Устройство передачи и приема информации, содержащее блок ввода сообщений, первый вход которого является входом устройства, второй вход объединен с первыми входами передатчика и приемника и подключен к выходу элемента И, кодер, выход которого соединен с вторым входом передатчика, третий вход которого соединен с первым выходом формирователя кода частоты, вход которого подключен к первому выходу хронизатора, второй выход которого соединен с первым входом блока контроля .занятости канала, второй вход которого соединен с выходом приемника и объединен с входом декодера, первый выход декодера подключен к третьему входу блока контроля занятости канала, первый вход элемента И соединен с выходом контроля занятости канала, первый выход блока ввода сообщений подключен к первому входу формирователя приоритетов, второй выход формирователя кода частоты соединен с вторым входом приемника, третий вход которого подключен к приемной антенне, выход передатчика соединен с передающей антенной, о т л иТаким образом помехоустойчивость функционирования в условиях мультипликативных помех заявляемого устройства оказывается выше, чем у известного устройства, на величину А РОШ.Э.

чающееся тем, что, с целью повышения

помехоустойчивости устройства, в него введены блок формирования кодограмм, блок управления и блок инвертирования, первый вход которого соединен с вторым выходом блока ввода сообщений и объединен с первым входом блока управления, первый вход блока формирования кодограмм соединен с вторым выходом декодера, второй вход блока управления подключен к третьему выходу хронизатора, третий вход соединен с первым выходом блока инвертирования, второй выход которого подключен к четвертому входу блока управления, пятый вход которого соединен с выходом формирователя приоритетов, шестой и седьмой входы блока

управления подключены к первому выходу блока формирования кодограмм и второму выходу хронизатора соответственно, первый выход блока управления подключен к входу кодера, второй и третий выходы блока

управления соединены с вторыми входами блока формирования кодограмм и блока инвертирования соответственно, четвертый и пятый выходы блока управления подключены к вторым входам элемента И и формирователя приоритетов соответственно, второй выход блока формирования является выходом устройства.

вторым входом счетчика импульсов, с первым входом первого элемента И и входом элемента задержки, выход которого подключен к первому входу второго элемента И и к входу первого инвертора, выход которого соединен со вторым входом первого элемента И, выход счетчика импульсов подключен к входу дешифратора, выход второго инвертора соединен с вторым входом второго элемента И, выход которого подключей к первому входу второго регистра памяти, выход первого элемента И подключен к объединенным входам группы первого регистра памяти, выходы группы которого подключены к соответствующим входам

группы второго регистра памяти, выход которого является вторым выходом блока инвертирования,

блока управления, первые входы четвертого, пятого и шестого элементов И являются вторым входом блока управления , первый вход первого триггера является третьим входом блока управления, второй вход первого триггера соединен с выходом первого реверсивного счетчика, первый и второй входы которого подключены соответственно к выходам четвертого и пятого элементов И, выход первого инвертора соединен с первыми входами второго и третьего элементов И и с вторыми входами четвертого и шестого элементов И, выход первого элемента ИЛИ является первым выходом блока управления, выход первого триггера соединен с вторым входом пятого элемента И, входом первого инвертора, первым входом первого элемента И и является вторым выходом блока управления, второй вход первого элемента И является четвертым входом блока

управления, выход первого элемента И подключен к первому входу первого элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, второй вход второго элемента И является пятым входом

блока управления, выход второго элемента И соединен с первым входом второго элемента ИЛИ, второй вход которого объединен с первым входом девятого элемента И. входом второго инвертора и подключен к

выходу второго триггера, выход второго триггера является третьим выходом блока управления, первый вход второго триггера является шестым входом блока управления, второй вход второго триггера соединен с выходом второго реверсивного счетчика, объединенные первый вход восьмого элемента И и второй вход девятого элемента И являются седьмым входом блока управления, выходы восьмого и девятого элементов

От%

И подключены к первому и второму входам второго реверсивного счетчика соответственно, выход второго инвертора соединен с вторым входом восьмого элемента и первым входом десятого элемента И, второй вход которого подключен к выходу шестого элемента И, выходы второго элемента И/1И и десятого элемента И являются соответст-. венно четвертым и пятым выходами блока управления.

9иг. 2.

Wfreen

frswjea

ut. 5

Фиг 7.

| Устройство передачи и приема информации | 1982 |

|

SU1083382A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1993-02-07—Публикация

1991-01-28—Подача